Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gm604-i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| dsPl | C33EPXXXGM3XX/6XX/7XX Product Family                                                                             |     |

|------|------------------------------------------------------------------------------------------------------------------|-----|

| 1.0  | Device Overview                                                                                                  |     |

| 2.0  | Guidelines for Getting Started with 16-Bit Digital Signal Controllers                                            |     |

| 3.0  | CPU                                                                                                              |     |

| 4.0  | Memory Organization                                                                                              |     |

| 5.0  | Flash Program Memory                                                                                             | 103 |

| 6.0  | Resets                                                                                                           | 111 |

| 7.0  | Interrupt Controller                                                                                             | 115 |

| 8.0  | Direct Memory Access (DMA)                                                                                       | 129 |

| 9.0  | Oscillator Configuration                                                                                         | 143 |

| 10.0 | Power-Saving Features                                                                                            | 153 |

| 11.0 | I/O Ports                                                                                                        | 163 |

| 12.0 | Timer1                                                                                                           |     |

| 13.0 |                                                                                                                  |     |

| 14.0 | Input Capture                                                                                                    | 219 |

| 15.0 | Output Compare                                                                                                   | 223 |

| 16.0 | <b>J</b>                                                                                                         |     |

| 17.0 | Quadrature Encoder Interface (QEI) Module                                                                        |     |

| 18.0 |                                                                                                                  |     |

| 19.0 |                                                                                                                  |     |

| 20.0 |                                                                                                                  |     |

| 21.0 | Controller Area Network (CAN) Module (dsPIC33EPXXXGM6XX/7XX Devices Only)                                        |     |

| 22.0 |                                                                                                                  |     |

| 23.0 | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                                                                  |     |

| 24.0 |                                                                                                                  |     |

| 25.0 |                                                                                                                  |     |

| 26.0 |                                                                                                                  |     |

| 27.0 |                                                                                                                  |     |

| 28.0 |                                                                                                                  |     |

| 29.0 |                                                                                                                  |     |

| 30.0 |                                                                                                                  |     |

|      | Instruction Set Summary                                                                                          |     |

| 32.0 | e e de la construcción de la constru |     |

| 33.0 |                                                                                                                  |     |

| 34.0 | High-Temperature Electrical Characteristics                                                                      |     |

|      | Packaging Information                                                                                            |     |

|      | endix A: Revision History                                                                                        |     |

|      | x                                                                                                                |     |

|      | Microchip Web Site                                                                                               |     |

|      | omer Change Notification Service                                                                                 |     |

|      | omer Support                                                                                                     |     |

| Prod | uct Identification System                                                                                        |     |

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Ref-erence Manual"*, which are available from the Microchip web site (www.microchip.com). These documents should be considered as the general reference for the operation of a particular module or device feature.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70000600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70000598)

- "Timers" (DS70362)

- "Input Capture" (DS70000352)

- "Output Compare" (DS70005157)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582)

- "Serial Peripheral Interface (SPI)" (DS70005185)

- "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70000195)

- "Data Converter Interface (DCI) Module" (DS70356)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70000357)

- "32-Bit Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Parallel Master Port (PMP)" (DS70576)

- "Device Configuration" (DS70000618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

| TABLE 1-1: PINC                              |             | J DESC         | КІРП    | ONS (CONTINUED)                                                                                                                             |

|----------------------------------------------|-------------|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                     | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                                                                                 |

| INDX1 <sup>(1)</sup>                         | I           | ST             | Yes     | Quadrature Encoder Index1 pulse input.                                                                                                      |

| HOME1 <sup>(1)</sup>                         | I           | ST             | Yes     | Quadrature Encoder Home1 pulse input.                                                                                                       |

| QEA1 <sup>(1)</sup>                          | I.          | ST             | Yes     | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer                                                                              |

| QEB1 <sup>(1)</sup>                          | I           | ST             | Yes     | external clock input in Timer mode.<br>Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer<br>external gate input in Timer mode. |

| CNTCMP1 <sup>(1)</sup>                       | 0           | —              | Yes     | Quadrature Encoder Compare Output 1.                                                                                                        |

| INDX2 <sup>(1)</sup>                         | I           | ST             | Yes     | Quadrature Encoder Index2 Pulse input.                                                                                                      |

| HOME2 <sup>(1)</sup>                         | 1           | ST             | Yes     | Quadrature Encoder Home2 Pulse input.                                                                                                       |

| QEA2 <sup>(1)</sup>                          | I           | ST             | Yes     | Quadrature Encoder Phase A input in QEI2 mode. Auxiliary timer                                                                              |

| QEB2 <sup>(1)</sup>                          | I           | ST             | Yes     | external clock input in Timer mode.<br>Quadrature Encoder Phase B input in QEI2 mode. Auxiliary timer<br>external gate input in Timer mode. |

| CNTCMP2 <sup>(1)</sup>                       | 0           | —              | Yes     | Quadrature Encoder Compare Output 2.                                                                                                        |

| COFS                                         | I/O         | ST             | Yes     | Data Converter Interface frame synchronization pin.                                                                                         |

| CSCK                                         | I/O         | ST             | Yes     | Data Converter Interface serial clock input/output pin.                                                                                     |

| CSDI                                         | I           | ST             | Yes     | Data Converter Interface serial data input pin.                                                                                             |

| CSDO                                         | 0           | —              | Yes     | Data Converter Interface serial data output pin.                                                                                            |

| C1RX                                         | Ι           | ST             | Yes     | CAN1 bus receive pin.                                                                                                                       |

| C1TX                                         | 0           | —              | Yes     | CAN1 bus transmit pin                                                                                                                       |

| C2RX                                         | I           | ST             | Yes     | CAN2 bus receive pin.                                                                                                                       |

| C2TX                                         | 0           | —              | Yes     | CAN2 bus transmit pin                                                                                                                       |

| RTCC                                         | 0           | —              | No      | Real-Time Clock and Calendar alarm output.                                                                                                  |

| CVREF                                        | 0           | Analog         | No      | Comparator Voltage Reference output.                                                                                                        |

| C1IN1+, C1IN2-,<br>C1IN1-, C1IN3-            | Ι           | Analog         | No      | Comparator 1 inputs.                                                                                                                        |

| C1OUT                                        | 0           | —              | Yes     | Comparator 1 output.                                                                                                                        |

| C2IN1+, C2IN2-,<br>C2IN1-, C2IN3-            | Ι           | Analog         | No      | Comparator 2 inputs.                                                                                                                        |

| C2OUT                                        | 0           | —              | Yes     | Comparator 2 output.                                                                                                                        |

| C3IN1+, C3IN2-,<br>C2IN1-, C3IN3-            | I           | Analog         | No      | Comparator 3 inputs.                                                                                                                        |

| C3OUT                                        | 0           | —              | Yes     | Comparator 3 output.                                                                                                                        |

| C4IN1+, C4IN2-,<br>C4IN1-, C4IN3-            | I           | Analog         | No      | Comparator 4 inputs.                                                                                                                        |

| C4OUT                                        | 0           | —              | Yes     | Comparator 4 output.                                                                                                                        |

| C5IN1-, C5IN2-,<br>C5IN3-, C5IN4-,<br>C5IN1+ | I           | Analog         | No      | Comparator 5 inputs.                                                                                                                        |

| C5OUT                                        | 0           | —              | Yes     | Comparator 5 output.                                                                                                                        |

| Legend: CMOS = CM                            | IOS co      | mpatible       | input o | or output Analog = Analog input P = Power                                                                                                   |

## TABLE 1-1:PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

Note 1: This pin is not available on all devices. For more information, see the "Pin Diagrams" section for pin availability.

2: AVDD must be connected at all times.

I = Input

NOTES:

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

## 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

# dsPIC33EPXXXGM3XX/6XX/7XX

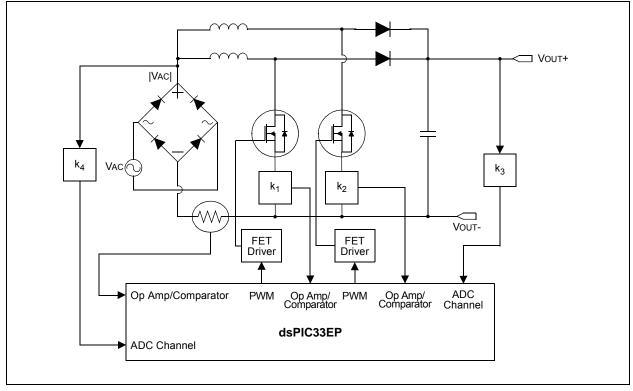

## FIGURE 2-7: INTERLEAVED PFC

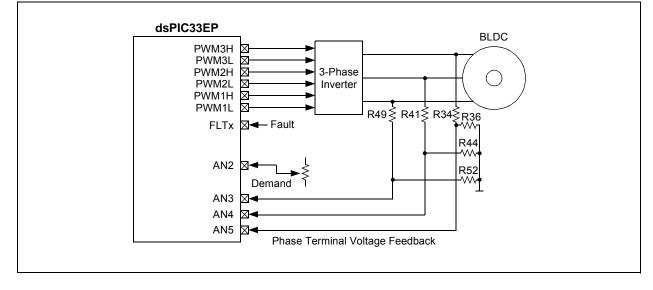

#### FIGURE 2-8: BEMF VOLTAGE MEASURED USING THE ADC MODULE

## 3.7 Arithmetic Logic Unit (ALU)

The dsPIC33EPXXXGM3XX/6XX/7XX family ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.7.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier, the ALU supports unsigned, signed, or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.7.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.8 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- Signed, unsigned or mixed-sign DSP multiply (US)

- Conventional or convergent rounding (RND)

- Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

| TABLE 3-2: | DSP INSTRUCTIONS |

|------------|------------------|

|            | SUMMARY          |

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

|-------------|-------------------------|-------------------|

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

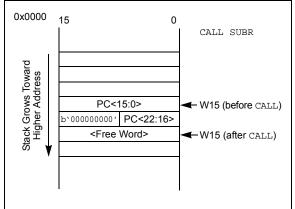

### 4.3.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack     |

|-------|-----------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the |

|       | hardware.                               |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGM3XX/6XX/7XX devices and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack, working from lower toward higher addresses. Figure 4-13 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-13. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain the Software Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore, restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a 'C' development environment

#### FIGURE 4-13: C.

#### CALL STACK FRAME

## 4.4 Instruction Addressing Modes

The addressing modes shown in Table 4-66 form the basis of the addressing modes optimized to support the specific features of the individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

#### 4.4.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.4.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- · Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

Note: Not all instructions support all of the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

#### REGISTER 11-32: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| U-0          | U-0                                                                                                                                               | R/W-0            | R/W-0                                   | R/W-0        | R/W-0            | R/W-0    | R/W-0 |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|--------------|------------------|----------|-------|--|--|--|

| _            | —                                                                                                                                                 |                  | RP39R<5:0>                              |              |                  |          |       |  |  |  |

| bit 15       |                                                                                                                                                   |                  |                                         |              |                  |          | bit 8 |  |  |  |

|              |                                                                                                                                                   | DAMA             |                                         | DAMO         | DAVA             | DAMA     | DAMO  |  |  |  |

| U-0          | U-0                                                                                                                                               | R/W-0            | R/W-0                                   | R/W-0        | R/W-0            | R/W-0    | R/W-0 |  |  |  |

| —            | —                                                                                                                                                 | — RP38R<5:0>     |                                         |              |                  |          |       |  |  |  |

| bit 7        |                                                                                                                                                   |                  |                                         |              |                  |          | bit 0 |  |  |  |

|              |                                                                                                                                                   |                  |                                         |              |                  |          |       |  |  |  |

| Legend:      |                                                                                                                                                   |                  |                                         |              |                  |          |       |  |  |  |

| R = Readab   | le bit                                                                                                                                            | W = Writable     | bit                                     | U = Unimplen | nented bit, read | d as '0' |       |  |  |  |

| -n = Value a | t POR                                                                                                                                             | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |              |                  |          | iown  |  |  |  |

| bit 15-14    | Unimplemen                                                                                                                                        | ted: Read as '   | 0'                                      |              |                  |          |       |  |  |  |

| bit 13-8     | bit 13-8 <b>RP39R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP39 Output Pin bits (see Table 11-3 for peripheral function numbers) |                  |                                         |              |                  |          |       |  |  |  |

| bit 7-6      | Unimplemented: Read as '0'                                                                                                                        |                  |                                         |              |                  |          |       |  |  |  |

| bit 5-0      | <b>RP38R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP38 Output Pin bits                                                           |                  |                                         |              |                  |          |       |  |  |  |

|              |                                                                                                                                                   |                  |                                         | -            |                  |          |       |  |  |  |

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-33: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0                                | U-0                                                                                     | R/W-0           | R/W-0 | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |  |

|------------------------------------|-----------------------------------------------------------------------------------------|-----------------|-------|-----------------------------------------|-----------------|----------|-------|--|--|

| _                                  | _                                                                                       |                 |       | RP41                                    | R<5:0>          |          |       |  |  |

| bit 15                             |                                                                                         |                 |       |                                         |                 |          | bit 8 |  |  |

|                                    |                                                                                         |                 |       |                                         |                 |          |       |  |  |

| U-0                                | U-0                                                                                     | R/W-0           | R/W-0 | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |  |

| _                                  | _                                                                                       |                 |       | RP40                                    | R<5:0>          |          |       |  |  |

| bit 7                              | ÷                                                                                       |                 |       |                                         |                 |          | bit 0 |  |  |

|                                    |                                                                                         |                 |       |                                         |                 |          |       |  |  |

| Legend:                            |                                                                                         |                 |       |                                         |                 |          |       |  |  |

| R = Readable                       | e bit                                                                                   | W = Writable    | bit   | U = Unimplem                            | nented bit, rea | d as '0' |       |  |  |

| -n = Value at POR '1' = Bit is set |                                                                                         |                 |       | '0' = Bit is cleared x = Bit is unknown |                 |          | nown  |  |  |

|                                    |                                                                                         |                 |       |                                         |                 |          |       |  |  |

| bit 15-14                          | Unimpleme                                                                               | nted: Read as ' | 0'    |                                         |                 |          |       |  |  |

| bit 13-8                           | <b>RP41R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP41 Output Pin bits |                 |       |                                         |                 |          |       |  |  |

(see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-3 for peripheral function numbers)

# 12.1 Timer1 Control Register

# REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0                                                     | U-0                                                            | R/W-0                              | U-0            | U-0              | U-0                       | U-0                | U-0         |  |  |  |

|-----------------------------------------------------------|----------------------------------------------------------------|------------------------------------|----------------|------------------|---------------------------|--------------------|-------------|--|--|--|

| TON <sup>(1)</sup>                                        | —                                                              | TSIDL                              | _              | —                | —                         | —                  | —           |  |  |  |

| bit 15                                                    |                                                                |                                    |                |                  |                           |                    | bit 8       |  |  |  |

|                                                           |                                                                |                                    |                |                  |                           |                    |             |  |  |  |

| U-0                                                       | R/W-0                                                          | R/W-0                              | R/W-0          | U-0              | R/W-0                     | R/W-0              | U-0         |  |  |  |

| _                                                         | TGATE                                                          | TCKPS1                             | TCKPS1         |                  | TSYNC <sup>(1)</sup>      | TCS <sup>(1)</sup> | —           |  |  |  |

| bit 7                                                     |                                                                |                                    |                |                  |                           |                    | bit 0       |  |  |  |

| r                                                         |                                                                |                                    |                |                  |                           |                    |             |  |  |  |

| Legend:                                                   |                                                                |                                    |                |                  |                           |                    |             |  |  |  |

| R = Readable                                              |                                                                | W = Writable                       |                | -                | mented bit, read          |                    |             |  |  |  |

| -n = Value at F                                           | POR                                                            | '1' = Bit is set                   |                | '0' = Bit is cle | ared                      | x = Bit is unkr    | IOWN        |  |  |  |

|                                                           | TON: Timer1                                                    | o                                  |                |                  |                           |                    |             |  |  |  |

| bit 15                                                    | 1 = Starts 16-                                                 |                                    |                |                  |                           |                    |             |  |  |  |

|                                                           | 1 = Starts 16-<br>0 = Stops 16-                                |                                    |                |                  |                           |                    |             |  |  |  |

| bit 14                                                    | •                                                              | ted: Read as '                     | )'             |                  |                           |                    |             |  |  |  |

| bit 13                                                    | -                                                              | 1 Stop in Idle N                   |                |                  |                           |                    |             |  |  |  |

|                                                           | 1 = Discontine                                                 | ues module op                      | eration when   | device enters l  | dle mode                  |                    |             |  |  |  |

|                                                           |                                                                | s module opera                     |                | ode              |                           |                    |             |  |  |  |

| bit 12-7                                                  | -                                                              | ted: Read as '                     |                |                  |                           |                    |             |  |  |  |

| bit 6                                                     |                                                                | er1 Gated Time                     | Accumulation   | Enable bit       |                           |                    |             |  |  |  |

|                                                           | When TCS =<br>This bit is igno                                 |                                    |                |                  |                           |                    |             |  |  |  |

|                                                           | When TCS =                                                     |                                    |                |                  |                           |                    |             |  |  |  |

|                                                           |                                                                | e accumulatior                     | n is enabled   |                  |                           |                    |             |  |  |  |

|                                                           | 0 = Gated tim                                                  | e accumulatior                     | n is disabled  |                  |                           |                    |             |  |  |  |

| bit 5-4                                                   |                                                                | : Timer1 Input                     | Clock Prescal  | e Select bits    |                           |                    |             |  |  |  |

|                                                           | 11 = 1:256<br>10 = 1:64                                        |                                    |                |                  |                           |                    |             |  |  |  |

|                                                           | 01 = 1:8                                                       |                                    |                |                  |                           |                    |             |  |  |  |

|                                                           | 00 = 1:1                                                       |                                    |                |                  |                           |                    |             |  |  |  |

| bit 3                                                     | Unimplemen                                                     | ted: Read as '                     | )'             |                  |                           |                    |             |  |  |  |

| bit 2                                                     |                                                                | er1 External Clo                   | ock Input Synd | chronization Se  | elect bit <sup>(1)</sup>  |                    |             |  |  |  |

|                                                           | When TCS = $\frac{1}{1}$                                       |                                    | a al ciana ut  |                  |                           |                    |             |  |  |  |

|                                                           |                                                                | izes external cl<br>synchronize ex |                | nout             |                           |                    |             |  |  |  |

|                                                           | 0 = Does not synchronize external clock input<br>When TCS = 0: |                                    |                |                  |                           |                    |             |  |  |  |

|                                                           | This bit is ignored.                                           |                                    |                |                  |                           |                    |             |  |  |  |

| bit 1                                                     | TCS: Timer1 Clock Source Select bit <sup>(1)</sup>             |                                    |                |                  |                           |                    |             |  |  |  |

| 1 = External clock is from pin, T1CK (on the rising edge) |                                                                |                                    |                |                  |                           |                    |             |  |  |  |

| hit 0                                                     | 0 = Internal clock (FP)<br>Unimplemented: Read as '0'          |                                    |                |                  |                           |                    |             |  |  |  |

| bit 0                                                     | ommplemen                                                      |                                    | J              |                  |                           |                    |             |  |  |  |

|                                                           | en Timer1 is en<br>mpts by user s                              |                                    |                |                  | ode (TCS = 1, T<br>nored. | SYNC = 1, TO       | N = 1), any |  |  |  |

# 13.0 TIMER2/3, TIMER4/5, TIMER6/7 AND TIMER8/9

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Timers" (DS70362), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3, Timer4/5, Timer6/7 and Timer8/9 modules are 32-bit timers, which can also be configured as eight independent 16-bit timers with selectable operating modes.

As a 32-bit timer, Timer2/3, Timer4/5, Timer6/7 and Timer8/9 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with All 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

- They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare modules

- ADC1 Event Trigger (Timer2/3 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON, T5CON, T6CON, T7CON, T8CON and T9CON registers. T2CON, T4CON, T6CON and T8CON are shown in generic form in Register 13-1. T3CON, T5CON, T7CON and T9CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2, Timer4, Timer6 and Timer8 are the least significant word (Isw); Timer3, Timer5, Timer7 and Timer9 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON, T5CON, T7CON and T9CON register control bits are ignored. Only T2CON, T4CON, T6CON and T8CON register control bits are used for setup and control. Timer2, Timer4, Timer6 and Timer8 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3, Timer5, Timer7 and Timer9 interrupt flags.

A block diagram for an example of a 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

Note: Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

# REGISTER 16-11: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7-6 | 6  | <b>DTC&lt;1:0&gt;:</b> Dead-Time Control bits<br>11 = Dead-Time Compensation mode                                                                                                                                                                                                                                                  |

|---------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |    | <ul> <li>10 = Dead-time function is disabled</li> <li>01 = Negative dead time is actively applied for Complementary Output mode</li> <li>00 = Positive dead time is actively applied for all Output modes</li> </ul>                                                                                                               |

| bit 5   |    | <b>DTCP:</b> Dead-Time Compensation Polarity bit <sup>(3)</sup>                                                                                                                                                                                                                                                                    |

|         |    | <u>When Set to '⊥':</u><br>If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.<br>If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                                                                                                                                                |

|         |    | <u>When Set to '<math>o</math>':</u><br>If DTCMPx = 0, PWMHx is shortened and PWMLx is lengthened.<br>If DTCMPx = 1, PWMLx is shortened and PWMHx is lengthened.                                                                                                                                                                   |

| bit 4   |    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                         |

| bit 3   |    | MTBS: Master Time Base Select bit                                                                                                                                                                                                                                                                                                  |

|         |    | <ul> <li>1 = PWMx generator uses the secondary master time base for synchronization and as the clock source for the PWMx generation logic (if secondary time base is available)</li> <li>0 = PWMx generator uses the primary master time base for synchronization and as the clock source for the PWMx generation logic</li> </ul> |

| bit 2   |    | <b>CAM:</b> Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                                                                                                                                                                                                        |

|         |    | 1 = Center-Aligned mode is enabled                                                                                                                                                                                                                                                                                                 |

| bit 1   |    | 0 = Edge-Aligned mode is enabled<br><b>XPRES:</b> External PWMx Reset Control bit <sup>(5)</sup>                                                                                                                                                                                                                                   |

| DILI    |    | <ul> <li>1 = Current-limit source resets the time base for this PWMx generator if it is in Independent Time Base<br/>mode</li> </ul>                                                                                                                                                                                               |

| bit 0   |    | <ul> <li>0 = External pins do not affect the PWMx time base</li> <li>IUE: Immediate Update Enable bit<sup>(2)</sup></li> </ul>                                                                                                                                                                                                     |

| DILU    |    | <ul> <li>1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate</li> <li>0 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the PWMx period boundary</li> </ul>                                                                                                          |

| Note    | 1: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.                                                                                                                                                                                                                       |

|         | 2: | These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                                                                                                                                                                                                                             |

|         | 3: | DTC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored.                                                                                                                                                                                                                                                                |

|         | 4: | The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.                                                                                                                                                                                                           |

|         |    |                                                                                                                                                                                                                                                                                                                                    |

**5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

## **REGISTER 17-6: POSxHLD: POSITION COUNTER x HOLD REGISTER**

| R/W-0                                                                   | R/W-0 | R/W-0          | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------------------------------------------------------------------|-------|----------------|-------|------------------------------------|-------|-------|-------|--|--|

|                                                                         |       |                | POSH  | LD<15:8>                           |       |       |       |  |  |

| bit 15 bit 8                                                            |       |                |       |                                    |       |       |       |  |  |

|                                                                         |       |                |       |                                    |       |       |       |  |  |

| R/W-0                                                                   | R/W-0 | R/W-0          | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                                                         |       |                | POSH  | ILD<7:0>                           |       |       |       |  |  |

| bit 7                                                                   |       |                |       |                                    |       |       | bit 0 |  |  |

|                                                                         |       |                |       |                                    |       |       |       |  |  |

| Legend:                                                                 |       |                |       |                                    |       |       |       |  |  |

| R = Readable I                                                          | bit   | W = Writable I | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkn |       |                | nown  |                                    |       |       |       |  |  |

bit 15-0 **POSHLD<15:0>:** Holding Register for Reading and Writing POSxCNT bits

### REGISTER 17-7: VELxCNT: VELOCITY COUNTER x REGISTER

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0            | R/W-0 | R/W-0           | R/W-0 |  |  |  |

|----------------------------------------------------------------------|-------|-------|-------|------------------|-------|-----------------|-------|--|--|--|

| VELCNT<15:8>                                                         |       |       |       |                  |       |                 |       |  |  |  |

| bit 15 bit 8                                                         |       |       |       |                  |       |                 |       |  |  |  |

|                                                                      |       |       |       |                  |       |                 |       |  |  |  |

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0            | R/W-0 | R/W-0           | R/W-0 |  |  |  |

|                                                                      |       |       | VELC  | NT<7:0>          |       |                 |       |  |  |  |

| bit 7                                                                |       |       |       |                  |       |                 | bit 0 |  |  |  |

|                                                                      |       |       |       |                  |       |                 |       |  |  |  |

| Legend:                                                              |       |       |       |                  |       |                 |       |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |       |                  |       |                 |       |  |  |  |

| -n = Value at POR '1' = Bit is s                                     |       |       |       | '0' = Bit is cle | ared  | x = Bit is unkr | nown  |  |  |  |

| L                                                                    |       |       |       |                  |       |                 |       |  |  |  |

bit 15-0 VELCNT<15:0>: Velocity Counter x bits

## REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6 | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                     |

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                       |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                   |

|       | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit;<br/>hardware clears at the end of the master Acknowledge sequence</li> <li>0 = Acknowledge sequence is not in progress</li> </ul>             |

| bit 3 | RCEN: Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                          |

|       | 1 = Enables Receive mode for I <sup>2</sup> C; hardware clears at the end of the eighth bit of a master receive data byte                                                                                                                     |

|       | 0 = Receive sequence is not in progress                                                                                                                                                                                                       |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                             |

|       | 1 = Initiates Stop condition on SDAx and SCLx pins; hardware clears at the end of a master Stop sequence                                                                                                                                      |

|       | 0 = Stop condition is not in progress                                                                                                                                                                                                         |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|       | 1 = Initiates Repeated Start condition on SDAx and SCLx pins; hardware clears at the end of a master<br>Repeated Start sequence                                                                                                               |

|       | 0 = Repeated Start condition is not in progress                                                                                                                                                                                               |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                   |

|       | 1 = Initiates Start condition on SDAx and SCLx pins; hardware clears at the end of a master Start sequence                                                                                                                                    |

|       | 0 = Start condition is not in progress                                                                                                                                                                                                        |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

|  | REGISTER 24-2: | DCICON2: DCI CONTROL REGISTER 2 |

|--|----------------|---------------------------------|

|--|----------------|---------------------------------|

| r-0             | r-0                                                                                                                                         | r-0                                                       | r-0          | R/W-0            | R/W-0           | r-0            | R/W-0          |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------|------------------|-----------------|----------------|----------------|--|--|--|

| r               | r                                                                                                                                           | r                                                         | r            | BLEN1            | BLEN0           | r              | COFSG3         |  |  |  |

| bit 15          | •                                                                                                                                           |                                                           |              | •                |                 | •              | bit 8          |  |  |  |

| <b>D</b> 444 0  | <b>DMU</b> O                                                                                                                                | DANO                                                      |              | <b>D44 0</b>     | DAALO           | DAMA           | <b>D</b> 444.0 |  |  |  |

| R/W-0           | R/W-0                                                                                                                                       | R/W-0                                                     | r-0          | R/W-0            | R/W-0           | R/W-0          | R/W-0          |  |  |  |

| COFSG2<br>bit 7 | COFSG1                                                                                                                                      | COFSG0                                                    | r            | WS3              | WS2             | WS1            | WS0<br>bit (   |  |  |  |

|                 |                                                                                                                                             |                                                           |              |                  |                 |                |                |  |  |  |

| Legend:         |                                                                                                                                             | r = Reserved b                                            | it           |                  |                 |                |                |  |  |  |

| R = Readab      | ole bit                                                                                                                                     | W = Writable b                                            | it           | U = Unimpler     | mented bit, rea | ad as '0'      |                |  |  |  |

| -n = Value a    | It POR                                                                                                                                      | '1' = Bit is set                                          |              | '0' = Bit is cle | ared            | x = Bit is unk | nown           |  |  |  |

| bit 15-12       | Reserved: R                                                                                                                                 | load as '0'                                               |              |                  |                 |                |                |  |  |  |

| bit 11-10       |                                                                                                                                             |                                                           | ontrol hito  |                  |                 |                |                |  |  |  |

|                 | BLEN<1:0>: Buffer Length Control bits                                                                                                       |                                                           |              |                  |                 |                |                |  |  |  |

|                 |                                                                                                                                             | 11 = Four data words will be buffered between interrupts  |              |                  |                 |                |                |  |  |  |

|                 |                                                                                                                                             | 10 = Three data words will be buffered between interrupts |              |                  |                 |                |                |  |  |  |

|                 | <ul> <li>01 = Two data words will be buffered between interrupts</li> <li>00 = One data word will be buffered between interrupts</li> </ul> |                                                           |              |                  |                 |                |                |  |  |  |

| bit 9           | Reserved: Read as '0'                                                                                                                       |                                                           |              |                  |                 |                |                |  |  |  |

| bit 8-5         | COFSG<3:0                                                                                                                                   | >: Frame Sync G                                           | Senerator Co | ontrol bits      |                 |                |                |  |  |  |

|                 | 1111 = Data frame has 16 words                                                                                                              |                                                           |              |                  |                 |                |                |  |  |  |

|                 | •                                                                                                                                           |                                                           |              |                  |                 |                |                |  |  |  |

|                 | •                                                                                                                                           |                                                           |              |                  |                 |                |                |  |  |  |

|                 | •                                                                                                                                           |                                                           |              |                  |                 |                |                |  |  |  |

|                 | 0010 = Data frame has 3 words<br>0001 = Data frame has 2 words                                                                              |                                                           |              |                  |                 |                |                |  |  |  |

|                 | 0001 = Data frame has 2 words<br>0000 = Data frame has 1 word                                                                               |                                                           |              |                  |                 |                |                |  |  |  |

| bit 4           | Reserved: R                                                                                                                                 |                                                           | -            |                  |                 |                |                |  |  |  |

| bit 3-0         | WS<3:0>: DCI Data Word Size bits                                                                                                            |                                                           |              |                  |                 |                |                |  |  |  |

|                 | 1111 = Data word size is 16 bits                                                                                                            |                                                           |              |                  |                 |                |                |  |  |  |

|                 | IIII – Dala                                                                                                                                 | word size is 16 l                                         | 5115         |                  |                 |                |                |  |  |  |

|                 | •<br>•                                                                                                                                      | word size is 16 l                                         | JIIS         |                  |                 |                |                |  |  |  |