Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

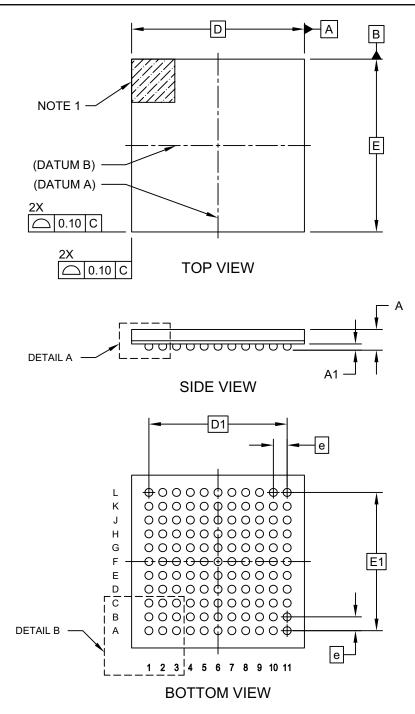

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gm604-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

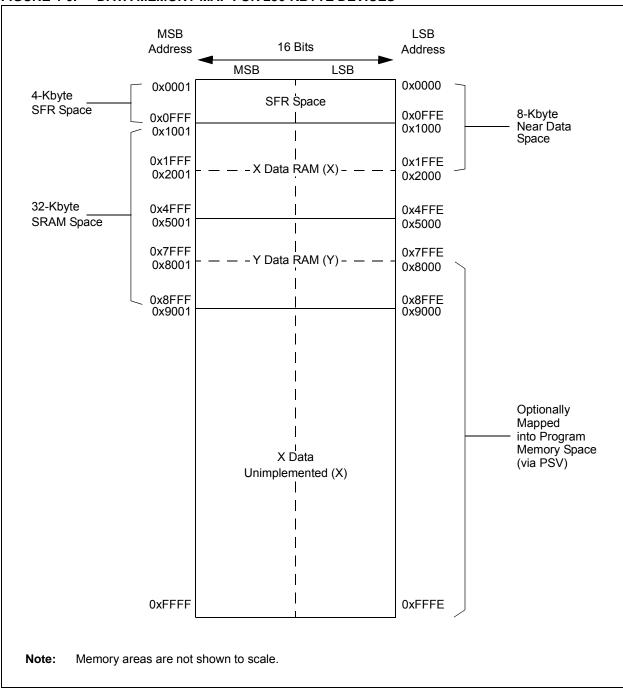

FIGURE 4-6: DATA MEMORY MAP FOR 256-KBYTE DEVICES

## 4.3 Special Function Register Maps

## TABLE 4-1: CPU CORE REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                       | Bit 14 | Bit 13 | Bit 12      | Bit 11     | Bit 10 | Bit 9      | Bit 8       | Bit 7       | Bit 6  | Bit 5      | Bit 4      | Bit 3        | Bit 2       | Bit 1    | Bit 0 | All<br>Resets |

|-------------|-------|------------------------------|--------|--------|-------------|------------|--------|------------|-------------|-------------|--------|------------|------------|--------------|-------------|----------|-------|---------------|

| W0          | 0000  |                              |        |        |             |            |        | 1          | W0 (WR      | EG)         |        |            |            |              |             | <b>I</b> |       | xxxx          |

| W1          | 0002  |                              |        |        |             |            |        |            |             |             |        | xxxx       |            |              |             |          |       |               |

| W2          | 0004  |                              |        |        |             |            |        |            | W2          |             |        |            |            |              |             |          |       | xxxx          |

| W3          | 0006  |                              |        |        |             |            |        |            | W3          |             |        |            |            |              |             |          |       | xxxx          |

| W4          | 0008  |                              |        |        |             |            |        |            | W4          |             |        |            |            |              |             |          |       | xxxx          |

| W5          | 000A  |                              |        |        |             |            |        |            | W5          |             |        |            |            |              |             |          |       | xxxx          |

| W6          | 000C  |                              |        |        |             |            |        |            | W6          |             |        |            |            |              |             |          |       | xxxx          |

| W7          | 000E  |                              |        |        |             |            |        |            | W7          |             |        |            |            |              |             |          |       | xxxx          |

| W8          | 0010  |                              |        |        |             |            |        |            | W8          |             |        |            |            |              |             |          |       | xxxx          |

| W9          | 0012  |                              |        |        |             |            |        |            | W9          |             |        |            |            |              |             |          |       | xxxx          |

| W10         | 0014  |                              |        |        |             |            |        |            | W10         |             |        |            |            |              |             |          |       | xxxx          |

| W11         | 0016  |                              |        |        |             |            |        |            | W11         |             |        |            |            |              |             |          |       | xxxx          |

| W12         | 0018  |                              |        |        |             |            |        |            | W12         |             |        |            |            |              |             |          |       | xxxx          |

| W13         | 001A  |                              |        |        |             |            |        |            | W13         |             |        |            |            |              |             |          |       | xxxx          |

| W14         | 001C  |                              |        |        |             |            |        |            | W14         |             |        |            |            |              |             |          |       | xxxx          |

| W15         | 001E  |                              |        |        |             |            |        |            | W15         |             |        |            |            |              |             |          |       | xxxx          |

| SPLIM       | 0020  |                              |        |        |             |            |        |            | SPLI        | N           |        |            |            |              |             |          |       | 0000          |

| ACCAL       | 0022  |                              |        |        |             |            |        |            | ACCA        | L           |        |            |            |              |             |          |       | 0000          |

| ACCAH       | 0024  |                              |        |        |             |            |        |            | ACCA        | .H          |        |            |            |              |             |          |       | 0000          |

| ACCAU       | 0026  |                              |        | Się    | gn Extensio | n of ACCA< | 39>    |            |             |             |        |            | ACO        | CAU          |             |          |       | 0000          |

| ACCBL       | 0028  |                              |        |        |             |            |        |            | ACCB        | L           |        |            |            |              |             |          |       | 0000          |

| ACCBH       | 002A  |                              |        |        |             |            |        |            | ACCB        | Н           |        |            |            |              |             |          |       | 0000          |

| ACCBU       | 002C  |                              |        | Się    | gn Extensio | n of ACCB< | 39>    |            |             |             |        |            | ACO        | CBU          |             |          |       | 0000          |

| PCL         | 002E  |                              |        | -      |             |            | Pr     | ogram Cour | nter Low Wo | rd Register |        |            |            |              |             |          | —     | 0000          |

| PCH         | 0030  | _                            | —      | —      | _           | _          | _      | —          | —           | —           |        | Pr         | ogram Cou  | unter High V | Vord Regist | ter      |       | 0000          |

| DSRPAG      | 0032  | _                            | —      | —      | —           | _          | —      |            |             |             | Data S | pace Read  | l Page Reg | gister       |             |          |       | 0001          |

| DSWPAG      | 0034  | _                            | —      | —      | —           | —          | —      | —          |             |             | 0      | Data Space | Write Pag  | e Register   |             |          |       | 0001          |

| RCOUNT      | 0036  | REPEAT Loop Count Register 0 |        |        |             |            |        |            | 0000        |             |        |            |            |              |             |          |       |               |

| DCOUNT      | 0038  |                              |        |        |             |            |        |            | DCOUNT<     | :15:0>      |        |            |            |              |             |          |       | 0000          |

| DOSTARTL    | 003A  |                              |        |        |             |            |        | DOS        | TARTL<15:1  | >           |        |            |            |              |             |          | —     | 0000          |

| DOSTARTH    | 003C  | -                            |        | —      | —           | —          | -      | _          | —           | _           | —      |            |            | DOSTAF       | RTH<5:0>    |          |       | 0000          |

| DOENDL      | 003E  |                              |        |        |             |            |        | DO         | ENDL<15:1>  | >           |        |            |            |              |             |          | _     | 0000          |

| DOENDH      | 0040  | -                            |        | —      | _           | _          | -      | —          | —           | _           | —      |            |            | DOEN         | DH<5:0>     |          |       | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000689D-page 46

| <b>TABLE 4-17:</b> | I2C1 AND I2C2 REGISTER MAP |

|--------------------|----------------------------|

|--------------------|----------------------------|

| SFR<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                    | Bit 8      | Bit 7       | Bit 6   | Bit 5       | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|---------|--------|---------|--------|--------|--------|--------------------------|------------|-------------|---------|-------------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV     | 0200  | —       | _      | —       | -      | —      | _      | —                        | _          |             |         |             | I2C1 Receiv  | ve Register  |       |       |       | 0000          |

| I2C1TRN     | 0202  | _       | _      | _       | _      | —      | _      | —                        | _          |             |         |             | I2C1 Transr  | nit Register |       |       |       | OOFF          |

| I2C1BRG     | 0204  |         |        |         |        |        |        | В                        | aud Rate C | Generator R | egister |             |              |              |       |       |       | 0000          |

| I2C1CON     | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                   | SMEN       | GCEN        | STREN   | ACKDT       | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT    | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                   | ADD10      | IWCOL       | I2COV   | D_A         | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD     | 020A  | _       | _      | _       | _      | _      | _      |                          |            |             |         | I2C1 Addre  | ess Register |              |       |       |       | 0000          |

| I2C1MSK     | 020C  | _       | _      | _       | _      | _      | _      |                          |            |             | 12      | 2C1 Address | Mask Regis   | ster         |       |       |       | 0000          |

| I2C2RCV     | 0210  | _       | _      | _       | _      | _      | _      | _                        | -          |             |         |             | I2C2 Receiv  | ve Register  |       |       |       | 0000          |

| I2C2TRN     | 0212  | _       | _      | _       | _      | _      | _      | _                        | -          |             |         |             | I2C2 Transr  | nit Register |       |       |       | OOFF          |

| I2C2BRG     | 0214  |         |        |         |        |        |        | В                        | aud Rate C | Generator R | egister |             |              |              |       |       |       | 0000          |

| I2C2CON     | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                   | SMEN       | GCEN        | STREN   | ACKDT       | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT    | 0218  | ACKSTAT | TRSTAT | _       | _      | —      | BCL    | GCSTAT                   | ADD10      | IWCOL       | I2COV   | D_A         | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD     | 021A  | _       | _      | _       | _      | —      | _      | I2C2 Address Register 00 |            |             |         |             |              | 0000         |       |       |       |               |

| I2C2MSK     | 021C  |         | _      | —       | —      | —      | _      |                          |            |             | 12      | 2C2 Address | Mask Regis   | ster         |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-18: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10                           | Bit 9 | Bit 8     | Bit 7         | Bit 6    | Bit 5 | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|----------|--------|----------|--------|--------|----------------------------------|-------|-----------|---------------|----------|-------|-------------|--------|--------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _                                | UEN1  | UEN0      | WAKE          | LPBACK   | ABAUD | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1 | UTXINV | UTXISEL0 |        | UTXBRK | UTXEN                            | UTXBF | TRMT      | URXISEL1      | URXISEL0 | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _        |        | —        |        | —      | —                                | —     |           |               |          | UART1 | Fransmit Re | gister |        |        |       | xxxx          |

| U1RXREG     | 0226  | _        | _      | _        | _      | _      | _                                | _     |           |               |          | UART1 | Receive Re  | gister |        |        |       | 0000          |

| U1BRG       | 0228  |          |        |          |        |        |                                  | Ba    | ud Rate C | Generator Pre | scaler   |       |             |        |        |        |       | 0000          |

| U2MODE      | 0230  | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _                                | UEN1  | UEN0      | WAKE          | LPBACK   | ABAUD | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN                            | UTXBF | TRMT      | URXISEL1      | URXISEL0 | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _        | _      | _        | _      | _      | _                                | _     |           |               |          | UART2 | Fransmit Re | gister |        |        |       | xxxx          |

| U2RXREG     | 0236  | _        | —      | _        | _      | —      | _                                | —     |           |               |          | UART2 | Receive Re  | gister |        |        |       | 0000          |

| U2BRG       | 0238  |          |        |          |        |        | Baud Rate Generator Prescaler 00 |       |           |               |          |       | 0000        |        |        |        |       |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

| R/SO-0 <sup>(1</sup> | ) R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup> | R/W-0                        | U-0                     | U-0                     | R/W-0                   | R/W-0                  |

|----------------------|-------------------------|----------------------|------------------------------|-------------------------|-------------------------|-------------------------|------------------------|

| WR                   | WREN                    | WRERR                | NVMSIDL <sup>(2)</sup>       |                         |                         | RPDF                    | URERR <sup>(6)</sup>   |

| bit 15               |                         | •                    |                              |                         |                         |                         | bit                    |

|                      |                         |                      |                              | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>   |

| U-0                  | U-0                     | U-0                  | U-0                          |                         |                         |                         |                        |

|                      | —                       | —                    | —                            | NVMOP3 <sup>(3,4)</sup> | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4</sup> |

| bit 7                |                         |                      |                              |                         |                         |                         | bit                    |

| Legend:              |                         | SO = Settab          | le Only bit                  |                         |                         |                         |                        |

| R = Reada            | able bit                | W = Writable         | e bit                        | U = Unimplem            | ented bit, read         | as '0'                  |                        |

| -n = Value           | at POR                  | '1' = Bit is se      | et                           | '0' = Bit is clea       | ired                    | x = Bit is unkn         | own                    |

|                      |                         |                      |                              |                         |                         |                         |                        |

| oit 15               | WR: NVM Wr              | te Control bit       | (1)                          |                         |                         |                         |                        |

|                      | 1 = Initiates           | a Flash mem          | ory program o                | r erase operati         | on; the operati         | on is self-timed        | and the bit            |

|                      |                         | •                    |                              | on is complete          |                         |                         |                        |

|                      | -                       | -                    | -                            | ete and inactive        |                         |                         |                        |

| pit 14               | WREN: NVM               |                      |                              |                         |                         |                         |                        |

|                      |                         |                      | n/erase operati              |                         |                         |                         |                        |

|                      |                         |                      | erase operatio               |                         |                         |                         |                        |

| oit 13               |                         | •                    | ence Error Flag              |                         |                         |                         |                        |

|                      |                         |                      |                              | ce attempt, or te       | ermination has c        | occurred (bit is s      | et automatical         |

|                      | •                       | et attempt of th     | ,                            | pleted normally         |                         |                         |                        |

| bit 12               |                         |                      | e Control bit <sup>(2)</sup> | -                       |                         |                         |                        |

| JILIZ                |                         |                      |                              | ndby mode duri          | aa Idla mada            |                         |                        |

|                      |                         |                      | is active durin              |                         | ly lule mode            |                         |                        |

| bit 11-10            | Unimplemen              |                      |                              | ig falo filodo          |                         |                         |                        |

| oit 9                | -                       |                      |                              | Data Format Co          | ntrol bit               |                         |                        |

| 5                    |                         |                      |                              | pressed format          |                         |                         |                        |

|                      |                         |                      |                              | ompressed form          |                         |                         |                        |

| bit 8                |                         |                      |                              | g Data Underru          |                         | (6)                     |                        |

|                      |                         |                      |                              |                         |                         | een termination         | due to a dat           |

|                      | underrun                |                      |                              | 0 0 1                   |                         |                         |                        |

|                      | 0 = Indicates           | no data unde         | errun error is de            | etected                 |                         |                         |                        |

| bit 7-4              | Unimplemen              | ted: Read as         | '0'                          |                         |                         |                         |                        |

| Note 1:              | These bits can o        | nly be reset o       | n POR.                       |                         |                         |                         |                        |

| 2:                   | If this bit is set, the |                      |                              |                         | nd upon exiting         | g Idle mode, the        | re is a delay          |

|                      | (TVREG) before F        | -                    | -                            |                         |                         |                         |                        |

|                      | All other combina       |                      |                              | •                       |                         |                         |                        |

| 4:                   | Execution of the        | PWRSAV instru        | uction is ignore             | d while any of t        | he NVM operat           | tions are in prog       | ress.                  |

| -                    |                         |                      |                              |                         |                         |                         |                        |

- 5: Two adjacent words on a 4-word boundary are programmed during execution of this operation.

- 6: When URERR is set, the bus mastered row programming operation will terminate with the WRERR bit still set.

| R/W-0        | R/W-0                                     | U-0                                         | U-0            | R/W-0                 | U-0              | R/W-0            | R/W-0        |

|--------------|-------------------------------------------|---------------------------------------------|----------------|-----------------------|------------------|------------------|--------------|

| TRAPR        | IOPUWR                                    | _                                           |                | VREGSF                | _                | CM               | VREGS        |

| bit 15       |                                           |                                             |                |                       |                  |                  | bit 8        |

|              |                                           |                                             |                |                       |                  |                  |              |

| R/W-0        | R/W-0                                     | R/W-0                                       | R/W-0          | R/W-0                 | R/W-0            | R/W-1            | R/W-1        |

| EXTR         | SWR                                       | SWDTEN <sup>(2)</sup>                       | WDTO           | SLEEP                 | IDLE             | BOR              | POR          |

| bit 7        |                                           |                                             |                |                       |                  |                  | bit          |

| Legend:      |                                           |                                             |                |                       |                  |                  |              |

| R = Readal   | ole bit                                   | W = Writable b                              | oit            | U = Unimplem          | nented bit, read | l as '0'         |              |

| -n = Value a | at POR                                    | '1' = Bit is set                            |                | '0' = Bit is clea     | ared             | x = Bit is unk   | nown         |

| hit 1E       |                                           | Depart Flag hit                             |                |                       |                  |                  |              |

| bit 15       | -                                         | Reset Flag bit<br>onflict Reset has         | occurred       |                       |                  |                  |              |

|              |                                           | onflict Reset has                           |                | d                     |                  |                  |              |

| bit 14       | IOPUWR: Ille                              | gal Opcode or l                             | Jninitialized  | W Access Rese         | et Flag bit      |                  |              |

|              | 1 = An illega                             | al opcode detec                             | tion, an illeg | gal address mo        | de or Uninitial  | ized W registe   | er used as a |

|              |                                           | Pointer caused                              |                | Dogistor Dogot k      | a not a courra   | d                |              |

| bit 13-12    | -                                         | l opcode or Unir                            |                | Register Reset r      | las not occurre  | u                |              |

| bit 11       | •                                         | i <b>ted:</b> Read as '0<br>ash Voltage Reg |                | by During Sloop       | , bit            |                  |              |

|              |                                           | Itage regulator i                           |                |                       |                  |                  |              |

|              |                                           | Itage regulator                             |                |                       | ing Sleep        |                  |              |

| bit 10       | Unimplemen                                | ted: Read as '0                             | ,              | -                     |                  |                  |              |

| bit 9        | CM: Configur                              | ation Mismatch                              | Flag bit       |                       |                  |                  |              |

|              | •                                         | uration Mismatcl                            |                |                       |                  |                  |              |

|              | •                                         | uration Mismatcl                            |                |                       |                  |                  |              |

| bit 8        |                                           | age Regulator S                             |                |                       |                  |                  |              |

|              |                                           | egulator is activ                           |                |                       |                  |                  |              |

| bit 7        | -                                         | nal Reset (MCLF                             | -              | node during Sie       | eb.              |                  |              |

|              |                                           | Clear (pin) Res                             | ,              | red                   |                  |                  |              |

|              |                                           | Clear (pin) Res                             |                |                       |                  |                  |              |

| bit 6        | SWR: Softwa                               | IRE RESET (Instru                           | uction) Flag   | bit                   |                  |                  |              |

|              |                                           | instruction has l                           |                |                       |                  |                  |              |

|              |                                           | instruction has i                           |                |                       |                  |                  |              |

| bit 5        |                                           | oftware Enable/[                            | Disable of W   | DT bit <sup>(2)</sup> |                  |                  |              |

|              | 1 = WDT is e<br>0 = WDT is d              |                                             |                |                       |                  |                  |              |

| bit 4        |                                           | hdog Timer Tim                              | e-out Elag bi  | it                    |                  |                  |              |

| with i       |                                           | e-out has occurr                            | -              |                       |                  |                  |              |

|              |                                           | e-out has not oc                            |                |                       |                  |                  |              |

|              | All of the Reset sta<br>cause a device Re |                                             | set or cleare  | d in software. S      | etting one of th | ese bits in soft | ware does no |

| <b>2:</b>    | f the FWDTEN Co                           | onfiguration bit is                         | s '1' (unprog  | rammed), the W        | /DT is always e  | nabled, regard   | lless of the |

#### RCON: RESET CONTROL REGISTER<sup>(1)</sup> **REGISTER 6-1:**

e сy SWDTEN bit setting.

| U-0              | U-0 | U-0              | U-0 | U-0              | U-0              | U-0             | U-0    |

|------------------|-----|------------------|-----|------------------|------------------|-----------------|--------|

| —                | —   | —                |     | —                | _                | —               | —      |

| bit 15           |     |                  |     |                  |                  |                 | bit 8  |

|                  |     |                  |     |                  |                  |                 |        |

| U-0              | U-0 | U-0              | U-0 | R-0              | R-0              | R-0             | R-0    |

| —                |     | —                | _   | PWCOL3           | PWCOL2           | PWCOL1          | PWCOL0 |

| bit 7            |     |                  |     |                  |                  |                 | bit (  |

|                  |     |                  |     |                  |                  |                 |        |

| Legend:          |     |                  |     |                  |                  |                 |        |

| R = Readable b   | bit | W = Writable I   | bit | U = Unimplen     | nented bit, read | as '0'          |        |

| -n = Value at PO | OR  | '1' = Bit is set |     | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

## REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

| bit 15-4 | Unimplemented: Read as '0'                                                                   |

|----------|----------------------------------------------------------------------------------------------|

| bit 3    | PWCOL3: Channel 3 Peripheral Write Collision Flag bit                                        |

|          | <ul><li>1 = Write collision is detected</li><li>0 = No write collision is detected</li></ul> |

| bit 2    | PWCOL2: Channel 2 Peripheral Write Collision Flag bit                                        |

|          | 1 = Write collision is detected                                                              |

|          | 0 = No write collision is detected                                                           |

| bit 1    | <b>PWCOL1:</b> Channel 1 Peripheral Write Collision Flag bit                                 |

|          | 1 = Write collision is detected                                                              |

|          | 0 = No write collision is detected                                                           |

| bit 0    | PWCOL0: Channel 0 Peripheral Write Collision Flag bit                                        |

|          | 1 = Write collision is detected                                                              |

|          | 0 = No write collision is detected                                                           |

| R/W-0         | U-0                          | R/W-0                                | R/W-0           | R/W-0                         | R/W-0                 | R/W-0                 | R/W-0                 |

|---------------|------------------------------|--------------------------------------|-----------------|-------------------------------|-----------------------|-----------------------|-----------------------|

| ROON          |                              | ROSSLP                               | ROSEL           | RODIV3 <sup>(1)</sup>         | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |

| bit 15        |                              |                                      |                 |                               |                       |                       | bit 8                 |

|               |                              |                                      |                 |                               |                       |                       |                       |

| U-0           | U-0                          | U-0                                  | U-0             | U-0                           | U-0                   | U-0                   | U-0                   |

| bit 7         |                              | _                                    | _               |                               |                       |                       | bit (                 |

|               |                              |                                      |                 |                               |                       |                       |                       |

| Legend:       |                              |                                      |                 |                               |                       |                       |                       |

| R = Readable  |                              | W = Writable                         |                 |                               | nented bit, read      |                       |                       |

| -n = Value at | POR                          | '1' = Bit is set                     |                 | '0' = Bit is cle              | ared                  | x = Bit is unkr       | IOWN                  |

| bit 15        | ROON: Refer                  | ence Oscillato                       | r Output Enat   | ole bit                       |                       |                       |                       |

|               |                              |                                      |                 | on the REFCL                  | .K pin <sup>(2)</sup> |                       |                       |

|               | 0 = Reference                | e oscillator outp                    | out is disabled | t                             |                       |                       |                       |

| bit 14        | Unimplemen                   | ted: Read as '                       | 0'              |                               |                       |                       |                       |

| bit 13        | ROSSLP: Re                   | ference Oscilla                      | ator Run in Sle | eep bit                       |                       |                       |                       |

|               |                              | e oscillator out<br>e oscillator out |                 | to run in Sleep<br>d in Sleep |                       |                       |                       |

| bit 12        | ROSEL: Refe                  | erence Oscillato                     | or Source Sel   | ect bit                       |                       |                       |                       |

|               |                              | crystal is used<br>lock is used as   |                 |                               |                       |                       |                       |

| bit 11-8      | RODIV<3:0>:                  | Reference Os                         | cillator Divide | er bits <sup>(1)</sup>        |                       |                       |                       |

|               |                              | ence clock divi                      |                 |                               |                       |                       |                       |

|               |                              | ence clock divi                      | •               |                               |                       |                       |                       |

|               |                              | ence clock divi<br>ence clock divi   | •               |                               |                       |                       |                       |

|               |                              | ence clock divi                      |                 |                               |                       |                       |                       |

|               |                              | ence clock divi                      |                 |                               |                       |                       |                       |

|               |                              | ence clock divi                      |                 |                               |                       |                       |                       |

|               |                              | ence clock divi                      |                 |                               |                       |                       |                       |

|               |                              | ence clock divi<br>ence clock divi   | -               |                               |                       |                       |                       |

|               |                              | ence clock divi                      | ,               |                               |                       |                       |                       |

|               |                              | ence clock divi                      | •               |                               |                       |                       |                       |

|               | 0011 = Refer                 | ence clock divi                      | ded by 8        |                               |                       |                       |                       |

|               |                              | ence clock divi                      |                 |                               |                       |                       |                       |

|               | 0001 = Refer<br>0000 = Refer | ence clock divi                      | aed by 2        |                               |                       |                       |                       |

| bit 7-0       |                              |                                      | 0'              |                               |                       |                       |                       |

|               | ommplemen                    | ted: Read as '                       | U               |                               |                       |                       |                       |

## **REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER**

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

## 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control x register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the "**Pin Diagrams**" section for the available 5V tolerant pins and Table 33-10 for the maximum VIH specification for each pin.

## 11.2 Configuring Analog and Digital Port Pins

The ANSELx registers control the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1 in **Section 1.0 "Device Overview"**).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADCx module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

## 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP, as shown in Example 11-1.

## 11.3 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States (COS), even in Sleep mode when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the ICN functionality of each I/O port. The CNENx registers contain the ICN interrupt enable control bits for each of the input pins. Setting any of these bits enables an ICN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pulldown connected to it. The pull-ups and pull-downs act as a current source or sink source connected to the pin, and eliminate the need for external resistors when pushbutton or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on Input Change    |

|-------|--------------------------------------------|

|       | Notification pins should always be dis-    |

|       | abled when the port pin is configured as a |

|       | digital output.                            |

#### EXAMPLE 11-1: PORTB WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

## REGISTER 11-30: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0               | U-0       | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-------------------|-----------|------------------|-------|------------------|-----------------|-----------------|-------|

| _                 | _         |                  |       | RP35             | R<5:0>          |                 |       |

| bit 15            |           |                  |       |                  |                 |                 | bit 8 |

|                   |           |                  |       |                  |                 |                 |       |

| U-0               | U-0       | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| —                 | —         |                  |       | RP20             | R<5:0>          |                 |       |

| bit 7             |           |                  |       |                  |                 |                 | bit 0 |

|                   |           |                  |       |                  |                 |                 |       |

| Legend:           |           |                  |       |                  |                 |                 |       |

| R = Readable      | e bit     | W = Writable     | bit   | U = Unimplen     | nented bit, rea | d as '0'        |       |

| -n = Value at POR |           | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

|                   |           |                  |       |                  |                 |                 |       |

| bit 15-14         | Unimpleme | nted: Read as '  | 0'    |                  |                 |                 |       |

| bit 13-8          |           | >: Peripheral Ou | •     | •                | RP35 Output     | Pin bits        |       |

| 2.1.1.0.0 | (see Table 11-3 for peripheral function numbers)                                                                                         |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP20R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-31: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0          | U-0 | R/W-0            | R/W-0      | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|--------------|-----|------------------|------------|-------------------|----------------|-----------------|-------|

| _            | —   |                  |            | RP37F             | २<5:0>         |                 |       |

| bit 15       |     |                  |            |                   |                |                 | bit 8 |

| U-0          | U-0 | R/W-0            | R/W-0      | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|              | —   |                  | RP36R<5:0> |                   |                |                 |       |

| bit 7        |     |                  |            |                   |                |                 | bit 0 |

| Legend:      |     |                  |            |                   |                |                 |       |

| R = Readable | bit | W = Writable     | bit        | U = Unimplem      | ented bit, rea | ad as '0'       |       |

|              | OR  | '1' = Bit is set |            | '0' = Bit is clea | ired           | x = Bit is unkr | nown  |

bit 13-8 **RP37R<5:0>:** Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP36R<5:0>:** Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-3 for peripheral function numbers)

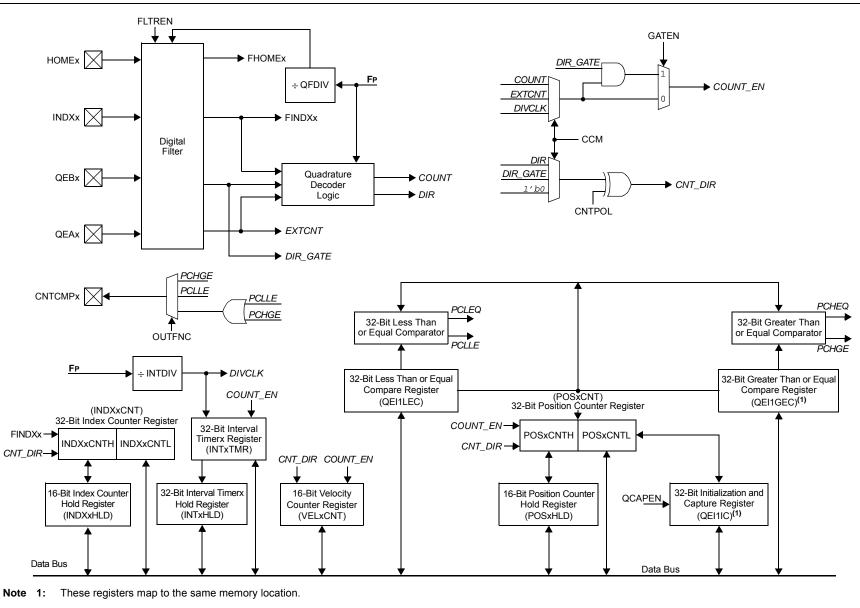

#### FIGURE 17-1: QEIX BLOCK DIAGRAM

JSPIC33EPXXXGM3XX/6XX/7XX

## REGISTER 21-8: CxEC: CANx TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0      |

|----------|----------|----------|----------|----------|----------|----------|----------|

| TERRCNT7 | TERRCNT6 | TERRCNT5 | TERRCNT4 | TERRCNT3 | TERRCNT2 | TERRCNT1 | TERRCNT0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R-0      |

|----------|----------|----------|----------|----------|----------|----------|----------|

| RERRCNT7 | RERRCNT6 | RERRCNT5 | RERRCNT4 | RERRCNT3 | RERRCNT2 | RERRCNT1 | RERRCNT0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 TERRCNT<7:0>: Transmit Error Count bits

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

## REGISTER 21-9: CxCFG1: CANx BAUD RATE CONFIGURATION REGISTER 1

| U-0             | U-0                | U-0                                                                                             | U-0        | U-0               | U-0              | U-0             | U-0   |  |  |

|-----------------|--------------------|-------------------------------------------------------------------------------------------------|------------|-------------------|------------------|-----------------|-------|--|--|

|                 |                    |                                                                                                 | <u> </u>   |                   |                  | <u> </u>        | 0-0   |  |  |

|                 |                    |                                                                                                 |            |                   |                  |                 |       |  |  |

| bit 15          |                    |                                                                                                 |            |                   |                  |                 | bit   |  |  |

|                 |                    |                                                                                                 |            |                   |                  |                 |       |  |  |

| R/W-0           | R/W-0              | R/W-0                                                                                           | R/W-0      | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |

| SJW1            | SJW0               | BRP5                                                                                            | BRP4       | BRP3              | BRP2             | BRP1            | BRP0  |  |  |

| bit 7           |                    |                                                                                                 |            |                   |                  |                 | bit   |  |  |

|                 |                    |                                                                                                 |            |                   |                  |                 |       |  |  |

| Legend:         |                    |                                                                                                 |            |                   |                  |                 |       |  |  |

| R = Readable    | e bit              | W = Writable                                                                                    | bit        | U = Unimplen      | nented bit, read | l as '0'        |       |  |  |

| -n = Value at I | POR                | '1' = Bit is set                                                                                |            | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |  |

|                 |                    |                                                                                                 |            |                   |                  |                 |       |  |  |

| bit 15-8        | Unimplemer         | ted: Read as '                                                                                  | 0'         |                   |                  |                 |       |  |  |

| bit 7-6         | SJW<1:0>: S        | Synchronization                                                                                 | Jump Width | bits              |                  |                 |       |  |  |

|                 | 11 = Length        | 1 = Length is 4 x TQ                                                                            |            |                   |                  |                 |       |  |  |

|                 | 10 = Length        | is 3 x Tq                                                                                       |            |                   |                  |                 |       |  |  |

|                 | 01 = Length        |                                                                                                 |            |                   |                  |                 |       |  |  |

|                 | 00 = Length        | is 1 x Tq                                                                                       |            |                   |                  |                 |       |  |  |

| bit 5-0         | BRP<5:0>: E        | Baud Rate Pres                                                                                  | caler bits |                   |                  |                 |       |  |  |

| 11 1111         |                    | <sup>-</sup> Q = 2 x 64 x 1/l                                                                   | FCAN       |                   |                  |                 |       |  |  |

|                 | •                  |                                                                                                 |            |                   |                  |                 |       |  |  |

|                 | •                  |                                                                                                 |            |                   |                  |                 |       |  |  |

|                 |                    |                                                                                                 |            |                   |                  |                 |       |  |  |

|                 | •                  |                                                                                                 |            |                   |                  |                 |       |  |  |

|                 |                    | $Q = 2 \times 3 \times 1/F_{0}$                                                                 |            |                   |                  |                 |       |  |  |

|                 | 00 0001 <b>= T</b> | <sup>-</sup> Q = 2 x 3 x 1/F(<br><sup>-</sup> Q = 2 x 2 x 1/F(<br><sup>-</sup> Q = 2 x 1 x 1/F( | CAN        |                   |                  |                 |       |  |  |

| R/W-0           | R/W-0                          | R/W-0                                                                                 | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |

|-----------------|--------------------------------|---------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|---------|--|--|--|

| PTGCLK2         | PTGCLK1                        | PTGCLK0                                                                               | PTGDIV4         | PTGDIV3          | PTGDIV2          | PTGDIV1         | PTGDIV0 |  |  |  |

| bit 15          | •                              |                                                                                       |                 |                  |                  |                 | bit 8   |  |  |  |

|                 |                                |                                                                                       |                 |                  |                  |                 |         |  |  |  |

| R/W-0           | R/W-0                          | R/W-0                                                                                 | R/W-0           | U-0              | R/W-0            | R/W-0           | R/W-0   |  |  |  |

| PTGPWD3         | PTGPWD2                        | PTGPWD1                                                                               | PTGPWD0         | —                | PTGWDT2          | PTGWDT1         | PTGWDT0 |  |  |  |

| bit 7           |                                |                                                                                       |                 |                  |                  |                 | bit 0   |  |  |  |

| Legend:         |                                |                                                                                       |                 |                  |                  |                 |         |  |  |  |

| R = Readable    | bit                            | W = Writable                                                                          | bit             | U = Unimpler     | mented bit, read | l as '0'        |         |  |  |  |

| -n = Value at F | POR                            | '1' = Bit is set                                                                      |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |

|                 |                                |                                                                                       |                 | <b>a</b>         |                  |                 |         |  |  |  |

| bit 15-13       |                                | >: Select PTG                                                                         | Module Clock    | Source bits      |                  |                 |         |  |  |  |

|                 | 111 = Reserv<br>110 = Reserv   |                                                                                       |                 |                  |                  |                 |         |  |  |  |

|                 |                                | odule clock so                                                                        | urce will be T3 | CLK              |                  |                 |         |  |  |  |

|                 |                                | odule clock so                                                                        |                 |                  |                  |                 |         |  |  |  |

|                 |                                | odule clock so                                                                        |                 |                  |                  |                 |         |  |  |  |

|                 |                                | 10 = PTG module clock source will be TAD<br>01 = PTG module clock source will be Fosc |                 |                  |                  |                 |         |  |  |  |

|                 |                                | odule clock so                                                                        |                 |                  |                  |                 |         |  |  |  |

| bit 12-8        | PTGDIV<4:0>                    | -: PTG Module                                                                         | Clock Presca    | ler (divider) bi | ts               |                 |         |  |  |  |

|                 | 11111 = Divid<br>11110 = Divid |                                                                                       |                 |                  |                  |                 |         |  |  |  |

|                 | •                              |                                                                                       |                 |                  |                  |                 |         |  |  |  |

|                 | •                              |                                                                                       |                 |                  |                  |                 |         |  |  |  |

|                 | 00001 = Divic<br>00000 = Divic | •                                                                                     |                 |                  |                  |                 |         |  |  |  |

| bit 7-4         | PTGPWD<3:0                     | <b>0&gt;:</b> PTG Trigge                                                              | er Output Pulse | e-Width bits     |                  |                 |         |  |  |  |

|                 |                                | gger outputs ar                                                                       |                 |                  |                  |                 |         |  |  |  |

|                 | 1110 = All trig                | gger outputs ar                                                                       | e 15 PIG cloc   | k cycles wide    |                  |                 |         |  |  |  |

|                 | •                              |                                                                                       |                 |                  |                  |                 |         |  |  |  |

|                 | •                              |                                                                                       |                 |                  |                  |                 |         |  |  |  |

|                 |                                | gger outputs ar<br>gger outputs ar                                                    |                 |                  |                  |                 |         |  |  |  |

| bit 3           | Unimplement                    | ted: Read as '                                                                        | 0'              |                  |                  |                 |         |  |  |  |

| bit 2-0         | PTGWDT<2:0                     | D>: Select PTO                                                                        | Watchdog Tir    | mer Time-out (   | Count Value bits | 3               |         |  |  |  |

|                 |                                | log Timer will t                                                                      |                 |                  |                  |                 |         |  |  |  |

|                 |                                | log Timer will t<br>log Timer will t                                                  |                 |                  |                  |                 |         |  |  |  |

|                 |                                | log Timer will t                                                                      |                 |                  |                  |                 |         |  |  |  |

|                 |                                | log Timer will t                                                                      |                 |                  |                  |                 |         |  |  |  |

|                 | 010 = Watchd                   | loa Timer will t                                                                      | ime-out after 1 | 6 PTG clocks     |                  |                 |         |  |  |  |

|                 |                                |                                                                                       |                 |                  |                  |                 |         |  |  |  |

|                 | 001 = Watchd                   | log Timer will t                                                                      | ime-out after 8 |                  |                  |                 |         |  |  |  |

## REGISTER 25-2: PTGCON: PTG CONTROL REGISTER

### REGISTER 26-2: CMxCON: OP AMP/COMPARATOR x CONTROL REGISTER (x = 1, 2, 3 OR 5)

bit 7

| R/W-0                 | R/W-0                 | R/W-0 | U-0                 | U-0 | R/W-0                 | R/W-0               | R/W-0               |

|-----------------------|-----------------------|-------|---------------------|-----|-----------------------|---------------------|---------------------|

| CON                   | COE                   | CPOL  | -                   | —   | OPMODE <sup>(2)</sup> | CEVT <sup>(3)</sup> | COUT                |

| bit 15                |                       |       |                     |     |                       |                     | bit 8               |

|                       |                       |       |                     |     |                       |                     |                     |

| R/W-0                 | R/W-0                 | U-0   | R/W-0               | U-0 | U-0                   | R/W-0               | R/W-0               |

| EVPOL1 <sup>(3)</sup> | EVPOL0 <sup>(3)</sup> | _     | CREF <sup>(1)</sup> | —   | _                     | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |

| _ | - |     |   |  |

|---|---|-----|---|--|

|   |   | bit | 0 |  |

| Legend:      |                      |                                                                                               |                                    |                                    |  |  |  |

|--------------|----------------------|-----------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|--|--|--|

| R = Readab   | le bit               | W = Writable bit                                                                              | U = Unimplemented bit, read as '0' |                                    |  |  |  |

| -n = Value a | It POR               | '1' = Bit is set                                                                              | '0' = Bit is cleared               | x = Bit is unknown                 |  |  |  |

| bit 15       | CON: Op              | Amp/Comparator Enable b                                                                       | it                                 |                                    |  |  |  |

|              |                      | parator is enabled<br>parator is disabled                                                     |                                    |                                    |  |  |  |

| bit 14       | COE: Co              | mparator Output Enable bit                                                                    |                                    |                                    |  |  |  |

|              |                      | parator output is present on<br>parator output is internal onl                                | •                                  |                                    |  |  |  |

| bit 13       | CPOL: C              | comparator Output Polarity S                                                                  | Select bit                         |                                    |  |  |  |

|              |                      | parator output is inverted parator output is not inverted                                     | d                                  |                                    |  |  |  |

| bit 12-11    | Unimple              | mented: Read as '0'                                                                           |                                    |                                    |  |  |  |

| bit 10       | OPMOD                | E: Op Amp Select bit <sup>(2)</sup>                                                           |                                    |                                    |  |  |  |

|              |                      | mp is enabled<br>mp is disabled                                                               |                                    |                                    |  |  |  |

| bit 9        | CEVT: C              | omparator Event bit <sup>(3)</sup>                                                            |                                    |                                    |  |  |  |

|              | inter                | parator event, according to<br>rupts until the bit is cleared<br>aparator event did not occur | the EVPOL<1:0> settings, occ       | urred; disables future triggers an |  |  |  |

| bit 8        | COUT: C              | omparator Output bit                                                                          |                                    |                                    |  |  |  |

|              | When CF              | OL = 0 (non-inverted polar                                                                    | ity):                              |                                    |  |  |  |

|              | 1 = VIN+             |                                                                                               |                                    |                                    |  |  |  |

|              | 0 = VIN+             |                                                                                               |                                    |                                    |  |  |  |

|              |                      | POL = 1 (inverted polarity):                                                                  |                                    |                                    |  |  |  |

|              | 1 = VIN+<br>0 = VIN+ | ••                                                                                            |                                    |                                    |  |  |  |

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- **2:** The op amp and the comparator can be used simultaneously in these devices. The OPMODE bit only enables the op amp while the comparator is still functional.