Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT   |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 18x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

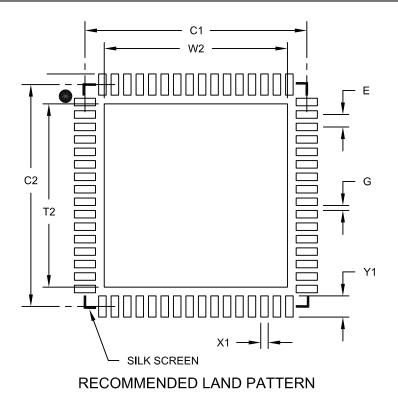

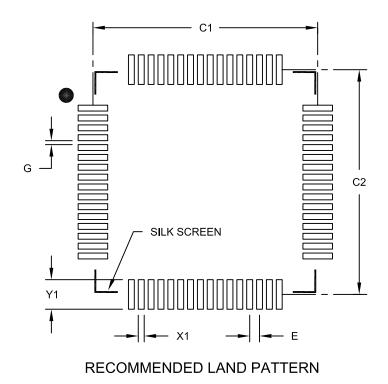

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 44-QFN (8×8)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gm604t-i-ml |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4-1: | CPU CORE REGISTER MAP | (CONTINUED) | 1 |

|------------|-----------------------|-------------|---|

|------------|-----------------------|-------------|---|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-----------|-----------|-------|-------|--------|--------|-------|-------|-------|---------------|

| SR          | 0042  | OA     | OB     | SA     | SB     | OAB    | SAB    | DA    | DC        | IPL2      | IPL1  | IPL0  | RA     | Ν      | OV    | Z     | С     | 0000          |

| CORCON      | 0044  | VAR    | _      | US1    | US0    | EDT    | DL1    | DL2   | DL0       | SATA      | SATB  | SATDW | ACCSAT | IPL3   | SFA   | RND   | IF    | 0020          |

| MODCON      | 0046  | XMODEN | YMODEN | _      | _      | BWM3   | BWM2   | BWM1  | BWM0      | YWM3      | YWM2  | YWM1  | YWM0   | XWM3   | XWM2  | XWM1  | XWM0  | 0000          |

| XMODSRT     | 0048  |        |        |        |        |        |        | XMO   | DSRT<15:0 | >         |       |       |        |        |       |       | _     | 0000          |

| XMODEND     | 004A  |        |        |        |        |        |        | XMO   | DEND<15:0 | >         |       |       |        |        |       |       | _     | 0001          |

| YMODSRT     | 004C  |        |        |        |        |        |        | YMO   | DSRT<15:0 | >         |       |       |        |        |       |       | _     | 0000          |

| YMODEND     | 004E  |        |        |        |        |        |        | YMO   | DEND<15:0 | >         |       |       |        |        |       |       | —     | 0001          |

| XBREV       | 0050  | BREN   |        |        |        |        |        |       | XBF       | REV<14:0> |       |       |        |        |       |       |       | 0000          |

| DISICNT     | 0052  | _      | _      |        |        |        |        |       |           | DISICNT<  | 13:0> |       |        |        |       |       |       | 0000          |

| TBLPAG      | 0054  | _      | _      | _      | _      | _      | _      | _     | _         |           |       |       | TBLPA  | G<7:0> |       |       |       | 0000          |

| MSTRPR      | 0058  |        |        |        |        |        |        |       | MSTRPR<   | :15:0>    |       |       |        |        |       |       |       | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-14: PWM GENERATOR 6 REGISTER MAP

| SFR Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11       | Bit 10    | Bit 9     | Bit 8            | Bit 7    | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|----------|-------|---------|---------|---------|---------|--------------|-----------|-----------|------------------|----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON6  | 0CC0  | FLTSTAT | CLSTAT  | TRGSTAT | FLTIEN  | CLIEN        | TRGIEN    | ITB       | MDCS             | DTC1     | DTC0    | DTCP     | -        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON6   | 0CC2  | PENH    | PENL    | POLH    | POLL    | PMOD1        | PMOD0     | OVRENH    | OVRENL           | OVRDAT1  | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | C000          |

| FCLCON6  | 0CC4  | IFLTMOD | CLSRC4  | CLSRC3  | CLSRC2  | CLSRC1       | CLSRC0    | CLPOL     | CLMOD            | FLTSRC4  | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 00F8          |

| PDC6     | 0CC6  |         |         |         |         |              |           |           | PDC6             | <15:0>   |         |          |          |          |          |          |          | 0000          |

| PHASE6   | 0CC8  |         |         |         |         |              |           |           | PHASE            | 6<15:0>  |         |          |          |          |          |          |          | 0000          |

| DTR6     | 0CCA  | _       | _       |         |         |              |           |           |                  | DTR6     | <13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR6  | 00000 | _       | _       |         |         |              |           |           |                  | ALTDTR   | 6<13:0> |          |          |          |          |          |          | 0000          |

| SDC6     | 0CCE  |         |         |         |         |              |           |           | SDC6             | <15:0>   |         |          |          |          |          |          |          | 0000          |

| SPHASE6  | 0CD0  |         |         |         |         |              |           |           | SPHASE           | 6<15:0>  |         |          |          |          |          |          |          | 0000          |

| TRIG6    | 0CD2  |         |         |         |         |              |           |           | TRGCM            | P<15:0>  |         |          |          |          |          |          |          | 0000          |

| TRGCON6  | 0CD4  | TRGDIV3 | TRGDIV2 | TRGDIV1 | TRGDIV0 | _            | —         | —         | _                | _        | —       | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP6  | 0CD8  |         |         |         |         |              |           |           | PWMCAF           | P6<15:0> |         |          |          | •        |          |          |          | 0000          |

| LEBCON6  | 0CDA  | PHR     | PHF     | PLR     | PLF     | FLTLEBEN     | CLLEBEN   | —         | —                | —        | _       | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY6  | 0CDC  | _       | -       | _       | _       |              |           |           | •                | •        | LEB<    | 11:0>    |          | •        | •        |          |          | 0000          |

| AUXCON6  | 0CDE  | _       | _       | _       | _       | BLANKSEL3    | BLANKSEL2 | BLANKSEL1 | <b>BLANKSEL0</b> | _        | _       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

| Logondu  |       |         | 1       |         |         | wn in hovede |           |           |                  |          |         |          |          |          |          |          |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-19: UART3 AND UART4 REGISTER MAP

| SFR<br>Name    | Addr. | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8     | Bit 7         | Bit 6    | Bit 5   | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|----------------|-------|----------|--------|----------|--------|--------|--------|--------|-----------|---------------|----------|---------|-------------|--------|--------|--------|-------|---------------|

| U3MODE         | 0250  | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1   | UEN0      | WAKE          | LPBACK   | ABAUD   | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U3STA          | 0252  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF  | TRMT      | URXISEL1      | URXISEL0 | ADDEN   | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| <b>U3TXREG</b> | 0254  | _        | _      | _        | _      | _      | _      | _      |           |               |          | UART3 T | ransmit Reg | gister |        |        |       | xxxx          |

| <b>U3RXREG</b> | 0256  | _        | _      | _        | _      | _      | _      | _      |           |               |          | UART3 F | Receive Reg | gister |        |        |       | 0000          |

| U3BRG          | 0258  |          |        |          |        |        |        | Baud I | Rate Gene | erator Presca | ler      |         |             |        |        |        |       | 0000          |

| U4MODE         | 02B0  | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1   | UEN0      | WAKE          | LPBACK   | ABAUD   | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U4STA          | 02B2  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF  | TRMT      | URXISEL1      | URXISEL0 | ADDEN   | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U4TXREG        | 02B4  | _        | _      | _        | _      | _      | _      | _      |           |               |          | UART4 T | ransmit Reg | gister |        |        |       | xxxx          |

| U4RXREG        | 02B6  | _        | _      | _        | _      | _      | _      | _      |           |               |          | UART4 F | Receive Reg | gister |        |        |       | 0000          |

| U4BRG          | 02B8  |          |        |          |        |        |        | Baud I | Rate Gene | erator Presca | ler      |         |             |        |        |        |       | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-20: SPI1, SPI2 AND SPI3 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9     | Bit 8       | Bit 7       | Bit 6       | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|--------|--------|---------|--------|--------|---------|-----------|-------------|-------------|-------------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT    | 0240  | SPIEN  | —      | SPISIDL | —      | _      | SPIBEC2 | SPIBEC1   | SPIBEC0     | SRMPT       | SPIROV      | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1    | 0242  | _      | —      | _       | DISSCK | DISSDO | MODE16  | SMP       | CKE         | SSEN        | CKP         | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2    | 0244  | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _       | _         | _           | _           | _           | _      | _      | _      | —      | FRMDLY | SPIBEN | 0000          |

| SPI1BUF     | 0248  |        |        |         |        |        |         | SPI1 Tran | smit and Re | ceive Buffe | er Register |        |        |        |        |        |        | 0000          |

| SPI2STAT    | 0260  | SPIEN  | _      | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1   | SPIBEC0     | SRMPT       | SPIROV      | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI2CON1    | 0262  | _      | —      | _       | DISSCK | DISSDO | MODE16  | SMP       | CKE         | SSEN        | CKP         | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI2CON2    | 0264  | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _       | _         | _           | _           | _           | _      | _      | _      | —      | FRMDLY | SPIBEN | 0000          |

| SPI2BUF     | 0268  |        |        |         |        |        |         | SPI2 Tran | smit and Re | ceive Buffe | er Register |        |        |        |        |        |        | 0000          |

| SPI3STAT    | 02A0  | SPIEN  | _      | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1   | SPIBEC0     | SRMPT       | SPIROV      | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI3CON1    | 02A2  | _      | —      | _       | DISSCK | DISSDO | MODE16  | SMP       | CKE         | SSEN        | CKP         | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI3CON2    | 02A4  | FRMEN  | SPIFSD | FRMPOL  | _      | —      | —       | _         | _           | _           | _           | _      | _      | —      | _      | FRMDLY | SPIBEN | 0000          |

| SPI3BUF     | 02A8  |        |        |         |        |        |         | SPI3 Tran | smit and Re | ceive Buffe | er Register |        |        |        |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

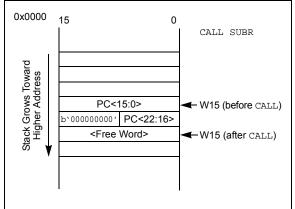

#### 4.3.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack     |

|-------|-----------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the |

|       | hardware.                               |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGM3XX/6XX/7XX devices and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack, working from lower toward higher addresses. Figure 4-13 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-13. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain the Software Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore, restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a 'C' development environment

#### FIGURE 4-13: C.

#### CALL STACK FRAME

## 4.4 Instruction Addressing Modes

The addressing modes shown in Table 4-66 form the basis of the addressing modes optimized to support the specific features of the individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

#### 4.4.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.4.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- · Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

Note: Not all instructions support all of the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Flash Programming" (DS70609), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation, over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33EPXXXGM3XX/6XX/7XX device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (Vss) and

Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data as a double program memory word, a row of 64 instructions (192 bytes), and erase program memory in blocks of 512 instruction words (1536 bytes) at a time.

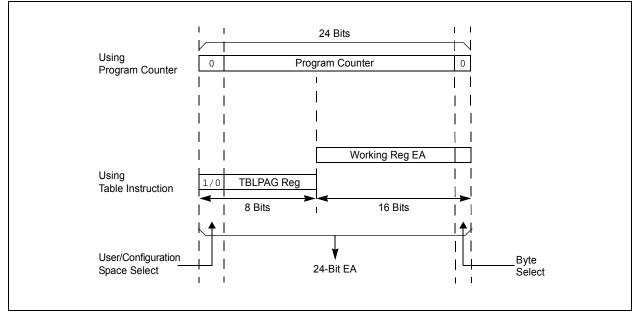

## 5.1 Table Instructions and Flash Programming

The Flash memory read and the double-word programming operations make use of the TBLRD and TBLWT instructions, respectively. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

#### REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0             | U-0                                                                                            | U-0                                                                                                                                                                       | U-0                                                                                             | R-0              | R-0              | R-0             | R-0     |

|-----------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------|------------------|-----------------|---------|

|                 |                                                                                                |                                                                                                                                                                           | —                                                                                               | ILR3             | ILR2             | ILR1            | ILR0    |

| bit 15          |                                                                                                | 1                                                                                                                                                                         |                                                                                                 |                  |                  |                 | bit 8   |

| R-0             | R-0                                                                                            | R-0                                                                                                                                                                       | R-0                                                                                             | R-0              | R-0              | R-0             | R-0     |

| VECNUM7         | VECNUM6                                                                                        | VECNUM5                                                                                                                                                                   | VECNUM4                                                                                         | VECNUM3          | VECNUM2          | VECNUM1         | VECNUM0 |

| bit 7           | VECINOMIC                                                                                      | VECINONIS                                                                                                                                                                 | VECINONIA                                                                                       | VECINONIS        | VECINONIZ        | VECNOWI         | bit (   |

| Legend:         |                                                                                                |                                                                                                                                                                           |                                                                                                 |                  |                  |                 |         |

| R = Readable    | bit                                                                                            | W = Writable                                                                                                                                                              | bit                                                                                             | U = Unimpler     | nented bit, read | l as '0'        |         |

| -n = Value at F | POR                                                                                            | '1' = Bit is set                                                                                                                                                          |                                                                                                 | '0' = Bit is cle |                  | x = Bit is unkr | nown    |

| bit 11-8        | 1111 = CPU<br>•<br>•<br>•<br>•<br>•                                                            | w CPU Interrup<br>Interrupt Priorit<br>Interrupt Priorit                                                                                                                  | y Level is 15<br>y Level is 1                                                                   |                  |                  |                 |         |

| bit 7-0         | VECNUM<7:                                                                                      | Interrupt Priorit<br>0>: Vector Num<br>255, Reserved                                                                                                                      | ber of Pendin                                                                                   | g Interrupt bits |                  |                 |         |

|                 | 00001000 =<br>00000111 =<br>00000110 =<br>00000101 =<br>00000100 =<br>00000011 =<br>00000010 = | 9, IC1 – Input 0<br>8, INT0 – Exter<br>7, Reserved; do<br>6, Generic soft<br>5, DMA Contro<br>4, Math error tr<br>3, Stack error tr<br>2, Generic hard<br>1, Address erro | nal Interrupt C<br>o not use<br>error trap<br>ller error trap<br>ap<br>rap<br>d trap<br>or trap | )                |                  |                 |         |

#### REGISTER 8-5: DMAXSTBH: DMA CHANNEL X START ADDRESS REGISTER B (HIGH)

| U-0    | U-0   | U-0   | U-0   | R/W-0  | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|--------|-------|-------|-------|

| _      | —     | _     | _     | —      | —     | —     | —     |

| bit 15 |       |       |       |        |       |       | bit 8 |

|        |       |       |       |        |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | STB<  | 23:16> |       |       |       |

| bit 7  |       |       |       |        |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: DMA Secondary Start Address bits (source or destination)

#### REGISTER 8-6: DMAXSTBL: DMA CHANNEL X START ADDRESS REGISTER B (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 | -     |                  | STB   | <15:8>            | -               | -               |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable I  | bit   | W = Writable I   | bit   | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 **STB<15:0>:** DMA Secondary Start Address bits (source or destination)

#### REGISTER 11-24: RPINR30: PERIPHERAL PIN SELECT INPUT REGISTER 30

| U-0          | U-0                  | U-0                                  | U-0   | U-0              | U-0              | U-0             | U-0    |

|--------------|----------------------|--------------------------------------|-------|------------------|------------------|-----------------|--------|

| _            | —                    | —                                    | —     | —                | —                | —               | —      |

| bit 15       |                      | -                                    |       |                  |                  | •               | bit 8  |

|              |                      |                                      |       |                  |                  |                 |        |

| U-0          | R/W-0                | R/W-0                                | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| _            |                      |                                      |       | SS3R<6:0>        |                  |                 |        |

| bit 7        |                      |                                      |       |                  |                  |                 | bit 0  |

|              |                      |                                      |       |                  |                  |                 |        |

| Legend:      |                      |                                      |       |                  |                  |                 |        |

| R = Readab   | ole bit              | W = Writable                         | bit   | U = Unimpler     | mented bit, read | as '0'          |        |

| -n = Value a | at POR               | '1' = Bit is set                     |       | '0' = Bit is cle | ared             | x = Bit is unki | nown   |

|              |                      |                                      |       |                  |                  |                 |        |

| bit 15-7     | Unimplemen           | nted: Read as '                      | 0'    |                  |                  |                 |        |

| bit 6-0      |                      | Assign SPI3 Sla<br>I-2 for input pin |       | . ,              | e Corresponding  | g RPn/RPIn Piı  | n bits |

|              | 1111111 <b>= I</b> r | nput tied to RP1                     | 124   |                  |                  |                 |        |

|              | •                    |                                      |       |                  |                  |                 |        |

• • 0000001 = Input tied to CMP1 0000000 = Input tied to Vss

# 16.2 PWMx Control Registers

## REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | HS/HC-0 | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|---------|-------|---------------------|------------------------|------------------------|

| PTEN   | —   | PTSIDL | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |         |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0      | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2(1) | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 |                         |                         |                         |                        |            |                        | bit 0                  |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit              |

|-------------------|-----------------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared x = Bit is unknown |

| bit 15  | PTEN: PWMx Module Enable bit                                                                                                                 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = PWMx module is enabled                                                                                                                   |

|         | 0 = PWMx module is disabled                                                                                                                  |

| bit 14  | Unimplemented: Read as '0'                                                                                                                   |

| bit 13  | PTSIDL: PWMx Time Base Stop in Idle Mode bit                                                                                                 |

|         | <ul> <li>1 = PWMx time base halts in CPU Idle mode</li> <li>0 = PWMx time base runs in CPU Idle mode</li> </ul>                              |

| bit 12  | SESTAT: Special Event Interrupt Status bit                                                                                                   |

|         | 1 = Special event interrupt is pending                                                                                                       |

|         | 0 = Special event interrupt is not pending                                                                                                   |

| bit 11  | SEIEN: Special Event Interrupt Enable bit                                                                                                    |

|         | 1 = Special event interrupt is enabled                                                                                                       |

|         | 0 = Special event interrupt is disabled                                                                                                      |

| bit 10  | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup>                                                                                     |

|         | 1 = Active Period register is updated immediately                                                                                            |

|         | 0 = Active Period register updates occur on PWMx cycle boundaries                                                                            |

| bit 9   | SYNCPOL: Synchronize Input and Output Polarity bit <sup>(1)</sup>                                                                            |

|         | 1 = SYNCI1/SYNCO1 polarity is inverted (active-low)<br>0 = SYNCI1/SYNCO1 is active-high                                                      |

| bit 8   | SYNCOEN: Primary Time Base Sync Enable bit <sup>(1)</sup>                                                                                    |

|         | 1 = SYNCO1 output is enabled                                                                                                                 |

|         | 0 = SYNCO1 output is disabled                                                                                                                |

| bit 7   | SYNCEN: External Time Base Synchronization Enable bit <sup>(1)</sup>                                                                         |

|         | 1 = External synchronization of primary time base is enabled                                                                                 |

|         | 0 = External synchronization of primary time base is disabled                                                                                |

| Note 1: | These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user                                        |

|         | application must program the Period register with a value that is slightly larger than the expected period of                                |

| 0       | the external synchronization input signal.<br>See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection |

| 2:      | See Section ZD.U. Ferioneral Irigger Generator (FIG) Woodule" for information on this selection                                              |

2: See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

# REGISTER 16-11: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7-6 | 6  | <b>DTC&lt;1:0&gt;:</b> Dead-Time Control bits<br>11 = Dead-Time Compensation mode                                                                                                                                                                                                                                                  |

|---------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |    | <ul> <li>10 = Dead-time function is disabled</li> <li>01 = Negative dead time is actively applied for Complementary Output mode</li> <li>00 = Positive dead time is actively applied for all Output modes</li> </ul>                                                                                                               |

| bit 5   |    | <b>DTCP:</b> Dead-Time Compensation Polarity bit <sup>(3)</sup>                                                                                                                                                                                                                                                                    |

|         |    | <u>When Set to '⊥':</u><br>If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.<br>If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                                                                                                                                                |

|         |    | <u>When Set to '<math>o</math>':</u><br>If DTCMPx = 0, PWMHx is shortened and PWMLx is lengthened.<br>If DTCMPx = 1, PWMLx is shortened and PWMHx is lengthened.                                                                                                                                                                   |

| bit 4   |    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                         |

| bit 3   |    | MTBS: Master Time Base Select bit                                                                                                                                                                                                                                                                                                  |

|         |    | <ul> <li>1 = PWMx generator uses the secondary master time base for synchronization and as the clock source for the PWMx generation logic (if secondary time base is available)</li> <li>0 = PWMx generator uses the primary master time base for synchronization and as the clock source for the PWMx generation logic</li> </ul> |

| bit 2   |    | <b>CAM:</b> Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                                                                                                                                                                                                        |

|         |    | 1 = Center-Aligned mode is enabled                                                                                                                                                                                                                                                                                                 |

| bit 1   |    | 0 = Edge-Aligned mode is enabled<br><b>XPRES:</b> External PWMx Reset Control bit <sup>(5)</sup>                                                                                                                                                                                                                                   |

| DILI    |    | <ul> <li>1 = Current-limit source resets the time base for this PWMx generator if it is in Independent Time Base<br/>mode</li> </ul>                                                                                                                                                                                               |

| bit 0   |    | <ul> <li>0 = External pins do not affect the PWMx time base</li> <li>IUE: Immediate Update Enable bit<sup>(2)</sup></li> </ul>                                                                                                                                                                                                     |

| DILU    |    | <ul> <li>1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate</li> <li>0 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the PWMx period boundary</li> </ul>                                                                                                          |

| Note    | 1: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.                                                                                                                                                                                                                       |

|         | 2: | These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                                                                                                                                                                                                                             |

|         | 3: | DTC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored.                                                                                                                                                                                                                                                                |

|         | 4: | The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.                                                                                                                                                                                                           |

|         |    |                                                                                                                                                                                                                                                                                                                                    |

**5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

# dsPIC33EPXXXGM3XX/6XX/7XX

| R/W-0                   | R/W-0                                                                                                                                                                      | R/W-0                                                                                                                                                                                   | R/W-0                                                 | R/W-0            | R/W-0              | R/W-0           | R/W-0 |  |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|--------------------|-----------------|-------|--|--|--|--|--|

| QCAPEN                  | FLTREN                                                                                                                                                                     | QFDIV2                                                                                                                                                                                  | QFDIV1                                                | QFDIV0           | OUTFNC1            | OUTFNC0         | SWPAB |  |  |  |  |  |

| bit 15                  |                                                                                                                                                                            |                                                                                                                                                                                         |                                                       |                  |                    |                 | bit 8 |  |  |  |  |  |

| R/W-0                   | R/W-0                                                                                                                                                                      | R/W-0                                                                                                                                                                                   | R/W-0                                                 | R-x              | R-x                | R-x             | R-x   |  |  |  |  |  |

| HOMPOL                  | IDXPOL                                                                                                                                                                     | QEBPOL                                                                                                                                                                                  | QEAPOL                                                | HOME             | INDEX              | QEB             | QEA   |  |  |  |  |  |

| bit 7                   |                                                                                                                                                                            | 4                                                                                                                                                                                       |                                                       |                  |                    | ~               | bit C |  |  |  |  |  |

| Legend:                 |                                                                                                                                                                            |                                                                                                                                                                                         |                                                       |                  |                    |                 |       |  |  |  |  |  |

| R = Readable            | bit                                                                                                                                                                        | W = Writable                                                                                                                                                                            | bit                                                   | U = Unimple      | mented bit, read   | as '0'          |       |  |  |  |  |  |

| -n = Value at F         | POR                                                                                                                                                                        | '1' = Bit is set                                                                                                                                                                        |                                                       | '0' = Bit is cle | eared              | x = Bit is unkn | own   |  |  |  |  |  |

| bit 15                  | <b>QCAPEN:</b> Q                                                                                                                                                           | Elx Position Co                                                                                                                                                                         | ounter Input Ca                                       | apture Enable    | bit                |                 |       |  |  |  |  |  |

|                         | 1 = Index ma                                                                                                                                                               | atch event of ho                                                                                                                                                                        | ome input trigg                                       | ers a position   | capture event      |                 |       |  |  |  |  |  |

|                         |                                                                                                                                                                            |                                                                                                                                                                                         | •                                                     |                  | position capture   | e event         |       |  |  |  |  |  |

| bit 14                  |                                                                                                                                                                            | EAx/QEBx/IND                                                                                                                                                                            | -                                                     | ital Filter Enal | ole bit            |                 |       |  |  |  |  |  |

|                         |                                                                                                                                                                            | digital filter is a digital filter is a                                                                                                                                                 |                                                       | ssed)            |                    |                 |       |  |  |  |  |  |

| bit 13-11               |                                                                                                                                                                            | -                                                                                                                                                                                       |                                                       | -                | Filter Clock Divid | le Select hits  |       |  |  |  |  |  |

|                         |                                                                                                                                                                            | <b>QFDIV&lt;2:0&gt;:</b> QEAx/QEBx/INDXx/HOMEx Digital Input Filter Clock Divide Select bits<br>111 = 1:128 clock divide                                                                |                                                       |                  |                    |                 |       |  |  |  |  |  |

|                         | 110 <b>= 1:64 c</b>                                                                                                                                                        |                                                                                                                                                                                         |                                                       |                  |                    |                 |       |  |  |  |  |  |

|                         | 101 = 1:32 clock divide                                                                                                                                                    |                                                                                                                                                                                         |                                                       |                  |                    |                 |       |  |  |  |  |  |

|                         | 100 = 1:16 clock divide<br>011 = 1:8 clock divide                                                                                                                          |                                                                                                                                                                                         |                                                       |                  |                    |                 |       |  |  |  |  |  |

|                         | 011 = 1.8  clc<br>010 = 1:4  clc                                                                                                                                           |                                                                                                                                                                                         |                                                       |                  |                    |                 |       |  |  |  |  |  |

|                         | 001 = 1:2 clo                                                                                                                                                              |                                                                                                                                                                                         |                                                       |                  |                    |                 |       |  |  |  |  |  |

|                         | 000 = 1:1 clo                                                                                                                                                              | ock divide                                                                                                                                                                              |                                                       |                  |                    |                 |       |  |  |  |  |  |

| bit 10-9                |                                                                                                                                                                            | 0>: QEIx Modu                                                                                                                                                                           | -                                                     |                  |                    |                 |       |  |  |  |  |  |

|                         |                                                                                                                                                                            |                                                                                                                                                                                         |                                                       |                  | $SxCNT \ge QEIx$   | GEC             |       |  |  |  |  |  |

|                         |                                                                                                                                                                            | ITCMPx pin go<br>ITCMPx pin go                                                                                                                                                          |                                                       |                  |                    |                 |       |  |  |  |  |  |

|                         | 00 = Output                                                                                                                                                                |                                                                                                                                                                                         |                                                       |                  |                    |                 |       |  |  |  |  |  |

| bit 8                   | SWPAB: Sw                                                                                                                                                                  | ap QEAx and (                                                                                                                                                                           | QEBx Inputs bi                                        | t                |                    |                 |       |  |  |  |  |  |

|                         |                                                                                                                                                                            | d QEBx are sv                                                                                                                                                                           |                                                       |                  | ecoder logic       |                 |       |  |  |  |  |  |

|                         | 0 = QEAx an                                                                                                                                                                | d QEBx are no                                                                                                                                                                           | t swapped                                             |                  |                    |                 |       |  |  |  |  |  |

| 1.11.7                  |                                                                                                                                                                            |                                                                                                                                                                                         |                                                       |                  |                    |                 |       |  |  |  |  |  |

| bit 7                   |                                                                                                                                                                            | OMEx Input Po                                                                                                                                                                           | plarity Select b                                      | it               |                    |                 |       |  |  |  |  |  |

| DIT /                   | 1 = Input is ir                                                                                                                                                            | nverted                                                                                                                                                                                 | plarity Select b                                      | it               |                    |                 |       |  |  |  |  |  |

|                         | 1 = Input is ir<br>0 = Input is n                                                                                                                                          | nverted<br>lot inverted                                                                                                                                                                 | -                                                     | it               |                    |                 |       |  |  |  |  |  |

| bit 6                   | 1 = Input is ir<br>0 = Input is n<br>IDXPOL: INE                                                                                                                           | nverted<br>not inverted<br>DXx Input Pola                                                                                                                                               | -                                                     | it               |                    |                 |       |  |  |  |  |  |

|                         | 1 = Input is ir<br>0 = Input is n                                                                                                                                          | nverted<br>not inverted<br>DXx Input Pola<br>nverted                                                                                                                                    | -                                                     | it               |                    |                 |       |  |  |  |  |  |

| bit 6                   | 1 = Input is ir<br>0 = Input is n<br>IDXPOL: INE<br>1 = Input is ir<br>0 = Input is n                                                                                      | nverted<br>lot inverted<br>DXx Input Pola<br>nverted<br>lot inverted                                                                                                                    | ity Select bit                                        | it               |                    |                 |       |  |  |  |  |  |

|                         | 1 = Input is ir<br>0 = Input is n<br>IDXPOL: INE<br>1 = Input is ir<br>0 = Input is n                                                                                      | nverted<br>not inverted<br>DXx Input Pola<br>nverted<br>not inverted<br>EBx Input Pola                                                                                                  | ity Select bit                                        | it               |                    |                 |       |  |  |  |  |  |

| bit 6                   | 1 = Input is ir<br>0 = Input is n<br>IDXPOL: INE<br>1 = Input is ir<br>0 = Input is n<br>QEBPOL: Q                                                                         | nverted<br>not inverted<br>DXx Input Pola<br>nverted<br>not inverted<br>EBx Input Pola<br>inverted                                                                                      | ity Select bit                                        | it               |                    |                 |       |  |  |  |  |  |

| bit 6                   | 1 = Input is in<br>0 = Input is in<br><b>IDXPOL:</b> INE<br>1 = Input is in<br>0 = Input is in<br><b>QEBPOL:</b> Q<br>1 = Input is in<br>0 = Input is in                   | nverted<br>not inverted<br>DXx Input Pola<br>nverted<br>not inverted<br>EBx Input Pola<br>inverted                                                                                      | ity Select bit<br>rity Select bit                     | it               |                    |                 |       |  |  |  |  |  |

| bit 6<br>bit 5          | 1 = Input is in<br>0 = Input is in<br>IDXPOL: INE<br>1 = Input is in<br>0 = Input is in<br>QEBPOL: Q<br>1 = Input is i<br>0 = Input is i<br>QEAPOL: Q<br>1 = Input is i    | nverted<br>not inverted<br>DXx Input Pola<br>nverted<br>not inverted<br>EBx Input Pola<br>not inverted<br>EAx Input Pola<br>inverted                                                    | ity Select bit<br>rity Select bit                     | it               |                    |                 |       |  |  |  |  |  |

| bit 6<br>bit 5<br>bit 4 | 1 = Input is in<br>0 = Input is in<br>IDXPOL: INE<br>1 = Input is in<br>0 = Input is in<br>QEBPOL: Q<br>1 = Input is in<br>QEAPOL: Q<br>1 = Input is in<br>0 = Input is in | nverted<br>not inverted<br>DXx Input Pola<br>nverted<br>EBx Input Pola<br>inverted<br>not inverted<br>EAx Input Pola<br>inverted<br>not inverted<br>not inverted                        | rity Select bit<br>rity Select bit<br>rity Select bit |                  |                    |                 |       |  |  |  |  |  |

| bit 6<br>bit 5          | 1 = Input is in<br>0 = Input is in<br>IDXPOL: INE<br>1 = Input is in<br>0 = Input is in<br>QEBPOL: Q<br>1 = Input is in<br>QEAPOL: Q<br>1 = Input is in<br>0 = Input is in | nverted<br>not inverted<br>DXx Input Pola<br>not inverted<br>EBx Input Pola<br>inverted<br>not inverted<br>EAx Input Pola<br>inverted<br>not inverted<br>not inverted<br>us of HOMEx Ir | rity Select bit<br>rity Select bit<br>rity Select bit |                  | l bit              |                 |       |  |  |  |  |  |

#### REGISTER 17-2: QEIXIOC: QEIX I/O CONTROL REGISTER

© 2013-2014 Microchip Technology Inc.

## REGISTER 21-8: CxEC: CANx TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0      |

|----------|----------|----------|----------|----------|----------|----------|----------|

| TERRCNT7 | TERRCNT6 | TERRCNT5 | TERRCNT4 | TERRCNT3 | TERRCNT2 | TERRCNT1 | TERRCNT0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R-0      |

|----------|----------|----------|----------|----------|----------|----------|----------|

| RERRCNT7 | RERRCNT6 | RERRCNT5 | RERRCNT4 | RERRCNT3 | RERRCNT2 | RERRCNT1 | RERRCNT0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 TERRCNT<7:0>: Transmit Error Count bits

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

#### REGISTER 21-9: CxCFG1: CANx BAUD RATE CONFIGURATION REGISTER 1

| U-0                 | U-0                                                                                                                          | U-0                                                                                                   | U-0                                | U-0              | U-0              | U-0             | U-0   |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------|------------------|------------------|-----------------|-------|

| _                   | —                                                                                                                            | _                                                                                                     |                                    | —                | —                | —               |       |

| bit 15              |                                                                                                                              |                                                                                                       |                                    |                  |                  |                 | bit   |

|                     |                                                                                                                              |                                                                                                       |                                    |                  |                  |                 |       |

| R/W-0               | R/W-0                                                                                                                        | R/W-0                                                                                                 | R/W-0                              | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| SJW1                | SJW0                                                                                                                         | BRP5                                                                                                  | BRP4                               | BRP3             | BRP2             | BRP1            | BRP0  |

| bit 7               |                                                                                                                              |                                                                                                       |                                    |                  |                  |                 | bit   |

|                     |                                                                                                                              |                                                                                                       |                                    |                  |                  |                 |       |

| Legend:             |                                                                                                                              |                                                                                                       |                                    |                  |                  |                 |       |

| R = Readable        | e bit                                                                                                                        | W = Writable                                                                                          | bit                                | U = Unimplen     | nented bit, read | as '0'          |       |

| -n = Value at       | POR                                                                                                                          | '1' = Bit is set                                                                                      |                                    | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                     |                                                                                                                              |                                                                                                       |                                    |                  |                  |                 |       |

|                     |                                                                                                                              |                                                                                                       |                                    |                  |                  |                 |       |

| bit 15-8            | Unimplemen                                                                                                                   | ited: Read as '                                                                                       | 0'                                 |                  |                  |                 |       |

| bit 15-8<br>bit 7-6 | -                                                                                                                            | i <b>ted:</b> Read as '<br>Synchronization                                                            |                                    | bits             |                  |                 |       |

|                     | <b>SJW&lt;1:0&gt;:</b> S<br>11 = Length i                                                                                    | Synchronization<br>is 4 x TQ                                                                          |                                    | bits             |                  |                 |       |

|                     | <b>SJW&lt;1:0&gt;:</b> S<br>11 = Length i<br>10 = Length i                                                                   | Synchronization<br>is 4 x TQ<br>is 3 x TQ                                                             |                                    | bits             |                  |                 |       |

|                     | <b>SJW&lt;1:0&gt;:</b> S<br>11 = Length i<br>10 = Length i<br>01 = Length i                                                  | Synchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ                                                   |                                    | bits             |                  |                 |       |

| bit 7-6             | <b>SJW&lt;1:0&gt;:</b> S<br>11 = Length i<br>10 = Length i<br>01 = Length i<br>00 = Length i                                 | Synchronization<br>Is 4 x TQ<br>Is 3 x TQ<br>Is 2 x TQ<br>Is 1 x TQ                                   | i Jump Width                       | bits             |                  |                 |       |