Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Decalis                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gm710-e-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Ref-erence Manual"*, which are available from the Microchip web site (www.microchip.com). These documents should be considered as the general reference for the operation of a particular module or device feature.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70000600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70000598)

- "Timers" (DS70362)

- "Input Capture" (DS70000352)

- "Output Compare" (DS70005157)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582)

- "Serial Peripheral Interface (SPI)" (DS70005185)

- "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70000195)

- "Data Converter Interface (DCI) Module" (DS70356)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70000357)

- "32-Bit Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Parallel Master Port (PMP)" (DS70576)

- "Device Configuration" (DS70000618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

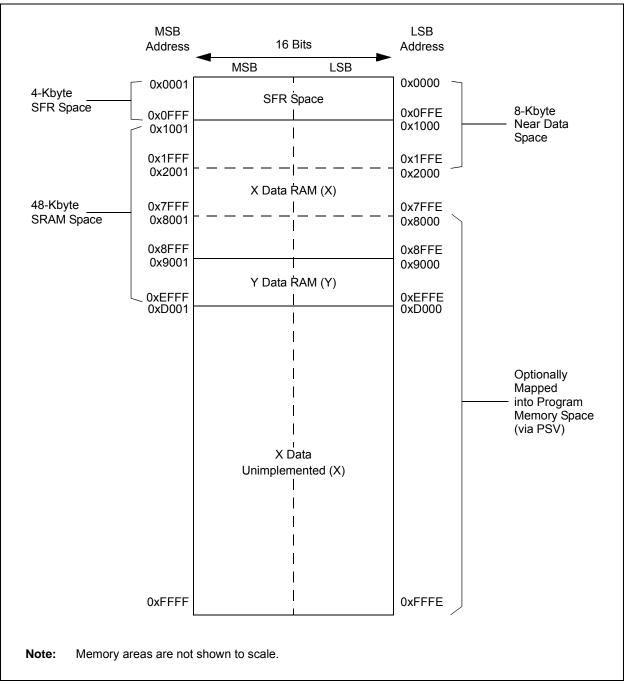

#### FIGURE 4-7: DATA MEMORY MAP FOR 512-KBYTE DEVICES

| TABLE 4-1: | CPU CORE REGISTER MAP | (CONTINUED) | 1 |

|------------|-----------------------|-------------|---|

|------------|-----------------------|-------------|---|

|             |       |        | -             |        |        | ••••••• | -      | -     | -         |           |       | -     |        |        |       | -     |       |               |

|-------------|-------|--------|---------------|--------|--------|---------|--------|-------|-----------|-----------|-------|-------|--------|--------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14        | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9 | Bit 8     | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| SR          | 0042  | OA     | OB            | SA     | SB     | OAB     | SAB    | DA    | DC        | IPL2      | IPL1  | IPL0  | RA     | Ν      | OV    | Z     | С     | 0000          |

| CORCON      | 0044  | VAR    | _             | US1    | US0    | EDT     | DL1    | DL2   | DL0       | SATA      | SATB  | SATDW | ACCSAT | IPL3   | SFA   | RND   | IF    | 0020          |

| MODCON      | 0046  | XMODEN | YMODEN        | _      | _      | BWM3    | BWM2   | BWM1  | BWM0      | YWM3      | YWM2  | YWM1  | YWM0   | XWM3   | XWM2  | XWM1  | XWM0  | 0000          |

| XMODSRT     | 0048  |        | XMODSRT<15:0> |        |        |         |        |       |           |           |       | _     | 0000   |        |       |       |       |               |

| XMODEND     | 004A  |        | XMODEND<15:0> |        |        |         |        |       |           |           | _     | 0001  |        |        |       |       |       |               |

| YMODSRT     | 004C  |        |               |        |        |         |        | YMO   | DSRT<15:0 | >         |       |       |        |        |       |       | _     | 0000          |

| YMODEND     | 004E  |        |               |        |        |         |        | YMO   | DEND<15:0 | >         |       |       |        |        |       |       | —     | 0001          |

| XBREV       | 0050  | BREN   |               |        |        |         |        |       | XBF       | REV<14:0> |       |       |        |        |       |       |       | 0000          |

| DISICNT     | 0052  | _      | _             |        |        |         |        |       |           | DISICNT<  | 13:0> |       |        |        |       |       |       | 0000          |

| TBLPAG      | 0054  | _      | _             | _      | _      | _       | _      | _     | _         |           |       |       | TBLPA  | G<7:0> |       |       |       | 0000          |

| MSTRPR      | 0058  |        | MSTRPR<15:0>  |        |        |         |        |       |           |           | 0000  |       |        |        |       |       |       |               |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

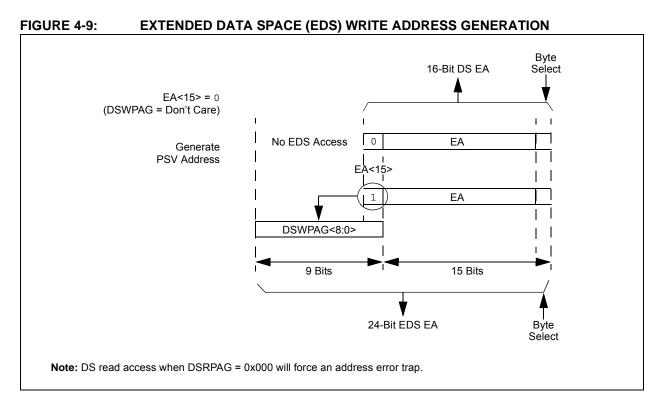

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Figure 4-10.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS only. The Data Space and EDS can be read from, and written to, using DSRPAG and DSWPAG, respectively.

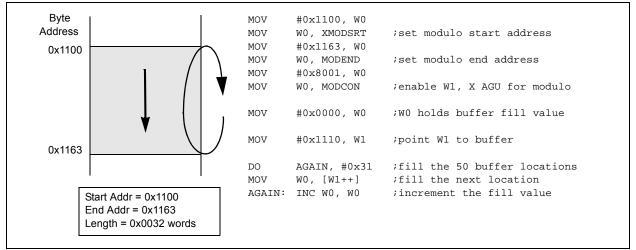

# 4.5 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a Bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.5.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word-sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.5.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register bits, MODCON<15:0>, contain enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM) to which Modulo Addressing is to be applied is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set (MODCON<14>).

#### FIGURE 4-14: MODULO ADDRESSING OPERATION EXAMPLE

| U-0                | R/W-0                                                                                                                                                     | R/W-0                                                       | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|

| —                  |                                                                                                                                                           |                                                             |       | HOME1R<6:0        | >               |                 |       |  |  |  |  |  |

| bit 15             |                                                                                                                                                           |                                                             |       |                   |                 |                 | bit 8 |  |  |  |  |  |

|                    |                                                                                                                                                           |                                                             |       |                   |                 |                 |       |  |  |  |  |  |

| U-0                | R/W-0                                                                                                                                                     | R/W-0                                                       | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |

| _                  |                                                                                                                                                           |                                                             |       | INDX1R<6:0>       | >               |                 |       |  |  |  |  |  |

| bit 7              |                                                                                                                                                           |                                                             |       |                   |                 |                 | bit 0 |  |  |  |  |  |

|                    |                                                                                                                                                           |                                                             |       |                   |                 |                 |       |  |  |  |  |  |

| Legend:            |                                                                                                                                                           |                                                             |       |                   |                 |                 |       |  |  |  |  |  |

| R = Readable bit   |                                                                                                                                                           | W = Writable                                                | bit   | U = Unimplen      | nented bit, rea | id as '0'       |       |  |  |  |  |  |

| -n = Value a       | It POR                                                                                                                                                    | '1' = Bit is set                                            |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |  |  |

| bit 15<br>bit 14-8 | Unimplemented: Read as '0'<br>HOME1R<6:0>: Assign QEI1 HOME (HOME1) to the Corresponding RPn Pin bits<br>(see Table 11-2 for input pin selection numbers) |                                                             |       |                   |                 |                 |       |  |  |  |  |  |

|                    | -                                                                                                                                                         | 1-2 for input pin<br>Input tied to RPI                      |       | nbers)            |                 |                 |       |  |  |  |  |  |

|                    | •                                                                                                                                                         |                                                             |       |                   |                 |                 |       |  |  |  |  |  |

|                    | •                                                                                                                                                         |                                                             |       |                   |                 |                 |       |  |  |  |  |  |

|                    | •                                                                                                                                                         |                                                             |       |                   |                 |                 |       |  |  |  |  |  |

|                    |                                                                                                                                                           | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss |       |                   |                 |                 |       |  |  |  |  |  |

| bit 7              |                                                                                                                                                           | nted: Read as '                                             |       |                   |                 |                 |       |  |  |  |  |  |

| bit 6-0            |                                                                                                                                                           |                                                             |       |                   |                 |                 |       |  |  |  |  |  |

|                    |                                                                                                                                                           | Input tied to CM<br>Input tied to Vss                       |       |                   |                 |                 |       |  |  |  |  |  |

# REGISTER 11-11: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15

| U-0                                | U-0   | U-0        | U-0                                     | U-0                                | U-0   | U-0   | U-0   |  |  |

|------------------------------------|-------|------------|-----------------------------------------|------------------------------------|-------|-------|-------|--|--|

| —                                  | —     | —          | —                                       | —                                  | —     | _     | —     |  |  |

| bit 15                             |       |            |                                         |                                    |       |       | bit 8 |  |  |

|                                    |       |            |                                         |                                    |       |       |       |  |  |

| U-0                                | R/W-0 | R/W-0      | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

| —                                  |       | COFSR<6:0> |                                         |                                    |       |       |       |  |  |

| bit 7                              |       |            |                                         |                                    |       |       | bit 0 |  |  |

|                                    |       |            |                                         |                                    |       |       |       |  |  |

| Legend:                            |       |            |                                         |                                    |       |       |       |  |  |

| R = Readable bit W = Writable bit  |       |            | bit                                     | U = Unimplemented bit, read as '0' |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set |       |            | '0' = Bit is cleared x = Bit is unknown |                                    |       |       |       |  |  |

# REGISTER 11-19: RPINR25: PERIPHERAL PIN SELECT INPUT REGISTER 25

#### bit 15-7 Unimplemented: Read as '0'

bit 6-0 **COFSR<6:0>:** Assign DCI Frame Sync Input (COFS) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111100 = Input tied to RPI124

•

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

## REGISTER 11-36: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| U-0           | U-0                                                                        | R/W-0                                | R/W-0                           | R/W-0                              | R/W-0         | R/W-0              | R/W-0 |  |

|---------------|----------------------------------------------------------------------------|--------------------------------------|---------------------------------|------------------------------------|---------------|--------------------|-------|--|

| _             | —                                                                          |                                      |                                 | RP55                               | R<5:0>        |                    |       |  |

| bit 15        |                                                                            |                                      |                                 |                                    |               |                    | bit 8 |  |

| U-0           | U-0                                                                        | R/W-0                                |                                 | D/M/ 0                             | D/M/ 0        | D/M/ O             | DAM 0 |  |

| 0-0           | 0-0                                                                        | R/W-U                                | R/W-0                           | R/W-0                              | R/W-0         | R/W-0              | R/W-0 |  |

|               |                                                                            |                                      |                                 | RP54                               | R<5:0>        |                    |       |  |

| bit 7         |                                                                            |                                      |                                 |                                    |               |                    | bit 0 |  |

|               |                                                                            |                                      |                                 |                                    |               |                    |       |  |

| Legend:       |                                                                            |                                      |                                 |                                    |               |                    |       |  |

| R = Readabl   | le bit                                                                     | W = Writable                         | bit                             | U = Unimplemented bit, read as '0' |               |                    |       |  |

| -n = Value at | t POR                                                                      | '1' = Bit is set                     | Bit is set '0' = Bit is cleared |                                    |               | x = Bit is unknown |       |  |

| bit 15-14     | Unimpleme                                                                  | nted: Read as '                      | 0'                              |                                    |               |                    |       |  |

| bit 13-8      |                                                                            | Peripheral Out<br>1-3 for peripheral | •                               | n is Assigned to mbers)            | RP55 Output I | Pin bits           |       |  |

| bit 7-6       | Unimpleme                                                                  | nted: Read as '                      | 0'                              |                                    |               |                    |       |  |

| bit 5-0       | RP54R<5:0>: Peripheral Output Function is Assigned to RP54 Output Pin bits |                                      |                                 |                                    |               |                    |       |  |

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-37: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0                                | U-0                                                                                     | R/W-0          | R/W-0               | R/W-0                              | R/W-0              | R/W-0 | R/W-0 |  |  |

|------------------------------------|-----------------------------------------------------------------------------------------|----------------|---------------------|------------------------------------|--------------------|-------|-------|--|--|

| _                                  | —                                                                                       |                |                     | RP57R<                             | <5:0>              |       |       |  |  |

| bit 15                             |                                                                                         |                |                     |                                    |                    |       | bit 8 |  |  |

|                                    |                                                                                         |                |                     |                                    |                    |       |       |  |  |

| U-0                                | U-0                                                                                     | R/W-0          | R/W-0               | R/W-0                              | R/W-0              | R/W-0 | R/W-0 |  |  |

| —                                  | —                                                                                       |                | RP56R<5:0>          |                                    |                    |       |       |  |  |

| bit 7                              |                                                                                         |                |                     |                                    |                    |       | bit 0 |  |  |

|                                    |                                                                                         |                |                     |                                    |                    |       |       |  |  |

| Legend:                            |                                                                                         |                |                     |                                    |                    |       |       |  |  |

| R = Readab                         | le bit                                                                                  | W = Writable   | bit                 | U = Unimplemented bit, read as '0' |                    |       |       |  |  |

| -n = Value at POR '1' = Bit is set |                                                                                         |                | '0' = Bit is cleare | ed                                 | x = Bit is unknown |       |       |  |  |

|                                    |                                                                                         |                |                     |                                    |                    |       |       |  |  |

| bit 15-14                          | Unimplemen                                                                              | ted: Read as ' | 0'                  |                                    |                    |       |       |  |  |

| bit 13-8                           | <b>RP57R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP57 Output Pin bits |                |                     |                                    |                    |       |       |  |  |

bit 13-8 **RP57R<5:0>:** Peripheral Output Function is Assigned to RP57 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP56R<5:0>:** Peripheral Output Function is Assigned to RP56 Output Pin bits (see Table 11-3 for peripheral function numbers)

# REGISTER 16-2: PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2

| U-0                                | U-0 | U-0 | U-0 | U-0                                     | U-0             | U-0   | U-0   |  |  |

|------------------------------------|-----|-----|-----|-----------------------------------------|-----------------|-------|-------|--|--|

| —                                  | —   | —   | —   | —                                       | —               | —     | _     |  |  |

| bit 15                             |     |     |     |                                         |                 |       | bit 8 |  |  |

|                                    |     |     |     |                                         |                 |       |       |  |  |

| U-0                                | U-0 | U-0 | U-0 | U-0                                     | R/W-0           | R/W-0 | R/W-0 |  |  |

| —                                  | —   | —   | —   | —                                       | PCLKDIV<2:0>(1) |       |       |  |  |

| bit 7                              |     |     | •   | •                                       |                 |       | bit 0 |  |  |

|                                    |     |     |     |                                         |                 |       |       |  |  |

| Legend:                            |     |     |     |                                         |                 |       |       |  |  |

| R = Readable bit W = Writable bit  |     |     | bit | U = Unimplemented bit, read as '0'      |                 |       |       |  |  |

| -n = Value at POR '1' = Bit is set |     |     |     | '0' = Bit is cleared x = Bit is unknown |                 |       |       |  |  |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved

- 110 = Divide-by-64

- 101 = Divide-by-32

- 100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Quadrature Encoder Interface (QEI)" (DS70601) which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

This chapter describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI module include:

- · 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 16-Bit Velocity Counter

- 32-Bit Position Initialization/Capture/Compare High Register

- 32-Bit Position Compare Low Register

- x4 Quadrature Count mode

- External Up/Down Count mode

- External Gated Count mode

- · External Gated Timer mode

- Internal Timer mode

Figure 17-1 illustrates the QEIx block diagram.

| U-0                                                                                       | U-0                | U-0              | U-0             | U-0              | U-0                        | U-0                | U-0   |  |  |

|-------------------------------------------------------------------------------------------|--------------------|------------------|-----------------|------------------|----------------------------|--------------------|-------|--|--|

| —                                                                                         | _                  | _                | _               | _                | _                          |                    | _     |  |  |

| bit 15                                                                                    |                    |                  |                 |                  | ı                          |                    | bit 8 |  |  |

|                                                                                           |                    |                  |                 |                  |                            |                    |       |  |  |

| U-0                                                                                       | U-0                | U-0              | R-0             | R-0              | R-0                        | R-0                | R-0   |  |  |

| —                                                                                         | —                  | —                | DNCNT<4:0>      |                  |                            |                    |       |  |  |

| bit 7                                                                                     |                    |                  |                 |                  |                            |                    | bit 0 |  |  |

|                                                                                           |                    |                  |                 |                  |                            |                    |       |  |  |

| Legend:                                                                                   |                    |                  |                 |                  |                            |                    |       |  |  |

| R = Readable bit W =                                                                      |                    | W = Writable     | bit             | U = Unimpler     | plemented bit, read as '0' |                    |       |  |  |

| -n = Value at P                                                                           | OR                 | '1' = Bit is set |                 | '0' = Bit is cle | eared                      | x = Bit is unknown |       |  |  |

|                                                                                           |                    |                  |                 |                  |                            |                    |       |  |  |

| bit 15-5                                                                                  | Unimplemen         | ted: Read as 'o  | כ'              |                  |                            |                    |       |  |  |

| bit 4-0                                                                                   | DNCNT<4:0>         | : DeviceNet™     | Filter Bit Num  | iber bits        |                            |                    |       |  |  |

|                                                                                           | 10010-11111        | L = Invalid sele | ction           |                  |                            |                    |       |  |  |

|                                                                                           | 10001 <b>= Com</b> | npare up to Dat  | a Byte 3, bit 6 | 6 with EID<17>   | •                          |                    |       |  |  |

|                                                                                           | •                  |                  |                 |                  |                            |                    |       |  |  |

|                                                                                           | •                  |                  |                 |                  |                            |                    |       |  |  |

| •                                                                                         |                    |                  |                 |                  |                            |                    |       |  |  |

| 00001 = Compare up to Data Byte 1, bit 7 with EID<0><br>00000 = Do not compare data bytes |                    |                  |                 |                  |                            |                    |       |  |  |

# REGISTER 21-2: CxCTRL2: CANx CONTROL REGISTER 2

| R/W-0             | R/W-0  | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |

|-------------------|--------|------------------|--------|------------------------------------|--------|--------------------|--------|--|

| F15BP3            | F15BP2 | F15BP1           | F15BP0 | F14BP3                             | F14BP2 | F14BP1             | F14BP0 |  |

| bit 15            |        |                  |        | ·                                  |        |                    | bit 8  |  |

|                   |        |                  |        |                                    |        |                    |        |  |

| R/W-0             | R/W-0  | R/W-0            | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |

| F13BP3            | F13BP2 | F13BP1           | F13BP0 | F12BP3                             | F12BP2 | F12BP1             | F12BP0 |  |

| bit 7             |        |                  |        |                                    |        |                    | bit 0  |  |

|                   |        |                  |        |                                    |        |                    |        |  |

| Legend:           |        |                  |        |                                    |        |                    |        |  |

| R = Readable bit  |        | W = Writable     | bit    | U = Unimplemented bit, read as '0' |        |                    |        |  |

| -n = Value at POR |        | '1' = Bit is set |        | '0' = Bit is cle                   | ared   | x = Bit is unknown |        |  |

# REGISTER 21-15: CxBUFPNT4: CANx FILTERS 12-15 BUFFER POINTER REGISTER 4

| bit 15-12 | F15BP<3:0>: RX Buffer Mask for Filter 15 bits<br>1111 = Filter hits received in RX FIFO buffer<br>1110 = Filter hits received in RX Buffer 14 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|           | •                                                                                                                                             |

|           | •                                                                                                                                             |

|           | 0001 = Filter hits received in RX Buffer 1<br>0000 = Filter hits received in RX Buffer 0                                                      |

| bit 11-8  | F14BP<3:0>: RX Buffer Mask for Filter 14 bits (same values as bits 15-12)                                                                     |

| bit 7-4   | F13BP<3:0>: RX Buffer Mask for Filter 13 bits (same values as bits 15-12)                                                                     |

| bit 3-0   | F12BP<3:0>: RX Buffer Mask for Filter 12 bits (same values as bits 15-12)                                                                     |

|                       | R/W-0                                                                                                                                     | R/W-0                                                                                | U-0                              | U-0               | U-0             | R/W-0               | R/W-0               |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------|-------------------|-----------------|---------------------|---------------------|--|--|--|

| CON                   | COE                                                                                                                                       | CPOL                                                                                 |                                  | _                 |                 | CEVT <sup>(2)</sup> | COUT                |  |  |  |

| bit 15                |                                                                                                                                           | 1                                                                                    |                                  |                   |                 |                     | bit                 |  |  |  |

|                       |                                                                                                                                           |                                                                                      |                                  |                   |                 |                     |                     |  |  |  |

| R/W-0                 | R/W-0                                                                                                                                     | U-0                                                                                  | R/W-0                            | U-0               | U-0             | R/W-0               | R/W-0               |  |  |  |

| EVPOL1 <sup>(2)</sup> | EVPOL0 <sup>(2)</sup>                                                                                                                     | —                                                                                    | CREF <sup>(1)</sup>              | —                 |                 | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |  |  |  |

| bit 7                 |                                                                                                                                           |                                                                                      |                                  |                   |                 |                     | bit                 |  |  |  |

| Legend:               |                                                                                                                                           |                                                                                      |                                  |                   |                 |                     |                     |  |  |  |

| R = Readable          | e bit                                                                                                                                     | W = Writable                                                                         | bit                              | U = Unimplen      | nented bit, rea | d as '0'            |                     |  |  |  |

| -n = Value at         | POR                                                                                                                                       | '1' = Bit is set                                                                     |                                  | '0' = Bit is clea | ared            | x = Bit is unkn     | own                 |  |  |  |

|                       |                                                                                                                                           |                                                                                      |                                  |                   |                 |                     |                     |  |  |  |

| bit 15                | CON: Op Am                                                                                                                                | p/Comparator                                                                         | Enable bit                       |                   |                 |                     |                     |  |  |  |

|                       | 1 = Comparator is enabled                                                                                                                 |                                                                                      |                                  |                   |                 |                     |                     |  |  |  |

|                       | 0 = Comparat                                                                                                                              |                                                                                      |                                  |                   |                 |                     |                     |  |  |  |

| bit 14                | COE: Comparator Output Enable bit                                                                                                         |                                                                                      |                                  |                   |                 |                     |                     |  |  |  |

|                       |                                                                                                                                           | or output is pro<br>or output is int                                                 | esent on the C<br>ernal only     | xOUT pin          |                 |                     |                     |  |  |  |

| bit 13                | CPOL: Comparator Output Polarity Select bit                                                                                               |                                                                                      |                                  |                   |                 |                     |                     |  |  |  |

|                       | 1 = Comparator output is inverted                                                                                                         |                                                                                      |                                  |                   |                 |                     |                     |  |  |  |

|                       |                                                                                                                                           | or output is no                                                                      |                                  |                   |                 |                     |                     |  |  |  |

| bit 12-10             | -                                                                                                                                         | ted: Read as '                                                                       |                                  |                   |                 |                     |                     |  |  |  |

| bit 9                 | <b>CEVT:</b> Comparator Event bit <sup>(2)</sup>                                                                                          |                                                                                      |                                  |                   |                 |                     |                     |  |  |  |

| bit 5                 | 1 = Comparator event, according to the EVPOL<1:0> settings, occurred; disables future triggers and<br>interrupts until the bit is cleared |                                                                                      |                                  |                   |                 |                     |                     |  |  |  |

| bit 0                 | interrunte                                                                                                                                |                                                                                      | hored                            |                   |                 |                     |                     |  |  |  |

| bit 0                 |                                                                                                                                           |                                                                                      |                                  |                   |                 |                     |                     |  |  |  |

|                       | 0 = Compara                                                                                                                               | tor event did n                                                                      | ot occur                         |                   |                 |                     |                     |  |  |  |

|                       | 0 = Compara<br>COUT: Comp                                                                                                                 | tor event did n<br>arator Output b                                                   | ot occur<br>bit                  |                   |                 |                     |                     |  |  |  |

|                       | 0 = Compara<br>COUT: Comp                                                                                                                 | tor event did n<br>arator Output b<br>= 0 (non-invert                                | ot occur<br>bit                  |                   |                 |                     |                     |  |  |  |

|                       | 0 = Compara<br>COUT: Comp<br>When CPOL :                                                                                                  | tor event did n<br>arator Output t<br>= <u>0 (non-invert</u><br><del>\</del> -       | ot occur<br>bit                  |                   |                 |                     |                     |  |  |  |

| bit 8                 | 0 = Compara<br><b>COUT</b> : Comp<br><u>When CPOL</u><br>1 = VIN+ > VIN<br>0 = VIN+ < VIN<br><u>When CPOL</u>                             | tor event did n<br>arator Output t<br>= 0 (non-invert<br>N-<br>N-<br>= 1 (inverted p | ot occur<br>bit<br>ed polarity): |                   |                 |                     |                     |  |  |  |

|                       | 0 = Compara<br><b>COUT:</b> Comp<br><u>When CPOL</u><br>1 = VIN+ > VIN<br>0 = VIN+ < VIN                                                  | tor event did n<br>arator Output k<br>= 0 (non-invert<br>N-<br>= 1 (inverted p<br>N- | ot occur<br>bit<br>ed polarity): |                   |                 |                     |                     |  |  |  |

2: After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator Event bit, CEVT (CMxCON<9>), and the Comparator Combined Interrupt Flag, CMPIF (IFS1<2>), **must be cleared** before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

#### CM4CON: OP AMP/COMPARATOR 4 CONTROL REGISTER (CONTINUED) REGISTER 26-3: EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits<sup>(2)</sup> bit 7-6 11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0) 10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0) If CPOL = 1 (inverted polarity): Low-to-high transition of the comparator output. If CPOL = 0 (non-inverted polarity): High-to-low transition of the comparator output. 01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity selected comparator output (while CEVT = 0) If CPOL = 1 (inverted polarity): High-to-low transition of the comparator output. If CPOL = 0 (non-inverted polarity): Low-to-high transition of the comparator output. 00 = Trigger/event/interrupt generation is disabled Unimplemented: Read as '0' bit 5 CREF: Comparator Reference Select bit (VIN+ input)<sup>(1)</sup> bit 4 1 = VIN+ input connects to internal CVREFIN voltage 0 = VIN+ input connects to C4IN1+ pin bit 3-2 Unimplemented: Read as '0' CCH<1:0>: Comparator Channel Select bits<sup>(1)</sup> bit 1-0 11 = VIN- input of comparator connects to OA3/AN6 10 = VIN- input of comparator connects to OA2/AN0 01 = VIN- input of comparator connects to OA1/AN3 00 = VIN- input of comparator connects to C4IN1-Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

2: After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator Event bit, CEVT (CMxCON<9>), and the Comparator Combined Interrupt Flag, CMPIF (IFS1<2>), **must be cleared** before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax             | Description                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|---------|-----------------------------|---------------------------------------------------|---------------|----------------|--------------------------|

| 46                 | MOV                  | MOV     | f,Wn                        | Move f to Wn                                      | 1             | 1              | None                     |

|                    |                      | MOV     | f                           | Move f to f                                       | 1             | 1              | None                     |

|                    |                      | MOV     | f,WREG                      | Move f to WREG                                    | 1             | 1              | None                     |

|                    |                      | MOV     | #lit16,Wn                   | Move 16-bit literal to Wn                         | 1             | 1              | None                     |

|                    |                      | MOV.b   | #lit8,Wn                    | Move 8-bit literal to Wn                          | 1             | 1              | None                     |

|                    |                      | MOV     | Wn,f                        | Move Wn to f                                      | 1             | 1              | None                     |

|                    |                      | MOV     | Wso,Wdo                     | Move Ws to Wd                                     | 1             | 1              | None                     |

|                    |                      | MOV     | WREG, f                     | Move WREG to f                                    | 1             | 1              | None                     |

|                    |                      | MOV.D   | Wns,Wd                      | Move Double from W(ns):W(ns + 1) to Wd            | 1             | 2              | None                     |

|                    |                      | MOV.D   | Ws,Wnd                      | Move Double from Ws to W(nd + 1):W(nd)            | 1             | 2              | None                     |

| 17                 | MOVPAG               | MOVPAG  | #lit10,DSRPAG               | Move 10-bit literal to DSRPAG                     | 1             | 1              | None                     |

|                    |                      | MOVPAG  | #lit9,DSWPAG                | Move 9-bit literal to DSWPAG                      | 1             | 1              | None                     |

|                    |                      | MOVPAG  | #lit8,TBLPAG                | Move 8-bit literal to TBLPAG                      | 1             | 1              | None                     |

|                    |                      | MOVPAGW | Ws, DSRPAG                  | Move Ws<9:0> to DSRPAG                            | 1             | 1              | None                     |

|                    |                      | MOVPAGW | Ws, DSWPAG                  | Move Ws<8:0> to DSWPAG                            | 1             | 1              | None                     |

|                    |                      | MOVPAGW | Ws, TBLPAG                  | Move Ws<7:0> to TBLPAG                            | 1             | 1              | None                     |

| 18                 | MOVSAC               | MOVSAC  | Acc,Wx,Wxd,Wy,Wyd,AWB       | Prefetch and store accumulator                    | 1             | 1              | None                     |

| 19                 | MPY                  | MPY     | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd     | Multiply Wm by Wn to Accumulator                  | 1             | 1              | OA,OB,OAI<br>SA,SB,SAI   |

|                    |                      | MPY     | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd     | Square Wm to Accumulator                          | 1             | 1              | OA,OB,OA<br>SA,SB,SA     |

| 50                 | MPY.N                | MPY.N   | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd     | -(Multiply Wm by Wn) to Accumulator               | 1             | 1              | None                     |

| 51                 | MSC                  | MSC     | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd,AWB | Multiply and Subtract from Accumulator            | 1             | 1              | OA,OB,OA<br>SA,SB,SA     |

| 52                 | MUL                  | MUL.SS  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = signed(Wb) *<br>signed(Ws)       | 1             | 1              | None                     |

|                    |                      | MUL.SS  | Wb,Ws,Acc                   | Accumulator = signed(Wb) * signed(Ws)             | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(Ws)     | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,Ws,Acc                   | Accumulator = signed(Wb) *<br>unsigned(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Acc                | Accumulator = signed(Wb) * unsigned(lit5)         | 1             | 1              | None                     |

|                    |                      | MUL.US  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = unsigned(Wb) *<br>signed(Ws)     | 1             | 1              | None                     |

|                    |                      | MUL.US  | Wb,Ws,Acc                   | Accumulator = unsigned(Wb) *<br>signed(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Acc                | Accumulator = unsigned(Wb) *<br>unsigned(lit5)    | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,Ws,Acc                   | Accumulator = unsigned(Wb) *<br>unsigned(Ws)      | 1             | 1              | None                     |

|                    |                      | MULW.SS | Wb,Ws,Wnd                   | Wnd = signed(Wb) * signed(Ws)                     | 1             | 1              | None                     |

|                    |                      | MULW.SU | Wb,Ws,Wnd                   | Wnd = signed(Wb) * unsigned(Ws)                   | 1             | 1              | None                     |

|                    |                      | MULW.US | Wb,Ws,Wnd                   | Wnd = unsigned(Wb) * signed(Ws)                   | 1             | 1              | None                     |

|                    |                      | MULW.UU | Wb,Ws,Wnd                   | Wnd = unsigned(Wb) * unsigned(Ws)                 | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd                | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(lit5)   | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd                | Wnd = signed(Wb) * unsigned(lit5)                 | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd                | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5) | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd                | Wnd = unsigned(Wb) * unsigned(lit5)               | 1             | 1              | None                     |

|                    |                      | MUL     | f                           | W3:W2 = f * WREG                                  | 1             | 1              | None                     |

| TABLE 31-2: INSTRUCTION SET OVERVIEW (CONTINUED) |

|--------------------------------------------------|

|--------------------------------------------------|

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

# 32.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# 32.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 32.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 32.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

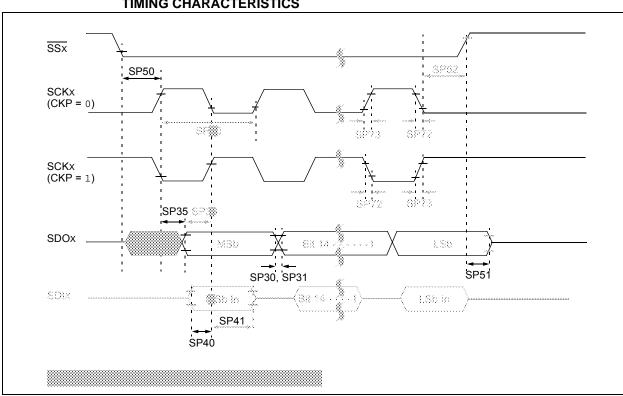

FIGURE 33-21: SPI2 AND SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

#### TABLE 33-53: OP AMP/COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| AC CHARACTERISTICS |        |                | Standard Operating Conditions (see Note 2): 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |      |      |       |            |  |

|--------------------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|

| Param.             | Symbol | Characteristic | Min.                                                                                                                                                                                                              | Тур. | Max. | Units | Conditions |  |

| VR310              | TSET   | Settling Time  |                                                                                                                                                                                                                   | 1    | 10   | μS    | (Note 1)   |  |

**Note 1:** Settling time is measured while CVRR = 1 and the CVR<3:0> bits transition from '0000' to '1111'.

2: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 33-12 for the minimum and maximum BOR values.

#### TABLE 33-54: OP AMP/COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 1): 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |            |       |                      |  |  |

|--------------------|--------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|-------|----------------------|--|--|

| Param<br>No.       | Symbol | Characteristics                                              | Min.                                                                                                                                                                                                                                                                                             | Тур. | Max.       | Units | Conditions           |  |  |

| VRD310             | CVRES  | Resolution                                                   | CVRSRC/24                                                                                                                                                                                                                                                                                        | _    | CVRSRC/32  | LSb   |                      |  |  |

| VRD311             | CVRAA  | Absolute Accuracy of<br>Internal DAC Input to<br>Comparators | —                                                                                                                                                                                                                                                                                                | _    | ±25        | mV    | AVDD = CVRSRC = 3.3V |  |  |

| VRD312             | CVRAA1 | Absolute Accuracy of<br>CVREFXO pins                         |                                                                                                                                                                                                                                                                                                  |      | +75/-25    | mV    | AVDD = CVRSRC = 3.3V |  |  |

| VRD313             | CVRSRC | Input Reference Voltage                                      | 0                                                                                                                                                                                                                                                                                                | _    | AVDD + 0.3 | V     |                      |  |  |

| VRD314             | CVRout | Buffer Output Resistance                                     | _                                                                                                                                                                                                                                                                                                | 1.5k | _          | Ω     |                      |  |  |

| VRD315             | CVCL   | Permissible Capacitive<br>Load (CVREFxO pins)                | —                                                                                                                                                                                                                                                                                                | _    | 25         | pF    |                      |  |  |

| VRD316             | IOCVR  | Permissible Current<br>Output (CVREFxO pins)                 | Ι                                                                                                                                                                                                                                                                                                | —    | 1          | mA    |                      |  |  |

| VRD317             | ION    | Current Consumed<br>When Module is Enabled                   | —                                                                                                                                                                                                                                                                                                |      | 500        | μA    | AVDD = 3.6V          |  |  |

| VRD318             | IOFF   | Current Consumed<br>When Module is<br>Disabled               | —                                                                                                                                                                                                                                                                                                | _    | 1          | nA    | AVDD = 3.6V          |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 33-12 for the minimum and maximum BOR values.

#### 35.1 Package Marking Information (Continued)

64-Lead TQFP (10x10x1 mm)

Example

100-Lead TQFP (12x12x1 mm)

100-Lead TQFP (14x14x1 mm)

121-Lead TFBGA (10x10x1.1 mm)

Example

Example

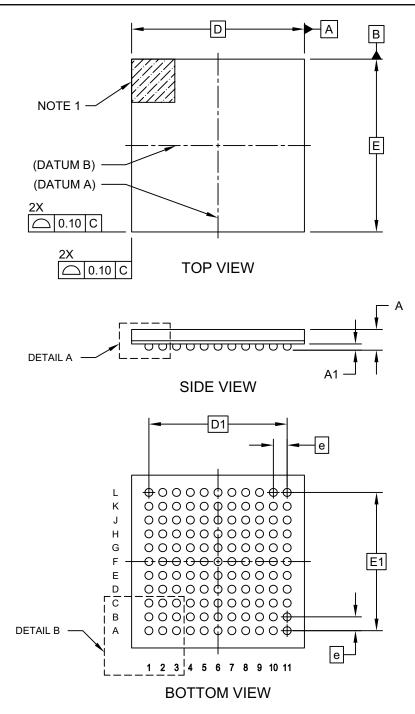

# 121-Ball Plastic Thin Profile Fine Pitch Ball Grid Array (BG) - 10x10x1.10 mm Body [TFBGA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-148 Rev F Sheet 1 of 2