Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

E·XE

| 2 0 0 0 0 0                |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | -                                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | -                                                                                |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

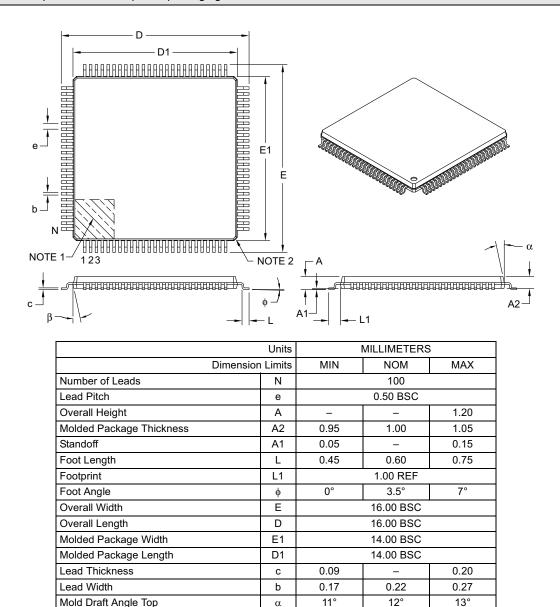

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gm710-h-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXXGM3XX/6XX/7XX

| - U:<br>N-0 R/A<br>TB SAT<br>C = Cl<br>W = W<br>'1' = B<br>Variable Exception<br>ked exception p<br>blemented: Ref<br>0>: DSP Multip<br>Reserved                            | on proces<br>processir                                                                                                                                                                                           | it<br>cessing Later<br>ssing latency                                                                                                                                                                                                                                                                                                                                           | '0' = Bit is cle<br>ncy Control bit<br>is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R-0<br>DL1<br>R/W-0<br>RND<br>d as '0'<br>x = Bit is unkn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R-0<br>DL0<br>bit<br>R/W-0<br>IF<br>bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V-0 R/A<br>TB SAT<br>C = Cl<br>W = W<br>'1' = B<br>Variable Exception<br>riable exception<br>ked exception p<br><b>Demented:</b> Re<br><b>0&gt;:</b> DSP Multip<br>Reserved | W-1<br>TDW<br>learable I<br>Vritable b<br>Bit is set<br>otion Proces<br>processir                                                                                                                                | R/W-0<br>ACCSAT<br>bit<br>it                                                                                                                                                                                                                                                                                                                                                   | R/C-0<br>IPL3 <sup>(2)</sup><br>U = Unimpler<br>'0' = Bit is cle<br>ncy Control bit<br>is enabled                                                                                                                                                                                                                                                                                                                                                                                                 | R-0<br>SFA<br>mented bit, read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0<br>RND<br>d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0<br>IF<br>bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TB SAT<br>C = Cl<br>W = W<br>'1' = B<br>Variable Excep<br>iriable exception<br>ked exception p<br>blemented: Re<br>0>: DSP Multip<br>Reserved                               | Iearable I<br>Vritable b<br>Bit is set<br>otion Proces<br>processir                                                                                                                                              | ACCSAT<br>bit<br>it<br>cessing Later<br>ssing latency                                                                                                                                                                                                                                                                                                                          | U = Unimpler<br>'0' = Bit is cle<br>ncy Control bit<br>is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                 | SFA<br>mented bit, read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0<br>IF<br>bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TB SAT<br>C = Cl<br>W = W<br>'1' = B<br>Variable Excep<br>iriable exception<br>ked exception p<br>blemented: Re<br>0>: DSP Multip<br>Reserved                               | Iearable I<br>Vritable b<br>Bit is set<br>otion Proces<br>processir                                                                                                                                              | ACCSAT<br>bit<br>it<br>cessing Later<br>ssing latency                                                                                                                                                                                                                                                                                                                          | U = Unimpler<br>'0' = Bit is cle<br>ncy Control bit<br>is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                 | SFA<br>mented bit, read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IF<br>bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| C = Cl<br>W = W<br>'1' = B<br>Variable Exception<br>riable exception<br>ked exception p<br>blemented: Re<br>0>: DSP Multip<br>Reserved                                      | learable I<br>Vritable b<br>Bit is set<br>otion Proces<br>processir                                                                                                                                              | bit<br>it<br>cessing Later<br>ssing latency                                                                                                                                                                                                                                                                                                                                    | U = Unimpler<br>'0' = Bit is cle<br>ncy Control bit<br>is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                 | mented bit, read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| W = W<br>'1' = B<br>Variable Exception<br>variable exception<br>ked exception p<br>blemented: Ref<br>0>: DSP Multip<br>Reserved                                             | Vritable b<br>Bit is set<br>otion Proc<br>on proces<br>processir                                                                                                                                                 | it<br>cessing Later<br>ssing latency                                                                                                                                                                                                                                                                                                                                           | '0' = Bit is cle<br>ncy Control bit<br>is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| W = W<br>'1' = B<br>Variable Exception<br>variable exception<br>ked exception p<br>blemented: Ref<br>0>: DSP Multip<br>Reserved                                             | Vritable b<br>Bit is set<br>otion Proc<br>on proces<br>processir                                                                                                                                                 | it<br>cessing Later<br>ssing latency                                                                                                                                                                                                                                                                                                                                           | '0' = Bit is cle<br>ncy Control bit<br>is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | own                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| '1' = B<br>Variable Exception<br>variable exception<br>ved exception p<br>blemented: Re<br>0>: DSP Multip<br>Reserved                                                       | Bit is set<br>otion Proc<br>on proces<br>processir                                                                                                                                                               | cessing Later<br>ssing latency                                                                                                                                                                                                                                                                                                                                                 | '0' = Bit is cle<br>ncy Control bit<br>is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | own                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Variable Excep<br>iriable exceptio<br>ked exception p<br><b>blemented:</b> Re<br><b>0&gt;:</b> DSP Multip<br>Reserved                                                       | otion Proc<br>on proces<br>processir                                                                                                                                                                             | sing latency                                                                                                                                                                                                                                                                                                                                                                   | ncy Control bit<br>is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | x = Bit is unkn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | own                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| riable exceptio<br>ked exception p<br>blemented: Re<br>0>: DSP Multip<br>Reserved                                                                                           | on proces<br>processir                                                                                                                                                                                           | sing latency                                                                                                                                                                                                                                                                                                                                                                   | is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <b>0&gt;:</b> DSP Multi <sub>l</sub><br>Reserved                                                                                                                            | ead as '0'                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                | enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Reserved                                                                                                                                                                    |                                                                                                                                                                                                                  | ,                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                             | ply Unsig                                                                                                                                                                                                        | ned/Signed                                                                                                                                                                                                                                                                                                                                                                     | Control bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| )SP engine mu<br>)SP engine mu<br>)SP engine mu                                                                                                                             | ultiplies a                                                                                                                                                                                                      | re unsigned                                                                                                                                                                                                                                                                                                                                                                    | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Early DO Loop <sup>-</sup>                                                                                                                                                  | Terminati                                                                                                                                                                                                        | on Control b                                                                                                                                                                                                                                                                                                                                                                   | it <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| rminates exect<br>o effect                                                                                                                                                  | uting DO I                                                                                                                                                                                                       | loop at end c                                                                                                                                                                                                                                                                                                                                                                  | of current loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | iteration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0>: DO Loop N                                                                                                                                                               | lesting Le                                                                                                                                                                                                       | evel Status b                                                                                                                                                                                                                                                                                                                                                                  | its                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7 DO loops are                                                                                                                                                              | e active                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                             |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1 DO loop is ac                                                                                                                                                             |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -                                                                                                                                                                           |                                                                                                                                                                                                                  | ble bit                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| cumulator A sa                                                                                                                                                              | aturation                                                                                                                                                                                                        | is enabled                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                             |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                             |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ata Space write                                                                                                                                                             | saturatio                                                                                                                                                                                                        | on is enabled                                                                                                                                                                                                                                                                                                                                                                  | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -                                                                                                                                                                           |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |