Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 30x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm306-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "CPU" (DS70359), which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word, with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle, effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

#### 3.1 Registers

The dsPIC33EPXXXGM3XX/6XX/7XX devices have sixteen 16-bit Working registers in the programmer's model. Each of the Working registers can act as a data, address or address offset register. The 16th Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

#### 3.2 Instruction Set

The device instruction set has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

## 3.3 Data Space Addressing

The Base Data Space can be addressed as 4K words or 8 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operate solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EP devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Space boundary is device-specific.

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space at any 16K program word boundary. The program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Data Space Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. Refer to "Data Memory" (DS70595) and "Program Memory" (DS70613) in the "dsPIC33/ PIC24 Family Reference Manual" for more details on EDS, PSV and table accesses.

On dsPIC33EP devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

## 3.4 Addressing Modes

The CPU supports these addressing modes:

- · Inherent (no operand)

- Relative

- Literal

- Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

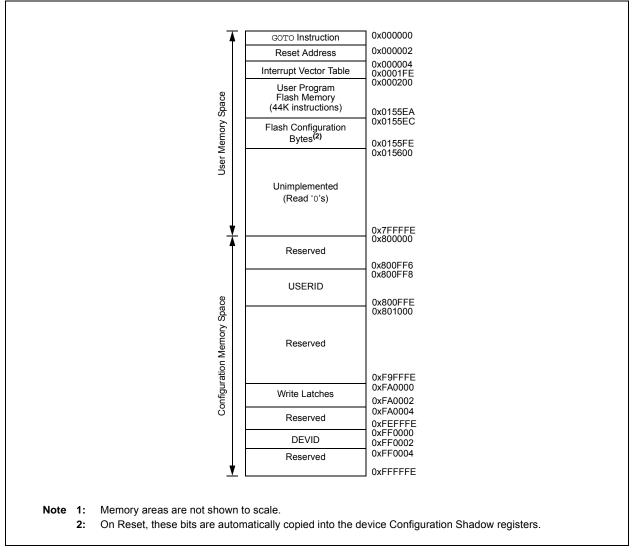

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/ 7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Program Memory" (DS70613), which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGM3XX/6XX/7XX family architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

#### 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXXGM3XX/6XX/7XX devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.7 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-3.

#### FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP128GM3XX/6XX/7XX DEVICES<sup>(1)</sup>

#### TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXGM3XX DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8  | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-----------------------|--------|--------|-------|--------|--------|--------|--------|--------|--------|---------------|

| PMD1        | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD                 | DCIMD  | I2C1MD | U2MD  | U1MD   | SPI2MD | SPI1MD | —      | —      | AD1MD  | 0000          |

| PMD2        | 0762  | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD                 | IC1MD  | OC8MD  | OC7MD | OC6MD  | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3        | 0764  | T9MD   | T8MD   | T7MD   | T6MD   | _      | CMPMD  | RTCCMD <sup>(1)</sup> | PMPMD  | CRCMD  | _     | QEI2MD | _      | U3MD   | _      | I2C2MD | ADC2MD | 0000          |

| PMD4        | 0766  | _      | _      | _      | _      | _      | _      | _                     | _      | _      | _     | U4MD   | _      | REFOMD | CTMUMD | _      | _      | 0000          |

| PMD6        | 076A  | _      | _      | PWM6MD | PWM5MD | PWM4MD | PWM3MD | PWM2MD                | PWM1MD | _      | _     | _      | _      | _      | _      | _      | SPI3MD | 0000          |

|             |       |        |        |        |        |        |        |                       |        |        |       |        | DMA0MD |        |        |        |        |               |

| PMD7        | 076C  |        |        |        |        |        |        |                       |        |        |       |        | DMA1MD | PTGMD  |        |        |        |               |

| PMD7        | 0760  | _      | _      | _      | _      | _      | _      | _                     | _      | _      | _     | _      | DMA2MD | PIGMD  | _      | _      | _      | 0000          |

|             |       |        |        |        |        |        |        |                       |        |        |       |        | DMA3MD |        |        |        |        |               |

Legend:

— = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1:

The RTCCMD bit is not available on 44-pin devices.

| TABLE 7-1: INTERRUPT VECTOR DETAILS |

|-------------------------------------|

|-------------------------------------|

|                                          | Vector | IRQ        |                  | Inte     | Interrupt Bit Location |             |  |  |

|------------------------------------------|--------|------------|------------------|----------|------------------------|-------------|--|--|

| Interrupt Source                         | #      | #          | IVT Address      | Flag     | Enable                 | Priority    |  |  |

|                                          | Highe  | est Natura | I Order Priority |          |                        |             |  |  |

| INT0 – External Interrupt 0              | 8      | 0          | 0x000014         | IFS0<0>  | IEC0<0>                | IPC0<2:0>   |  |  |

| IC1 – Input Capture 1                    | 9      | 1          | 0x000016         | IFS0<1>  | IEC0<1>                | IPC0<6:4>   |  |  |

| OC1 – Output Compare 1                   | 10     | 2          | 0x000018         | IFS0<2>  | IEC0<2>                | IPC0<10:8>  |  |  |

| T1 – Timer1                              | 11     | 3          | 0x00001A         | IFS0<3>  | IEC0<3>                | IPC0<14:12> |  |  |

| DMA0 – DMA Channel 0                     | 12     | 4          | 0x00001C         | IFS0<4>  | IEC0<4>                | IPC1<2:0>   |  |  |

| IC2 – Input Capture 2                    | 13     | 5          | 0x00001E         | IFS0<5>  | IEC0<5>                | IPC1<6:4>   |  |  |

| OC2 – Output Compare 2                   | 14     | 6          | 0x000020         | IFS0<6>  | IEC0<6>                | IPC1<10:8>  |  |  |

| T2 – Timer2                              | 15     | 7          | 0x000022         | IFS0<7>  | IEC0<7>                | IPC1<14:12> |  |  |

| T3 – Timer3                              | 16     | 8          | 0x000024         | IFS0<8>  | IEC0<8>                | IPC2<2:0>   |  |  |

| SPI1E – SPI1 Error                       | 17     | 9          | 0x000026         | IFS0<9>  | IEC0<9>                | IPC2<6:4>   |  |  |

| SPI1 – SPI1 Transfer Done                | 18     | 10         | 0x000028         | IFS0<10> | IEC0<10>               | IPC2<10:8>  |  |  |

| U1RX – UART1 Receiver                    | 19     | 11         | 0x00002A         | IFS0<11> | IEC0<11>               | IPC2<14:12> |  |  |

| U1TX – UART1 Transmitter                 | 20     | 12         | 0x00002C         | IFS0<12> | IEC0<12>               | IPC3<2:0>   |  |  |

| AD1 – ADC1 Convert Done                  | 21     | 13         | 0x00002E         | IFS0<13> | IEC0<13>               | IPC3<6:4>   |  |  |

| DMA1 – DMA Channel 1                     | 22     | 14         | 0x000030         | IFS0<14> | IEC0<14>               | IPC3<10:8>  |  |  |

| Reserved                                 | 23     | 15         | 0x000032         | _        | _                      |             |  |  |

| SI2C1 – I2C1 Slave Event                 | 24     | 16         | 0x000034         | IFS1<0>  | IEC1<0>                | IPC4<2:0>   |  |  |

| MI2C1 – I2C1 Master Event                | 25     | 17         | 0x000036         | IFS1<1>  | IEC1<1>                | IPC4<6:4>   |  |  |

| CMP1 – Comparator Combined Event         | 26     | 18         | 0x000038         | IFS1<2>  | IEC1<2>                | IPC4<10:8>  |  |  |

| CN – Input Change Interrupt              | 27     | 19         | 0x00003A         | IFS1<3>  | IEC1<3>                | IPC4<14:12> |  |  |

| INT1 – External Interrupt 1              | 28     | 20         | 0x00003C         | IFS1<4>  | IEC1<4>                | IPC5<2:0>   |  |  |

| AD2 – ADC2 Convert Done                  | 29     | 21         | 0x00003E         | IFS1<5>  | IEC1<5>                | IPC5<6:4>   |  |  |

| IC7 – Input Capture 7                    | 30     | 22         | 0x000040         | IFS1<6>  | IEC1<6>                | IPC5<10:8>  |  |  |

| IC8 – Input Capture 8                    | 31     | 23         | 0x000042         | IFS1<7>  | IEC1<7>                | IPC5<14:12> |  |  |

| DMA2 – DMA Channel 2                     | 32     | 24         | 0x000044         | IFS1<8>  | IEC1<8>                | IPC6<2:0>   |  |  |

| OC3 – Output Compare 3                   | 33     | 25         | 0x000046         | IFS1<9>  | IEC1<9>                | IPC6<6:4>   |  |  |

| OC4 – Output Compare 4                   | 34     | 26         | 0x000048         | IFS1<10> | IEC1<10>               | IPC6<10:8>  |  |  |

| T4 – Timer4                              | 35     | 27         | 0x00004A         | IFS1<11> | IEC1<11>               | IPC6<14:12> |  |  |

| T5 – Timer5                              | 36     | 28         | 0x00004C         | IFS1<12> | IEC1<12>               | IPC7<2:0>   |  |  |

| INT2 – External Interrupt 2              | 37     | 29         | 0x00004E         | IFS1<13> | IEC1<13>               | IPC7<6:4>   |  |  |

| U2RX – UART2 Receiver                    | 38     | 30         | 0x000050         | IFS1<14> | IEC1<14>               | IPC7<10:8>  |  |  |

| U2TX – UART2 Transmitter                 | 39     | 31         | 0x000052         | IFS1<15> | IEC1<15>               | IPC7<14:12> |  |  |

| SPI2E – SPI2 Error                       | 40     | 32         | 0x000054         | IFS2<0>  | IEC2<0>                | IPC8<2:0>   |  |  |

| SPI2 – SPI2 Transfer Done                | 41     | 33         | 0x000056         | IFS2<1>  | IEC2<1>                | IPC8<6:4>   |  |  |

| C1RX – CAN1 RX Data Ready <sup>(1)</sup> | 42     | 34         | 0x000058         | IFS2<2>  | IEC2<2>                | IPC8<10:8>  |  |  |

| C1 – CAN1 Event <sup>(1)</sup>           | 43     | 35         | 0x00005A         | IFS2<3>  | IEC2<3>                | IPC8<14:12> |  |  |

| DMA3 – DMA Channel 3                     | 44     | 36         | 0x00005C         | IFS2<4>  | IEC2<4>                | IPC9<2:0>   |  |  |

| IC3 – Input Capture 3                    | 45     | 37         | 0x00005E         | IFS2<5>  | IEC2<5>                | IPC9<6:4>   |  |  |

| IC4 – Input Capture 4                    | 46     | 38         | 0x000060         | IFS2<6>  | IEC2<6>                | IPC9<10:8>  |  |  |

| IC5 – Input Capture 5                    | 47     | 39         | 0x000062         | IFS2<7>  | IEC2<7>                | IPC9<14:12> |  |  |

| IC6 – Input Capture 6                    | 48     | 40         | 0x000064         | IFS2<8>  | IEC2<8>                | IPC10<2:0>  |  |  |

Note 1: This interrupt source is available on dsPIC33EPXXXGM6XX/7XX devices only.

2: This interrupt source is not available on 44-pin devices.

#### TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

|                                                    | Vector | IRQ   |                   | Inte     | errupt Bit L | ocation      |

|----------------------------------------------------|--------|-------|-------------------|----------|--------------|--------------|

| Interrupt Source                                   | #      | #     | IVT Address       | Flag     | Enable       | Priority     |

| OC5 – Output Compare 5                             | 49     | 41    | 0x000066          | IFS2<9>  | IEC2<9>      | IPC10<6:4>   |

| OC6 – Output Compare 6                             | 50     | 42    | 0x000068          | IFS2<10> | IEC2<10>     | IPC10<10:8>  |

| OC7 – Output Compare 7                             | 51     | 43    | 0x00006A          | IFS2<11> | IEC2<11>     | IPC10<14:12> |

| OC8 – Output Compare 8                             | 52     | 44    | 0x00006C          | IFS2<12> | IEC2<12>     | IPC11<2:0>   |

| PMP – Parallel Master Port <sup>(2)</sup>          | 53     | 45    | 0x00006E          | IFS2<13> | IEC2<13>     | IPC11<6:4>   |

| Reserved                                           | 54     | 46    | 0x000070          | _        | _            | _            |

| T6 – Timer6                                        | 55     | 47    | 0x000072          | IFS2<15> | IEC2<15>     | IPC11<14:12> |

| T7 – Timer7                                        | 56     | 48    | 0x000074          | IFS3<0>  | IEC3<0>      | IPC12<2:0>   |

| SI2C2 – I2C2 Slave Event                           | 57     | 49    | 0x000076          | IFS3<1>  | IEC3<1>      | IPC12<6:4>   |

| MI2C2 – I2C2 Master Event                          | 58     | 50    | 0x000078          | IFS3<2>  | IEC3<2>      | IPC12<10:8>  |

| T8 – Timer8                                        | 59     | 51    | 0x00007A          | IFS3<3>  | IEC3<3>      | IPC12<14:12> |

| T9 – Timer9                                        | 60     | 52    | 0x00007C          | IFS3<4>  | IEC3<4>      | IPC13<2:0>   |

| INT3 – External Interrupt 3                        | 61     | 53    | 0x00007E          | IFS3<5>  | IEC3<5>      | IPC13<6:4>   |

| INT4 – External Interrupt 4                        | 62     | 54    | 0x000080          | IFS3<6>  | IEC3<6>      | IPC13<10:8>  |

| C2RX – CAN2 RX Data Ready <sup>(1)</sup>           | 63     | 55    | 0x000082          | IFS3<7>  | IEC3<7>      | IPC13<14:12> |

| C2 – CAN2 Event <sup>(1)</sup>                     | 64     | 56    | 0x000084          | IFS3<8>  | IEC3<8>      | IPC14<2:0>   |

| PSEM – PCPWM Primary Event                         | 65     | 57    | 0x000086          | IFS3<9>  | IEC3<9>      | IPC14<6:4>   |

| QEI1 – QEI1 Position Counter Compare               | 66     | 58    | 0x000088          | IFS3<10> | IEC3<10>     | IPC14<10:8>  |

| DCIE – DCI Fault Interrupt                         | 67     | 59    | 0x00008A          | IFS3<11> | IEC3<11>     | IPC14<14:12> |

| DCI – DCI Transfer Done                            | 68     | 60    | 0x00008C          | IFS3<12> | IEC3<12>     | IPC15<2:0>   |

| Reserved                                           | 69     | 61    | 0x00008E          | —        | —            | _            |

| RTCC – Real-Time Clock and Calendar <sup>(2)</sup> | 70     | 62    | 0x000090          | IFS3<14> | IEC3<14>     | IPC15<10:8>  |

| Reserved                                           | 71-72  | 63-64 | 0x000092-0x000094 | —        | _            | _            |

| U1E – UART1 Error Interrupt                        | 73     | 65    | 0x000096          | IFS4<1>  | IEC4<1>      | IPC16<6:4>   |

| U2E – UART2 Error Interrupt                        | 74     | 66    | 0x000098          | IFS4<2>  | IEC4<2>      | IPC16<10:8>  |

| CRC – CRC Generator Interrupt                      | 75     | 67    | 0x00009A          | IFS4<3>  | IEC4<3>      | IPC16<14:12> |

| Reserved                                           | 76-77  | 68-69 | 0x00009C-0x00009E | —        | —            | _            |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>         | 78     | 70    | 0x0000A0          | IFS4<6>  | IEC4<6>      | IPC17<10:8>  |

| C2TX – CAN2 TX Data Request <sup>(1)</sup>         | 79     | 71    | 0x0000A2          | IFS4<7>  | IEC4<7>      | IPC17<14:12> |

| Reserved                                           | 80     | 72    | 0x0000A4          | —        | —            | -            |

| PSESM – PCPWM Secondary Event                      | 81     | 73    | 0x0000A6          | IFS4<9>  | IEC4<9>      | IPC18<6:4>   |

| Reserved                                           | 82     | 74    | 0x0000A8          | —        | —            | -            |

| QEI2 – QEI2 Position Counter Compare               | 83     | 75    | 0x0000AA          | IFS4<11> | IEC4<11>     | IPC18<14:12> |

| Reserved                                           | 84     | 76    | 0x0000AC          | —        | —            | -            |

| CTMU – CTMU Interrupt                              | 85     | 77    | 0x0000AE          | IFS4<13> | IEC4<13>     | IPC19<6:4>   |

| Reserved                                           | 86-88  | 78-80 | 0x0000B0-0x0000B4 | —        | —            | -            |

| U3E – UART3 Error Interrupt                        | 89     | 81    | 0x0000B6          | IFS5<1>  | IEC5<1>      | IPC20<6:4>   |

| U3RX – UART3 Receiver                              | 90     | 82    | 0x0000B8          | IFS5<2>  | IEC5<2>      | IPC20<10:8>  |

| U3TX – UART3 Transmitter                           | 91     | 83    | 0x0000BA          | IFS5<3>  | IEC5<3>      | IPC20<14:12> |

| Reserved                                           | 92-94  | 84-86 | 0x0000BC-0x0000C0 |          |              | —            |

| U4E – UART4 Error Interrupt                        | 95     | 87    | 0x0000C2          | IFS5<7>  | IEC5<7>      | IPC21<14:12> |

| U4RX – UART4 Receiver                              | 96     | 88    | 0x0000C4          | IFS5<8>  | IEC5<8>      | IPC22<2:0>   |

| U4TX – UART4 Transmitter                           | 97     | 89    | 0x0000C6          | IFS5<9>  | IEC5<9>      | IPC22<6:4>   |

Note 1: This interrupt source is available on dsPIC33EPXXXGM6XX/7XX devices only.

2: This interrupt source is not available on 44-pin devices.

## **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

| bit 5 | LOCK: PLL Lock Status bit (read-only)                                                                                                                                                     |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that PLL is in lock or PLL start-up timer is satisfied</li> <li>0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled</li> </ul> |

| bit 4 | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 3 | <b>CF:</b> Clock Fail Detect bit (read/clear by application) <sup>(5)</sup>                                                                                                               |

|       | <ul><li>1 = FSCM has detected clock failure</li><li>0 = FSCM has not detected clock failure</li></ul>                                                                                     |

| bit 2 | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 1 | LPOSCEN: Secondary (LP) Oscillator Enable bit                                                                                                                                             |

|       | <ul><li>1 = Enables Secondary Oscillator (SOSC)</li><li>0 = Disables Secondary Oscillator</li></ul>                                                                                       |

| bit 0 | OSWEN: Oscillator Switch Enable bit                                                                                                                                                       |

|       | <ul> <li>1 = Requests oscillator switch to selection specified by the NOSC&lt;2:0&gt; bits</li> <li>0 = Oscillator switch is complete</li> </ul>                                          |

- **Note 1:** Writes to this register require an unlock sequence. Refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Oscillator"** (DS70580), available from the Microchip web site for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This register resets only on a Power-on Reset (POR).

- 4: Secondary Oscillator (SOSC) selection is valid on 64-pin and 100-pin devices, and defaults to FRC/N on 44-pin devices.

- 5: Only '0' should be written to the CF bit in order to clear it. If a '1' is written to CF, it will have the same effect as a detected clock failure, including an oscillator fail trap.

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

| bit 4 | SPI2MD: SPI2 Module Disable bit                     |

|-------|-----------------------------------------------------|

|       | 1 = SPI2 module is disabled                         |

|       | 0 = SPI2 module is enabled                          |

| bit 3 | SPI1MD: SPI1 Module Disable bit                     |

|       | 1 = SPI1 module is disabled                         |

|       | 0 = SPI1 module is enabled                          |

| bit 2 | C2MD: CAN2 Module Disable bit <sup>(1)</sup>        |

|       | 1 = CAN2 module is disabled                         |

|       | 0 = CAN2 module is enabled                          |

| bit 1 | <b>C1MD:</b> CAN1 Module Disable bit <sup>(1)</sup> |

|       | 1 = CAN1 module is disabled                         |

|       | 0 = CAN1 module is enabled                          |

| bit 0 | AD1MD: ADC1 Module Disable bit                      |

|       | 1 = ADC1 module is disabled                         |

|       | 0 = ADC1 module is enabled                          |

|       |                                                     |

Note 1: These bits are available on dsPIC33EPXXXGM6XX/7XX devices only.

#### REGISTER 11-30: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0           | U-0       | R/W-0            | R/W-0 | R/W-0                               | R/W-0           | R/W-0    | R/W-0 |

|---------------|-----------|------------------|-------|-------------------------------------|-----------------|----------|-------|

| _             | _         |                  |       | RP35                                | R<5:0>          |          |       |

| bit 15        |           |                  |       |                                     |                 |          | bit 8 |

|               |           |                  |       |                                     |                 |          |       |

| U-0           | U-0       | R/W-0            | R/W-0 | R/W-0                               | R/W-0           | R/W-0    | R/W-0 |

| —             | —         |                  |       | RP20                                | R<5:0>          |          |       |

| bit 7         |           |                  |       |                                     |                 |          | bit 0 |

|               |           |                  |       |                                     |                 |          |       |

| Legend:       |           |                  |       |                                     |                 |          |       |

| R = Readable  | e bit     | W = Writable     | bit   | U = Unimplen                        | nented bit, rea | d as '0' |       |

| -n = Value at | POR       | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unk |                 |          | nown  |

|               |           |                  |       |                                     |                 |          |       |

| bit 15-14     | Unimpleme | nted: Read as '  | 0'    |                                     |                 |          |       |

| bit 13-8      |           | >: Peripheral Ou | •     | •                                   | RP35 Output     | Pin bits |       |

| 2.1.1.0.0 | (see Table 11-3 for peripheral function numbers)                                                                                         |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP20R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-31: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0                                | U-0 | R/W-0        | R/W-0 | R/W-0                                   | R/W-0          | R/W-0     | R/W-0 |  |  |

|------------------------------------|-----|--------------|-------|-----------------------------------------|----------------|-----------|-------|--|--|

| _                                  | —   |              |       | RP37F                                   | २<5:0>         |           |       |  |  |

| bit 15                             |     |              |       |                                         |                |           | bit 8 |  |  |

| U-0                                | U-0 | R/W-0        | R/W-0 | R/W-0                                   | R/W-0          | R/W-0     | R/W-0 |  |  |

|                                    | —   |              |       | RP36F                                   | R<5:0>         |           |       |  |  |

| bit 7                              |     |              |       |                                         |                |           | bit 0 |  |  |

| Legend:                            |     |              |       |                                         |                |           |       |  |  |

| R = Readable                       | bit | W = Writable | bit   | U = Unimplem                            | ented bit, rea | ad as '0' |       |  |  |

| -n = Value at POR '1' = Bit is set |     |              |       | '0' = Bit is cleared x = Bit is unknown |                |           |       |  |  |

bit 13-8 **RP37R<5:0>:** Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP36R<5:0>:** Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-3 for peripheral function numbers)

#### REGISTER 11-36: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| U-0           | U-0                                                                        | R/W-0                                | R/W-0 | R/W-0                   | R/W-0            | R/W-0           | R/W-0 |  |  |

|---------------|----------------------------------------------------------------------------|--------------------------------------|-------|-------------------------|------------------|-----------------|-------|--|--|

| _             | —                                                                          |                                      |       | RP55                    | R<5:0>           |                 |       |  |  |

| bit 15        |                                                                            |                                      |       |                         |                  |                 | bit 8 |  |  |

| U-0           | U-0                                                                        | R/W-0                                |       | D/M/ 0                  | D/M/ 0           |                 | DAM 0 |  |  |

| 0-0           | 0-0                                                                        | R/W-U                                | R/W-0 | R/W-0                   | R/W-0            | R/W-0           | R/W-0 |  |  |

|               |                                                                            |                                      |       | RP54                    | R<5:0>           |                 |       |  |  |

| bit 7         |                                                                            |                                      |       |                         |                  |                 | bit 0 |  |  |

|               |                                                                            |                                      |       |                         |                  |                 |       |  |  |

| Legend:       |                                                                            |                                      |       |                         |                  |                 |       |  |  |

| R = Readabl   | le bit                                                                     | W = Writable                         | bit   | U = Unimplen            | nented bit, read | d as '0'        |       |  |  |

| -n = Value at | t POR                                                                      | '1' = Bit is set                     |       | '0' = Bit is clea       | ared             | x = Bit is unkr | nown  |  |  |

| bit 15-14     | Unimpleme                                                                  | nted: Read as '                      | 0'    |                         |                  |                 |       |  |  |

| bit 13-8      |                                                                            | Peripheral Out<br>1-3 for peripheral | •     | n is Assigned to mbers) | RP55 Output I    | Pin bits        |       |  |  |

| bit 7-6       | Unimpleme                                                                  | nted: Read as '                      | 0'    |                         |                  |                 |       |  |  |

| bit 5-0       | RP54R<5:0>: Peripheral Output Function is Assigned to RP54 Output Pin bits |                                      |       |                         |                  |                 |       |  |  |

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-37: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0          | U-0        | R/W-0            | R/W-0          | R/W-0                                   | R/W-0         | R/W-0    | R/W-0 |  |  |

|--------------|------------|------------------|----------------|-----------------------------------------|---------------|----------|-------|--|--|

| _            | —          |                  |                | RP57R<                                  | <5:0>         |          |       |  |  |

| bit 15       |            |                  |                |                                         |               |          | bit 8 |  |  |

|              |            |                  |                |                                         |               |          |       |  |  |

| U-0          | U-0        | R/W-0            | R/W-0          | R/W-0                                   | R/W-0         | R/W-0    | R/W-0 |  |  |

| —            | —          |                  |                | RP56R<                                  | <5:0>         |          |       |  |  |

| bit 7        |            |                  |                |                                         |               |          | bit 0 |  |  |

|              |            |                  |                |                                         |               |          |       |  |  |

| Legend:      |            |                  |                |                                         |               |          |       |  |  |

| R = Readab   | le bit     | W = Writable     | bit            | U = Unimpleme                           | nted bit, rea | d as '0' |       |  |  |

| -n = Value a | t POR      | '1' = Bit is set |                | '0' = Bit is cleared x = Bit is unknown |               |          |       |  |  |

|              |            |                  |                |                                         |               |          |       |  |  |

| bit 15-14    | Unimplemen | ted: Read as '   | 0'             |                                         |               |          |       |  |  |

| bit 13-8     | RP57R<5:0> | • Peripheral Ou  | Itout Function | n is Assigned to RI                     | 257 Output    | Pin bits |       |  |  |

bit 13-8 **RP57R<5:0>:** Peripheral Output Function is Assigned to RP57 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP56R<5:0>:** Peripheral Output Function is Assigned to RP56 Output Pin bits (see Table 11-3 for peripheral function numbers)

## 13.1 Timer Control Registers

## REGISTER 13-1: TxCON (T2CON, T4CON, T6CON AND T8CON) CONTROL REGISTER

| R/W-0            | U-0                                                            | R/W-0             | U-0            | U-0              | U-0             | U-0                | U-0   |  |  |

|------------------|----------------------------------------------------------------|-------------------|----------------|------------------|-----------------|--------------------|-------|--|--|

| TON              |                                                                | TSIDL             | —              | —                | _               | —                  |       |  |  |

| bit 15           |                                                                |                   |                |                  |                 |                    | bit 8 |  |  |

|                  |                                                                |                   |                |                  |                 |                    |       |  |  |

| U-0              | R/W-0                                                          | R/W-0             | R/W-0          | R/W-0            | U-0             | R/W-0              | U-0   |  |  |

|                  | TGATE                                                          | TCKPS1            | TCKPS0         | T32              | _               | TCS <sup>(1)</sup> |       |  |  |

| bit 7            |                                                                |                   |                |                  |                 |                    | bit 0 |  |  |

|                  |                                                                |                   |                |                  |                 |                    |       |  |  |

| Legend:          |                                                                |                   |                |                  |                 |                    |       |  |  |

| R = Readable b   |                                                                | W = Writable      |                | •                | nented bit, rea |                    |       |  |  |

| -n = Value at P0 | DR                                                             | '1' = Bit is set  |                | '0' = Bit is cle | ared            | x = Bit is unkn    | own   |  |  |

|                  |                                                                | <b>a</b>          |                |                  |                 |                    |       |  |  |

|                  | TON: Timerx                                                    |                   |                |                  |                 |                    |       |  |  |

|                  | When T32 = 1<br>1 = Starts 32-                                 |                   |                |                  |                 |                    |       |  |  |

|                  | 0 = Stops 32-                                                  |                   |                |                  |                 |                    |       |  |  |

|                  | When T32 = 0                                                   |                   |                |                  |                 |                    |       |  |  |

|                  | 1 = Starts 16-                                                 |                   |                |                  |                 |                    |       |  |  |

| bit 14           | 0 = Stops 16-                                                  | ted: Read as '    | ٦ <sup>3</sup> |                  |                 |                    |       |  |  |

|                  | -                                                              | x Stop in Idle M  |                |                  |                 |                    |       |  |  |

| bit 15           |                                                                | ues module op     |                | device enters l  | dle mode        |                    |       |  |  |

|                  |                                                                | s module opera    |                |                  |                 |                    |       |  |  |

| bit 12-7         | Unimplemented: Read as '0'                                     |                   |                |                  |                 |                    |       |  |  |

| bit 6            | TGATE: Timerx Gated Time Accumulation Enable bit               |                   |                |                  |                 |                    |       |  |  |

|                  | When TCS = $1$ :                                               |                   |                |                  |                 |                    |       |  |  |

|                  | This bit is igno                                               |                   |                |                  |                 |                    |       |  |  |

|                  | <u>When TCS = 0:</u><br>1 = Gated time accumulation is enabled |                   |                |                  |                 |                    |       |  |  |

|                  |                                                                | e accumulation    |                |                  |                 |                    |       |  |  |

| bit 5-4          | TCKPS<1:0>                                                     | : Timerx Input    | Clock Prescal  | e Select bits    |                 |                    |       |  |  |

|                  | 11 = 1:256                                                     |                   |                |                  |                 |                    |       |  |  |

|                  | 10 = 1:64<br>01 = 1:8                                          |                   |                |                  |                 |                    |       |  |  |

|                  | 01 = 1.0<br>00 = 1.1                                           |                   |                |                  |                 |                    |       |  |  |

| bit 3            | <b>T32:</b> 32-Bit Timer Mode Select bit                       |                   |                |                  |                 |                    |       |  |  |

|                  | 1 = Timerx an                                                  | nd Timery form    | a single 32-bi | t timer          |                 |                    |       |  |  |

|                  | 0 = Timerx and Timery act as two 16-bit timers                 |                   |                |                  |                 |                    |       |  |  |

|                  |                                                                | ted: Read as '    |                |                  |                 |                    |       |  |  |

|                  |                                                                | Clock Source S    |                |                  |                 |                    |       |  |  |

|                  |                                                                | clock is from pir | n, TxCK (on th | e rising edge)   |                 |                    |       |  |  |

|                  | 0 = Internal cl                                                |                   |                |                  |                 |                    |       |  |  |

| bit 0            | Unimplomen                                                     | ted: Read as '    | ר <b>י</b>     |                  |                 |                    |       |  |  |

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXGM3XX/6XX/7XX devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring: PWMLOCK = 0.

To gain write access to these locked registers, the user application must write two consecutive values of 0xABCD and 0x4321 to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWM1 WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

| 1                                                                                                            | pulled high externally in order to clear and disable the fault<br>register requires unlock sequence                                                                                                                                                                                               |  |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <pre>mov #0xabcd, w10 mov #0x4321, w11 mov #0x0000, w0 mov w10, PWMKEY mov w11, PWMKEY mov w0, FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |  |

| -                                                                                                            | and polarity using the IOCON1 register<br>register requires unlock sequence                                                                                                                                                                                                                       |  |

| <pre>mov #0xabcd, w10 mov #0x4321, w11 mov #0xF000, w0 mov w10, PWMKEY mov w11, PWMKEY mov w0, IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |  |

#### REGISTER 25-1: PTGCST: PTG CONTROL/STATUS REGISTER (CONTINUED)

- bit 1-0 PTGITM<1:0>: PTG Input Trigger Command Operating Mode bits<sup>(1)</sup>

- 11 = Single level detect with step delay is not executed on exit of command (regardless of PTGCTRL command)

- 10 = Single level detect with step delay is executed on exit of command

- 01 = Continuous edge detect with step delay is not executed on exit of command (regardless of PTGCTRL command)

- 00 = Continuous edge detect with step delay is executed on exit of command

- Note 1: These bits apply to the PTGWHI and PTGWLO commands only.

- **2:** This bit is only used with the PTGCTRL Step command software trigger option.

| bit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                          |  |  |

|---------|------------------------|-------------|---------------------------------------------|--|--|

|         | PTGWHI(1)              | 0000        | PWM Special Event Trigger                   |  |  |

|         | or<br>(1)              | 0001        | PWM master time base synchronization output |  |  |

|         | PTGWLO(1)              | 0010        | PWM1 interrupt                              |  |  |

|         |                        | 0011        | PWM2 interrupt                              |  |  |

|         |                        | 0100        | PWM3 interrupt                              |  |  |

|         |                        | 0101        | PWM4 interrupt                              |  |  |

|         |                        | 0110        | PWM5 interrupt                              |  |  |

|         |                        | 0111        | OC1 Trigger Event                           |  |  |

|         |                        | 1000        | OC2 Trigger Event                           |  |  |

|         |                        | 1001        | IC1 Trigger Event                           |  |  |

|         |                        | 1010        | CMP1 Trigger Event                          |  |  |

|         |                        | 1011        | CMP2 Trigger Event                          |  |  |

|         |                        | 1100        | CMP3 Trigger Event                          |  |  |

|         |                        | 1101        | CMP4 Trigger Event                          |  |  |

|         |                        | 1110        | ADC conversion done interrupt               |  |  |

|         |                        | 1111        | INT2 external interrupt                     |  |  |

|         | PTGIRQ(1)              | 0000        | Generate PTG Interrupt 0                    |  |  |

|         |                        | 0001        | Generate PTG Interrupt 1                    |  |  |

|         |                        | 0010        | Generate PTG Interrupt 2                    |  |  |

|         |                        | 0011        | Generate PTG Interrupt 3                    |  |  |

|         |                        | 0100        | Reserved                                    |  |  |

|         |                        | •           | •                                           |  |  |

|         |                        | •           | •                                           |  |  |

|         |                        | 1111        | Reserved                                    |  |  |

|         | PTGTRIG <sup>(2)</sup> | 00000       | PTGO0                                       |  |  |

|         | 1 1011110              | 00001       | PTGO1                                       |  |  |

|         |                        | •           | •                                           |  |  |

|         |                        | •           | •                                           |  |  |

|         |                        | •           | •                                           |  |  |

|         |                        | 11110       | PTGO30                                      |  |  |

|         |                        | 11111       | PTGO31                                      |  |  |

TABLE 25-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 25-2 for the trigger output descriptions.

| DC CHARACTER                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |    |               |       |            |      |         |

|----------------------------------------|-------------------------------------------------------|----|---------------|-------|------------|------|---------|

| Parameter No. Typ. <sup>(2)</sup> Max. |                                                       |    | Doze<br>Ratio | Units | Conditions |      |         |

| Doze Current (IDOZE) <sup>(1)</sup>    |                                                       |    |               |       |            |      |         |

| DC73a                                  | 20                                                    | 53 | 1:2           | mA    | -40°C      | 3.3V | 70 MIPS |

| DC73g                                  | 8                                                     | 30 | 1:128         | mA    |            |      | 70 MIPS |

| DC70a                                  | 19                                                    | 53 | 1:2           | mA    | +25°C      | 3.3V | 60 MIPS |

| DC70g                                  | 8                                                     | 30 | 1:128         | mA    | +25 C      |      |         |

| DC71a                                  | 20                                                    | 53 | 1:2           | mA    | . 05%0     | 3.3V | 60 MIPS |

| DC71g                                  | 10                                                    | 30 | 1:128         | mA    | +85°C      |      |         |

| DC72a                                  | 25                                                    | 42 | 1:2           | mA    | +125°C     | 3.3V | 50 MIPS |

| DC72g                                  | 12                                                    | 30 | 1:128         | mA    | +125 C     |      | 50 MIPS |

#### TABLE 33-9: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

• Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as outputs and driving low

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- CPU executing

```

while(1)

{

NOP();

}

```

- · JTAG is disabled

- 2: Data in the "Typical" column is at 3.3V, +25°C unless otherwise specified.

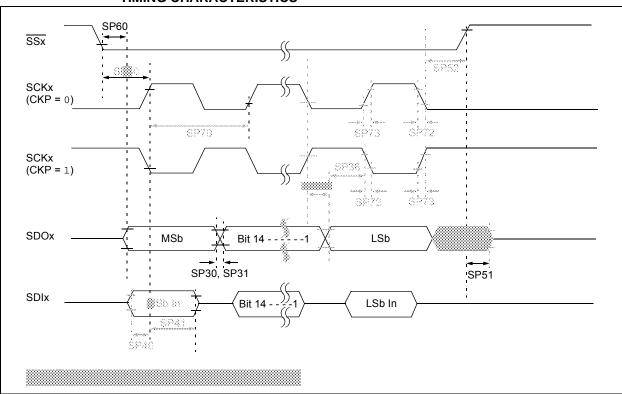

#### FIGURE 33-20: SPI2 AND SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

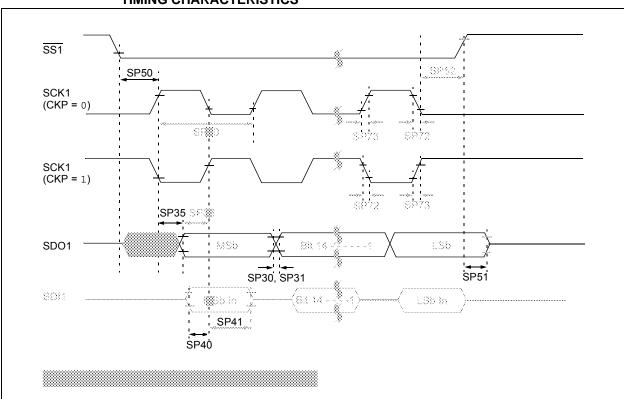

FIGURE 33-29: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

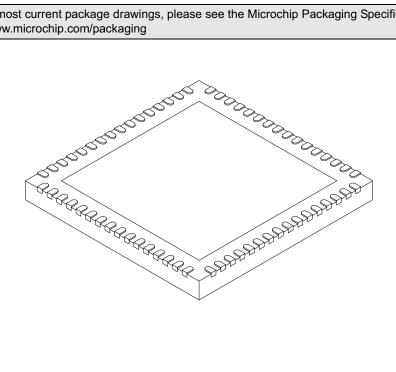

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    | Ν    | /ILLIMETER | S    |  |

|------------------------|----------|------|------------|------|--|

| Dimensio               | n Limits | MIN  | NOM        | MAX  |  |

| Number of Pins         | N        | 64   |            |      |  |

| Pitch                  | е        |      | 0.50 BSC   |      |  |

| Overall Height         | A        | 0.80 | 0.90       | 1.00 |  |

| Standoff               | A1       | 0.00 | 0.02       | 0.05 |  |

| Contact Thickness      | A3       |      | 0.20 REF   |      |  |

| Overall Width          | E        |      | 9.00 BSC   |      |  |

| Exposed Pad Width      | E2       | 7.05 | 7.15       | 7.50 |  |

| Overall Length         | D        |      | 9.00 BSC   |      |  |

| Exposed Pad Length     | D2       | 7.05 | 7.15       | 7.50 |  |

| Contact Width          | b        | 0.18 | 0.25       | 0.30 |  |

| Contact Length         | L        | 0.30 | 0.40       | 0.50 |  |

| Contact-to-Exposed Pad | K        | 0.20 | -          | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-149C Sheet 2 of 2

| PMP Pinout and Connections to           |     |

|-----------------------------------------|-----|

| External Devices                        |     |

| Programmer's Model                      |     |

| PTG Module                              |     |

| QEIx Module                             |     |

| Recommended Minimum Connection          | 22  |

| Remappable Input for U1RX               |     |

| Reset System                            |     |

| RTCC Module                             |     |

| Shared Port Structure                   |     |

| Single-Phase Synchronous Buck Converter | 25  |

| SPIx Module                             |     |

| Suggested Oscillator Circuit Placement  | 23  |

| Type B Timer (Timer2/4/6/8)             | 214 |

| Type B/Type C Timer Pair (32-Bit Timer) |     |

| Type C Timer (Timer3/5/7/9)             |     |

| UARTx Module                            |     |

| User-Programmable Blanking Function     |     |

| Watchdog Timer (WDT)                    | 417 |

| Brown-out Reset (BOR)                   | 416 |

## С

| C Compilers<br>MPLAB XC Compilers    |       | 430   |

|--------------------------------------|-------|-------|

| CAN Module                           |       | 430   |

| Control Registers                    |       | 207   |

| Message Buffers                      |       |       |

| Word 0                               |       |       |

| Word 1                               |       |       |

| Word 2                               |       |       |

| Word 3                               |       |       |

| Word 4                               |       |       |

| Word 5                               |       |       |

| Word 6                               |       |       |

| Word 7                               |       |       |

| Modes of Operation                   |       |       |

| Overview                             |       |       |

| CAN Module (CAN)                     |       |       |

| Charge Time Measurement Unit (CTMU)  |       |       |

| Code Examples                        |       |       |

| IC1 Connection to HOME1 QEI1 Digital |       |       |

| Filter Input on Pin 43               |       | . 166 |

| PORTB Write/Read                     |       | . 164 |

| PWM1 Write-Protected Register        |       |       |

| Unlock Sequence                      |       | 230   |

| PWRSAV Instruction Syntax            |       | 153   |

| Code Protection                      | .411, | 418   |

| CodeGuard Security                   | .411, | 418   |

| Configuration Bits                   |       | .411  |

| Description                          |       | .413  |

| CPU                                  |       | 27    |

| Addressing Modes                     |       |       |

| Arithmetic Logic Unit (ALU)          |       |       |

| Control Registers                    |       |       |

| Data Space Addressing                |       | 27    |

| DSP Engine                           |       | 35    |

| Instruction Set                      |       | 27    |

| Programmer's Model                   |       |       |

| Register Descriptions                |       | 29    |

| CTMU                                 |       |       |

| Control Registers                    |       |       |

| Customer Change Notification Service |       | 536   |

| Customer Notification Service        |       |       |

| Customer Support                     |       | 536   |

|                                      |       |       |

## D

| Data Address Space                         |

|--------------------------------------------|

| Memory Map for 128-Kbyte Devices           |

| Memory Map for 256-Kbyte Devices           |

| Memory Map for 512-Kbyte Devices           |

| Near Data Space 41                         |

| Organization and Alignment 41              |

| SFR Space 41                               |

| Width 41                                   |

| Data Converter Interface (DCI) Module      |

| Data Memory                                |

| Arbitration and Bus Master Priority        |

| DC Characteristics                         |

| Brown-out Reset (BOR) 443                  |

| CTMU Current Source 490                    |

| Doze Current (IDOZE) 439, 501              |

| Filter Capacitor (CEFC) Specifications 435 |

| High Temperature 500                       |

| I/O Pin Input Specifications 440           |

| I/O Pin Output Specifications 443, 502     |

| Idle Current (IIDLE)                       |

| Op Amp/Comparator Specifications 488       |

| Op Amp/Comparator Voltage                  |

| Reference Specifications 489               |

| Operating Current (IDD) 436, 501           |

| Operating MIPS vs. Voltage 434, 500        |

| Power-Down Current (IPD) 438, 500          |

| Program Memory 444, 502                    |

| Temperature and Voltage 500                |

| Temperature and Voltage Specifications     |

| Thermal Operating Conditions               |

| Thermal Packaging Characteristics          |

| DCI                                        |

| Control Registers 344                      |

| Introduction 343                           |

| Demo/Development Boards, Evaluation        |

| and Starter Kits 432                       |

| Development Support 429                    |

| Third-Party Tools 432                      |

| DMA Controller                             |

| Channel to Peripheral Associations 130     |

| Control Registers 132                      |

| DMAxCNT 132                                |

| DMAxCON 132                                |

| DMAxPAD 132                                |

| DMAxREQ 132                                |

| DMAxSTAL/H 132                             |

| DMAxSTBL/H 132                             |

| Supported Peripherals 129                  |

| Doze Mode 155                              |

| E                                          |

| Electrical Characteristics | 433      |

|----------------------------|----------|

| AC                         | 445, 503 |

| Equations                  |          |

| Device Operating Frequency | 144      |

| Fosc Calculation           | 144      |

| Fvco Calculation           | 144      |

| Errata                     | 12       |

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support