Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | -                                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) |                                                                                  |

| Data Converters            | A/D 30x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm306-h-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: PINC                              |             | J DESC         | КІРП    | ONS (CONTINUED)                                                                                                                             |

|----------------------------------------------|-------------|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                     | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                                                                                 |

| INDX1 <sup>(1)</sup>                         | I           | ST             | Yes     | Quadrature Encoder Index1 pulse input.                                                                                                      |

| HOME1 <sup>(1)</sup>                         | I           | ST             | Yes     | Quadrature Encoder Home1 pulse input.                                                                                                       |

| QEA1 <sup>(1)</sup>                          | I.          | ST             | Yes     | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer                                                                              |

| QEB1 <sup>(1)</sup>                          | I           | ST             | Yes     | external clock input in Timer mode.<br>Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer<br>external gate input in Timer mode. |

| CNTCMP1 <sup>(1)</sup>                       | 0           | —              | Yes     | Quadrature Encoder Compare Output 1.                                                                                                        |

| INDX2 <sup>(1)</sup>                         | I           | ST             | Yes     | Quadrature Encoder Index2 Pulse input.                                                                                                      |

| HOME2 <sup>(1)</sup>                         | 1           | ST             | Yes     | Quadrature Encoder Home2 Pulse input.                                                                                                       |

| QEA2 <sup>(1)</sup>                          | I           | ST             | Yes     | Quadrature Encoder Phase A input in QEI2 mode. Auxiliary timer                                                                              |

| QEB2 <sup>(1)</sup>                          | I           | ST             | Yes     | external clock input in Timer mode.<br>Quadrature Encoder Phase B input in QEI2 mode. Auxiliary timer<br>external gate input in Timer mode. |

| CNTCMP2 <sup>(1)</sup>                       | 0           | —              | Yes     | Quadrature Encoder Compare Output 2.                                                                                                        |

| COFS                                         | I/O         | ST             | Yes     | Data Converter Interface frame synchronization pin.                                                                                         |

| CSCK                                         | I/O         | ST             | Yes     | Data Converter Interface serial clock input/output pin.                                                                                     |

| CSDI                                         | I           | ST             | Yes     | Data Converter Interface serial data input pin.                                                                                             |

| CSDO                                         | 0           | —              | Yes     | Data Converter Interface serial data output pin.                                                                                            |

| C1RX                                         | Ι           | ST             | Yes     | CAN1 bus receive pin.                                                                                                                       |

| C1TX                                         | 0           | —              | Yes     | CAN1 bus transmit pin                                                                                                                       |

| C2RX                                         | Ι           | ST             | Yes     | CAN2 bus receive pin.                                                                                                                       |

| C2TX                                         | 0           | —              | Yes     | CAN2 bus transmit pin                                                                                                                       |

| RTCC                                         | 0           | —              | No      | Real-Time Clock and Calendar alarm output.                                                                                                  |

| CVREF                                        | 0           | Analog         | No      | Comparator Voltage Reference output.                                                                                                        |

| C1IN1+, C1IN2-,<br>C1IN1-, C1IN3-            | Ι           | Analog         | No      | Comparator 1 inputs.                                                                                                                        |

| C1OUT                                        | 0           | —              | Yes     | Comparator 1 output.                                                                                                                        |

| C2IN1+, C2IN2-,<br>C2IN1-, C2IN3-            | Ι           | Analog         | No      | Comparator 2 inputs.                                                                                                                        |

| C2OUT                                        | 0           | —              | Yes     | Comparator 2 output.                                                                                                                        |

| C3IN1+, C3IN2-,<br>C2IN1-, C3IN3-            | I           | Analog         | No      | Comparator 3 inputs.                                                                                                                        |

| C3OUT                                        | 0           | —              | Yes     | Comparator 3 output.                                                                                                                        |

| C4IN1+, C4IN2-,<br>C4IN1-, C4IN3-            | I           | Analog         | No      | Comparator 4 inputs.                                                                                                                        |

| C4OUT                                        | 0           | —              | Yes     | Comparator 4 output.                                                                                                                        |

| C5IN1-, C5IN2-,<br>C5IN3-, C5IN4-,<br>C5IN1+ | I           | Analog         | No      | Comparator 5 inputs.                                                                                                                        |

| C5OUT                                        | 0           | —              | Yes     | Comparator 5 output.                                                                                                                        |

| Legend: CMOS = CM                            | IOS co      | mpatible       | input o | or output Analog = Analog input P = Power                                                                                                   |

#### TABLE 1-1:PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

Note 1: This pin is not available on all devices. For more information, see the "Pin Diagrams" section for pin availability.

2: AVDD must be connected at all times.

I = Input

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| U-0          | U-0                | U-0              | U-0   | U-0              | U-0              | U-0             | U-0   |

|--------------|--------------------|------------------|-------|------------------|------------------|-----------------|-------|

| _            | —                  | —                | —     | —                | —                | _               | _     |

| bit 15       |                    | ·                |       |                  |                  |                 | bit 8 |

|              |                    |                  |       |                  |                  |                 |       |

| U-0          | R/W-0              | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| _            |                    |                  |       | T2CKR<6:0>       | >                |                 |       |

| bit 7        |                    |                  |       |                  |                  |                 | bit 0 |

|              |                    |                  |       |                  |                  |                 |       |

| Legend:      |                    |                  |       |                  |                  |                 |       |

| R = Readat   | ole bit            | W = Writable     | bit   | U = Unimpler     | mented bit, read | d as '0'        |       |

| -n = Value a | at POR             | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              |                    |                  |       |                  |                  |                 |       |

| bit 15-7     | Unimplemer         | ted: Read as '   | 0'    |                  |                  |                 |       |

| bit 6-0      |                    | -: Assign Timer  |       | . ,              | he Correspondi   | ng RPn pin bits | 3     |

|              | 1111100 <b>=  </b> | nput tied to RP  | 124   |                  |                  |                 |       |

|              | •                  |                  |       |                  |                  |                 |       |

|              | •                  |                  |       |                  |                  |                 |       |

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

© 2013-2014 Microchip Technology Inc.

| U-0                                                                       | R/W-0                                      | R/W-0                                                                        | R/W-0     | R/W-0        | R/W-0           | R/W-0       | R/W-0 |

|---------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------|-----------|--------------|-----------------|-------------|-------|

|                                                                           |                                            |                                                                              |           | C2RXR<6:0>   |                 |             |       |

| bit 15                                                                    |                                            |                                                                              |           |              |                 |             | bit 8 |

|                                                                           |                                            |                                                                              |           |              |                 |             |       |

| U-0                                                                       | R/W-0                                      | R/W-0                                                                        | R/W-0     | R/W-0        | R/W-0           | R/W-0       | R/W-0 |

| —                                                                         |                                            |                                                                              |           | C1RXR<6:0>   |                 |             |       |

| bit 7                                                                     |                                            |                                                                              |           |              |                 |             | bit ( |

|                                                                           |                                            |                                                                              |           |              |                 |             |       |

| Legend:                                                                   |                                            |                                                                              |           |              |                 |             |       |

| R = Readat                                                                | ole bit                                    | W = Writable                                                                 | bit       | U = Unimplem | nented bit, rea | d as '0'    |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow |                                            |                                                                              |           |              |                 |             | iown  |

|                                                                           | 11111100 =  <br>•<br>•<br>•<br>•<br>•<br>• | 1-2 for input pin<br>nput tied to RPI<br>nput tied to CM<br>nput tied to Vss | 124<br>P1 | ,            |                 |             |       |

| bit 7                                                                     |                                            | nted: Read as '                                                              |           |              |                 |             |       |

| bit 6-0                                                                   | C10VD-6.0                                  | >: Assign CAN1                                                               |           |              |                 | Do Dio hito |       |

# REGISTER 11-20: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26<sup>(1)</sup>

Note 1: This register is not available on dsPIC33EPXXXGM3XX devices.

| U-0                               | R/W-0              | R/W-0                                | R/W-0            | R/W-0       | R/W-0                | R/W-0          | R/W-0              |  |

|-----------------------------------|--------------------|--------------------------------------|------------------|-------------|----------------------|----------------|--------------------|--|

| _                                 |                    |                                      |                  | SYNCI1R<6:0 | )>                   |                |                    |  |

| bit 15                            |                    |                                      |                  |             |                      |                | bit 8              |  |

|                                   |                    |                                      |                  |             |                      |                |                    |  |

| U-0                               | U-0                | U-0                                  | U-0              | U-0         | U-0                  | U-0            | U-0                |  |

| _                                 | —                  | _                                    | —                | —           |                      | —              |                    |  |

| bit 7                             |                    |                                      |                  |             |                      |                | bit 0              |  |

|                                   |                    |                                      |                  |             |                      |                |                    |  |

| Legend:                           |                    |                                      |                  |             |                      |                |                    |  |

| R = Readable bit W = Writable bit |                    | U = Unimplei                         | mented bit, read | l as '0'    |                      |                |                    |  |

| -n = Value a                      | at POR             | '1' = Bit is set                     | I' = Bit is set  |             | '0' = Bit is cleared |                | x = Bit is unknown |  |

|                                   |                    |                                      |                  |             |                      |                |                    |  |

| bit 15                            | Unimplemer         | nted: Read as 'o                     | 0'               |             |                      |                |                    |  |

| bit 14-8                          |                    | <b>0&gt;:</b> Assign PWI             |                  |             | o the Correspon      | ding RPn Pin b | its                |  |

|                                   | 1111100 <b>=  </b> | nput tied to RPI                     | 124              |             |                      |                |                    |  |

|                                   | •                  |                                      |                  |             |                      |                |                    |  |

|                                   | •                  |                                      |                  |             |                      |                |                    |  |

|                                   | •                  | nout tigd to CM                      | D1               |             |                      |                |                    |  |

|                                   |                    | nput tied to CMI<br>nput tied to Vss |                  |             |                      |                |                    |  |

| bit 7-0                           |                    | nted: Read as '                      |                  |             |                      |                |                    |  |

|                                   | ompleme            |                                      | 0                |             |                      |                |                    |  |

#### REGISTER 11-25: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37

## REGISTER 11-29: RPINR41: PERIPHERAL PIN SELECT INPUT REGISTER 41

| U-0                 | U-0          | U-0                                  | U-0         | U-0                                     | U-0               | U-0           | U-0            |

|---------------------|--------------|--------------------------------------|-------------|-----------------------------------------|-------------------|---------------|----------------|

| _                   | —            | —                                    | _           | _                                       | —                 | —             | —              |

| bit 15              |              |                                      |             |                                         |                   |               | bit 8          |

|                     |              |                                      |             |                                         |                   |               |                |

| U-0                 | R/W-0        | R/W-0                                | R/W-0       | R/W-0                                   | R/W-0             | R/W-0         | R/W-0          |

| _                   |              |                                      |             | DTCMP6R<6:                              | 0>                |               |                |

| bit 7               |              |                                      |             |                                         |                   |               | bit 0          |

|                     |              |                                      |             |                                         |                   |               |                |

| Legend:             |              |                                      |             |                                         |                   |               |                |

| R = Readabl         | e bit        | W = Writable                         | bit         | U = Unimpler                            | mented bit, read  | as '0'        |                |

| -n = Value at       | POR          | '1' = Bit is set                     |             | '0' = Bit is cleared x = Bit is unknown |                   |               | nown           |

| bit 15-7<br>bit 6-0 | DTCMP6R<6    |                                      | M Dead-Time |                                         | on Input 6 to the | Corresponding | g RPn Pin bits |

|                     |              | -2 for input pin<br>nput tied to RPI |             | ibers)                                  |                   |               |                |

|                     | 0000001 = lr | put tied to CMI                      | P1          |                                         |                   |               |                |

0000000 = Input tied to Vss

#### REGISTER 11-32: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| U-0          | U-0        | R/W-0                               | R/W-0          | R/W-0                   | R/W-0            | R/W-0           | R/W-0 |

|--------------|------------|-------------------------------------|----------------|-------------------------|------------------|-----------------|-------|

| _            | —          |                                     |                | RP39                    | R<5:0>           |                 |       |

| bit 15       |            |                                     |                |                         |                  |                 | bit 8 |

|              |            | DAMA                                |                | DAMO                    | DAVA             | DAMA            | DAMO  |

| U-0          | U-0        | R/W-0                               | R/W-0          | R/W-0                   | R/W-0            | R/W-0           | R/W-0 |

| —            | —          |                                     |                | RP38                    | R<5:0>           |                 |       |

| bit 7        |            |                                     |                |                         |                  |                 | bit 0 |

|              |            |                                     |                |                         |                  |                 |       |

| Legend:      |            |                                     |                |                         |                  |                 |       |

| R = Readab   | le bit     | W = Writable                        | bit            | U = Unimplen            | nented bit, read | d as '0'        |       |

| -n = Value a | t POR      | '1' = Bit is set                    |                | '0' = Bit is clea       | ared             | x = Bit is unkr | iown  |

| bit 15-14    | Unimplemen | ted: Read as '                      | 0'             |                         |                  |                 |       |

| bit 13-8     |            | : Peripheral Ou<br>-3 for periphera |                | i is Assigned to mbers) | RP39 Output F    | Pin bits        |       |

| bit 7-6      | Unimplemen | ted: Read as '                      | 0'             |                         |                  |                 |       |

| bit 5-0      | RP38R<5:0> | : Peripheral Ou                     | utput Function | is Assigned to          | RP38 Output F    | Pin bits        |       |

|              |            |                                     |                | -                       |                  |                 |       |

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-33: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0           | U-0        | R/W-0            | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|---------------|------------|------------------|---------------|-------------------|-----------------|-----------------|-------|

| _             | _          |                  |               | RP41              | R<5:0>          |                 |       |

| bit 15        |            |                  |               |                   |                 |                 | bit 8 |

|               |            |                  |               |                   |                 |                 |       |

| U-0           | U-0        | R/W-0            | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| _             | _          |                  |               | RP40              | R<5:0>          |                 |       |

| bit 7         | ÷          |                  |               |                   |                 |                 | bit 0 |

|               |            |                  |               |                   |                 |                 |       |

| Legend:       |            |                  |               |                   |                 |                 |       |

| R = Readable  | e bit      | W = Writable     | bit           | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at | POR        | '1' = Bit is set |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|               |            |                  |               |                   |                 |                 |       |

| bit 15-14     | Unimpleme  | nted: Read as '  | 0'            |                   |                 |                 |       |

| bit 13-8      | RP41R<5:0> | . Peripheral Ou  | tput Function | n is Assigned to  | RP41 Output     | Pin bits        |       |

(see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-3 for peripheral function numbers)

NOTES:

| R/W-0               | R/W-0                                                                                                                                                                       | R/W-0                                                                                                                       | R/W-0                         | R/W-0            | R/W-0                 | R/W-0                | R/W-0   |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------|-----------------------|----------------------|---------|

| IFLTMOD             | CLSRC4                                                                                                                                                                      | CLSRC3                                                                                                                      | CLSRC2                        | CLSRC1           | CLSRC0                | CLPOL <sup>(1)</sup> | CLMOD   |

| bit 15              |                                                                                                                                                                             |                                                                                                                             |                               |                  |                       |                      | bit 8   |

|                     |                                                                                                                                                                             |                                                                                                                             |                               |                  |                       |                      |         |

| R/W-1               | R/W-1                                                                                                                                                                       | R/W-1                                                                                                                       | R/W-1                         | R/W-1            | R/W-0                 | R/W-0                | R/W-0   |

| FLTSRC4             | FLTSRC3                                                                                                                                                                     | FLTSRC2                                                                                                                     | FLTSRC1                       | FLTSRC0          | FLTPOL <sup>(1)</sup> | FLTMOD1              | FLTMOD0 |

| bit 7               |                                                                                                                                                                             |                                                                                                                             |                               |                  |                       |                      | bit     |

| Legend:             |                                                                                                                                                                             |                                                                                                                             |                               |                  |                       |                      |         |

| R = Readable        | bit                                                                                                                                                                         | W = Writable                                                                                                                | bit                           | U = Unimplen     | nented bit, read      | 1 as '0'             |         |

| -n = Value at I     | POR                                                                                                                                                                         | '1' = Bit is set                                                                                                            |                               | '0' = Bit is cle | ared                  | x = Bit is unkr      | nown    |

| bit 15<br>bit 14-10 | 1 = Independ<br>0 = Independ                                                                                                                                                | dependent Fau<br>lent Fault mode<br>lent Fault mode<br>: Current-Limit                                                      | e is enabled<br>e is disabled |                  | t for the PWM         | < Generator # b      | its     |

|                     | 11111 = Faul<br>11110 = Res                                                                                                                                                 | lt 32                                                                                                                       |                               |                  |                       |                      |         |

|                     | •                                                                                                                                                                           |                                                                                                                             |                               |                  |                       |                      |         |

|                     | 01011 = Com<br>01010 = Op A<br>01001 = Op A<br>01000 = Op A<br>00111 = Faul<br>00101 = Faul<br>00101 = Faul<br>00011 = Faul<br>00010 = Faul<br>00001 = Faul<br>00001 = Faul | Amp/Comparat<br>Amp/Comparat<br>Amp/Comparat<br>t 8<br>tt 8<br>tt 7<br>tt 6<br>tt 5<br>tt 5<br>tt 4<br>tt 3<br>tt 2<br>tt 1 | or 3<br>or 2<br>or 1          |                  | (1)                   |                      |         |

| bit 9               | 1 = The selec                                                                                                                                                               | ent-Limit Polari<br>ted current-lim<br>ted current-lim                                                                      | it source is ac               | tive-low         | (1)                   |                      |         |

| bit 8               |                                                                                                                                                                             | rent-Limit Mode<br>imit mode is er                                                                                          | nabled                        | WMx Generato     | or # bit              |                      |         |

#### REGISTER 16-21: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER

**Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# 20.1 UART Helpful Tips

- In multi-node direct connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pullup or pull-down resistor on the RX pin, depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

2. The first character received on wake-up from Sleep mode, caused by activity on the UxRX pin of the UART module, will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid. This is to be expected.

#### BUFFER 21-5: CANx MESSAGE BUFFER WORD 4

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | Byte  | 3<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|                 |       |                  | Byte  | 2<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimpler     | mented bit, rea | id as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle |                 | x = Bit is unkı | nown  |

bit 15-8 Byte 3<15:8>: CANx Message Byte 3

bit 7-0 Byte 2<7:0>: CANx Message Byte 2

#### BUFFER 21-6: CANx MESSAGE BUFFER WORD 5

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | Byte  | 5<15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x           | R/W-x           | R/W-x |

|                 |       |                  | Byte  | 4<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 7-0 Byte 4<7:0>: CANx Message Byte 4

| r-0            | r-0                                                                                                          | r-0                                                                                                                                                                                                                                                                                            | r-0                          | R-0              | R-0             | R-0             | R-0   |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------|-----------------|-----------------|-------|--|--|

| r              | r                                                                                                            | r                                                                                                                                                                                                                                                                                              | r                            | SLOT3            | SLOT2           | SLOT1           | SLOT0 |  |  |

| bit 15         |                                                                                                              |                                                                                                                                                                                                                                                                                                |                              |                  |                 |                 | bit   |  |  |

| r-0            | r-0                                                                                                          | r-0                                                                                                                                                                                                                                                                                            | r-0                          | R-0              | R-0             | R-0             | R-0   |  |  |

| r              | r                                                                                                            | r                                                                                                                                                                                                                                                                                              | r                            | ROV              | RFUL            | TUNF            | TMPTY |  |  |

| bit 7          |                                                                                                              |                                                                                                                                                                                                                                                                                                |                              |                  |                 |                 | bit   |  |  |

| Legend:        |                                                                                                              | r = Reserved                                                                                                                                                                                                                                                                                   | bit                          |                  |                 |                 |       |  |  |

| R = Readab     | le bit                                                                                                       | W = Writable                                                                                                                                                                                                                                                                                   | bit                          | U = Unimpler     | mented bit, rea | d as '0'        |       |  |  |

| -n = Value a   | t POR                                                                                                        | '1' = Bit is set                                                                                                                                                                                                                                                                               | :                            | '0' = Bit is cle |                 | x = Bit is unkr | nown  |  |  |

|                | 1111 = Slot 1<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | is currently ac<br>is currently ac<br>is currently ac                                                                                                                                                                                                                                          | ctive<br>ctive               |                  |                 |                 |       |  |  |

| bit 7-4        | Reserved: Re                                                                                                 |                                                                                                                                                                                                                                                                                                |                              |                  |                 |                 |       |  |  |

| bit 3<br>bit 2 | 1 = A receive<br>0 = A receive<br><b>RFUL:</b> Receiv<br>1 = New data                                        | <ul> <li>ROV: Receive Overflow Status bit</li> <li>1 = A receive overflow has occurred for at least one Receive register</li> <li>0 = A receive overflow has not occurred</li> <li>RFUL: Receive Buffer Full Status bit</li> <li>1 = New data is available in the Receive registers</li> </ul> |                              |                  |                 |                 |       |  |  |

| bit 1          | <b>TUNF:</b> Transr<br>1 = A transmit                                                                        | <ul> <li>0 = The Receive registers have old data</li> <li>TUNF: Transmit Buffer Underflow Status bit</li> <li>1 = A transmit underflow has occurred for at least one Transmit register</li> <li>0 = A transmit underflow has not occurred</li> </ul>                                           |                              |                  |                 |                 |       |  |  |

| bit 0          | <b>TMPTY:</b> Trans<br>1 = The Trans                                                                         | smit Buffer Err                                                                                                                                                                                                                                                                                | ipty Status bit<br>are empty | -                |                 |                 |       |  |  |

# REGISTER 24-4: DCISTAT: DCI STATUS REGISTER

# REGISTER 25-4: PTGT0LIM: PTG TIMER0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0    | R/W-0 |

|-----------------------------------|-------|------------------|-------|------------------|-----------------|----------|-------|

|                                   |       |                  | PTGT0 | _IM<15:8>        |                 |          |       |

| bit 15                            |       |                  |       |                  |                 |          | bit 8 |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0    | R/W-0 |

|                                   |       |                  | PTGT0 | LIM<7:0>         |                 |          |       |

| bit 7                             |       |                  |       |                  |                 |          | bit 0 |

| Legend:                           |       |                  |       |                  |                 |          |       |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimpler     | nented bit, rea | d as '0' |       |

| -n = Value at P                   | POR   | '1' = Bit is set |       | '0' = Bit is cle | •               |          |       |

bit 15-0 **PTGT0LIM<15:0>:** PTG Timer0 Limit Register bits

General purpose Timer0 Limit register (effective only with a PTGT0 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

#### REGISTER 25-5: PTGT1LIM: PTG TIMER1 LIMIT REGISTER<sup>(1)</sup>

| PTGT1LIM<15:8><br>bit 15 b | R/W-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|----------------------------|----------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| bit 15 b                   | PTGT1LIM<15:8> |       |       |       |       |       |       |       |  |  |  |

|                            | bit 15         |       |       |       |       |       |       |       |  |  |  |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| PTGT1LIM<7:0> |       |       |       |       |       |       |       |  |  |  |

| bit 7         |       |       |       |       |       |       | bit 0 |  |  |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

- bit 15-0 **PTGT1LIM<15:0>:** PTG Timer1 Limit Register bits General purpose Timer1 Limit register (effective only with a PTGT1 Step command).

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

| U-0           | U-0                                                                                                                                                                      | U-0                                                                          | U-0                            | R/W-0                        | R/W-0            | U-0             | U-0   |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------|------------------------------|------------------|-----------------|-------|--|--|--|--|

|               | _                                                                                                                                                                        | _                                                                            | _                              | CVRR1                        | VREFSEL          |                 |       |  |  |  |  |

| bit 15        |                                                                                                                                                                          |                                                                              |                                |                              |                  |                 | bi    |  |  |  |  |

|               |                                                                                                                                                                          |                                                                              |                                |                              |                  |                 |       |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                                                    | R/W-0                                                                        | R/W-0                          | R/W-0                        | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

| CVREN         | CVROE                                                                                                                                                                    | CVRR0                                                                        | CVRSS                          | CVR3                         | CVR2             | CVR1            | CVR0  |  |  |  |  |

| bit 7         |                                                                                                                                                                          |                                                                              |                                |                              |                  |                 | bit   |  |  |  |  |

| Legend:       |                                                                                                                                                                          |                                                                              |                                |                              |                  |                 |       |  |  |  |  |

| R = Readabl   | e bit                                                                                                                                                                    | W = Writable                                                                 | bit                            | U = Unimple                  | mented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value at | t POR                                                                                                                                                                    | '1' = Bit is set                                                             |                                | '0' = Bit is cle             | eared            | x = Bit is unkn | iown  |  |  |  |  |

| -             |                                                                                                                                                                          |                                                                              |                                |                              |                  |                 |       |  |  |  |  |

| bit 15-12     | Unimplemen                                                                                                                                                               | ted: Read as '                                                               | 0'                             |                              |                  |                 |       |  |  |  |  |

| bit 11        | CVRR1: Com<br>See bit 5.                                                                                                                                                 | nparator Voltage                                                             | e Reference I                  | Range Selectio               | on bit           |                 |       |  |  |  |  |

| bit 10        | VREFSEL: V                                                                                                                                                               | oltage Referen                                                               | ce Select bit                  |                              |                  |                 |       |  |  |  |  |

|               | 1 = CVREFIN                                                                                                                                                              | -                                                                            |                                |                              |                  |                 |       |  |  |  |  |

|               | 0 = CVREFIN                                                                                                                                                              | is generated by                                                              | the resistor                   | network                      |                  |                 |       |  |  |  |  |

| bit 9-8       | Unimplemen                                                                                                                                                               | ted: Read as '                                                               | 0'                             |                              |                  |                 |       |  |  |  |  |

| bit 7         | CVREN: Con                                                                                                                                                               | nparator Voltag                                                              | Enable bit                     |                              |                  |                 |       |  |  |  |  |

|               | •                                                                                                                                                                        | tor voltage refe<br>tor voltage refe                                         |                                | •                            | wn               |                 |       |  |  |  |  |

| bit 6         | CVROE: Comparator Voltage Reference Output Enable on CVREF10 Pin bit                                                                                                     |                                                                              |                                |                              |                  |                 |       |  |  |  |  |

|               |                                                                                                                                                                          | evel is output or<br>evel is disconne                                        |                                |                              |                  |                 |       |  |  |  |  |

| bit 11, 5     | <b>CVRR&lt;1:0&gt;:</b> Comparator Voltage Reference Range Selection bits                                                                                                |                                                                              |                                |                              |                  |                 |       |  |  |  |  |

|               | 10 = 0.33 CV<br>01 = 0.00 CV                                                                                                                                             | /RSRC to 0.94, v<br>/RSRC to 0.96, v<br>/RSRC to 0.67, v<br>/RSRC to 0.75, v | vith CVRSRC/2<br>vith CVRSRC/2 | 24 step-size<br>24 step-size |                  |                 |       |  |  |  |  |

| bit 4         |                                                                                                                                                                          | nparator Voltag                                                              |                                | •                            | on bit           |                 |       |  |  |  |  |

|               | 1 = Compara                                                                                                                                                              | tor voltage refe                                                             | rence source                   | , CVRSRC = C\                | /REF+ – AVSS     |                 |       |  |  |  |  |

| bit 3-0       |                                                                                                                                                                          | •                                                                            |                                |                              |                  | 0> ≤ 15 bits    |       |  |  |  |  |

|               | <b>CVR&lt;3:0&gt;</b> Comparator Voltage Reference Value Selection $0 \le CVR<3:0> \le 15$ bits<br><u>When CVRR&lt;1:0&gt; = 11:</u><br>CVREF = (CVR<3:0>/16) • (CVRSRC) |                                                                              |                                |                              |                  |                 |       |  |  |  |  |

|               | When CVRR<br>CVREF = (1/3                                                                                                                                                | < <u>1:0&gt; = 10:</u><br>) • (CVRSRC) +                                     | (CVR<3:0>/2                    | 24) ● (CVRSRC)               |                  |                 |       |  |  |  |  |

|               | When CVRR                                                                                                                                                                |                                                                              |                                | ,                            |                  |                 |       |  |  |  |  |

|               | •                                                                                                                                                                        | , ,                                                                          | JVRORU)                        |                              |                  |                 |       |  |  |  |  |

|               | When CVRR                                                                                                                                                                | <1:0> = 0.0                                                                  |                                |                              |                  |                 |       |  |  |  |  |

## REGISTER 26-7: CVR1CON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER 1

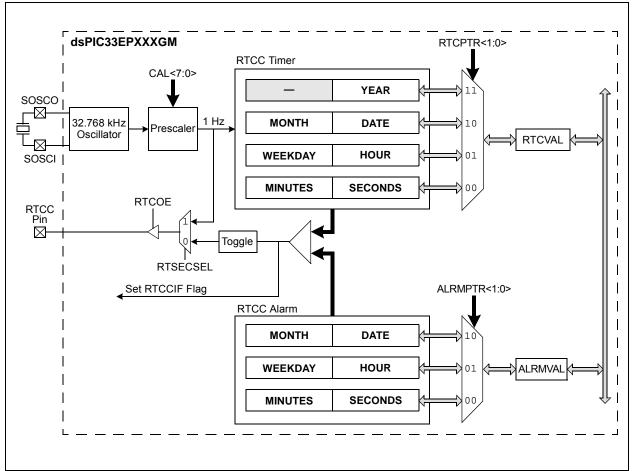

# dsPIC33EPXXXGM3XX/6XX/7XX

#### FIGURE 27-1: RTCC BLOCK DIAGRAM

**Note:** The RTCC is only operational on devices which include the SOSC; therefore, the RTCC module is not available on 44-pin devices.

| R/W-0         | R/W-0                                                                                                                                              | R/W-0                                         | R/W-0         | R/W-0             | R/W-0            | R/W-0            | R/W-0         |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------|-------------------|------------------|------------------|---------------|--|--|--|--|

| ALRMEN        | CHIME                                                                                                                                              | AMASK3                                        | AMASK2        | AMASK1            | AMASK0           | ALRMPTR1         | ALRMPTR0      |  |  |  |  |

| bit 15        |                                                                                                                                                    |                                               |               |                   |                  |                  | bit 8         |  |  |  |  |

|               |                                                                                                                                                    |                                               |               |                   |                  |                  |               |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                              | R/W-0                                         | R/W-0         | R/W-0             | R/W-0            | R/W-0            | R/W-0         |  |  |  |  |

| ARPT7         | ARPT6                                                                                                                                              | ARPT5                                         | ARPT4         | ARPT3             | ARPT2            | ARPT1            | ARPT0         |  |  |  |  |

| bit 7         |                                                                                                                                                    |                                               |               |                   |                  |                  | bit C         |  |  |  |  |

| Legend:       |                                                                                                                                                    |                                               |               |                   |                  |                  |               |  |  |  |  |

| R = Readable  | ) bit                                                                                                                                              | W = Writable                                  | bit           | U = Unimplen      | nented bit, rea  | d as '0'         |               |  |  |  |  |

| -n = Value at | POR                                                                                                                                                | '1' = Bit is set                              |               | '0' = Bit is clea | ared             | x = Bit is unkr  | nown          |  |  |  |  |

|               |                                                                                                                                                    |                                               |               |                   |                  |                  |               |  |  |  |  |

| bit 15        |                                                                                                                                                    | larm Enable bit                               |               |                   |                  |                  |               |  |  |  |  |

|               | CHIME =                                                                                                                                            | = 0)                                          | ed automatica | illy after an ala | rm event wher    | never ARPT<7:    | )> = 0x00 and |  |  |  |  |

|               | 0 = Alarm is                                                                                                                                       |                                               |               |                   |                  |                  |               |  |  |  |  |

| bit 14        |                                                                                                                                                    | ne Enable bit                                 |               |                   |                  |                  |               |  |  |  |  |

|               |                                                                                                                                                    | s enabled; ARP<br>s disabled <sup>,</sup> ARP |               |                   |                  |                  |               |  |  |  |  |

| bit 13-10     | <ul> <li>0 = Chime is disabled; ARPT&lt;7:0&gt; bits stop once they reach 0x00</li> <li>AMASK&lt;3:0&gt;: Alarm Mask Configuration bits</li> </ul> |                                               |               |                   |                  |                  |               |  |  |  |  |

|               | 0000 = Every half second                                                                                                                           |                                               |               |                   |                  |                  |               |  |  |  |  |

|               | 0001 = Every second                                                                                                                                |                                               |               |                   |                  |                  |               |  |  |  |  |

|               |                                                                                                                                                    | y 10 seconds                                  |               |                   |                  |                  |               |  |  |  |  |

|               | 0011 = Ever                                                                                                                                        |                                               |               |                   |                  |                  |               |  |  |  |  |

|               | 0100 = Ever                                                                                                                                        |                                               |               |                   |                  |                  |               |  |  |  |  |

|               | 0110 = Once                                                                                                                                        |                                               |               |                   |                  |                  |               |  |  |  |  |

|               | 0111 = Once a week                                                                                                                                 |                                               |               |                   |                  |                  |               |  |  |  |  |

|               | 1000 = Once a month<br>1001 = Once a year (except when configured for February 29th, once every 4 years)                                           |                                               |               |                   |                  |                  |               |  |  |  |  |

|               |                                                                                                                                                    | e a year (excep<br>erved – do not ι           |               | ired for Februa   | iry 29th, once e | every 4 years)   |               |  |  |  |  |

|               |                                                                                                                                                    | erved – do not u                              |               |                   |                  |                  |               |  |  |  |  |

| bit 9-8       | ALRMPTR<                                                                                                                                           | 1:0>: Alarm Val                               | ue Register W | indow Pointer     | bits             |                  |               |  |  |  |  |

|               |                                                                                                                                                    |                                               | •             |                   |                  | RMVAL register   | . The         |  |  |  |  |