Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT   |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | -                                                                                 |

| Data Converters            | A/D 30x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm306t-i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 5 MHz < FIN < 13.6 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

### 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

### 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

- Dual motor control

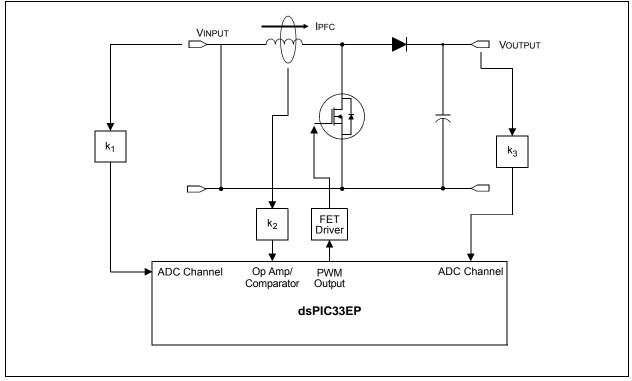

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

# **REGISTER 3-2:** CORCON: CORE CONTROL REGISTER<sup>(3)</sup> (CONTINUED)

| bit 3 | IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup><br>1 = CPU Interrupt Priority Level is greater than 7<br>0 = CPU Interrupt Priority Level is 7 or less                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | SFA: Stack Frame Active Status bit                                                                                                                                                                                |

|       | <ul> <li>1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and DSWPAG values</li> <li>0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space</li> </ul> |

| bit 1 | RND: Rounding Mode Select bit                                                                                                                                                                                     |

|       | <ul> <li>1 = Biased (conventional) rounding is enabled</li> <li>0 = Unbiased (convergent) rounding is enabled</li> </ul>                                                                                          |

| bit 0 | IF: Integer or Fractional Multiplier Mode Select bit                                                                                                                                                              |

|       | <ul><li>1 = Integer mode is enabled for DSP multiply</li><li>0 = Fractional mode is enabled for DSP multiply</li></ul>                                                                                            |

|       |                                                                                                                                                                                                                   |

- **Note 1:** This bit is always read as '0'.

- 2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

- 3: Refer to the "dsPIC33/PIC24 Family Reference Manual", "CPU" (DS70359) for more detailed information.

| TABLE 4-28: CAN2 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FOR dsPIC33EPXXXGM60X/7XX DEVICES <sup>(1)</sup> (CONTINUED | <b>TABLE 4-28</b> : | CAN2 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FO | )R dsPIC33EPXXXGM60X/7XX DEVICES <sup>(1)</sup> (CONTINUED) |

|--------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------|-------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------|-------------------------------------------------------------|

| SFR<br>Name | Addr.            | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|------------------|--------|--------|--------|--------|--------|--------|-------|-------|----------|-------|-------|-------|-------|-------|-------|-------|---------------|

| C2RXF11SID  | 056C             | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | _     | EXIDE | —     | EID17 | EID16 | xxxx          |

| C2RXF11EID  | D 056E EID<15:0> |        |        |        |        |        |        |       |       |          | xxxx  |       |       |       |       |       |       |               |

| C2RXF12SID  | 0570             | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | _     | MIDE  | _     | EID17 | EID16 | xxxx          |

| C2RXF12EID  | EID<15:0>        |        |        |        |        |        |        |       |       |          | xxxx  |       |       |       |       |       |       |               |

| C2RXF13SID  | 0574             | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | —     | MIDE  | —     | EID17 | EID16 | xxxx          |

| C2RXF13EID  | 0576             |        |        |        |        |        |        |       | E     | ID<15:0> |       |       |       |       |       |       |       | xxxx          |

| C2RXF14SID  | 0578             | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | —     | MIDE  | —     | EID17 | EID16 | xxxx          |

| C2RXF14EID  | D 057A EID<15:0> |        |        |        |        |        |        |       |       |          | xxxx  |       |       |       |       |       |       |               |

| C2RXF15SID  | 057C             | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | —     | MIDE  | _     | EID17 | EID16 | xxxx          |

| C2RXF15EID  | 057E             |        |        |        |        |        |        |       | E     | ID<15:0> |       |       |       |       |       |       |       | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers are not present on dsPIC33EPXXXGM3XX devices.

### TABLE 4-29: PROGRAMMABLE CRC REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 15         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         F |   |         |         |         |         |               |            |         | All<br>Resets |       |       |       |       |       |      |

|-------------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------|---------|---------|---------|---------------|------------|---------|---------------|-------|-------|-------|-------|-------|------|

| CRCCON1     | 0640  | CRCEN  | RCEN - CSIDL VWORD4 VWORD3 VWORD2 VWORD1 VWORD0 CRCFUL CRCMPT CRCISEL CRCGO LENDIAN 0                                                                                                                                    |   |         |         |         |         |               |            | 0000    |               |       |       |       |       |       |      |

| CRCCON2     | 0642  | _      | _                                                                                                                                                                                                                        | _ | DWIDTH4 | DWIDTH3 | DWIDTH2 | DWIDTH1 | DWIDTH0       | _          | _       | _             | PLEN4 | PLEN3 | PLEN2 | PLEN1 | PLEN0 | 0000 |

| CRCXORL     | 0644  |        | X<15:1> —                                                                                                                                                                                                                |   |         |         |         |         |               |            |         | 0000          |       |       |       |       |       |      |

| CRCXORH     | 0646  |        | X<31:16>                                                                                                                                                                                                                 |   |         |         |         |         |               |            |         | 0000          |       |       |       |       |       |      |

| CRCDATL     | 0648  |        |                                                                                                                                                                                                                          |   |         |         |         | CRC E   | Data Input Lo | w Word Re  | egister |               |       |       |       |       |       | 0000 |

| CRCDATH     | 064A  |        |                                                                                                                                                                                                                          |   |         |         |         | CRC D   | ata Input Hi  | gh Word Re | egister |               |       |       |       |       |       | 0000 |

| CRCWDATL    | 064C  |        | CRC Result Low Word Register                                                                                                                                                                                             |   |         |         |         |         |               |            |         | 0000          |       |       |       |       |       |      |

| CRCWDATH    | 064E  |        |                                                                                                                                                                                                                          |   |         |         |         | CRC     | Result High   | Word Reg   | ister   |               |       |       |       |       |       | 0000 |

**Legend:** — = unimplemented, read as '0'. Shaded bits are not used in the operation of the programmable CRC module.

### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0            | U-0 | U-0            | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-----|----------------|-------|--------------|------------------|--------|-------|

| —              |     | —              | —     | —            | —                | —      | —     |

| bit 15         |     |                |       |              |                  |        | bit 8 |

|                |     |                |       |              |                  |        |       |

| W-0            | W-0 | W-0            | W-0   | W-0          | W-0              | W-0    | W-0   |

|                |     |                | NVMKI | EY<7:0>      |                  |        |       |

| bit 7          |     |                |       |              |                  |        | bit 0 |

|                |     |                |       |              |                  |        |       |

| Legend:        |     |                |       |              |                  |        |       |

| R = Readable I | bit | W = Writable b | oit   | U = Unimpler | mented bit, read | as '0' |       |

|                |     |                |       |              |                  |        |       |

'0' = Bit is cleared

bit 15-8 Unimplemented: Read as '0'

-n = Value at POR

bit 7-0 NVMKEY<7:0>: NVM Key Register (write-only) bits

'1' = Bit is set

### REGISTER 5-5: NVMSRCADRH: NONVOLATILE DATA MEMORY UPPER ADDRESS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-x | R/W-x | R/W-x | R/W-x    | R/W-x      | R/W-x | R/W-x | R/W-x |

|-------|-------|-------|----------|------------|-------|-------|-------|

|       |       |       | NVMSRCAD | DRH<23:16> |       |       |       |

| bit 7 |       |       |          |            |       |       | bit 0 |

|       |       |       |          |            |       |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMSRCADRH<23:16>: Nonvolatile Data Memory Upper Address bits

x = Bit is unknown

# dsPIC33EPXXXGM3XX/6XX/7XX

FIGURE 7-1: dsPIC33EPXXXGM3XX/6XX/7XX INTERRUPT VECTOR TABLE

| <b>▲</b>                          | Reset – GOTO Instruction         | 0x000000 |                          |

|-----------------------------------|----------------------------------|----------|--------------------------|

|                                   | Reset – GOTO Address             | 0x000002 |                          |

| £                                 | Oscillator Fail Trap Vector      | 0x000004 |                          |

| rior                              | Address Error Trap Vector        | 0x000006 |                          |

| ር<br>አ                            | Generic Hard Trap Vector         | 0x000008 |                          |

| Orde                              | Stack Error Trap Vector          | 0x00000A |                          |

| ផ្ទ                               | Math Error Trap Vector           | 0x00000C |                          |

| atur                              | DMA Controller Error Trap Vector | 0x00000E |                          |

| ž b                               | Generic Soft Trap Vector         | 0x000010 |                          |

| Decreasing Natural Order Priority | Reserved                         | 0x000012 |                          |

| crea                              | Interrupt Vector 0               | 0x000014 |                          |

| Dec                               | Interrupt Vector 1               | 0x000016 |                          |

|                                   | :                                | :        |                          |

| ,                                 | :                                | :        |                          |

| ĭ                                 | :                                | :        |                          |

| 2                                 | Interrupt Vector 52              | 0x00007C |                          |

|                                   | Interrupt Vector 53              | 0x00007E |                          |

|                                   | Interrupt Vector 54              | 0x000080 | $\backslash$             |

|                                   | :                                | :        | See Table 7-1 for        |

|                                   | :                                | :        | Interrupt Vector Details |

|                                   | :                                | :        |                          |

|                                   | Interrupt Vector 116             | 0x0000FC |                          |

|                                   | Interrupt Vector 117             | 0x0000FE |                          |

|                                   | Interrupt Vector 118             | 0x000100 |                          |

|                                   | Interrupt Vector 119             | 0x000102 |                          |

|                                   | Interrupt Vector 120             | 0x000104 |                          |

|                                   | :                                | :        |                          |

|                                   | :                                | :        |                          |

|                                   | :                                | :        |                          |

| V                                 | Interrupt Vector 244             | 0x0001FC |                          |

|                                   | Interrupt Vector 245             | 0x0001FE | /                        |

|                                   | START OF CODE                    | 0x000200 |                          |

### REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

| U-0          | U-0                            | U-0                                                              | U-0                            | U-0                    | U-0              | U-0             | U-0   |

|--------------|--------------------------------|------------------------------------------------------------------|--------------------------------|------------------------|------------------|-----------------|-------|

| _            | _                              | —                                                                | _                              | —                      | _                | _               | _     |

| bit 15       | ·                              |                                                                  |                                |                        |                  |                 | bit 8 |

|              |                                |                                                                  |                                |                        |                  |                 |       |

| U-0          | U-0                            | U-0                                                              | U-0                            | R-1                    | R-1              | R-1             | R-1   |

| —            | —                              | —                                                                | _                              |                        | LSTCH            | <3:0>           |       |

| bit 7        |                                |                                                                  |                                |                        |                  |                 | bit 0 |

|              |                                |                                                                  |                                |                        |                  |                 |       |

| Legend:      |                                |                                                                  |                                |                        |                  |                 |       |

| R = Readab   | ole bit                        | W = Writable                                                     | bit                            | U = Unimpler           | mented bit, read | as '0'          |       |

| -n = Value a | at POR                         | '1' = Bit is set                                                 |                                | '0' = Bit is cle       | ared             | x = Bit is unkr | nown  |

|              |                                |                                                                  |                                |                        |                  |                 |       |

| bit 15-4     | Unimplemen                     | ted: Read as 'o                                                  | o'                             |                        |                  |                 |       |

| bit 3-0      | LSTCH<3:0>                     | : Last DMA Co                                                    | ntroller Chanr                 | nel Active Statu       | is bits          |                 |       |

|              | 1111 = No DI<br>1110 = Rese    | MA transfer has<br>rved                                          | s occurred sin                 | ice system Res         | set              |                 |       |

|              | •                              |                                                                  |                                |                        |                  |                 |       |

|              | •                              |                                                                  |                                |                        |                  |                 |       |

|              | •                              |                                                                  |                                |                        |                  |                 |       |

|              | 0010 = Last o<br>0001 = Last o | rved<br>data transfer wa<br>data transfer wa<br>data transfer wa | as handled by<br>as handled by | Channel 2<br>Channel 1 |                  |                 |       |

0000 = Last data transfer was handled by Channel 0

# **REGISTER 9-2:** CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup> (CONTINUED)

- **Note 1:** This bit is cleared when the ROI bit is set and an interrupt occurs.

- 2: This register resets only on a Power-on Reset (POR).

- **3:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- 4: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| Legend:<br>R = Readable | bit   | W = Writable | bit   | U = Unimplem | nented bit, read | l as '0' |       |

|-------------------------|-------|--------------|-------|--------------|------------------|----------|-------|

| bit 7                   |       |              |       |              |                  |          | bit 0 |

| OC8MD                   | OC7MD | OC6MD        | OC5MD | OC4MD        | OC3MD            | OC2MD    | OC1MD |

| R/W-0                   | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                         |       |              |       |              |                  |          |       |

| bit 15                  |       |              |       |              |                  |          | bit 8 |

| IC8MD                   | IC7MD | IC6MD        | IC5MD | IC4MD        | IC3MD            | IC2MD    | IC1MD |

| R/W-0                   | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                         |       |              |       |              |                  |          |       |

'0' = Bit is cleared

### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

bit 15-8 **IC8MD:IC1MD:** Input Capture x (x = 1-8) Module Disable bits

'1' = Bit is set

1 = Input Capture x module is disabled

-n = Value at POR

0 = Input Capture x module is enabled

bit 7-0 OC8MD:OC1MD: Output Compare x (x = 1-8) Module Disable bits

1 = Output Compare x module is disabled

0 = Output Compare x module is enabled

x = Bit is unknown

| U-0                                | R/W-0                                                                                  | R/W-0                                                                                    | R/W-0                                             | R/W-0                     | R/W-0           | R/W-0                               | R/W-0 |

|------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------|-----------------|-------------------------------------|-------|

| _                                  |                                                                                        |                                                                                          |                                                   | QEB2R<6:0>                | •               |                                     |       |

| bit 15                             | ·                                                                                      |                                                                                          |                                                   |                           |                 |                                     | bit 8 |

|                                    |                                                                                        |                                                                                          |                                                   |                           |                 |                                     |       |

| U-0                                | R/W-0                                                                                  | R/W-0                                                                                    | R/W-0                                             | R/W-0                     | R/W-0           | R/W-0                               | R/W-0 |

| —                                  |                                                                                        |                                                                                          |                                                   | QEA2R<6:0>                | •               |                                     |       |

| bit 7                              |                                                                                        |                                                                                          |                                                   |                           |                 |                                     | bit 0 |

|                                    |                                                                                        |                                                                                          |                                                   |                           |                 |                                     |       |

| Legend:                            |                                                                                        |                                                                                          |                                                   |                           |                 |                                     |       |

| R = Readabl                        | le bit                                                                                 | W = Writable                                                                             | bit                                               | U = Unimplen              | nented bit, rea | ad as '0'                           |       |

| -n = Value at POR '1' = Bit is set |                                                                                        |                                                                                          |                                                   | '0' = Bit is clea         | nown            |                                     |       |

| bit 14-8<br>bit 7<br>bit 6-0       | (see Table 1<br>1111111 = I<br>0000001 = I<br>0000000 = I<br>Unimplement<br>QEA2R<6:03 |                                                                                          | selection nur<br>127<br>P1<br>0'<br>I2 Phase A (C | nbers)<br>QEA2) to the Co |                 | n/RPIn Pin bits<br>RPn/RPIn Pin bit | s     |

|                                    | 1111111 =  <br>•<br>•<br>•<br>•<br>•<br>•                                              | 1-2 for input pin<br>nput tied to RP <sup>-</sup><br>nput tied to CM<br>nput tied to Vss | 127<br>P1                                         | nbers)                    |                 |                                     |       |

### REGISTER 11-12: RPINR16: PERIPHERAL PIN SELECT INPUT REGISTER 16

# REGISTER 16-11: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7-6 | 6  | <b>DTC&lt;1:0&gt;:</b> Dead-Time Control bits<br>11 = Dead-Time Compensation mode                                                                                                                                                                                                                                                  |

|---------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |    | <ul> <li>10 = Dead-time function is disabled</li> <li>01 = Negative dead time is actively applied for Complementary Output mode</li> <li>00 = Positive dead time is actively applied for all Output modes</li> </ul>                                                                                                               |

| bit 5   |    | <b>DTCP:</b> Dead-Time Compensation Polarity bit <sup>(3)</sup>                                                                                                                                                                                                                                                                    |

|         |    | <u>When Set to '⊥':</u><br>If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.<br>If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                                                                                                                                                |

|         |    | <u>When Set to '<math>o</math>':</u><br>If DTCMPx = 0, PWMHx is shortened and PWMLx is lengthened.<br>If DTCMPx = 1, PWMLx is shortened and PWMHx is lengthened.                                                                                                                                                                   |

| bit 4   |    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                         |

| bit 3   |    | MTBS: Master Time Base Select bit                                                                                                                                                                                                                                                                                                  |

|         |    | <ul> <li>1 = PWMx generator uses the secondary master time base for synchronization and as the clock source for the PWMx generation logic (if secondary time base is available)</li> <li>0 = PWMx generator uses the primary master time base for synchronization and as the clock source for the PWMx generation logic</li> </ul> |

| bit 2   |    | <b>CAM:</b> Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                                                                                                                                                                                                        |

|         |    | 1 = Center-Aligned mode is enabled                                                                                                                                                                                                                                                                                                 |

| bit 1   |    | 0 = Edge-Aligned mode is enabled<br><b>XPRES:</b> External PWMx Reset Control bit <sup>(5)</sup>                                                                                                                                                                                                                                   |

| DILI    |    | <ul> <li>1 = Current-limit source resets the time base for this PWMx generator if it is in Independent Time Base<br/>mode</li> </ul>                                                                                                                                                                                               |

| bit 0   |    | <ul> <li>0 = External pins do not affect the PWMx time base</li> <li>IUE: Immediate Update Enable bit<sup>(2)</sup></li> </ul>                                                                                                                                                                                                     |

| DILU    |    | <ul> <li>1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate</li> <li>0 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the PWMx period boundary</li> </ul>                                                                                                          |

| Note    | 1: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.                                                                                                                                                                                                                       |

|         | 2: | These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                                                                                                                                                                                                                             |

|         | 3: | DTC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored.                                                                                                                                                                                                                                                                |

|         | 4: | The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.                                                                                                                                                                                                           |

|         |    |                                                                                                                                                                                                                                                                                                                                    |

**5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

### REGISTER 17-17: INTxTMRH: INTERVAL TIMERx HIGH WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | INTTM | R<31:24>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INTTM | R<23:16>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|                 |       |                  |       |                  |                 |                 |       |

bit 15-0 INTTMR<31:16>: High Word Used to Form 32-Bit Interval Timerx Register (INTxTMR) bits

### REGISTER 17-18: INTxTMRL: INTERVAL TIMERx LOW WORD REGISTER

| R/W-0                                                                | R/W-0            | R/W-0       | R/W-0                                                       | R/W-0                                                                                              | R/W-0                                                                          | R/W-0                                                                                                                                                          |

|----------------------------------------------------------------------|------------------|-------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                      |                  | INTTM       | IR<15:8>                                                    |                                                                                                    |                                                                                |                                                                                                                                                                |

|                                                                      |                  |             |                                                             |                                                                                                    |                                                                                | bit 8                                                                                                                                                          |

|                                                                      |                  |             |                                                             |                                                                                                    |                                                                                |                                                                                                                                                                |

| R/W-0                                                                | R/W-0            | R/W-0       | R/W-0                                                       | R/W-0                                                                                              | R/W-0                                                                          | R/W-0                                                                                                                                                          |

|                                                                      |                  | INTT        | /IR<7:0>                                                    |                                                                                                    |                                                                                |                                                                                                                                                                |

|                                                                      |                  |             |                                                             |                                                                                                    |                                                                                | bit 0                                                                                                                                                          |

|                                                                      |                  |             |                                                             |                                                                                                    |                                                                                |                                                                                                                                                                |

|                                                                      |                  |             |                                                             |                                                                                                    |                                                                                |                                                                                                                                                                |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |             |                                                             |                                                                                                    |                                                                                |                                                                                                                                                                |

| OR                                                                   | '1' = Bit is set |             | '0' = Bit is cle                                            | ared                                                                                               | x = Bit is unkr                                                                | nown                                                                                                                                                           |

|                                                                      | R/W-0            | R/W-0 R/W-0 | INTTM<br>R/W-0 R/W-0 R/W-0<br>INTTM<br>Dit W = Writable bit | INTTMR<15:8>           R/W-0         R/W-0         R/W-0           INTTMR<7:0>         INTTMR<7:0> | INTTMR<15:8>           R/W-0         R/W-0         R/W-0           INTTMR<7:0> | INTTMR<15:8>         R/W-0       R/W-0       R/W-0       R/W-0         INTTMR<7:0>         Dit       W = Writable bit       U = Unimplemented bit, read as '0' |

bit 15-0 INTTMR<15:0>: Low Word Used to Form 32-Bit Interval Timerx Register (INTxTMR) bits

# 21.3 CAN Control Registers

### REGISTER 21-1: CxCTRL1: CANx CONTROL REGISTER 1

| U-0                                | U-0        | R/W-0           | R/W-0                                   | R/W-0        | R/W-1            | R/W-0    | R/W-0  |

|------------------------------------|------------|-----------------|-----------------------------------------|--------------|------------------|----------|--------|

| —                                  | —          | CSIDL           | ABAT                                    | CANCKS       | REQOP2           | REQOP1   | REQOP0 |

| bit 15                             |            |                 |                                         |              |                  |          | bit 8  |

|                                    |            |                 |                                         |              |                  |          |        |

| R-1                                | R-0        | R-0             | U-0                                     | R/W-0        | U-0              | U-0      | R/W-0  |

| OPMODE2                            | OPMODE1    | OPMODE0         | _                                       | CANCAP       | —                |          | WIN    |

| bit 7                              | •          |                 |                                         | •            |                  |          | bit 0  |

|                                    |            |                 |                                         |              |                  |          |        |

| Legend:                            |            |                 |                                         |              |                  |          |        |

| R = Readable I                     | bit        | W = Writable b  | pit                                     | U = Unimpler | nented bit, read | l as '0' |        |

| -n = Value at POR '1' = Bit is set |            |                 | '0' = Bit is cleared x = Bit is unknown |              |                  | nown     |        |

|                                    |            |                 |                                         |              |                  |          |        |

| bit 15-14                          | Unimplemen | ted: Read as '0 | )'                                      |              |                  |          |        |

| bit 13           | <b>CSIDL:</b> CANx Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode                                                                                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12           | <ul> <li>ABAT: Abort All Pending Transmissions bit</li> <li>1 = Signals all transmit buffers to abort transmission</li> <li>0 = Module will clear this bit when all transmissions are aborted</li> </ul>                                                                                                               |

| bit 11           | <b>CANCKS:</b> CANx Module Clock (FCAN) Source Select bit<br>1 = FCAN is equal to 2 * FP<br>0 = FCAN is equal to FP                                                                                                                                                                                                    |

| bit 10-8         | REQOP<2:0>: Request Operation Mode bits<br>111 = Set Listen All Messages mode<br>110 = Reserved<br>101 = Reserved<br>100 = Set Configuration mode<br>011 = Set Listen Only mode<br>010 = Set Loopback mode<br>001 = Set Disable mode<br>000 = Set Normal Operation mode                                                |

| bit 7-5          | OPMODE<2:0>: Operation Mode bits<br>111 = Module is in Listen All Messages mode<br>110 = Reserved<br>101 = Reserved<br>100 = Module is in Configuration mode<br>011 = Module is in Listen Only mode<br>010 = Module is in Loopback mode<br>001 = Module is in Disable mode<br>000 = Module is in Normal Operation mode |

| bit 4            | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                             |

| bit 3            | <b>CANCAP:</b> CANx Message Receive Timer Capture Event Enable bit<br>1 = Enables input capture based on CAN message receive<br>0 = Disables CAN capture                                                                                                                                                               |

| bit 2-1<br>bit 0 | Unimplemented: Read as '0'<br>WIN: SFR Map Window Select bit<br>1 = Uses filter window<br>0 = Uses buffer window                                                                                                                                                                                                       |

### REGISTER 21-24: CxRXOVF1: CANx RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0           | R/C-0 | R/C-0            | R/C-0            | R/C-0             | R/C-0           | R/C-0           | R/C-0 |  |

|-----------------|-------|------------------|------------------|-------------------|-----------------|-----------------|-------|--|

|                 |       |                  | RXOV             | F<15:8>           |                 |                 |       |  |

| bit 15          |       |                  |                  |                   |                 |                 | bit 8 |  |

|                 |       |                  |                  |                   |                 |                 |       |  |

| R/C-0           | R/C-0 | R/C-0            | R/C-0            | R/C-0             | R/C-0           | R/C-0           | R/C-0 |  |

| RXOVF<7:0>      |       |                  |                  |                   |                 |                 |       |  |

| bit 7           |       |                  |                  |                   |                 |                 | bit 0 |  |

|                 |       |                  |                  |                   |                 |                 |       |  |

| Legend:         |       | C = Writable b   | oit, but only '( | )' can be written | to clear the b  | it              |       |  |

| R = Readable    | bit   | W = Writable     | bit              | U = Unimplen      | nented bit, rea | d as '0'        |       |  |

| -n = Value at F | POR   | '1' = Bit is set |                  | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |

bit 15-0 **RXOVF<15:0>:** Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

### REGISTER 21-25: CxRXOVF2: CANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0                                                                  | R/C-0 | R/C-0            | R/C-0 | R/C-0             | R/C-0           | R/C-0           | R/C-0 |  |  |

|------------------------------------------------------------------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|--|--|

| RXOVF<31:24>                                                           |       |                  |       |                   |                 |                 |       |  |  |

| bit 15 bit 8                                                           |       |                  |       |                   |                 |                 |       |  |  |

|                                                                        |       |                  |       |                   |                 |                 |       |  |  |

| R/C-0                                                                  | R/C-0 | R/C-0            | R/C-0 | R/C-0             | R/C-0           | R/C-0           | R/C-0 |  |  |

| RXOVF<23:16>                                                           |       |                  |       |                   |                 |                 |       |  |  |

| bit 7 bit 0                                                            |       |                  |       |                   |                 |                 |       |  |  |

|                                                                        |       |                  |       |                   |                 |                 |       |  |  |

| Legend: C = Writable bit, but only '0' can be written to clear the bit |       |                  |       |                   |                 |                 |       |  |  |

| R = Readable                                                           | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, rea | d as '0'        |       |  |  |

| -n = Value at P                                                        | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |

| •                                                                      |       |                  |       |                   |                 |                 |       |  |  |

bit 15-0 RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

| R/W-0         | R/W-0                                              | R/W-0                          | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0    |  |  |  |

|---------------|----------------------------------------------------|--------------------------------|-----------------|-------------------|------------------|-----------------|----------|--|--|--|

| EDG1MOD       | EDG1POL                                            | EDG1SEL3                       | EDG1SEL2        | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT |  |  |  |

| bit 15        | •                                                  | •                              |                 | •                 | •                |                 | bit 8    |  |  |  |

|               |                                                    |                                |                 |                   |                  |                 |          |  |  |  |

| R/W-0         | R/W-0                                              | R/W-0                          | R/W-0           | R/W-0             | R/W-0            | U-0             | U-0      |  |  |  |

| EDG2MOD       | EDG2POL                                            | EDG2SEL3                       | EDG2SEL2        | EDG2SEL1          | EDG2SEL0         | —               | —        |  |  |  |

| bit 7         | •                                                  | •                              |                 | •                 | •                |                 | bit 0    |  |  |  |

|               |                                                    |                                |                 |                   |                  |                 |          |  |  |  |

| Legend:       |                                                    |                                |                 |                   |                  |                 |          |  |  |  |

| R = Readable  | bit                                                | W = Writable                   | oit             | U = Unimplem      | nented bit, read | l as '0'        |          |  |  |  |

| -n = Value at | POR                                                | '1' = Bit is set               |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |  |  |  |

|               |                                                    |                                |                 |                   |                  |                 |          |  |  |  |

| bit 15        | EDG1MOD: E                                         | Edge 1 Edge Sa                 | ampling Mode    | Selection bit     |                  |                 |          |  |  |  |

|               | •                                                  | edge-sensitive                 |                 |                   |                  |                 |          |  |  |  |

|               | •                                                  | level-sensitive                |                 |                   |                  |                 |          |  |  |  |

| bit 14        |                                                    | dge 1 Polarity                 |                 |                   |                  |                 |          |  |  |  |

|               |                                                    | programmed f<br>programmed f   |                 |                   |                  |                 |          |  |  |  |

| bit 13-10     | -                                                  | :0>: Edge 1 So                 | -               |                   |                  |                 |          |  |  |  |

| DIL 13-10     | 1111 = Fosc                                        | <b>0&gt;.</b> Euge 130         |                 | 5                 |                  |                 |          |  |  |  |

|               | 1110 = OSCI                                        | pin                            |                 |                   |                  |                 |          |  |  |  |

|               | 1101 = FRC oscillator                              |                                |                 |                   |                  |                 |          |  |  |  |

|               | 1100 = Reserved<br>1011 = Internal LPRC oscillator |                                |                 |                   |                  |                 |          |  |  |  |

|               | 1011 = Intern<br>1010 = Reser                      |                                | itor            |                   |                  |                 |          |  |  |  |

|               | 1010 = Reser<br>100x = Reser                       |                                |                 |                   |                  |                 |          |  |  |  |

|               | 01xx = Reser                                       |                                |                 |                   |                  |                 |          |  |  |  |

|               | 0011 = CTED                                        |                                |                 |                   |                  |                 |          |  |  |  |

|               | 0010 = CTED<br>0001 = OC1 r                        | •                              |                 |                   |                  |                 |          |  |  |  |

|               | 0001 = OCT1                                        |                                |                 |                   |                  |                 |          |  |  |  |

| bit 9         |                                                    | Edge 2 Status b                | it              |                   |                  |                 |          |  |  |  |

|               |                                                    | -                              |                 | vritten to contro | I the edge sou   | rce.            |          |  |  |  |

|               | 1 = Edge 2 h                                       | as occurred                    |                 |                   | 0                |                 |          |  |  |  |

|               | 0 = Edge 2 ha                                      | as not occurred                | 1               |                   |                  |                 |          |  |  |  |

| bit 8         |                                                    | Edge 1 Status b                |                 |                   |                  |                 |          |  |  |  |

|               |                                                    | -                              | 1 and can be v  | vritten to contro | ol the edge sour | rce.            |          |  |  |  |

|               | 1 = Edge 1 ha                                      | as occurred<br>as not occurred | I               |                   |                  |                 |          |  |  |  |

| bit 7         | •                                                  | Edge 2 Edge Sa                 |                 | Selection bit     |                  |                 |          |  |  |  |

|               |                                                    | edge-sensitive                 |                 |                   |                  |                 |          |  |  |  |

|               | -                                                  | level-sensitive                |                 |                   |                  |                 |          |  |  |  |

| bit 6         | EDG2POL: E                                         | dge 2 Polarity                 | Select bit      |                   |                  |                 |          |  |  |  |

|               |                                                    | programmed f                   |                 |                   |                  |                 |          |  |  |  |

|               | 0 = Edge 2 is                                      | programmed f                   | or a negative e | edge response     |                  |                 |          |  |  |  |

|               | he TGEN bit is<br>0G2SELx bits fi                  |                                |                 |                   | selected as the  | e Edge 2 sourc  | e in the |  |  |  |

### REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

| R/W-0                 | U-0                                                                                                       | U-0                                                                                               | R/W-0                                              | R/W-0                           | R/W-0                | R/W-0                | R/W-0                |

|-----------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------|----------------------|----------------------|----------------------|

| ADRC                  | _                                                                                                         |                                                                                                   | SAMC4 <sup>(1)</sup>                               | SAMC3 <sup>(1)</sup>            | SAMC2 <sup>(1)</sup> | SAMC1 <sup>(1)</sup> | SAMC0 <sup>(1)</sup> |

| bit 15                |                                                                                                           | ·                                                                                                 | •                                                  |                                 |                      |                      | bit 8                |

| R/W-0                 | R/W-0                                                                                                     | R/W-0                                                                                             | R/W-0                                              | R/W-0                           | R/W-0                | R/W-0                | R/W-0                |

| ADCS7(2)              | ADCS6 <sup>(2)</sup>                                                                                      | ADCS5 <sup>(2)</sup>                                                                              | ADCS4 <sup>(2)</sup>                               | ADCS3 <sup>(2)</sup>            | ADCS2 <sup>(2)</sup> | ADCS1 <sup>(2)</sup> | ADCS0 <sup>(2)</sup> |

| bit 7                 |                                                                                                           |                                                                                                   |                                                    |                                 |                      |                      | bit (                |

| Legend:               |                                                                                                           |                                                                                                   |                                                    |                                 |                      |                      |                      |

| R = Readable          | e bit                                                                                                     | W = Writable I                                                                                    | bit                                                | U = Unimplen                    | nented bit, read     | d as '0'             |                      |

| -n = Value at         | POR                                                                                                       | '1' = Bit is set                                                                                  |                                                    | '0' = Bit is cle                | ared                 | x = Bit is unkr      | nown                 |

| bit 14-13<br>bit 12-8 | Unimplemen                                                                                                | ived from syste<br>ted: Read as '(<br>Auto-Sample T<br>AD                                         | )'                                                 |                                 |                      |                      |                      |

|                       | •<br>•<br>00001 = 1 TA<br>00000 = 0 TA                                                                    | D                                                                                                 |                                                    |                                 |                      |                      |                      |

| bit 7-0               | 11111111 =<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ADCx Convers<br>TP • (ADCS<7:<br>TP • (ADCS<7:<br>TP • (ADCS<7:<br>TP • (ADCS<7:<br>TP • (ADCS<7: | 0> + 1) = TP •<br>0> + 1) = TP •<br>0> + 1) = TP • | 256 = Tad<br>3 = Tad<br>2 = Tad |                      |                      |                      |

|                       | nis bit is only use<br>nis bit is not usec                                                                |                                                                                                   | •                                                  | ,                               | nd SSRCG (AD         | 1CON1<4>) =          | 0.                   |

| REGISTER 23-3: ADXCONS: ADCX CONTROL REGISTER 3 | REGISTER 23-3: | ADxCON3: ADCx CONTROL REGISTER 3 |

|-------------------------------------------------|----------------|----------------------------------|

|-------------------------------------------------|----------------|----------------------------------|

Г

| АС СНА       | ARACTERIS | STICS                                   | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                        |      | or Industrial |       |                                                                            |

|--------------|-----------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|---------------|-------|----------------------------------------------------------------------------|

| Param<br>No. | Symbol    | Charac                                  | teristic <sup>(1)</sup>                                                                                                                                                                              | Min.                                   | Тур. | Max.          | Units | Conditions                                                                 |

| TB10         | ТтхН      | TxCK High<br>Time                       | Synchronous<br>mode                                                                                                                                                                                  | Greater of:<br>20 or<br>(Tcy + 20)/N   |      |               | ns    | Must also meet<br>Parameter TB15,<br>N = Prescale value<br>(1, 8, 64, 256) |

| TB11         | ΤτxL      | TxCK Low<br>Time                        | Synchronous<br>mode                                                                                                                                                                                  | Greater of:<br>20 or<br>(Tcy + 20)/N   |      |               | ns    | Must also meet<br>Parameter TB15,<br>N = Prescale value<br>(1, 8, 64, 256) |

| TB15         | ΤτχΡ      | TxCK Input<br>Period                    | Synchronous<br>mode                                                                                                                                                                                  | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _    | _             | ns    | N = Prescale value<br>(1, 8, 64, 256)                                      |

| TB20         | TCKEXTMRL | Delay from E<br>Clock Edge<br>Increment | External TxCK<br>to Timer                                                                                                                                                                            | 0.75 Tcy + 40                          |      | 1.75 Tcy + 40 | ns    |                                                                            |

#### TABLE 33-23: TIMER2 AND TIMER4 (TYPE B TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS . .

... ~ ....

. ....

.

.

Note 1: These parameters are characterized, but are not tested in manufacturing.