Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm310-e-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **REGISTER 3-2:** CORCON: CORE CONTROL REGISTER<sup>(3)</sup> (CONTINUED)

| bit 3 | IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup><br>1 = CPU Interrupt Priority Level is greater than 7<br>0 = CPU Interrupt Priority Level is 7 or less                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | SFA: Stack Frame Active Status bit                                                                                                                                                                                |

|       | <ul> <li>1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and DSWPAG values</li> <li>0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space</li> </ul> |

| bit 1 | RND: Rounding Mode Select bit                                                                                                                                                                                     |

|       | <ul> <li>1 = Biased (conventional) rounding is enabled</li> <li>0 = Unbiased (convergent) rounding is enabled</li> </ul>                                                                                          |

| bit 0 | IF: Integer or Fractional Multiplier Mode Select bit                                                                                                                                                              |

|       | <ul><li>1 = Integer mode is enabled for DSP multiply</li><li>0 = Fractional mode is enabled for DSP multiply</li></ul>                                                                                            |

|       |                                                                                                                                                                                                                   |

- **Note 1:** This bit is always read as '0'.

- 2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

- 3: Refer to the "dsPIC33/PIC24 Family Reference Manual", "CPU" (DS70359) for more detailed information.

| IABLE 4     | 4-0:  | 00                                    | IPUIC                               |          |         | SIER W  | AP      |       |            |             |               |        |          |          |          |          |          |               |

|-------------|-------|---------------------------------------|-------------------------------------|----------|---------|---------|---------|-------|------------|-------------|---------------|--------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15                                | Bit 14                              | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8      | Bit 7       | Bit 6         | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| OC1CON1     | 0900  | _                                     | —                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | ENFLTB     | ENFLTA      | —             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2     | 0902  | FLTMD                                 | FLTOUT                              | FLTTRIEN | OCINV   | —       | _       | _     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS       | 0904  |                                       |                                     |          |         |         |         | Ou    | Itput Comp | are 1 Seco  | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC1R        | 0906  |                                       |                                     |          |         |         |         |       | Output     | Compare 7   | 1 Register    |        |          |          |          |          |          | xxxx          |

| OC1TMR      | 0908  |                                       |                                     |          |         |         |         | Out   | tput Comp  | are 1 Time  | r Value Regis | ster   |          |          |          |          |          | xxxx          |

| OC2CON1     | 090A  | _                                     | —                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | ENFLTB     | ENFLTA      | -             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC2CON2     | 090C  | FLTMD                                 | FLTOUT                              | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS       | 090E  |                                       |                                     |          |         |         |         | Ou    | Itput Comp | oare 2 Seco | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC2R        | 0910  |                                       |                                     |          |         |         |         |       | Output     | Compare 2   | 2 Register    |        |          |          |          |          |          | xxxx          |

| OC2TMR      | 0912  |                                       |                                     |          |         |         | -       | Ou    | tput Comp  | are 2 Time  | r Value Regis | ster   |          | -        |          |          |          | xxxx          |

| OC3CON1     | 0914  | —                                     | _                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2     | 0916  | FLTMD                                 | FLTOUT                              | FLTTRIEN | OCINV   | _       | —       | _     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS       | 0918  |                                       |                                     |          |         |         |         | Ou    | tput Comp  | are 3 Seco  | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC3R        | 091A  |                                       |                                     |          |         |         |         |       | Output     | Compare 3   | 3 Register    |        |          |          |          |          |          | xxxx          |

| OC3TMR      | 091C  |                                       |                                     |          |         |         | -       | Ou    | tput Comp  | are 3 Time  | r Value Regis | ster   |          | -        |          |          |          | xxxx          |

| OC4CON1     | 091E  | —                                     | _                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC4CON2     | 0920  | FLTMD                                 | FLTOUT                              | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC4RS       | 0922  |                                       |                                     |          |         |         |         | Ou    | tput Comp  | oare 4 Seco | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC4R        | 0924  |                                       |                                     |          |         |         |         |       | Output     | Compare 4   | 4 Register    |        |          |          |          |          |          | xxxx          |

| OC4TMR      | 0926  |                                       |                                     |          |         |         |         | Ou    | tput Comp  | are 4 Time  | r Value Regis | ster   |          |          |          |          |          | xxxx          |

| OC5CON1     | 0928  |                                       | _                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC5CON2     | 092A  | FLTMD                                 | FLTOUT                              | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC5RS       | 092C  |                                       |                                     |          |         |         |         | Ou    | tput Comp  | are 5 Seco  | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC5R        | 092E  |                                       |                                     |          |         |         |         |       | Output     | Compare &   | 5 Register    |        |          |          |          |          |          | xxxx          |

| OC5TMR      | 0930  |                                       |                                     |          |         |         |         | Ou    | tput Comp  | are 5 Time  | r Value Regis | ster   |          |          |          |          |          | xxxx          |

| OC6CON1     | 0932  | —                                     | —                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC6CON2     | 0934  | FLTMD                                 | FLTOUT                              | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC6RS       | 0936  |                                       | Output Compare 6 Secondary Register |          |         |         |         |       |            |             |               |        | xxxx     |          |          |          |          |               |

| OC6R        | 0938  |                                       |                                     |          |         |         |         |       | Output     | Compare 6   | 6 Register    |        |          |          |          |          |          | xxxx          |

| OC6TMR      | 093A  | Output Compare 6 Timer Value Register |                                     |          |         |         |         |       |            |             | xxxx          |        |          |          |          |          |          |               |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Interrupts" (DS70000600), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGM3XX/6XX/7XX CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- · Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- · Fixed priority within a specified user priority level

- · Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The dsPIC33EPXXXGM3XX/6XX/7XX Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory, starting at location, 000004h. The IVT contains seven non-maskable trap vectors and up to 151 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGM3XX/6XX/7XX devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| TABLE 7-1: INTERRUPT VECTOR DETAILS |

|-------------------------------------|

|-------------------------------------|

|                                          | Vector | IRQ        |                  | Inte     | Interrupt Bit Location |             |  |  |

|------------------------------------------|--------|------------|------------------|----------|------------------------|-------------|--|--|

| Interrupt Source                         | #      | #          | IVT Address      | Flag     | Enable                 | Priority    |  |  |

|                                          | Highe  | est Natura | I Order Priority |          |                        |             |  |  |

| INT0 – External Interrupt 0              | 8      | 0          | 0x000014         | IFS0<0>  | IEC0<0>                | IPC0<2:0>   |  |  |

| IC1 – Input Capture 1                    | 9      | 1          | 0x000016         | IFS0<1>  | IEC0<1>                | IPC0<6:4>   |  |  |

| OC1 – Output Compare 1                   | 10     | 2          | 0x000018         | IFS0<2>  | IEC0<2>                | IPC0<10:8>  |  |  |

| T1 – Timer1                              | 11     | 3          | 0x00001A         | IFS0<3>  | IEC0<3>                | IPC0<14:12> |  |  |

| DMA0 – DMA Channel 0                     | 12     | 4          | 0x00001C         | IFS0<4>  | IEC0<4>                | IPC1<2:0>   |  |  |

| IC2 – Input Capture 2                    | 13     | 5          | 0x00001E         | IFS0<5>  | IEC0<5>                | IPC1<6:4>   |  |  |

| OC2 – Output Compare 2                   | 14     | 6          | 0x000020         | IFS0<6>  | IEC0<6>                | IPC1<10:8>  |  |  |

| T2 – Timer2                              | 15     | 7          | 0x000022         | IFS0<7>  | IEC0<7>                | IPC1<14:12> |  |  |

| T3 – Timer3                              | 16     | 8          | 0x000024         | IFS0<8>  | IEC0<8>                | IPC2<2:0>   |  |  |

| SPI1E – SPI1 Error                       | 17     | 9          | 0x000026         | IFS0<9>  | IEC0<9>                | IPC2<6:4>   |  |  |

| SPI1 – SPI1 Transfer Done                | 18     | 10         | 0x000028         | IFS0<10> | IEC0<10>               | IPC2<10:8>  |  |  |

| U1RX – UART1 Receiver                    | 19     | 11         | 0x00002A         | IFS0<11> | IEC0<11>               | IPC2<14:12> |  |  |

| U1TX – UART1 Transmitter                 | 20     | 12         | 0x00002C         | IFS0<12> | IEC0<12>               | IPC3<2:0>   |  |  |

| AD1 – ADC1 Convert Done                  | 21     | 13         | 0x00002E         | IFS0<13> | IEC0<13>               | IPC3<6:4>   |  |  |

| DMA1 – DMA Channel 1                     | 22     | 14         | 0x000030         | IFS0<14> | IEC0<14>               | IPC3<10:8>  |  |  |

| Reserved                                 | 23     | 15         | 0x000032         | _        | _                      |             |  |  |

| SI2C1 – I2C1 Slave Event                 | 24     | 16         | 0x000034         | IFS1<0>  | IEC1<0>                | IPC4<2:0>   |  |  |

| MI2C1 – I2C1 Master Event                | 25     | 17         | 0x000036         | IFS1<1>  | IEC1<1>                | IPC4<6:4>   |  |  |

| CMP1 – Comparator Combined Event         | 26     | 18         | 0x000038         | IFS1<2>  | IEC1<2>                | IPC4<10:8>  |  |  |

| CN – Input Change Interrupt              | 27     | 19         | 0x00003A         | IFS1<3>  | IEC1<3>                | IPC4<14:12> |  |  |

| INT1 – External Interrupt 1              | 28     | 20         | 0x00003C         | IFS1<4>  | IEC1<4>                | IPC5<2:0>   |  |  |

| AD2 – ADC2 Convert Done                  | 29     | 21         | 0x00003E         | IFS1<5>  | IEC1<5>                | IPC5<6:4>   |  |  |

| IC7 – Input Capture 7                    | 30     | 22         | 0x000040         | IFS1<6>  | IEC1<6>                | IPC5<10:8>  |  |  |

| IC8 – Input Capture 8                    | 31     | 23         | 0x000042         | IFS1<7>  | IEC1<7>                | IPC5<14:12> |  |  |

| DMA2 – DMA Channel 2                     | 32     | 24         | 0x000044         | IFS1<8>  | IEC1<8>                | IPC6<2:0>   |  |  |

| OC3 – Output Compare 3                   | 33     | 25         | 0x000046         | IFS1<9>  | IEC1<9>                | IPC6<6:4>   |  |  |

| OC4 – Output Compare 4                   | 34     | 26         | 0x000048         | IFS1<10> | IEC1<10>               | IPC6<10:8>  |  |  |

| T4 – Timer4                              | 35     | 27         | 0x00004A         | IFS1<11> | IEC1<11>               | IPC6<14:12> |  |  |

| T5 – Timer5                              | 36     | 28         | 0x00004C         | IFS1<12> | IEC1<12>               | IPC7<2:0>   |  |  |

| INT2 – External Interrupt 2              | 37     | 29         | 0x00004E         | IFS1<13> | IEC1<13>               | IPC7<6:4>   |  |  |

| U2RX – UART2 Receiver                    | 38     | 30         | 0x000050         | IFS1<14> | IEC1<14>               | IPC7<10:8>  |  |  |

| U2TX – UART2 Transmitter                 | 39     | 31         | 0x000052         | IFS1<15> | IEC1<15>               | IPC7<14:12> |  |  |

| SPI2E – SPI2 Error                       | 40     | 32         | 0x000054         | IFS2<0>  | IEC2<0>                | IPC8<2:0>   |  |  |

| SPI2 – SPI2 Transfer Done                | 41     | 33         | 0x000056         | IFS2<1>  | IEC2<1>                | IPC8<6:4>   |  |  |

| C1RX – CAN1 RX Data Ready <sup>(1)</sup> | 42     | 34         | 0x000058         | IFS2<2>  | IEC2<2>                | IPC8<10:8>  |  |  |

| C1 – CAN1 Event <sup>(1)</sup>           | 43     | 35         | 0x00005A         | IFS2<3>  | IEC2<3>                | IPC8<14:12> |  |  |

| DMA3 – DMA Channel 3                     | 44     | 36         | 0x00005C         | IFS2<4>  | IEC2<4>                | IPC9<2:0>   |  |  |

| IC3 – Input Capture 3                    | 45     | 37         | 0x00005E         | IFS2<5>  | IEC2<5>                | IPC9<6:4>   |  |  |

| IC4 – Input Capture 4                    | 46     | 38         | 0x000060         | IFS2<6>  | IEC2<6>                | IPC9<10:8>  |  |  |

| IC5 – Input Capture 5                    | 47     | 39         | 0x000062         | IFS2<7>  | IEC2<7>                | IPC9<14:12> |  |  |

| IC6 – Input Capture 6                    | 48     | 40         | 0x000064         | IFS2<8>  | IEC2<8>                | IPC10<2:0>  |  |  |

Note 1: This interrupt source is available on dsPIC33EPXXXGM6XX/7XX devices only.

2: This interrupt source is not available on 44-pin devices.

| R/W-1        | R/W-0           | R/W-0                                                       | U-0        | U-0              | U-0              | U-0             | U-0    |  |  |  |  |  |

|--------------|-----------------|-------------------------------------------------------------|------------|------------------|------------------|-----------------|--------|--|--|--|--|--|

| GIE          | DISI            | SWTRAP                                                      |            | —                |                  | —               |        |  |  |  |  |  |

| bit 15       |                 |                                                             |            |                  |                  |                 | bit 8  |  |  |  |  |  |

|              |                 |                                                             |            |                  |                  |                 |        |  |  |  |  |  |

| U-0          | U-0             | U-0                                                         | U-0        | U-0              | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

|              | —               | —                                                           | —          | —                | INT2EP           | INT1EP          | INT0EP |  |  |  |  |  |

| bit 7        |                 |                                                             |            |                  |                  |                 | bit 0  |  |  |  |  |  |

| 1            |                 |                                                             |            |                  |                  |                 |        |  |  |  |  |  |

| Legend:      | 1- 1-14         |                                                             | - :4       |                  |                  | (0)             |        |  |  |  |  |  |

| R = Readab   |                 | W = Writable I                                              | JIC        | -                | mented bit, read |                 |        |  |  |  |  |  |

| -n = Value a | t POR           | '1' = Bit is set                                            |            | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |  |  |  |  |

| bit 15       |                 | ntorrunt Enchla                                             | hit        |                  |                  |                 |        |  |  |  |  |  |

| DIC 15       |                 | nterrupt Enable<br>and associate                            |            | re enabled       |                  |                 |        |  |  |  |  |  |

|              |                 | are disabled, t                                             |            |                  |                  |                 |        |  |  |  |  |  |

| bit 14       | DISI: DISI In   | struction Statu                                             | s bit      |                  |                  |                 |        |  |  |  |  |  |

|              |                 | truction is active                                          |            |                  |                  |                 |        |  |  |  |  |  |

|              |                 | truction is not a                                           |            |                  |                  |                 |        |  |  |  |  |  |

| bit 13       |                 | SWTRAP: Software Trap Status bit                            |            |                  |                  |                 |        |  |  |  |  |  |

|              |                 | trap is enabled<br>trap is disabled                         |            |                  |                  |                 |        |  |  |  |  |  |

| bit 12-3     |                 | ted: Read as '                                              |            |                  |                  |                 |        |  |  |  |  |  |

| bit 2        | -               |                                                             |            | t Polarity Selec | t bit            |                 |        |  |  |  |  |  |

|              |                 | on negative edg                                             | •          | ,                |                  |                 |        |  |  |  |  |  |

|              | 0 = Interrupt o | on positive edg                                             | e          |                  |                  |                 |        |  |  |  |  |  |

| bit 1        | INT1EP: Exte    | IT1EP: External Interrupt 1 Edge Detect Polarity Select bit |            |                  |                  |                 |        |  |  |  |  |  |

|              |                 | on negative edg                                             |            |                  |                  |                 |        |  |  |  |  |  |

| bit 0        | INTOEP: Exte    | ernal Interrupt 0                                           | Edge Detec | t Polarity Selec | t bit            |                 |        |  |  |  |  |  |

|              |                 | on negative edg                                             |            |                  |                  |                 |        |  |  |  |  |  |

|              | 0 = Interrupt o | on positive edg                                             | e          |                  |                  |                 |        |  |  |  |  |  |

|              |                 |                                                             |            |                  |                  |                 |        |  |  |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| U-0              | U-0 | U-0              | U-0   | U-0     | U-0             | U-0    | U-0   |

|------------------|-----|------------------|-------|---------|-----------------|--------|-------|

| —                | _   | —                |       | _       | —               | _      | —     |

| bit 15           |     |                  |       |         |                 |        | bit 8 |

|                  |     |                  |       |         |                 |        |       |

| R-0              | R-0 | R-0              | R-0   | R-0     | R-0             | R-0    | R-0   |

|                  |     |                  | DSADR | <23:16> |                 |        |       |

| bit 7            |     |                  |       |         |                 |        | bit 0 |

|                  |     |                  |       |         |                 |        |       |

| Legend:          |     |                  |       |         |                 |        |       |

| P - Peadable bit |     | M = M/ritable bi | t     |         | monted hit read | ae 'O' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

### REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0                                                                        | R-0 | R-0 | R-0  | R-0     | R-0 | R-0 | R-0   |  |  |  |

|----------------------------------------------------------------------------|-----|-----|------|---------|-----|-----|-------|--|--|--|

| DSADR<15:8>                                                                |     |     |      |         |     |     |       |  |  |  |

| bit 15                                                                     |     |     |      |         |     |     | bit 8 |  |  |  |

|                                                                            |     |     |      |         |     |     |       |  |  |  |

| R-0                                                                        | R-0 | R-0 | R-0  | R-0     | R-0 | R-0 | R-0   |  |  |  |

|                                                                            |     |     | DSAD | )R<7:0> |     |     |       |  |  |  |

| bit 7                                                                      |     |     |      |         |     |     | bit 0 |  |  |  |

|                                                                            |     |     |      |         |     |     |       |  |  |  |

| Legend:                                                                    |     |     |      |         |     |     |       |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |     |     |      |         |     |     |       |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |     |     |      |         |     | own |       |  |  |  |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

| Legend:<br>R = Readable bit W = Writable bit |       |       | bit   | U = Unimplem | nented bit, read | l as '0' |       |

|----------------------------------------------|-------|-------|-------|--------------|------------------|----------|-------|

| bit 7                                        |       |       |       |              |                  |          | bit 0 |

| OC8MD                                        | OC7MD | OC6MD | OC5MD | OC4MD        | OC3MD            | OC2MD    | OC1MD |

| R/W-0                                        | R/W-0 | R/W-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                                              |       |       |       |              |                  |          |       |

| bit 15                                       |       |       |       |              |                  |          | bit 8 |

| IC8MD                                        | IC7MD | IC6MD | IC5MD | IC4MD        | IC3MD            | IC2MD    | IC1MD |

| R/W-0                                        | R/W-0 | R/W-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                                              |       |       |       |              |                  |          |       |

'0' = Bit is cleared

#### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

bit 15-8 **IC8MD:IC1MD:** Input Capture x (x = 1-8) Module Disable bits

'1' = Bit is set

1 = Input Capture x module is disabled

-n = Value at POR

0 = Input Capture x module is enabled

bit 7-0 OC8MD:OC1MD: Output Compare x (x = 1-8) Module Disable bits

1 = Output Compare x module is disabled

0 = Output Compare x module is enabled

x = Bit is unknown

| U-0          | U-0                | U-0                                                          | U-0   | U-0                                     | U-0              | U-0             | U-0   |

|--------------|--------------------|--------------------------------------------------------------|-------|-----------------------------------------|------------------|-----------------|-------|

| _            | _                  | _                                                            | —     |                                         | _                | _               | _     |

| bit 15       |                    |                                                              |       |                                         |                  |                 | bit 8 |

|              |                    |                                                              |       |                                         |                  |                 |       |

| U-0          | R/W-0              | R/W-0                                                        | R/W-0 | R/W-0                                   | R/W-0            | R/W-0           | R/W-0 |

| _            | T2CKR<6:0>         |                                                              |       |                                         |                  |                 |       |

| bit 7        | ·                  |                                                              |       |                                         |                  |                 | bit 0 |

|              |                    |                                                              |       |                                         |                  |                 |       |

| Legend:      |                    |                                                              |       |                                         |                  |                 |       |

| R = Readat   | ole bit            | W = Writable                                                 | bit   | U = Unimpler                            | nented bit, read | d as '0'        |       |

| -n = Value a | at POR             | '1' = Bit is set                                             |       | '0' = Bit is cleared x = Bit is unknown |                  |                 |       |

|              |                    |                                                              |       |                                         |                  |                 |       |

| bit 15-7     | Unimplemer         | nted: Read as '                                              | 0'    |                                         |                  |                 |       |

| bit 6-0      |                    | <ul> <li>Assign Timer.</li> <li>1-2 for input pin</li> </ul> |       | · /                                     | he Correspondi   | ng RPn pin bits | 3     |

|              | 1111100 <b>=  </b> | nput tied to RPI                                             | 124   |                                         |                  |                 |       |

|              | •                  |                                                              |       |                                         |                  |                 |       |

|              | •                  |                                                              |       |                                         |                  |                 |       |

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

© 2013-2014 Microchip Technology Inc.

| U-0               | U-0                                                         | U-0                                                                      | U-0                                                           | U-0                                | U-0   | U-0                | U-0   |  |

|-------------------|-------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------|-------|--------------------|-------|--|

| —                 | —                                                           | —                                                                        | _                                                             | —                                  | —     | —                  | —     |  |

| bit 15            | ·                                                           |                                                                          |                                                               | · · · ·                            |       | ·                  | bit 8 |  |

|                   |                                                             |                                                                          |                                                               |                                    |       |                    |       |  |

| U-0               | R/W-0                                                       | R/W-0                                                                    | R/W-0                                                         | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |

|                   |                                                             |                                                                          |                                                               | SS2R<6:0>                          |       |                    |       |  |

| bit 7             | ·                                                           |                                                                          |                                                               |                                    |       |                    | bit 0 |  |

|                   |                                                             |                                                                          |                                                               |                                    |       |                    |       |  |

| Legend:           |                                                             |                                                                          |                                                               |                                    |       |                    |       |  |

| R = Readat        | ole bit                                                     | W = Writable                                                             | bit                                                           | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value at POR |                                                             | (4) = D                                                                  |                                                               | '0' = Bit is clea                  | arad  | x = Bit is unknown |       |  |

|                   | at POR                                                      | '1' = Bit is set                                                         |                                                               | U = BIL IS CIER                    | areu  | X – DILIS ULIKI    | IOWI  |  |

|                   | at POR                                                      | I = BILIS Set                                                            |                                                               |                                    | areu  |                    | IOWI  |  |

| bit 15-7          |                                                             | ted: Read as '                                                           |                                                               |                                    |       |                    | IOWII |  |

|                   | Unimplemen<br>SS2R<6:0>:                                    | ted: Read as '                                                           | <sup>0'</sup><br>ave Select (S                                | S2) to the Corre                   |       |                    | IOWI  |  |

| bit 15-7          | Unimplemen<br>SS2R<6:0>:<br>(see Table 11                   | <b>ted:</b> Read as '<br>Assign SPI2 SI                                  | <sup>0'</sup><br>ave Select (S<br>selection nur               | S2) to the Corre                   |       |                    |       |  |

| bit 15-7          | Unimplemen<br>SS2R<6:0>:<br>(see Table 11                   | <b>ted:</b> Read as '<br>Assign SPI2 SI<br>-2 for input pin              | <sup>0'</sup><br>ave Select (S<br>selection nur               | S2) to the Corre                   |       |                    | IOWIT |  |

| bit 15-7          | Unimplemen<br>SS2R<6:0>:<br>(see Table 11                   | <b>ted:</b> Read as '<br>Assign SPI2 SI<br>-2 for input pin              | <sup>0'</sup><br>ave Select (S<br>selection nur               | S2) to the Corre                   |       |                    |       |  |

| bit 15-7          | Unimplemen<br>SS2R<6:0>: .<br>(see Table 11<br>1111100 = Ir | ted: Read as '<br>Assign SPI2 SI<br>-2 for input pin<br>nput tied to RPI | <sup>0'</sup><br>ave Select (S<br>selection nur<br>I124       | S2) to the Corre                   |       |                    | 10W11 |  |

| bit 15-7          | Unimplemen<br>SS2R<6:0>: .<br>(see Table 11<br>1111100 = Ir | <b>ted:</b> Read as '<br>Assign SPI2 SI<br>-2 for input pin              | <sup>0'</sup><br>ave Select (S<br>selection nur<br>I124<br>P1 | S2) to the Corre                   |       |                    |       |  |

## REGISTER 11-17: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

|                 |                           |                          | (1)                        |

|-----------------|---------------------------|--------------------------|----------------------------|

| REGISTER 11-42: | <b>RPOR12: PERIPHERAL</b> | <b>PIN SELECT OUTPUT</b> | REGISTER 12 <sup>(1)</sup> |

| U-0          | U-0      | R/W-0                                   | R/W-0 | R/W-0                              | R/W-0      | R/W-0           | R/W-0 |  |  |

|--------------|----------|-----------------------------------------|-------|------------------------------------|------------|-----------------|-------|--|--|

| -            | -        |                                         |       | RP127R                             | -          |                 |       |  |  |

| bit 15       |          |                                         |       |                                    |            |                 | bit 8 |  |  |

|              |          |                                         |       |                                    |            |                 |       |  |  |

| U-0          | U-0      | R/W-0                                   | R/W-0 | R/W-0                              | R/W-0      | R/W-0           | R/W-0 |  |  |

| —            | —        |                                         |       | RP126R                             | <5:0>      |                 |       |  |  |

| bit 7        |          |                                         |       |                                    |            |                 | bit 0 |  |  |

|              |          |                                         |       |                                    |            |                 |       |  |  |

| Legend:      |          |                                         |       |                                    |            |                 |       |  |  |

| R = Readab   | le bit   | W = Writable                            | bit   | U = Unimplemented bit, read as '0' |            |                 |       |  |  |

| -n = Value a | t POR    | '1' = Bit is set                        |       | '0' = Bit is cleare                | ed         | x = Bit is unkr | nown  |  |  |

|              |          |                                         |       |                                    |            |                 |       |  |  |

| bit 15-14    | Unimplem | ented: Read as '                        | 0'    |                                    |            |                 |       |  |  |

| bit 13-8     |          | :0>: Peripheral C<br>11-3 for periphera | •     | on is Assigned to F<br>mbers)      | RP127 Outp | ut Pin bits     |       |  |  |

| bit 7-6      | Unimplem | ented: Read as '                        | 0'    |                                    |            |                 |       |  |  |

| bit 5-0      | •        |                                         |       |                                    |            |                 |       |  |  |

Note 1: This register is not available on dsPIC33EPXXXGM30X/604/706 devices.

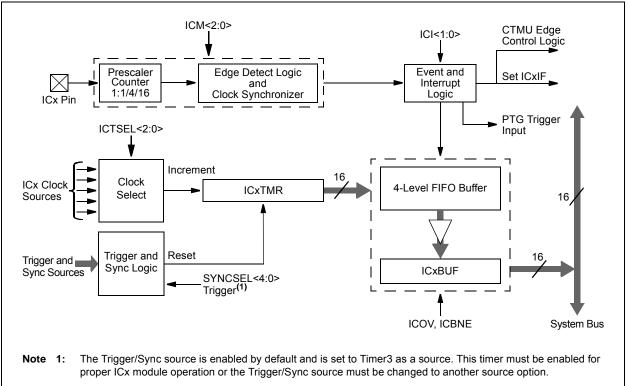

## 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Input Capture" (DS70000352), which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGM3XX/6XX/7XX devices support up to eight input capture channels.

Key features of the input capture module include:

- Hardware configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 31 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

### FIGURE 14-1: INPUT CAPTURE x MODULE BLOCK DIAGRAM

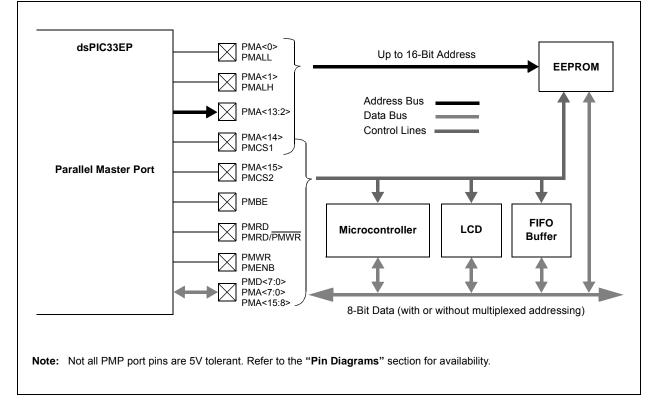

## 28.0 PARALLEL MASTER PORT (PMP)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Parallel Master Port (PMP)" (DS70576), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Parallel Master Port (PMP) module is a parallel 8-bit I/O module, specifically designed to communicate with a wide variety of parallel devices, such as communication peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP is highly configurable.

Key features of the PMP module include:

- Eight Data Lines

- Up to 16 Programmable Address Lines

- · Up to 2 Chip Select Lines

- Programmable Strobe Options:

- Individual read and write strobes, or

- Read/Write strobe with enable strobe

- Address Auto-Increment/Auto-Decrement

- Programmable Address/Data Multiplexing

- Programmable Polarity on Control Signals

- · Legacy Parallel Slave Port (PSP) Support

- Enhanced Parallel Slave Support:

- Address support

- 4-byte deep auto-incrementing buffer

- Programmable Wait States

#### FIGURE 28-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

NOTES:

| DC CHARACTER                        | Standard C<br>(unless oth<br>Operating t | herwise s | <b>tated)</b><br><sup>-</sup> e -40°C | ≤ Ta ≤ +8  | <b>o 3.6V</b><br>5°C for Industrial<br>25°C for Extended |      |         |

|-------------------------------------|------------------------------------------|-----------|---------------------------------------|------------|----------------------------------------------------------|------|---------|

| Parameter No.                       | Doze<br>Ratio                            | Units     |                                       | Conditions |                                                          |      |         |

| Doze Current (IDOZE) <sup>(1)</sup> |                                          |           |                                       |            |                                                          |      |         |

| DC73a                               | 20                                       | 53        | 1:2                                   | mA         | -40°C                                                    | 3.3V | 70 MIPS |

| DC73g                               | 8                                        | 30        | 1:128                                 | mA         | -40 C                                                    | 3.3V |         |

| DC70a                               | 19                                       | 53        | 1:2                                   | mA         | +25°C                                                    | 3.3V |         |

| DC70g                               | 8                                        | 30        | 1:128                                 | mA         | +25 C                                                    |      | 60 MIPS |

| DC71a                               | 20                                       | 53        | 1:2                                   | mA         | +85°C                                                    | 3.3V |         |

| DC71g                               | 10                                       | 30        | 1:128                                 | mA         | +00 C                                                    | 3.3V | 60 MIPS |

| DC72a                               | 25                                       | 42        | 1:2                                   | mA         | +125°C                                                   | 3.3V |         |

| DC72g                               | 12                                       | 30        | 1:128                                 | mA         | +125 C                                                   | 3.3V | 50 MIPS |

#### TABLE 33-9: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

• Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as outputs and driving low

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- CPU executing

```

while(1)

{

NOP();

}

```

- · JTAG is disabled

- 2: Data in the "Typical" column is at 3.3V, +25°C unless otherwise specified.

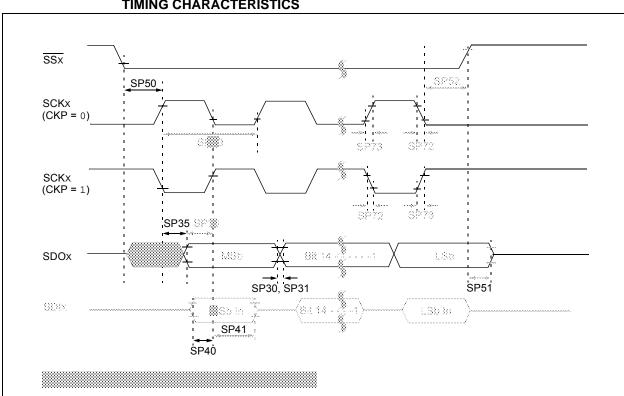

FIGURE 33-22: SPI2 AND SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

|              | ARACTER | ADCX MODULE SPECIF                                   | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 1): 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |         |                                   |                   |                                                                                                 |  |

|--------------|---------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------|-------------------|-------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol  | Characteristic                                       | Min.                                                                                                                                                                                                                                                                                                 | Тур.    | -40 C                             | ≤ IA ≤ +<br>Units | Conditions                                                                                      |  |

|              |         |                                                      | Device                                                                                                                                                                                                                                                                                               | Supply  | /                                 | •                 |                                                                                                 |  |

| AD01         | AVDD    | Module VDD Supply                                    | Greater of:<br>VDD – 0.3<br>or 3.0                                                                                                                                                                                                                                                                   | —       | Lesser of:<br>VDD + 0.3<br>or 3.6 | V                 |                                                                                                 |  |

| AD02         | AVss    | Module Vss Supply                                    | Vss – 0.3                                                                                                                                                                                                                                                                                            |         | Vss + 0.3                         | V                 |                                                                                                 |  |

|              |         | ·                                                    | Reference                                                                                                                                                                                                                                                                                            | ce Inpu | ts                                |                   | ·                                                                                               |  |

| AD05         | Vrefh   | Reference Voltage High                               | AVss + 2.7                                                                                                                                                                                                                                                                                           |         | AVDD                              | V                 | <b>(Note 1)</b><br>VREFH = VREF+,<br>VREFL = VREF-                                              |  |

| AD05a        |         |                                                      | 3.0                                                                                                                                                                                                                                                                                                  | _       | 3.6                               | V                 | VREFH = AVDD,<br>VREFL = AVSS = 0                                                               |  |

| AD06         | VREFL   | Reference Voltage Low                                | AVss                                                                                                                                                                                                                                                                                                 |         | AVDD - 2.7                        | V                 | (Note 1)                                                                                        |  |

| AD06a        |         |                                                      | 0                                                                                                                                                                                                                                                                                                    |         | 0                                 | V                 | VREFH = AVDD,<br>VREFL = AVSS = 0                                                               |  |

| AD07         | VREF    | Absolute Reference<br>Voltage                        | 2.7                                                                                                                                                                                                                                                                                                  | _       | 3.6                               | V                 | VREF = VREFH – VREFL                                                                            |  |

| AD08         | IREF    | Current Drain                                        | _                                                                                                                                                                                                                                                                                                    |         | 10<br>600                         | μΑ<br>μΑ          | ADC off<br>ADC on                                                                               |  |

| AD09         | Iad     | Operating Current                                    | —                                                                                                                                                                                                                                                                                                    | 5       | —                                 | mA                | ADC operating in 10-bit mode (Note 1)                                                           |  |

|              |         |                                                      | —                                                                                                                                                                                                                                                                                                    | 2       |                                   | mA                | ADC operating in 12-bit mode (Note 1)                                                           |  |

|              |         |                                                      | Analog                                                                                                                                                                                                                                                                                               | g Input |                                   |                   |                                                                                                 |  |

| AD12         | Vinh    | Input Voltage Range,<br>Vinn                         | VINL                                                                                                                                                                                                                                                                                                 | _       | Vrefh                             | V                 | This voltage reflects<br>Sample-and-Hold<br>Channels 0, 1, 2 and 3<br>(CH0-CH3), positive input |  |

| AD13         | VINL    | Input Voltage Range,<br>ViNL                         | VREFL                                                                                                                                                                                                                                                                                                |         | AVss + 1V                         | V                 | This voltage reflects<br>Sample-and-Hold<br>Channels 0, 1, 2 and 3<br>(CH0-CH3), negative input |  |

| AD17         | Rin     | Recommended<br>Impedance of Analog<br>Voltage Source | _                                                                                                                                                                                                                                                                                                    |         | 200                               | Ω                 | Impedance to achieve<br>maximum performance of<br>ADC                                           |  |

## TABLE 33-56: ADCx MODULE SPECIFICATIONS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 33-12 for the minimum and maximum BOR values.

## 34.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC33EPXXXGM3XX/6XX/7XX AC characteristics and timing parameters for high-temperature devices. However, all AC timing specifications in this section are the same as those in **Section 33.2 "AC Characteristics and Timing Parameters"**, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter OS53 in Section 33.2 "AC Characteristics and Timing Parameters" is the Industrial and Extended temperature equivalent of HOS53.

#### TABLE 34-10: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

| AC CHARACTERISTICS | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$<br>Operating voltage VDD range as described in Table 34-1. |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

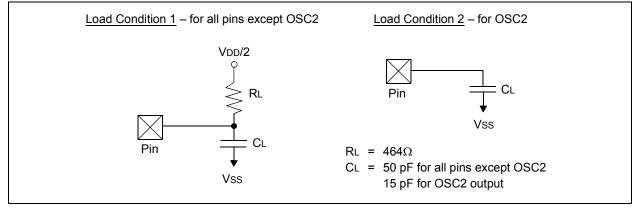

#### FIGURE 34-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | N   | MILLIMETERS |          |      |  |  |

|-------------------------|-----|-------------|----------|------|--|--|

| Dimension               | MIN | NOM         | MAX      |      |  |  |

| Number of Pins          | А   |             | 44       |      |  |  |

| Pitch                   | е   |             | 0.65 BSC |      |  |  |

| Overall Height          | A   | 0.80        | 0.90     | 1.00 |  |  |

| Standoff                | A1  | 0.00        | 0.02     | 0.05 |  |  |

| Terminal Thickness      | A3  |             | 0.20 REF |      |  |  |

| Overall Width           | Е   |             | 8.00 BSC |      |  |  |

| Exposed Pad Width       | E2  | 6.25        | 6.45     | 6.60 |  |  |

| Overall Length          | D   |             | 8.00 BSC |      |  |  |

| Exposed Pad Length      | D2  | 6.25        | 6.45     | 6.60 |  |  |

| Terminal Width          | b   | 0.20        | 0.30     | 0.35 |  |  |

| Terminal Length         | L   | 0.30        | 0.40     | 0.50 |  |  |

| Terminal-to-Exposed-Pad | К   | 0.20        | -        | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension. usually without tolerance. for information purposes only.

Microchip Technology Drawing C04-103C Sheet 2 of 2

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Ν        | MILLIMETERS |          |      |  |  |

|------------------------|----------|-------------|----------|------|--|--|

| Dimensio               | n Limits | MIN         | NOM      | MAX  |  |  |

| Number of Pins         | N        |             | 64       |      |  |  |

| Pitch                  | е        |             | 0.50 BSC |      |  |  |

| Overall Height         | A        | 0.80        | 0.90     | 1.00 |  |  |

| Standoff               | A1       | 0.00        | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3       | 0.20 REF    |          |      |  |  |

| Overall Width          | E        |             | 9.00 BSC |      |  |  |

| Exposed Pad Width      | E2       | 7.05        | 7.15     | 7.50 |  |  |

| Overall Length         | D        |             | 9.00 BSC |      |  |  |

| Exposed Pad Length     | D2       | 7.05        | 7.15     | 7.50 |  |  |

| Contact Width          | b        | 0.18        | 0.25     | 0.30 |  |  |

| Contact Length         | L        | 0.30        | 0.40     | 0.50 |  |  |

| Contact-to-Exposed Pad | K        | 0.20        | -        | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-149C Sheet 2 of 2

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support