Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm310-e-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXXGM3XX/6XX/7XX PRODUCT FAMILY

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1. Their pinout diagrams appear on the following pages.

|                   | ()                            |              |     |                      | R             | ema            | ppab                         | le P | eripł | neral  | s   |                                    |      |               |     |                              |                     |      |     |     |      |          |      |          |  |

|-------------------|-------------------------------|--------------|-----|----------------------|---------------|----------------|------------------------------|------|-------|--------|-----|------------------------------------|------|---------------|-----|------------------------------|---------------------|------|-----|-----|------|----------|------|----------|--|

| Device            | Program Flash Memory (Kbytes) | RAM (Kbytes) | CAN | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM (Channels) | QEI  | UART  | (1)SPI | DCI | External Interrupts <sup>(2)</sup> | I²C™ | CRC Generator | ADC | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | ЪТG | dWd | RTCC | I/O Pins | Pins | Packages |  |

| dsPIC33EP128GM304 | 128                           | 16           | 0   |                      |               |                |                              |      |       |        |     |                                    |      |               |     |                              |                     |      |     |     |      |          |      |          |  |

| dsPIC33EP128GM604 | 120                           | 10           | 2   |                      |               |                |                              |      |       |        |     |                                    |      |               |     |                              |                     |      |     |     |      |          |      |          |  |

| dsPIC33EP256GM304 | 256                           | 32           | 0   | 9/4                  | 8             | 8              | 12                           | 2    | 4     | 3      | 1   | 5                                  | 2    | 1             | 2   | 18                           | 4/5                 | 1    | Yes | No  | No   | 35       | 44   | TQFP,    |  |

| dsPIC33EP256GM604 | 250                           | 32           | 2   | 9/4                  | 0             | 0              |                              |      | 4     | 3      | 1   | 5                                  | 2    |               | 2   | 10                           | 4/5                 | 1    | res | INU | NO   | 35       | 44   | QFN      |  |

| dsPIC33EP512GM304 | 512                           | 48           | 0   |                      |               |                |                              |      |       |        |     |                                    |      |               |     |                              |                     |      |     |     |      |          |      |          |  |

| dsPIC33EP512GM604 | 512                           | 40           | 2   |                      |               |                |                              |      |       |        |     |                                    |      |               |     |                              |                     |      |     |     |      |          |      |          |  |

| dsPIC33EP128GM306 | 128                           | 16           | 0   |                      |               |                |                              |      |       |        |     |                                    |      |               |     |                              |                     |      |     |     |      |          |      |          |  |

| dsPIC33EP128GM706 | 120                           | 10           | 2   |                      |               |                |                              |      |       |        |     |                                    |      |               |     |                              |                     |      |     |     |      |          |      |          |  |

| dsPIC33EP256GM306 | 256                           | 32           | 0   | 9/4                  | 8             | 8              | 12                           | 2    | 4     | 3      | 1   | 5                                  | 2    | 1             | 2   | 30                           | 4/5                 | 1    | Yes | Yes | Yes  | 53       | 64   | TQFP,    |  |

| dsPIC33EP256GM706 | 250                           | 32           | 2   | 9/4                  | 0             | 0              | 12                           | 2    | 4     | 3      | 1   | 5                                  | 2    |               | 2   | 30                           | 4/5                 | 1    | res | 165 | res  | 55       | 04   | QFN      |  |

| dsPIC33EP512GM306 | 512                           | 48           | 0   |                      |               |                |                              |      |       |        |     |                                    |      |               |     |                              |                     |      |     |     |      |          |      |          |  |

| dsPIC33EP512GM706 | 512                           | 40           | 2   |                      |               |                |                              |      |       |        |     |                                    |      |               |     |                              |                     |      |     |     |      |          |      |          |  |

| dsPIC33EP128GM310 | 128                           | 16           | 0   |                      |               |                |                              |      |       |        |     |                                    |      |               |     |                              |                     |      |     |     |      |          |      |          |  |

| dsPIC33EP128GM710 | 120                           | 8 16         | 2   |                      |               |                |                              |      |       |        |     |                                    |      |               |     |                              |                     |      |     |     |      |          |      |          |  |

| dsPIC33EP256GM310 | 256                           | 256 32       | 0   | 9/4                  | 8             | 8              | 12                           | 2    | 4     | 3      | 1   | 5                                  | 2    | 1             | 2   | 49                           | 4/5                 | 1    | Yes | Yes | Yes  | 85       | 100/ | TQFP,    |  |

| dsPIC33EP256GM710 | 200                           | 256 32       | 2   |                      | 0             | 0              | 12                           | 2    | 7     | 5      | 1   | 5                                  | 2    |               | 2   | 43                           | 4/5                 |      | 103 | 163 | 163  | 00       | 121  | TFBGA    |  |

| dsPIC33EP512GM310 | 512                           | 512 48       | 0   | ļ                    |               |                |                              |      |       |        |     |                                    |      |               |     |                              |                     |      |     |     |      |          |      |          |  |

| dsPIC33EP512GM710 | 512                           | 40           | 2   |                      |               |                |                              |      |       |        |     |                                    |      |               |     |                              |                     |      |     |     |      |          |      |          |  |

### TABLE 1: dsPIC33EPXXXGM3XX/6XX/7XX FAMILY DEVICES

Note 1: Only SPI2 and SPI3 are remappable.

2: INT0 is not remappable.

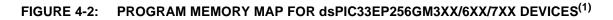

Note 1: Memory areas are not shown to scale.

2: On Reset, these bits are automatically copied into the device Configuration Shadow registers.

## TABLE 4-21: DCI REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14                        | Bit 13  | Bit 12 | Bit 11  | Bit 10    | Bit 9 | Bit 8       | Bit 7       | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|--------|-------------------------------|---------|--------|---------|-----------|-------|-------------|-------------|--------|--------|-------|-------|-------|--------|--------|---------------|

| DCICON1     | 0280  | DCIEN  | r                             | DCISIDL | r      | DLOOP   | CSCKD     | CSCKE | COFSD       | UNFM        | CSDOM  | DJST   | r     | r     | r     | COFSM1 | COFSM0 | 0000          |

| DCICON2     | 0282  | r      | r                             | r       | r      | BLEN1   | BLEN0     | r     | COFSG3      | COFSG2      | COFSG1 | COFSG0 | r     | WS3   | WS2   | WS1    | WS0    | 0000          |

| DCICON3     | 0284  | r      | r                             | r       | r      |         | BCG<11:0> |       |             |             |        | 0000   |       |       |       |        |        |               |

| DCISTAT     | 0286  | r      | r                             | r       | r      | SLOT3   | SLOT2     | SLOT1 | SLOT0       | r           | r      | r      | r     | ROV   | RFUL  | TUNF   | TMPTY  | 0000          |

| TSCON       | 0288  |        | TSE<15:0> 0000                |         |        |         |           |       |             |             | 0000   |        |       |       |       |        |        |               |

| RSCON       | 028C  |        | RSE<15:0> 0000                |         |        |         |           |       |             |             | 0000   |        |       |       |       |        |        |               |

| RXBUF0      | 0290  |        |                               |         |        |         |           | F     | Receive 0 D | ata Registe | r      |        |       |       |       |        |        | uuuu          |

| RXBUF1      | 0292  |        |                               |         |        |         |           | F     | Receive 1 D | ata Registe | r      |        |       |       |       |        |        | uuuu          |

| RXBUF2      | 0294  |        |                               |         |        |         |           | F     | Receive 2 D | ata Registe | r      |        |       |       |       |        |        | uuuu          |

| RXBUF3      | 0296  |        |                               |         |        |         |           | F     | Receive 3 D | ata Registe | r      |        |       |       |       |        |        | uuuu          |

| TXBUF0      | 0298  |        | Transmit 0 Data Register 0000 |         |        |         |           |       |             |             | 0000   |        |       |       |       |        |        |               |

| TXBUF1      | 029A  |        |                               |         |        |         |           | T     | ransmit 1 D | ata Registe | r      |        |       |       |       |        |        | 0000          |

| TXBUF2      | 029C  |        |                               |         |        |         |           | Г     | ransmit 2 D | ata Registe | r      |        |       |       |       |        |        | 0000          |

| TXBUF3      | 029E  |        |                               |         |        |         |           | I     | ransmit 3 D | ata Registe | r      |        |       |       |       |        |        | 0000          |

| Lanardi     |       | L      |                               |         |        | 1 (a) D |           |       |             |             |        |        |       |       |       |        |        |               |

Legend: u = unchanged; r = reserved; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-30: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGM304/604 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|-------|------------|-------|-------|--------|-------|-------|---------------|

| RPOR0       | 0680  | _      | -      |        |            | RP35F  | R<5:0> |       |       | _     | _     |            |       | RP20  | R<5:0> |       |       | 0000          |

| RPOR1       | 0682  | _      | —      |        | RP37R<5:0> |        |        |       |       | —     | _     |            |       | RP36  | R<5:0> |       |       | 0000          |

| RPOR2       | 0684  |        | —      |        | RP39R<5:0> |        |        |       |       | —     | _     | RP38R<5:0> |       |       |        |       |       | 0000          |

| RPOR3       | 0686  |        | —      |        |            | RP41F  | ۲<5:0> |       |       | —     | _     | RP40R<5:0> |       |       |        |       |       | 0000          |

| RPOR4       | 0688  |        | —      |        |            | RP43F  | R<5:0> |       |       | —     |       | RP42R<5:0> |       |       |        |       |       | 0000          |

| RPOR5       | 068A  |        | —      |        | RP49R<5:0> |        |        |       |       | —     |       | RP48R<5:0> |       |       |        |       |       | 0000          |

| RPOR6       | 068C  |        | —      |        | RP55R<5:0> |        |        |       |       | —     |       | RP54R<5:0> |       |       |        |       |       | 0000          |

| RPOR7       | 068E  |        | —      |        | RP57R<5:0> |        |        |       |       | _     | _     |            |       | RP56  | R<5:0> |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-31: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGM306/706 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|-------|------------|-------|-------|--------|-------|-------|---------------|

| RPOR0       | 0680  | _      | —      |        |            | RP35F  | R<5:0> |       |       | —     | _     | RP20R<5:0> |       |       |        |       |       | 0000          |

| RPOR1       | 0682  | _      | —      |        | RP37R<5:0> |        |        |       |       | —     | _     |            |       | RP36  | R<5:0> |       |       | 0000          |

| RPOR2       | 0684  | _      | —      |        | RP39R<5:0> |        |        |       |       | —     | _     |            |       | RP38  | R<5:0> |       |       | 0000          |

| RPOR3       | 0686  | _      | _      |        | RP41R<5:0> |        |        |       |       | _     | _     | RP40R<5:0> |       |       |        |       |       | 0000          |

| RPOR4       | 0688  | _      | _      |        |            | RP43F  | ₹<5:0> |       |       | _     | _     |            |       | RP42I | R<5:0> |       |       | 0000          |

| RPOR5       | 068A  | _      | _      |        |            | RP49F  | ₹<5:0> |       |       | _     | _     | RP48R<5:0> |       |       |        |       |       | 0000          |

| RPOR6       | 068C  | _      | _      |        |            | RP55F  | ₹<5:0> |       |       | _     | _     | RP54R<5:0> |       |       |        |       |       | 0000          |

| RPOR7       | 068E  | _      | _      |        | RP57R<5:0> |        |        |       |       | _     | _     | RP56R<5:0> |       |       |        |       | 0000  |               |

| RPOR8       | 0690  |        | _      |        | RP70R<5:0> |        |        |       |       | —     | _     | RP69R<5:0> |       |       |        |       | 0000  |               |

| RPOR9       | 0692  | _      | _      |        | RP97R<5:0> |        |        |       |       | _     | _     | _          | _     |       | _      | _     | _     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0         | U-0                                                  | R/W-0                                | R/W-0           | R/W-0                         | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |  |  |

|---------------|------------------------------------------------------|--------------------------------------|-----------------|-------------------------------|-----------------------|-----------------------|-----------------------|--|--|--|--|--|

| ROON          |                                                      | ROSSLP                               | ROSEL           | RODIV3 <sup>(1)</sup>         | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |  |  |  |

| bit 15        |                                                      |                                      |                 |                               |                       |                       | bit 8                 |  |  |  |  |  |

|               |                                                      |                                      |                 |                               |                       |                       |                       |  |  |  |  |  |

| U-0           | U-0                                                  | U-0                                  | U-0             | U-0                           | U-0                   | U-0                   | U-0                   |  |  |  |  |  |

| bit 7         |                                                      | _                                    | _               |                               |                       |                       | bit (                 |  |  |  |  |  |

|               |                                                      |                                      |                 |                               |                       |                       |                       |  |  |  |  |  |

| Legend:       |                                                      |                                      |                 |                               |                       |                       |                       |  |  |  |  |  |

| R = Readable  |                                                      | W = Writable                         |                 |                               | nented bit, read      |                       |                       |  |  |  |  |  |

| -n = Value at | POR                                                  | '1' = Bit is set                     |                 | '0' = Bit is cle              | ared                  | x = Bit is unkr       | IOWN                  |  |  |  |  |  |

| bit 15        | ROON: Refer                                          | ence Oscillato                       | r Output Enat   | ole bit                       |                       |                       |                       |  |  |  |  |  |

|               |                                                      |                                      |                 | on the REFCL                  | .K pin <sup>(2)</sup> |                       |                       |  |  |  |  |  |

|               | 0 = Reference                                        | e oscillator outp                    | out is disabled | t                             |                       |                       |                       |  |  |  |  |  |

| bit 14        | Unimplemen                                           | ted: Read as '                       | 0'              |                               |                       |                       |                       |  |  |  |  |  |

| bit 13        | <b>ROSSLP:</b> Reference Oscillator Run in Sleep bit |                                      |                 |                               |                       |                       |                       |  |  |  |  |  |

|               |                                                      | e oscillator out<br>e oscillator out |                 | to run in Sleep<br>d in Sleep |                       |                       |                       |  |  |  |  |  |

| bit 12        | ROSEL: Refe                                          | erence Oscillato                     | or Source Sel   | ect bit                       |                       |                       |                       |  |  |  |  |  |

|               |                                                      | crystal is used<br>lock is used as   |                 |                               |                       |                       |                       |  |  |  |  |  |

| bit 11-8      | RODIV<3:0>:                                          | Reference Os                         | cillator Divide | er bits <sup>(1)</sup>        |                       |                       |                       |  |  |  |  |  |

|               |                                                      | ence clock divi                      |                 |                               |                       |                       |                       |  |  |  |  |  |

|               |                                                      | ence clock divi                      | •               |                               |                       |                       |                       |  |  |  |  |  |

|               |                                                      | ence clock divi<br>ence clock divi   | •               |                               |                       |                       |                       |  |  |  |  |  |

|               |                                                      | ence clock divi                      |                 |                               |                       |                       |                       |  |  |  |  |  |

|               |                                                      | ence clock divi                      |                 |                               |                       |                       |                       |  |  |  |  |  |

|               |                                                      | ence clock divi                      |                 |                               |                       |                       |                       |  |  |  |  |  |

|               |                                                      | ence clock divi                      |                 |                               |                       |                       |                       |  |  |  |  |  |

|               |                                                      | ence clock divi<br>ence clock divi   | -               |                               |                       |                       |                       |  |  |  |  |  |

|               |                                                      | ence clock divi                      | ,               |                               |                       |                       |                       |  |  |  |  |  |

|               |                                                      | ence clock divi                      | •               |                               |                       |                       |                       |  |  |  |  |  |

|               | 0011 = Refer                                         | ence clock divi                      | ded by 8        |                               |                       |                       |                       |  |  |  |  |  |

|               |                                                      | ence clock divi                      |                 |                               |                       |                       |                       |  |  |  |  |  |

|               | 0001 = Refer<br>0000 = Refer                         | ence clock divi                      | aed by 2        |                               |                       |                       |                       |  |  |  |  |  |

| bit 7-0       |                                                      |                                      | 0'              |                               |                       |                       |                       |  |  |  |  |  |

|               | ommplemen                                            | ted: Read as '                       | U               |                               |                       |                       |                       |  |  |  |  |  |

### **REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER**

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

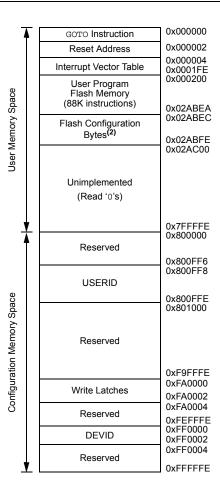

### 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-29). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

### 11.4.4.1 Virtual Connections

dsPIC33EPXXXGM3XX/6XX/7XX devices support virtual (internal) connections to the output of the op amp/comparator module (see Figure 26-1 in Section 26.0 "Op Amp/Comparator Module") and the PTG module (see Section 25.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXGM3XX/6XX/7XX devices support virtual connections to the filtered QEIx module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module").

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of `b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEIx module allows peripherals to be connected to the QEIx digital filter input. To utilize this filter, the QEIx module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEIx digital filter.

### EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43

| RPINR15 = 0x2500;<br>RPINR7 = 0x009; | /* Connect the QEI1 HOME1 input to RP37 (pin 43) */ /* Connect the IC1 input to the digital filter on the FHOME1 input */ |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| QEI1IOC = 0x4000;                    | /* Enable the QEI digital filter */                                                                                       |

| QEI1CON = 0x8000;                    | /* Enable the QEI module */                                                                                               |

| U-0          | R/W-0     | R/W-0                                 | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|-----------|---------------------------------------|-------|-------------------|-----------------|-----------------|-------|

| —            |           |                                       |       | IC6R<6:0>         |                 |                 |       |

| bit 15       |           |                                       |       |                   |                 |                 | bit 8 |

|              |           |                                       |       |                   |                 |                 |       |

| U-0          | R/W-0     | R/W-0                                 | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| _            |           |                                       |       | IC5R<6:0>         |                 |                 |       |

| bit 7        |           |                                       |       |                   |                 |                 | bit 0 |

|              |           |                                       |       |                   |                 |                 |       |

| Legend:      |           |                                       |       |                   |                 |                 |       |

| R = Readab   | ole bit   | W = Writable                          | bit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR    | '1' = Bit is set                      |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              |           |                                       |       |                   |                 |                 |       |

| bit 15       | Unimpleme | ented: Read as '                      | 0'    |                   |                 |                 |       |

| bit 14-8     |           | Assign Input Ca<br>11-2 for input pin |       |                   | onding RPn P    | in bits         |       |

|              | 1111100 = | Input tied to RPI                     | 124   |                   |                 |                 |       |

|              | •         |                                       |       |                   |                 |                 |       |

|              | •         |                                       |       |                   |                 |                 |       |

|              | 0000001 = | Input tied to CM                      | P1    |                   |                 |                 |       |

|              | 0000000 = | Input tied to Vss                     | ;     |                   |                 |                 |       |

| bit 7        | Unimpleme | ented: Read as '                      | 0'    |                   |                 |                 |       |

| bit 6-0      |           | Assign Input Ca<br>11-2 for input pin |       |                   | onding RPn P    | in bits         |       |

|              | 1111100 = | Input tied to RPI                     | 124   |                   |                 |                 |       |

|              | •         |                                       |       |                   |                 |                 |       |

|              | •         |                                       |       |                   |                 |                 |       |

|              | 0000001 = | Input tied to CM                      | P1    |                   |                 |                 |       |

|              |           | Input tied to Vss                     |       |                   |                 |                 |       |

|              |           |                                       |       |                   |                 |                 |       |

### REGISTER 11-6: RPINR9: PERIPHERAL PIN SELECT INPUT REGISTER 9

# 15.1 Output Compare Control Registers

### REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | R/W-0  |

|--------|-----|--------|---------|---------|---------|-----|--------|

| —      | —   | OCSIDL | OCTSEL2 | OCTSEL1 | OCTSEL0 | —   | ENFLTB |

| bit 15 |     |        |         |         |         |     | bit 8  |

| R/W-0  | U-0 | R/W-0, HSC | R/W-0, HSC | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|------------|------------|----------|-------|-------|-------|

| ENFLTA | —   | OCFLTB     | OCFLTA     | TRIGMODE | OCM2  | OCM1  | OCM0  |

| bit 7  |     |            |            |          |       |       | bit 0 |

| Legend:           | HSC = Hardware Settable/C | learable bit               |                    |

|-------------------|---------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Output Compare x Stop in Idle Mode Control bit                                                                                                                                                                                                                                                                                                                                                     |

|           | <ul> <li>1 = Output Compare x halts in CPU Idle mode</li> <li>0 = Output Compare x continues to operate in CPU Idle mode</li> </ul>                                                                                                                                                                                                                                                                        |

| bit 12-10 | OCTSEL<2:0>: Output Compare x Clock Select bits                                                                                                                                                                                                                                                                                                                                                            |

|           | <ul> <li>111 = Peripheral clock (FP)</li> <li>110 = Reserved</li> <li>101 = PTGOx clock<sup>(2)</sup></li> <li>100 = T1CLK is the clock source of OCx (only the synchronous clock is supported)</li> <li>011 = T5CLK is the clock source of OCx</li> <li>010 = T4CLK is the clock source of OCx</li> <li>001 = T3CLK is the clock source of OCx</li> <li>000 = T2CLK is the clock source of OCx</li> </ul> |

| bit 9     | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                 |

| bit 8     | ENFLTB: Fault B Input Enable bit                                                                                                                                                                                                                                                                                                                                                                           |

|           | <ul> <li>1 = Output Compare x Fault B input (OCFB) is enabled</li> <li>0 = Output Compare x Fault B input (OCFB) is disabled</li> </ul>                                                                                                                                                                                                                                                                    |

| bit 7     | ENFLTA: Fault A Input Enable bit                                                                                                                                                                                                                                                                                                                                                                           |

|           | <ul> <li>1 = Output Compare x Fault A input (OCFA) is enabled</li> <li>0 = Output Compare x Fault A input (OCFA) is disabled</li> </ul>                                                                                                                                                                                                                                                                    |

| bit 6     | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                 |

| bit 5     | OCFLTB: PWM Fault B Condition Status bit                                                                                                                                                                                                                                                                                                                                                                   |

|           | <ul> <li>1 = PWM Fault B condition on OCFB pin has occurred</li> <li>0 = No PWM Fault B condition on OCFB pin has occurred</li> </ul>                                                                                                                                                                                                                                                                      |

| bit 4     | OCFLTA: PWM Fault A Condition Status bit                                                                                                                                                                                                                                                                                                                                                                   |

|           | <ul> <li>1 = PWM Fault A condition on OCFA pin has occurred</li> <li>0 = No PWM Fault A condition on OCFA pin has occurred</li> </ul>                                                                                                                                                                                                                                                                      |

| Note 1:   | OCxR and OCxRS are double-buffered in PWM mode only.                                                                                                                                                                                                                                                                                                                                                       |

| 2:        | Each Output Compare x module (OCx) has one PTG clock source. See <b>Section 25.0 "Peripheral Trigger</b><br><b>Generator (PTG) Module</b> " for more information.<br>PTGO4 = OC1, OC5<br>PTGO5 = OC2, OC6<br>PTGO6 = OC3, OC7<br>PTGO7 = OC4, OC8                                                                                                                                                          |

# REGISTER 16-11: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7-6 | 6  | <b>DTC&lt;1:0&gt;:</b> Dead-Time Control bits<br>11 = Dead-Time Compensation mode                                                                                                                                                                                                                                                  |

|---------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |    | <ul> <li>10 = Dead-time function is disabled</li> <li>01 = Negative dead time is actively applied for Complementary Output mode</li> <li>00 = Positive dead time is actively applied for all Output modes</li> </ul>                                                                                                               |

| bit 5   |    | <b>DTCP:</b> Dead-Time Compensation Polarity bit <sup>(3)</sup>                                                                                                                                                                                                                                                                    |

|         |    | <u>When Set to '⊥':</u><br>If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.<br>If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                                                                                                                                                |

|         |    | <u>When Set to '<math>o</math>':</u><br>If DTCMPx = 0, PWMHx is shortened and PWMLx is lengthened.<br>If DTCMPx = 1, PWMLx is shortened and PWMHx is lengthened.                                                                                                                                                                   |

| bit 4   |    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                         |

| bit 3   |    | MTBS: Master Time Base Select bit                                                                                                                                                                                                                                                                                                  |

|         |    | <ul> <li>1 = PWMx generator uses the secondary master time base for synchronization and as the clock source for the PWMx generation logic (if secondary time base is available)</li> <li>0 = PWMx generator uses the primary master time base for synchronization and as the clock source for the PWMx generation logic</li> </ul> |

| bit 2   |    | <b>CAM:</b> Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                                                                                                                                                                                                        |

|         |    | 1 = Center-Aligned mode is enabled                                                                                                                                                                                                                                                                                                 |

| bit 1   |    | 0 = Edge-Aligned mode is enabled<br><b>XPRES:</b> External PWMx Reset Control bit <sup>(5)</sup>                                                                                                                                                                                                                                   |

| DILI    |    | <ul> <li>1 = Current-limit source resets the time base for this PWMx generator if it is in Independent Time Base<br/>mode</li> </ul>                                                                                                                                                                                               |

| bit 0   |    | <ul> <li>0 = External pins do not affect the PWMx time base</li> <li>IUE: Immediate Update Enable bit<sup>(2)</sup></li> </ul>                                                                                                                                                                                                     |

| DILU    |    | <ul> <li>1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate</li> <li>0 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the PWMx period boundary</li> </ul>                                                                                                          |

| Note    | 1: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.                                                                                                                                                                                                                       |

|         | 2: | These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                                                                                                                                                                                                                             |

|         | 3: | DTC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored.                                                                                                                                                                                                                                                                |

|         | 4: | The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.                                                                                                                                                                                                           |

|         |    |                                                                                                                                                                                                                                                                                                                                    |

**5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

| U-0                     | U-0                                          | R-0              | R-0            | R-0               | R-0            | R-0             | R-0   |  |  |  |  |  |

|-------------------------|----------------------------------------------|------------------|----------------|-------------------|----------------|-----------------|-------|--|--|--|--|--|

| —                       |                                              | FBP5             | FBP4           | FBP3              | FBP2           | FBP1            | FBP0  |  |  |  |  |  |

| oit 15                  | •                                            |                  |                |                   |                | •               | bit 8 |  |  |  |  |  |

|                         |                                              |                  |                |                   |                |                 |       |  |  |  |  |  |

| U-0                     | U-0                                          | R-0              | R-0            | R-0               | R-0            | R-0             | R-0   |  |  |  |  |  |

| —                       | —                                            | FNRB5            | FNRB4          | FNRB3             | FNRB2          | FNRB1           | FNRB0 |  |  |  |  |  |

| bit 7                   |                                              |                  |                |                   |                |                 | bit ( |  |  |  |  |  |

|                         |                                              |                  |                |                   |                |                 |       |  |  |  |  |  |

| Legend:<br>R = Readable | e hit                                        | W = Writable     | hit            | U = Unimplen      | nented hit rea | d as '0'        |       |  |  |  |  |  |

| -n = Value at           |                                              | '1' = Bit is set |                | '0' = Bit is clea |                | x = Bit is unkr |       |  |  |  |  |  |

|                         | TOR                                          |                  |                |                   | areu           |                 | IOWIT |  |  |  |  |  |

| bit 15-14               | Unimplemen                                   | ted: Read as '   | 0'             |                   |                |                 |       |  |  |  |  |  |

| bit 13-8                | FBP<5:0>: FIFO Buffer Pointer bits           |                  |                |                   |                |                 |       |  |  |  |  |  |

|                         | 011111 = RB31 buffer                         |                  |                |                   |                |                 |       |  |  |  |  |  |

|                         | 011110 = RB30 buffer                         |                  |                |                   |                |                 |       |  |  |  |  |  |

|                         | •                                            |                  |                |                   |                |                 |       |  |  |  |  |  |

|                         | •                                            |                  |                |                   |                |                 |       |  |  |  |  |  |

|                         |                                              |                  |                |                   |                |                 |       |  |  |  |  |  |

|                         | 000001 = TRB1 buffer<br>000000 = TRB0 buffer |                  |                |                   |                |                 |       |  |  |  |  |  |

| bit 7-6                 | Unimplemen                                   | ted: Read as '   | 0'             |                   |                |                 |       |  |  |  |  |  |

| bit 5-0                 | FNRB<5:0>:                                   | FIFO Next Rea    | ad Buffer Poir | nter bits         |                |                 |       |  |  |  |  |  |

|                         | 011111 <b>= RE</b>                           | 331 buffer       |                |                   |                |                 |       |  |  |  |  |  |

|                         | 011110 = RB30 buffer                         |                  |                |                   |                |                 |       |  |  |  |  |  |

|                         | •                                            |                  |                |                   |                |                 |       |  |  |  |  |  |

|                         | •                                            |                  |                |                   |                |                 |       |  |  |  |  |  |

|                         | •                                            |                  |                |                   |                |                 |       |  |  |  |  |  |

|                         | 000001 = TRB1 buffer<br>000000 = TRB0 buffer |                  |                |                   |                |                 |       |  |  |  |  |  |

## REGISTER 21-5: CxFIFO: CANx FIFO STATUS REGISTER

## REGISTER 21-11: CxFEN1: CANx ACCEPTANCE FILTER ENABLE REGISTER 1

| R/W-1           | R/W-1 | R/W-1            | R/W-1 | R/W-1                                   | R/W-1 | R/W-1 | R/W-1 |  |  |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|--|--|

|                 |       |                  | FLTE  | N<15:8>                                 |       |       |       |  |  |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |  |  |

|                 |       |                  |       |                                         |       |       |       |  |  |

| R/W-1           | R/W-1 | R/W-1            | R/W-1 | R/W-1                                   | R/W-1 | R/W-1 | R/W-1 |  |  |

|                 |       |                  | FLTE  | N<7:0>                                  |       |       |       |  |  |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |  |  |

|                 |       |                  |       |                                         |       |       |       |  |  |

| Legend:         |       |                  |       |                                         |       |       |       |  |  |

| R = Readable    | bit   | W = Writable b   | pit   | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n

0 = Disables Filter n

### REGISTER 21-12: CxBUFPNT1: CANx FILTERS 0-3 BUFFER POINTER REGISTER 1

| R/W-0                        | R/W-0                                                                                        | R/W-0                                                                                                                              | R/W-0                                                                                                     | R/W-0                                              | R/W-0            | R/W-0                       | R/W-0 |  |  |

|------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|-----------------------------|-------|--|--|

| F3BP3                        | F3BP2                                                                                        | F3BP1                                                                                                                              | F3BP0                                                                                                     | F2BP3                                              | F2BP2            | F2BP1                       | F2BP0 |  |  |

| bit 15                       | •                                                                                            | •                                                                                                                                  | •                                                                                                         |                                                    | •                |                             | bit 8 |  |  |

|                              |                                                                                              |                                                                                                                                    |                                                                                                           |                                                    |                  |                             |       |  |  |

| R/W-0                        | R/W-0                                                                                        | R/W-0                                                                                                                              | R/W-0                                                                                                     | R/W-0                                              | R/W-0            | R/W-0                       | R/W-0 |  |  |

| F1BP3                        | F1BP2                                                                                        | F1BP1                                                                                                                              | F1BP0                                                                                                     | F0BP3                                              | F0BP2            | F0BP1                       | F0BP0 |  |  |

| bit 7                        |                                                                                              |                                                                                                                                    |                                                                                                           |                                                    |                  |                             | bit 0 |  |  |

| Legend:                      |                                                                                              |                                                                                                                                    |                                                                                                           |                                                    |                  |                             |       |  |  |

|                              |                                                                                              |                                                                                                                                    |                                                                                                           | U = Unimplemented bit, read as '0'                 |                  |                             |       |  |  |

| R = Readabl                  | e bit                                                                                        | W = Writable                                                                                                                       | bit                                                                                                       | U = Unimplei                                       | mented bit, read | 1 as '0'                    |       |  |  |

| R = Readabl<br>-n = Value at |                                                                                              | W = Writable<br>'1' = Bit is set                                                                                                   |                                                                                                           | U = Unimpler<br>'0' = Bit is cle                   | ,                | l as '0'<br>x = Bit is unkr | nown  |  |  |

| -n = Value at                | POR                                                                                          | '1' = Bit is set                                                                                                                   | t                                                                                                         | ʻ0' = Bit is cle                                   | ,                |                             | nown  |  |  |

|                              | F3BP<3:0>:                                                                                   | '1' = Bit is set<br>RX Buffer Mas                                                                                                  | t<br>k for Filter 3 b                                                                                     | ʻ0' = Bit is cle                                   | ,                |                             | nown  |  |  |

| -n = Value at                | F3BP<3:0>:<br>1111 = Filter                                                                  | '1' = Bit is set<br>RX Buffer Mas<br>hits received in                                                                              | t<br>k for Filter 3 b<br>n RX FIFO bu                                                                     | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | nown  |  |  |

| -n = Value at                | F3BP<3:0>:<br>1111 = Filter                                                                  | '1' = Bit is set<br>RX Buffer Mas                                                                                                  | t<br>k for Filter 3 b<br>n RX FIFO bu                                                                     | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | nown  |  |  |

| -n = Value at                | F3BP<3:0>:<br>1111 = Filter                                                                  | '1' = Bit is set<br>RX Buffer Mas<br>hits received in                                                                              | t<br>k for Filter 3 b<br>n RX FIFO bu                                                                     | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | iown  |  |  |

| -n = Value at                | F3BP<3:0>:<br>1111 = Filter                                                                  | '1' = Bit is set<br>RX Buffer Mas<br>hits received in                                                                              | t<br>k for Filter 3 b<br>n RX FIFO bu                                                                     | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | nown  |  |  |

| -n = Value at                | F3BP<3:0>:<br>1111 = Filter<br>1110 = Filter<br>0001 = Filter                                | '1' = Bit is set<br>RX Buffer Mas<br>hits received in<br>hits received in<br>hits received in                                      | k for Filter 3 b<br>n RX FIFO bu<br>n RX Buffer 14<br>n RX Buffer 1                                       | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | nown  |  |  |

| -n = Value at<br>bit 15-12   | F3BP<3:0>:<br>1111 = Filter<br>1110 = Filter                                                 | '1' = Bit is set<br>RX Buffer Mas<br>hits received in<br>hits received in<br>hits received in<br>hits received in                  | k for Filter 3 b<br>n RX FIFO bur<br>n RX Buffer 14<br>n RX Buffer 1<br>n RX Buffer 0                     | '0' = Bit is cle<br>its<br>ffer<br>↓               | ared             | x = Bit is unkr             | nown  |  |  |

| -n = Value at                | F3BP<3:0>:<br>1111 = Filter<br>1110 = Filter                                                 | '1' = Bit is set<br>RX Buffer Mas<br>hits received in<br>hits received in<br>hits received in<br>hits received in                  | k for Filter 3 b<br>n RX FIFO bur<br>n RX Buffer 14<br>n RX Buffer 1<br>n RX Buffer 0                     | '0' = Bit is cle<br>its<br>ffer<br>↓               | ,                | x = Bit is unkr             | nown  |  |  |

| -n = Value at<br>bit 15-12   | F3BP<3:0>:<br>1111 = Filter<br>1110 = Filter<br>0001 = Filter<br>0000 = Filter<br>F2BP<3:0>: | '1' = Bit is set<br>RX Buffer Mas<br>hits received in<br>hits received in<br>hits received in<br>hits received in<br>RX Buffer Mas | k for Filter 3 b<br>n RX FIFO bur<br>n RX Buffer 14<br>n RX Buffer 1<br>n RX Buffer 0<br>k for Filter 2 b | '0' = Bit is cle<br>its<br>ffer<br>its (same value | ared             | x = Bit is unkr             | nown  |  |  |

| R/W-0                                                                                       | R/W-0                                                                        | R/W-0                                    | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |  |  |  |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------|--------|------------------------------------|--------|--------------------|--------|--|--|--|--|

| F7MSK1                                                                                      | F7MSK0                                                                       | F6MSK1                                   | F6MSK0 | F5MSK1                             | F5MSK0 | F4MSK1             | F4MSK0 |  |  |  |  |

| bit 15                                                                                      |                                                                              |                                          |        |                                    |        |                    | bit 8  |  |  |  |  |

|                                                                                             |                                                                              |                                          |        |                                    |        |                    |        |  |  |  |  |

| R/W-0                                                                                       | R/W-0                                                                        | R/W-0                                    | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0  |  |  |  |  |

| F3MSK1                                                                                      | F3MSK0                                                                       | F2MSK1                                   | F2MSK0 | F1MSK1                             | F1MSK0 | F0MSK1             | F0MSK0 |  |  |  |  |

| bit 7                                                                                       |                                                                              |                                          |        |                                    |        |                    | bit 0  |  |  |  |  |

|                                                                                             |                                                                              |                                          |        |                                    |        |                    |        |  |  |  |  |

| Legend:                                                                                     |                                                                              |                                          |        |                                    |        |                    |        |  |  |  |  |

| R = Readable                                                                                | e bit                                                                        | W = Writable bit                         |        | U = Unimplemented bit, read as '0' |        |                    |        |  |  |  |  |

| -n = Value at                                                                               | POR                                                                          | '1' = Bit is set                         |        | '0' = Bit is cleared               |        | x = Bit is unknown |        |  |  |  |  |

|                                                                                             |                                                                              |                                          |        |                                    |        |                    |        |  |  |  |  |

| bit 15-14                                                                                   | F7MSK<1:0>                                                                   | F7MSK<1:0>: Mask Source for Filter 7 bit |        |                                    |        |                    |        |  |  |  |  |

|                                                                                             | 11 = Reserved                                                                |                                          |        |                                    |        |                    |        |  |  |  |  |

|                                                                                             | 10 = Acceptance Mask 2 registers contain mask                                |                                          |        |                                    |        |                    |        |  |  |  |  |

|                                                                                             |                                                                              | nce Mask 1 reg                           | •      |                                    |        |                    |        |  |  |  |  |

|                                                                                             | •                                                                            | nce Mask 0 reg                           |        |                                    |        |                    |        |  |  |  |  |

| bit 13-12 <b>F6MSK&lt;1:0&gt;:</b> Mask Source for Filter 6 bit (same values as bits 15-14) |                                                                              |                                          |        |                                    |        |                    |        |  |  |  |  |

| bit 11-10                                                                                   |                                                                              |                                          |        |                                    |        |                    |        |  |  |  |  |

| bit 9-8 <b>F4MSK&lt;1:0&gt;:</b> Mask Source for Filter 4 bit (same values as bits 15-14)   |                                                                              |                                          |        |                                    |        |                    |        |  |  |  |  |

| bit 7-6                                                                                     | it 7-6 F3MSK<1:0>: Mask Source for Filter 3 bit (same values as bits 15-14)  |                                          |        |                                    |        |                    |        |  |  |  |  |

| bit 5-4                                                                                     | bit 5-4 F2MSK<1:0>: Mask Source for Filter 2 bit (same values as bits 15-14) |                                          |        |                                    |        |                    |        |  |  |  |  |

|                                                                                             |                                                                              |                                          |        |                                    |        |                    |        |  |  |  |  |

F1MSK<1:0>: Mask Source for Filter 1 bit (same values as bits 15-14)

FOMSK<1:0>: Mask Source for Filter 0 bit (same values as bits 15-14)

#### REGISTER 21-18: CxFMSKSEL1: CANx FILTERS 7-0 MASK SELECTION REGISTER 1

bit 3-2

bit 1-0

### **REGISTER 25-6: PTGSDLIM: PTG STEP DELAY LIMIT REGISTER**<sup>(1,2)</sup>

| R/W-0  | R/W-0        | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|--------|--------------|-------|--------|----------|-------|-------|-------|--|--|--|--|--|

|        |              |       | PTGSDL | IM<15:8> |       |       |       |  |  |  |  |  |

| bit 15 | bit 15 bit 8 |       |        |          |       |       |       |  |  |  |  |  |

|        |              |       |        |          |       |       |       |  |  |  |  |  |

| R/W-0  | R/W-0        | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|        |              |       | PTGSDL | _IM<7:0> |       |       |       |  |  |  |  |  |

| bit 7  |              |       |        |          |       |       | bit 0 |  |  |  |  |  |

|        |              |       |        |          |       |       |       |  |  |  |  |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |