Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

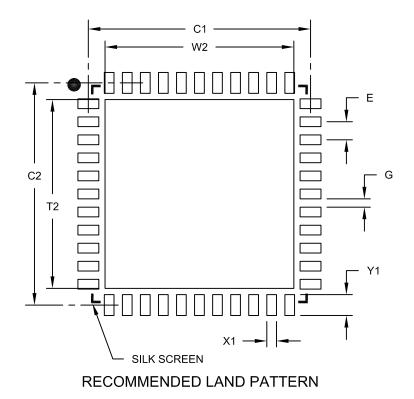

| Mounting Type              | Surface Mount                                                                    |

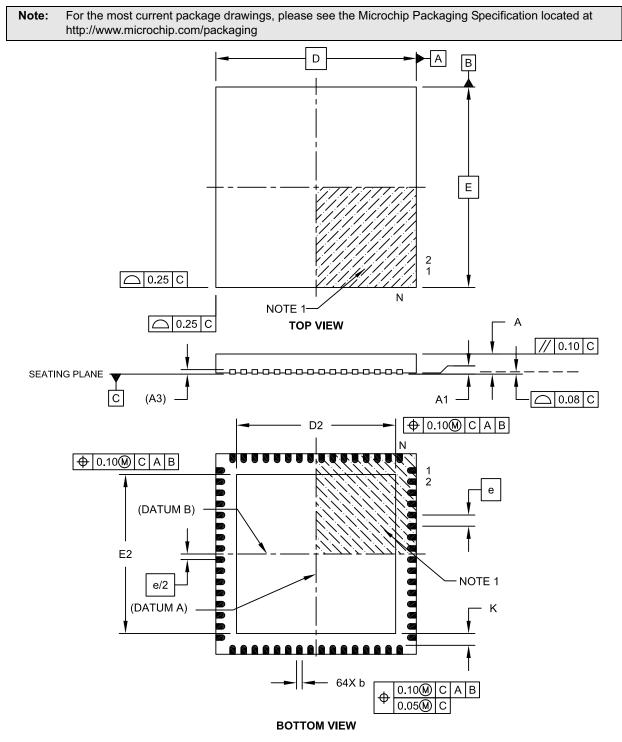

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm310-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

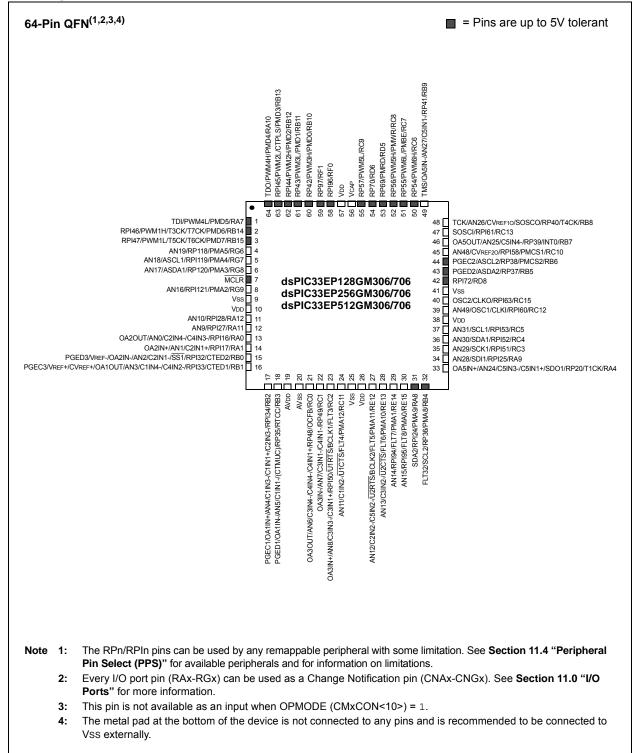

#### Pin Diagrams (Continued)

### dsPIC33EPXXXGM3XX/6XX/7XX

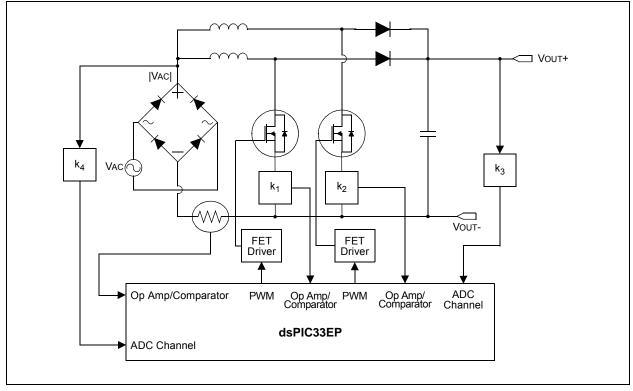

#### FIGURE 2-7: INTERLEAVED PFC

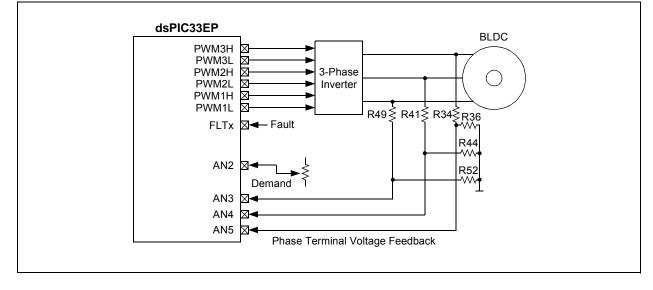

#### FIGURE 2-8: BEMF VOLTAGE MEASURED USING THE ADC MODULE

#### 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "CPU" (DS70359), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word, with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle, effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

#### 3.1 Registers

The dsPIC33EPXXXGM3XX/6XX/7XX devices have sixteen 16-bit Working registers in the programmer's model. Each of the Working registers can act as a data, address or address offset register. The 16th Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

#### 3.2 Instruction Set

The device instruction set has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

#### 3.3 Data Space Addressing

The Base Data Space can be addressed as 4K words or 8 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operate solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EP devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Space boundary is device-specific.

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space at any 16K program word boundary. The program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Data Space Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. Refer to "Data Memory" (DS70595) and "Program Memory" (DS70613) in the "dsPIC33/ PIC24 Family Reference Manual" for more details on EDS, PSV and table accesses.

On dsPIC33EP devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

#### 3.4 Addressing Modes

The CPU supports these addressing modes:

- · Inherent (no operand)

- Relative

- Literal

- Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

#### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup>                                                                                                                                                                                                                                                                                                                                 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9) 000 = CPU Interrupt Priority Level is 0 (8) |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                          |

|         | 1 = REPEAT loop is in progress<br>0 = REPEAT loop is not in progress                                                                                                                                                                                                                                                                                                                                |

| bit 3   | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                             |

|         | <ul><li>1 = Result was negative</li><li>0 = Result was non-negative (zero or positive)</li></ul>                                                                                                                                                                                                                                                                                                    |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                            |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                              |

| bit 1   | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                              |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = A carry-out from the Most Significant bit (MSb) of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                                                                                                                                                                     |

- **Note 1:** The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **2:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **3:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

| U-0          |                                                                      |                                                   |                            | DAMA              |                 | DAMA            |            |

|--------------|----------------------------------------------------------------------|---------------------------------------------------|----------------------------|-------------------|-----------------|-----------------|------------|

|              | R/W-0                                                                | R/W-0                                             | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0      |

|              |                                                                      |                                                   |                            | U4CTSR<6:0>       | >               |                 | h:t 0      |

| pit 15       |                                                                      |                                                   |                            |                   |                 |                 | bit 8      |

| U-0          | R/W-0                                                                | R/W-0                                             | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0      |

| _            |                                                                      |                                                   |                            | U4RXR<6:0>        |                 |                 |            |

| bit 7        |                                                                      |                                                   |                            |                   |                 |                 | bit 0      |

| Legend:      |                                                                      |                                                   |                            |                   |                 |                 |            |

| R = Readab   | ole bit                                                              | W = Writable                                      | bit                        | U = Unimplen      | nented bit, rea | d as '0'        |            |

| -n = Value a | at POR                                                               | '1' = Bit is set                                  |                            | '0' = Bit is clea | ared            | x = Bit is unkr | nown       |

|              |                                                                      | <b>0&gt;:</b> Assign UAR<br>1-2 for input pin     |                            |                   | o the Correspo  | onding RPn/RPI  | n Pin bits |

|              | (see Table 1 <sup>-</sup><br>1111111 = I<br>•<br>•                   | 1-2 for input pin<br>nput tied to RP <sup>7</sup> | selection nun<br>124       |                   | o the Corresp   | onding RPn/RPI  | n Pin bits |

|              | (see Table 1 <sup>-</sup><br>1111111 =  <br>•<br>•<br>•<br>0000001 = | 1-2 for input pin                                 | selection nun<br>124<br>P1 |                   | o the Corresp   | onding RPn/RPI  | n Pin bits |

| bit 7        | (see Table 1'<br>1111111 =  <br>•<br>•<br>0000001 =  <br>0000000 =   | 1-2 for input pin<br>nput tied to RP              | selection nun<br>124<br>P1 |                   | o the Correspo  | onding RPn/RPI  | n Pin bits |

#### REGISTER 11-22: RPINR28: PERIPHERAL PIN SELECT INPUT REGISTER 28

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

- bit 6-4

SYNCSRC<2:0>: Synchronous Source Selection bits<sup>(1)</sup>

111 = Reserved

...

...

...

100 = Reserved

011 = PTGO17<sup>(2)</sup>

010 = PTGO16<sup>(2)</sup>

001 = Reserved

000 = SYNCI1

bit 3-0

SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits<sup>(1)</sup>

1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event

...

0001 = 1:2 Postscaler generates Special Event Trigger on every second compare match event

...

0001 = 1:1 Postscaler generates Special Event Trigger on every second compare match event

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

| HS/HC-0    | ) HS/HC-0                            | HS/HC-0                                                                                                         | R/W-0                         | R/W-0              | R/W-0                | R/W-0                | R/W-0               |

|------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------|----------------------|----------------------|---------------------|

| FLTSTAT(   | (1) CLSTAT <sup>(1)</sup>            | TRGSTAT                                                                                                         | FLTIEN                        | CLIEN              | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |

| bit 15     |                                      |                                                                                                                 |                               |                    |                      | •                    | bit 8               |

|            |                                      |                                                                                                                 |                               |                    |                      |                      |                     |

| R/W-0      | R/W-0                                | R/W-0                                                                                                           | U-0                           | R/W-0              | R/W-0                | R/W-0                | R/W-0               |

| DTC1       | DTC0                                 | DTCP <sup>(3)</sup>                                                                                             | <u> </u>                      | MTBS               | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |

| bit 7      |                                      |                                                                                                                 |                               |                    |                      |                      | bit                 |

|            |                                      |                                                                                                                 |                               |                    |                      |                      |                     |

| Legend:    |                                      | HC = Hardware                                                                                                   |                               |                    | are Settable bit     |                      |                     |

| R = Reada  |                                      | W = Writable b                                                                                                  | it                            | -                  | mented bit, rea      |                      |                     |

| -n = Value | at POR                               | '1' = Bit is set                                                                                                |                               | '0' = Bit is cle   | eared                | x = Bit is unkr      | IOWN                |

| bit 15     |                                      | ault Interrupt Sta                                                                                              | tue hit(1)                    |                    |                      |                      |                     |

| DIL 15     |                                      | errupt is pending                                                                                               |                               |                    |                      |                      |                     |

|            |                                      | interrupt is pending                                                                                            |                               |                    |                      |                      |                     |

|            | This bit is cle                      | ared by setting:                                                                                                | FLTIEN = 0.                   |                    |                      |                      |                     |

| bit 14     | CLSTAT: Cu                           | rrent-Limit Interi                                                                                              | upt Status bit <sup>(1)</sup> | )                  |                      |                      |                     |

|            |                                      | imit interrupt is                                                                                               |                               |                    |                      |                      |                     |

|            |                                      | nt-limit interrupt<br>ared by setting:                                                                          |                               |                    |                      |                      |                     |

| bit 13     |                                      | rigger Interrupt                                                                                                |                               |                    |                      |                      |                     |

| DIC 15     |                                      | ngger menupt<br>nterrupt is pendi                                                                               |                               |                    |                      |                      |                     |

|            |                                      | r interrupt is pe                                                                                               | •                             |                    |                      |                      |                     |

|            | This bit is cle                      | ared by setting:                                                                                                | TRGIEN = 0.                   |                    |                      |                      |                     |

| bit 12     |                                      | It Interrupt Enat                                                                                               |                               |                    |                      |                      |                     |

|            |                                      | errupt is enabled<br>errupt is disabled                                                                         |                               | TAT bit is clear   | red                  |                      |                     |

| bit 11     | CLIEN: Curre                         | ent-Limit Interru                                                                                               | pt Enable bit                 |                    |                      |                      |                     |

|            |                                      | imit interrupt is of init interrupt is of init interrupt is of the second second second second second second se |                               | e CLSTAT bit i     | s cleared            |                      |                     |

| bit 10     |                                      | gger Interrupt E                                                                                                |                               |                    |                      |                      |                     |

|            |                                      | event generate                                                                                                  |                               | equest             |                      |                      |                     |

|            |                                      | vent interrupts a                                                                                               |                               | d the TRGSTA       | T bit is cleared     |                      |                     |

| bit 9      | ITB: Indepen                         | ident Time Base                                                                                                 | e Mode bit <sup>(2)</sup>     |                    |                      |                      |                     |

|            |                                      | register provide<br>egister provides                                                                            |                               |                    |                      | ator                 |                     |

| bit 8      | MDCS: Mast                           | er Duty Cycle R                                                                                                 | legister Select I             | oit <sup>(2)</sup> |                      |                      |                     |

|            | 1 = MDC reg                          | ister provides d<br>gister provides d                                                                           | uty cycle inform              | nation for this F  | -                    |                      |                     |

| Note 1:    | Software must cle                    | ear the interrupt                                                                                               | status here and               | d in the corres    | ponding IFSx b       | it in the interru    | pt controller.      |

|            | These bits should                    | •                                                                                                               |                               | -                  | •                    |                      |                     |

|            | DTC<1:0> = 11 fo                     | -                                                                                                               |                               |                    |                      |                      |                     |

|            | The Independent<br>CAM bit is ignore |                                                                                                                 | 5 = 1) mode mu                | st be enabled i    | to use Center-A      | Aligned mode. I      | If ITB = 0, the     |

|            |                                      |                                                                                                                 |                               |                    |                      |                      |                     |

#### REGISTER 16-11: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

| R/W-0         | R/W-0       | R/W-0                                 | U-0          | U-0              | U-0             | U-0               | U-0    |

|---------------|-------------|---------------------------------------|--------------|------------------|-----------------|-------------------|--------|

| FRMEN         | SPIFSD      | FRMPOL                                | —            | _                | _               | —                 | —      |

| bit 15        |             |                                       |              |                  |                 |                   | bit 8  |

|               |             |                                       |              |                  |                 |                   |        |

| U-0           | U-0         | U-0                                   | U-0          | U-0              | U-0             | R/W-0             | R/W-0  |

|               |             | —                                     |              |                  | _               | FRMDLY            | SPIBEN |

| bit 7         |             |                                       |              |                  |                 |                   | bit 0  |

|               |             |                                       |              |                  |                 |                   |        |

| Legend:       |             |                                       |              |                  |                 |                   |        |

| R = Readable  | e bit       | W = Writable b                        | bit          | U = Unimpler     | nented bit, rea | ad as '0'         |        |

| -n = Value at | POR         | '1' = Bit is set                      |              | '0' = Bit is cle | ared            | x = Bit is unkr   | nown   |

|               |             |                                       |              |                  |                 |                   |        |

| bit 15        |             | med SPIx Suppo                        |              | _                |                 |                   |        |

|               |             |                                       | •            | cpin is used as  | the Frame Sy    | nc pulse input/or | utput) |

| 1.11.4.4      |             | SPIx support is o                     |              |                  |                 |                   |        |

| bit 14        |             | x Frame Sync F                        |              | on Control bit   |                 |                   |        |

|               |             | /nc pulse input (<br>/nc pulse output |              |                  |                 |                   |        |

| bit 13        | -           | ame Sync Pulse                        | . ,          |                  |                 |                   |        |

|               |             | /nc pulse is activ                    | ,            |                  |                 |                   |        |

|               |             | /nc pulse is activ                    | U U          |                  |                 |                   |        |

| bit 12-2      | Unimplemen  | ted: Read as '0                       | ,            |                  |                 |                   |        |

| bit 1         | FRMDLY: Fra | ame Sync Pulse                        | Edge Select  | t bit            |                 |                   |        |

|               |             | /nc pulse coinci                      |              |                  |                 |                   |        |

|               | -           | nc pulse preced                       |              |                  |                 |                   |        |

| bit 0         |             | x Enhanced Bu                         |              | bit              |                 |                   |        |

|               |             | d Buffer is enabl                     |              | d modo)          |                 |                   |        |

|               |             | d Buffer is disab                     | ieu (Standan | u moue)          |                 |                   |        |

#### REGISTER 18-3: SPIxCON2: SPIx CONTROL REGISTER 2

| R/W-0              | R/W-0                                                                                            | R/W-0                                                                                                                             | R/W-0                                                                                   | R/W-0                                                        | R/W-0                 | R/W-0           | R/W-0          |

|--------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------|-----------------|----------------|

| ALRMEN             | CHIME                                                                                            | AMASK3                                                                                                                            | AMASK2                                                                                  | AMASK1                                                       | AMASK0                | ALRMPTR1        | ALRMPTR0       |

| bit 15             |                                                                                                  |                                                                                                                                   | 1                                                                                       | 1                                                            |                       |                 | bit 8          |

|                    |                                                                                                  |                                                                                                                                   |                                                                                         |                                                              |                       |                 |                |

| R/W-0              | R/W-0                                                                                            | R/W-0                                                                                                                             | R/W-0                                                                                   | R/W-0                                                        | R/W-0                 | R/W-0           | R/W-0          |

| ARPT7              | ARPT6                                                                                            | ARPT5                                                                                                                             | ARPT4                                                                                   | ARPT3                                                        | ARPT2                 | ARPT1           | ARPT0          |

| bit 7              |                                                                                                  |                                                                                                                                   |                                                                                         |                                                              |                       |                 | bit (          |

| Legend:            |                                                                                                  |                                                                                                                                   |                                                                                         |                                                              |                       |                 |                |

| R = Readable       | e bit                                                                                            | W = Writable                                                                                                                      | bit                                                                                     | U = Unimplem                                                 | nented bit, rea       | d as '0'        |                |

| -n = Value at      | POR                                                                                              | '1' = Bit is set                                                                                                                  |                                                                                         | '0' = Bit is clea                                            | ared                  | x = Bit is unkr | nown           |

|                    |                                                                                                  |                                                                                                                                   |                                                                                         |                                                              |                       |                 |                |

| bit 15             |                                                                                                  | larm Enable bit                                                                                                                   |                                                                                         |                                                              |                       |                 |                |

|                    | 1 = Alarm is<br>CHIME :                                                                          | enabled (clear                                                                                                                    | ed automatica                                                                           | lly after an ala                                             | rm event wher         | never ARP1<7:0  | 0 > = 0x00 and |

|                    | 0 = Alarm is                                                                                     | ,                                                                                                                                 |                                                                                         |                                                              |                       |                 |                |

| bit 14             | CHIME: Chir                                                                                      | ne Enable bit                                                                                                                     |                                                                                         |                                                              |                       |                 |                |

|                    | 1 = Chime is                                                                                     | s enabled; ARP                                                                                                                    | T<7:0> bits are                                                                         | e allowed to rol                                             | l over from 0x        | 00 to 0xFF      |                |

|                    | 0 = Chime is                                                                                     | s disabled; ARP                                                                                                                   | T<7:0> bits st                                                                          | op once they re                                              | each 0x00             |                 |                |

| bit 13-10          |                                                                                                  | >: Alarm Mask                                                                                                                     | Configuration                                                                           | bits                                                         |                       |                 |                |

|                    |                                                                                                  | y half second                                                                                                                     |                                                                                         |                                                              |                       |                 |                |

|                    | 0001 = Ever                                                                                      | y secona<br>y 10 seconds                                                                                                          |                                                                                         |                                                              |                       |                 |                |

|                    | 0011 = Ever                                                                                      |                                                                                                                                   |                                                                                         |                                                              |                       |                 |                |

|                    |                                                                                                  | y 10 minutes                                                                                                                      |                                                                                         |                                                              |                       |                 |                |

|                    | 0101 = Ever                                                                                      |                                                                                                                                   |                                                                                         |                                                              |                       |                 |                |

|                    | 0110 = Once<br>0111 = Once                                                                       |                                                                                                                                   |                                                                                         |                                                              |                       |                 |                |

|                    | 1000 = Once                                                                                      |                                                                                                                                   |                                                                                         |                                                              |                       |                 |                |

|                    |                                                                                                  |                                                                                                                                   |                                                                                         |                                                              |                       |                 |                |

|                    |                                                                                                  | e a year (except                                                                                                                  |                                                                                         | ired for Februa                                              | ry 29th, once e       | every 4 years)  |                |

|                    | 101x = Rese                                                                                      | e a year (except<br>erved – do not u                                                                                              | se                                                                                      | ired for Februa                                              | ry 29th, once e       | every 4 years)  |                |

| hit 9-8            | 101x = Rese<br>11xx = Rese                                                                       | e a year (except<br>erved – do not u<br>erved – do not u                                                                          | ise                                                                                     |                                                              |                       | every 4 years)  |                |

| bit 9-8            | 101x = Rese<br>11xx = Rese<br>ALRMPTR<                                                           | e a year (except<br>erved – do not u<br>erved – do not u<br><b>1:0&gt;:</b> Alarm Val                                             | ise<br>ise<br>ue Register W                                                             | indow Pointer                                                | bits                  |                 | The            |

| bit 9-8            | 101x = Rese<br>11xx = Rese<br>ALRMPTR<<br>Points to the                                          | e a year (except<br>erved – do not u<br>erved – do not u                                                                          | ise<br>lise<br>ue Register W<br>Alarm Value re                                          | indow Pointer l<br>egisters when r                           | bits<br>eading the AL | RMVAL register  |                |

|                    | 101x = Rese<br>11xx = Rese<br>ALRMPTR<<br>Points to the<br>ALRMPTR<                              | e a year (except<br>erved – do not u<br>erved – do not u<br>fros: Alarm Val<br>corresponding                                      | ise<br>ise<br>ue Register W<br>Alarm Value re<br>ements on eve                          | indow Pointer<br>egisters when r<br>ery read or write        | bits<br>eading the AL | RMVAL register  |                |

|                    | 101x = Rese<br>11xx = Rese<br>ALRMPTR<<br>Points to the<br>ALRMPTR<<br>ARPT<7:0>:                | e a year (except<br>erved – do not u<br>erved – do not u<br>1:0>: Alarm Val<br>corresponding<br>1:0> value decre                  | ise<br>ue Register W<br>Alarm Value re<br>ements on eve<br>Counter Value                | indow Pointer<br>egisters when r<br>ry read or write<br>bits | bits<br>eading the AL | RMVAL register  |                |

|                    | 101x = Rese<br>11xx = Rese<br>ALRMPTR<<br>Points to the<br>ALRMPTR<<br>ARPT<7:0>:                | e a year (except<br>erved – do not u<br>erved – do not u<br>1:0>: Alarm Valu<br>corresponding<br>1:0> value decre<br>Alarm Repeat | ise<br>ue Register W<br>Alarm Value re<br>ements on eve<br>Counter Value                | indow Pointer<br>egisters when r<br>ry read or write<br>bits | bits<br>eading the AL | RMVAL register  |                |

|                    | 101x = Rese<br>11xx = Rese<br>ALRMPTR<<br>Points to the<br>ALRMPTR<<br>ARPT<7:0>:                | e a year (except<br>erved – do not u<br>erved – do not u<br>1:0>: Alarm Valu<br>corresponding<br>1:0> value decre<br>Alarm Repeat | ise<br>ue Register W<br>Alarm Value re<br>ements on eve<br>Counter Value                | indow Pointer<br>egisters when r<br>ry read or write<br>bits | bits<br>eading the AL | RMVAL register  |                |

| bit 9-8<br>bit 7-0 | 101x = Rese<br>11xx = Rese<br>ALRMPTR<<br>Points to the<br>ALRMPTR<7<br>ARPT<7:0>:<br>11111111 = | e a year (except<br>erved – do not u<br>erved – do not u<br>1:0>: Alarm Valu<br>corresponding<br>1:0> value decre<br>Alarm Repeat | use<br>Register W<br>Alarm Value re<br>ements on eve<br>Counter Value<br>at 255 more ti | indow Pointer<br>egisters when r<br>ry read or write<br>bits | bits<br>eading the AL | RMVAL register  |                |

#### REGISTER 27-3: ALCFGRPT: ALARM CONFIGURATION REGISTER

#### 28.1 PMP Control Registers

#### REGISTER 28-1: PMCON: PARALLEL MASTER PORT CONTROL REGISTER<sup>(3)</sup>

| R/W-0                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                     | R/W-0                                  | R/W-0              | R/W-0        |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------|--------------|

| PMPEN                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PSIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ADRMUX1                                                                                                                                                                                                                                                                        | ADRMUX0                                                                                                                   | PTBEEN                                 | PTWREN             | PTRDEN       |

| bit 15                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                |                                                                                                                           |                                        |                    | bit 8        |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                |                                                                                                                           |                                        |                    |              |