Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      |                                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, Motor Control PWM, POR, PWM, WDT               |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) |                                                                                  |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm310-h-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name<br>Name<br>NameAddr.Bit 10Bit 10Bit 10Bit 10Bit 10Bit 10Bit 10Bit 20Bit 10Bit 20Bit                                                                                                                                                                                                                                                                                                                                                                                              |               |                                                            |       |       |       |        |            |              |              |            |            |        |         | MAP     | ISTER N | SREG   | TIMER  | 4-4:  | TABLE 4 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------------------------|-------|-------|-------|--------|------------|--------------|--------------|------------|------------|--------|---------|---------|---------|--------|--------|-------|---------|

| PR1       0102       Period Register 1         TICON       0104       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       —       TSYNC       TCS       —         TIM2       0106       -       Time?       Period Register       FORATE       TCKPS1       TCKPS1       TCKPS1       TCKPS0       —       TSYNC       TCS       —         TIM3       0106       -       Time?       Register for 32-bit timer operations only)       -       TTSYNC       TCS       —         TMR3       0104       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         PR3       0102       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         T3CON       0112       TON       -       TSIDL       -       -       -       TGATE       TCKPS1       TCKPS0       TSID       -       TCS       -         TMR4       0114       Ton       -       TSIDL       -       -       TImer6 Holding Register (                                                                                                                                                           | All<br>Resets | Bit 0                                                      | Bit 1 | Bit 2 | Bit 3 | Bit 4  | Bit 5      | Bit 6        | Bit 7        | Bit 8      | Bit 9      | Bit 10 | Bit 11  | Bit 12  | Bit 13  | Bit 14 | Bit 15 | Addr. | -       |

| TICON       014//       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       TSYNC       TCS       -         TMR2       0106       -       Timer2       Register       -       TGATE       TCKPS1       TCKPS0       -       TSYNC       TCS       -         TMR3       0106       -       Timer3       Register       -       TS2-bit filter operations only)       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       TCKPS0       T32       -       TCS       -       -       -       -       TCS       -       -       TCS       -       -       TCS       -       TCS       -       TCS       -       TCS       -       TCS       -       TCS       1       1       1                                                                                                                                                                                                    | 0000          |                                                            |       |       |       |        |            | r            | er1 Registe  | Tim        |            |        |         |         |         |        |        | 0100  | TMR1    |

| TMR2       0.106       Timer2 Register         TMR3HLD       0108       Timer3 Holding Register (For 32-bit timer operations only)         TMR3       0100       Period Register 2         PR2       0100       Period Register 2         PR3       0110       TON       -       TSIDL       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         T3CON       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4HD       0110       TON       -       TSIDL       -       -       -       -       TGCR       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5HD       0116       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5HD                                                                                                                                                                                             | FFFF          | -                                                          |       |       |       |        |            | 1            | od Register  | Peri       |            |        |         |         |         |        |        | 0102  | PR1     |

| TMR3HLD       0108       Timer3 Holding Register (For 32-bit timer operations only)         TMR3       010A       Timer3 Register         PR2       010C       Period Register 2         PR3       0100       Period Register 2         PR3       0100       Timer3 Register 2         PR3       0100       Timer3 Register 2         PR3       0110       TON -       TISDL -       -       Period Register 1         TMR4       0110       ToN -       Timer3 Register         TMR4       0114       Timer5 Holding Register (For 32-bit timer operations only)         TMR5       OTIR       TIMEr5 Register         TMR5       OTIR       ToKPS1       TCKPS1                                                                                                                                                                                                                                                                                                                          | 0000          | _                                                          | TCS   | TSYNC | _     | TCKPS0 | TCKPS1     | TGATE        |              | _          | _          | _      | —       | _       | TSIDL   | _      | TON    | 0104  | T1CON   |

| TMR3       010A       Timer3 Register 7         PR2       010C       Period Register 3         TZCON       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         T3CON       0112       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5       0114       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5       0118       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         T4CON       0112       TON       <                                                                                                                                                                                                               | 0000          | Timer2 Register                                            |       |       |       |        |            |              |              |            |            | 0106   | TMR2    |         |         |        |        |       |         |

| PR2       010C       Period Register 2         PR3       010E       Period Register 3         T2CON       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T3CON       0112       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR5HLD       0118       -       -       -       -       -       Period Register 4       Period Register 4         PR5       0110       -       -       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T4CON       0112       TON       -       TSIDL       -       -       -       -       TGA                                                                                                                                                                                                                   | xxxx          | Timer3 Holding Register (For 32-bit timer operations only) |       |       |       |        |            |              |              |            |            |        | 0108    | TMR3HLD |         |        |        |       |         |

| PR3         010E         Period Register 3           T2CON         0110         TON         -         TSIDL         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T3CON         0112         TON         -         TSIDL         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T3CON         0112         TON         -         TSIDL         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           TMR4         0114         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           TMR5         0116         -         -         -         TGATE         TCKPS0         T32         -         TCS         -          PR4         011A         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T4CON         011E         TON         -         TSIDL         -         -         -         TGATE         TCKPS0         T32                                                                                                             | 0000          |                                                            |       |       |       |        |            | r            | er3 Registe  | Tim        |            |        |         |         |         |        |        | 010A  | TMR3    |

| T2CON         0110         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS1         TCKPS0         T32         -         TCS         -           T3CON         0112         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS1         TCKPS0         T32         -         TCS         -           TMR4         0114         -         -         -         -         TGATE         TCKPS1         TCKPS0         -         -         TCS         -           TMR4         0114         -         -         -         -         TGS0         -         -         TCS         10116         -         -         TGATE         TCKPS1         TCKPS0         T32         -         TCS         -         -         TCS         -                                                                                                  | FFFF          | Period Register 2                                          |       |       |       |        |            |              |              |            |            |        | 010C    | PR2     |         |        |        |       |         |

| T3CON     0112     TON     —     TSIDL     —     —     —     —     TGATE     TCKPS0     —     —     —     TCS     —       TMR4     0114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FFFF          | Period Register 3                                          |       |       |       |        |            |              |              |            |            | 010E   | PR3     |         |         |        |        |       |         |

| TMR4     0114     Immediate     Timer4 Register       TMR4LD     0116     Timer5 Holding Register (For 32-bit timer operations only)       TMR5     0118       PR4     011A       PR5     011C       TMR6     012       TMR6     012       TMR7     012       TMR7     012       PR6     012       TMR7     0126       TMR7     0126       PR7     0128       PR7     0128       PR7     0120       TON     —       TMR7     0126       PR7     0128       PR7     0120       TON     —       TMR7     0126       PR7     0120       TON     —       TMR7     0126       PR7     0128       PR7     0120       TON     —       TMR7     0126       PR7     0120       TON     —       TMR7     0126       PR7     0120       TON     —       TMR8     0130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0000          | —                                                          | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | _            | _          |            | —      | —       |         | TSIDL   |        | TON    | 0110  | T2CON   |

| TMRSHLD       0116       TimerS Holding Register (For 32-bit timer operations only)         TMRS       0118       TimerS Register         PR4       011A       Period Register 4         PR5       011C       Period Register 5         T4CON       011E       TON       -       TSIDL       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T5CON       0120       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR6       0120       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR6       0122       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR7       0126       Timer7 Holding Register (For 32-bit timer operations only)       TImer7 Register       Period Register 6         PR7       012A       TSIDL       -       -       -       -       TGATE       TCKPS0       T32                                                                                                                                                                | 0000          | —                                                          | TCS   | —     | —     | TCKPS0 | TCKPS1     | TGATE        | _            | _          |            | —      | —       |         | TSIDL   |        | TON    | 0112  | T3CON   |

| TMR5       0118       Timer5 Register         PR4       011A       Period Register 4         PR5       011C       Period Register 5         T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T4CON       011E       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0122       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       —       —       —       —       —       —       —       —       —       —       TCS       —       —       —       —       —       —       TCS       P       P       P       P       P       P       P       P       P       P <t< td=""><td>0000</td><td></td><td></td><td></td><td></td><td></td><td></td><td>r</td><td>er4 Registe</td><td>Tim</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>0114</td><td>TMR4</td></t<>       | 0000          |                                                            |       |       |       |        |            | r            | er4 Registe  | Tim        |            |        |         |         |         |        |        | 0114  | TMR4    |

| PR4       011A       Period Register 4         PR5       011C       Period Register 5         T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0122       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR7       0126                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xxxx          | Timer5 Holding Register (For 32-bit timer operations only) |       |       |       |        |            |              |              |            |            | 0116   | TMR5HLD |         |         |        |        |       |         |

| PR5       011C       Period Register 5         T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         TMR6       0122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0000          | Timer5 Register                                            |       |       |       |        |            |              |              |            |            |        | 0118    | TMR5    |         |        |        |       |         |

| T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FFFF          | Period Register 4                                          |       |       |       |        |            |              |              |            |            |        | 011A    | PR4     |         |        |        |       |         |

| T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       —       —       TCS       —         TMR6       0122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FFFF          |                                                            |       |       |       |        |            | 5            | od Register  | Peri       |            |        |         |         |         |        |        | 011C  | PR5     |

| TMR6       0122       Timer6 Register         TMR7HLD       0124       Timer7 Holding Register (For 32-bit timer operations only)         TMR7       0126       Timer7 Register         PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       012C       TON       -       TSIDL       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR8       0130       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                           | 0000          | —                                                          | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | —            |            |            | —      | —       |         | TSIDL   | -      | TON    | 011E  | T4CON   |

| TMR7 HLD       0124       Timer7 Holding Register (For 32-bit timer operations only)         TMR7       0126       Timer7 Register         PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       0122       TON       -       TSIDL       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR8       0130       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       -       TImer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0000          | —                                                          | TCS   | —     | —     | TCKPS0 | TCKPS1     | TGATE        | —            |            |            | —      | —       |         | TSIDL   |        | TON    | 0120  | T5CON   |

| TMR7       0126       Timer7 Register         PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       012C       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR8       0130       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <td>0000</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>r</td> <td>ier6 Registe</td> <td>Tim</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>0122</td> <td>TMR6</td> | 0000          |                                                            |       |       |       |        |            | r            | ier6 Registe | Tim        |            |        |         |         |         |        |        | 0122  | TMR6    |

| PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       012C       TON       —       TSIDL       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T7CON       012E       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T7CON       012E       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         TMR8       0130       —       TSIDL       —       —       —       —       TImer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | xxxx          |                                                            |       |       |       |        | ions only) | timer operat | For 32-bit   | g Register | er7 Holdin | Time   |         |         |         |        |        | 0124  | TMR7HLD |

| PR7         012A         Period Register 7           T6CON         012C         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T7CON         012E         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T7CON         012E         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           TMR8         0130         -         TSIDL         -         -         -         TImer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0000          |                                                            |       |       |       |        |            | r            | er7 Registe  | Tim        |            |        |         |         |         |        |        | 0126  | TMR7    |

| T6CON     012C     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     T32     —     TCS     —       T7CON     012E     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     T32     —     TCS     —       T7CON     012E     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     —     —     TCS     —       TMR8     0130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | FFFF          |                                                            |       |       |       |        |            | 6            | od Register  | Peri       |            |        |         |         |         |        |        | 0128  | PR6     |

| T7CON     012E     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     —     —     TCS     —       TMR8     0130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FFFF          |                                                            |       |       |       |        |            | 7            | od Register  | Peri       |            |        |         |         |         |        |        | 012A  | PR7     |

| TMR8 0130 Timer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0000          | —                                                          | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | —            | —          | _          | —      | _       | —       | TSIDL   | _      | TON    | 012C  | T6CON   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0000          | —                                                          | TCS   | —     | _     | TCKPS0 | TCKPS1     | TGATE        | _            | —          | _          | —      | —       | —       | TSIDL   | _      | TON    | 012E  | T7CON   |

| TMR9HLD 0132 Timer9 Holding Register (For 32-bit timer operations only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0000          |                                                            |       |       |       |        |            | r            | er8 Registe  | Tim        |            |        |         |         |         |        |        | 0130  | TMR8    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | xxxx          |                                                            |       |       |       |        | ions only) | timer operat | For 32-bit   | g Register | er9 Holdin | Time   |         |         |         |        |        | 0132  | TMR9HLD |

| TMR9     0134     Timer9 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0000          | Timer9 Register                                            |       |       |       |        |            |              |              |            |            |        | 0134    | TMR9    |         |        |        |       |         |

| PR8 0136 Period Register 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FFFF          | Period Register 8                                          |       |       |       |        |            |              |              |            |            | 0136   | PR8     |         |         |        |        |       |         |

| PR9 0138 Period Register 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FFFF          | Period Register 9                                          |       |       |       |        |            |              |              |            | 0138       | PR9    |         |         |         |        |        |       |         |

| T8CON         013A         TON         —         TSIDL         —         —         —         —         TGATE         TCKPS1         TCKPS0         T32         —         TCS         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0000          | -                                                          | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | _            | _          | _          | _      | —       | _       | TSIDL   | _      | TON    | 013A  | T8CON   |

| T9CON     013C     TON     —     TSIDL     —     —     —     —     TGATE     TCKPS1     TCKPS0     —     —     TCS     —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0000          | -                                                          | TCS   | -     | _     | TCKPS0 | TCKPS1     | TGATE        | _            | _          | _          | _      | —       | —       | TSIDL   | _      | TON    | 013C  | T9CON   |

dsPIC33EPXXXGM3XX/6XX/7XX

### TABLE 4-4: TIMERS REGISTER MAP

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-30: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGM304/604 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|------------|------------|--------|--------|-------|-------|-------|------------|------------|--------|--------|--------|-------|-------|---------------|

| RPOR0       | 0680  | _      | -      |            | RP35R<5:0> |        |        |       |       | _     | _          | RP20R<5:0> |        |        |        |       | 0000  |               |

| RPOR1       | 0682  | _      | —      |            | RP37R<5:0> |        |        |       |       | —     | _          | RP36R<5:0> |        |        |        |       | 0000  |               |

| RPOR2       | 0684  |        | —      |            | RP39R<5:0> |        |        |       | —     | _     | RP38R<5:0> |            |        |        |        | 0000  |       |               |

| RPOR3       | 0686  |        | —      |            | RP41R<5:0> |        |        |       | —     | _     |            |            | RP40   | R<5:0> |        |       | 0000  |               |

| RPOR4       | 0688  |        | —      |            |            | RP43F  | R<5:0> |       |       | —     |            | RP42R<5:0> |        |        |        |       |       | 0000          |

| RPOR5       | 068A  |        | —      |            | RP49R<5:0> |        |        |       |       | —     |            | RP48R<5:0> |        |        |        |       | 0000  |               |

| RPOR6       | 068C  |        | —      | RP55R<5:0> |            |        |        | —     |       |       |            | RP54       | R<5:0> |        |        | 0000  |       |               |

| RPOR7       | 068E  |        | —      |            | RP57R<5:0> |        |        |       |       | _     | _          |            |        | RP56   | R<5:0> |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-31: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGM306/706 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7      | Bit 6      | Bit 5      | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|------------|------------|--------|--------|-------|-------|------------|------------|------------|-------|--------|--------|-------|-------|---------------|

| RPOR0       | 0680  | _      | —      |            | RP35R<5:0> |        |        |       |       | —          | _          | RP20R<5:0> |       |        |        |       |       | 0000          |

| RPOR1       | 0682  | _      | —      |            | RP37R<5:0> |        |        |       |       | —          | _          | RP36R<5:0> |       |        |        |       |       | 0000          |

| RPOR2       | 0684  | _      | —      |            | RP39R<5:0> |        |        |       | —     | _          | RP38R<5:0> |            |       |        |        | 0000  |       |               |

| RPOR3       | 0686  | _      | _      |            | RP41R<5:0> |        |        |       | _     | _          |            |            | RP40  | R<5:0> |        |       | 0000  |               |

| RPOR4       | 0688  | _      | _      |            | RP43R<5:0> |        |        |       | _     | _          |            |            | RP42I | R<5:0> |        |       | 0000  |               |

| RPOR5       | 068A  | _      | _      |            |            | RP49F  | ₹<5:0> |       |       | _          | _          |            |       | RP48   | R<5:0> |       |       | 0000          |

| RPOR6       | 068C  | _      | _      |            |            | RP55F  | ₹<5:0> |       |       | _          | _          | RP54R<5:0> |       |        |        | 0000  |       |               |

| RPOR7       | 068E  | _      | _      |            | RP57R<5:0> |        |        |       |       | _          | _          | RP56R<5:0> |       |        |        |       | 0000  |               |

| RPOR8       | 0690  |        | _      | RP70R<5:0> |            |        |        | —     | _     | RP69R<5:0> |            |            |       |        | 0000   |       |       |               |

| RPOR9       | 0692  | _      | _      |            | RP97R<5:0> |        |        |       |       | _          | _          | _          | _     |        | _      | _     | _     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

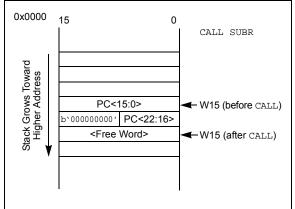

### 4.3.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack     |

|-------|-----------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the |

|       | hardware.                               |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGM3XX/6XX/7XX devices and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack, working from lower toward higher addresses. Figure 4-13 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-13. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain the Software Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore, restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a 'C' development environment

#### FIGURE 4-13: C.

#### CALL STACK FRAME

## 4.4 Instruction Addressing Modes

The addressing modes shown in Table 4-66 form the basis of the addressing modes optimized to support the specific features of the individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

#### 4.4.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

### 4.4.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- · Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

Note: Not all instructions support all of the addressing modes given above. Individual instructions can support different subsets of these addressing modes. NOTES:

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0              | U-0            | U-0   |

|-----------------|-------|------------------|-------|------------------|------------------|----------------|-------|

| —               | —     | —                | —     | —                | —                | _              | —     |

| bit 15          |       |                  |       |                  |                  |                | bit 8 |

|                 |       |                  |       |                  |                  |                |       |

| U-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0          | R/W-0 |

| —               |       |                  |       | COFSR<6:02       | >                |                |       |

| bit 7           |       |                  |       |                  |                  |                | bit 0 |

|                 |       |                  |       |                  |                  |                |       |

| Legend:         |       |                  |       |                  |                  |                |       |

| R = Readable b  | oit   | W = Writable I   | bit   | U = Unimpler     | mented bit, read | as '0'         |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unk | nown  |

## REGISTER 11-19: RPINR25: PERIPHERAL PIN SELECT INPUT REGISTER 25

#### bit 15-7 Unimplemented: Read as '0'

bit 6-0 **COFSR<6:0>:** Assign DCI Frame Sync Input (COFS) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111100 = Input tied to RPI124

•

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

| U-0              | R/W-0                                                                                                    | R/W-0                                                                                           | R/W-0                                                       | R/W-0                     | R/W-0           | R/W-0                              | R/W-0 |

|------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------|-----------------|------------------------------------|-------|

| _                |                                                                                                          |                                                                                                 |                                                             | U3CTSR<6:0                | >               |                                    |       |

| bit 15           | ·                                                                                                        |                                                                                                 |                                                             |                           |                 |                                    | bit 8 |

|                  |                                                                                                          |                                                                                                 |                                                             |                           |                 |                                    |       |

| U-0              | R/W-0                                                                                                    | R/W-0                                                                                           | R/W-0                                                       | R/W-0                     | R/W-0           | R/W-0                              | R/W-0 |

|                  |                                                                                                          |                                                                                                 |                                                             | U3RXR<6:0>                |                 |                                    |       |

| bit 7            |                                                                                                          |                                                                                                 |                                                             |                           |                 |                                    | bit 0 |

|                  |                                                                                                          |                                                                                                 |                                                             |                           |                 |                                    |       |

| Legend:          |                                                                                                          |                                                                                                 |                                                             |                           |                 |                                    |       |

| R = Readabl      | e bit                                                                                                    | W = Writable                                                                                    | bit                                                         | U = Unimplen              | nented bit, rea | ad as '0'                          |       |

| -n = Value at    | POR                                                                                                      | '1' = Bit is set                                                                                |                                                             | '0' = Bit is clea         | ared            | x = Bit is unkr                    | nown  |

| bit 7<br>bit 6-0 | (see Table 1'<br>1111111 = I<br>0000001 = I<br>0000000 = I<br>Unimplement<br>U3RXR<6:00<br>(see Table 1' | 1-2 for input pin<br>nput tied to RP<br>nput tied to CMI<br>nput tied to Vss<br>nted: Read as ' | selection nur<br> 24<br>P1<br>3 Receive (U<br>selection nur | nbers)<br>I3RX) to the Co |                 | onding RPn/RPI<br>RPn/RPIn Pin bit |       |

|                  |                                                                                                          | nput tied to CM<br>nput tied to Vss                                                             |                                                             |                           |                 |                                    |       |

### REGISTER 11-21: RPINR27: PERIPHERAL PIN SELECT INPUT REGISTER 27

|                 |                           |                          | (1)                        |

|-----------------|---------------------------|--------------------------|----------------------------|

| REGISTER 11-42: | <b>RPOR12: PERIPHERAL</b> | <b>PIN SELECT OUTPUT</b> | REGISTER 12 <sup>(1)</sup> |

| U-0          | U-0                                                                                                                                        | R/W-0                                   | R/W-0 | R/W-0                                   | R/W-0         | R/W-0       | R/W-0 |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------|-----------------------------------------|---------------|-------------|-------|--|--|--|

| -            | -                                                                                                                                          |                                         |       | RP127R                                  | -             |             |       |  |  |  |

| bit 15       |                                                                                                                                            |                                         |       |                                         |               |             | bit 8 |  |  |  |

|              |                                                                                                                                            |                                         |       |                                         |               |             |       |  |  |  |

| U-0          | U-0                                                                                                                                        | R/W-0                                   | R/W-0 | R/W-0                                   | R/W-0         | R/W-0       | R/W-0 |  |  |  |

| —            | —                                                                                                                                          |                                         |       | RP126R                                  | <5:0>         |             |       |  |  |  |

| bit 7        |                                                                                                                                            |                                         |       |                                         |               |             | bit 0 |  |  |  |

|              |                                                                                                                                            |                                         |       |                                         |               |             |       |  |  |  |

| Legend:      |                                                                                                                                            |                                         |       |                                         |               |             |       |  |  |  |

| R = Readab   | le bit                                                                                                                                     | W = Writable                            | bit   | U = Unimpleme                           | nted bit, rea | d as '0'    |       |  |  |  |

| -n = Value a | t POR                                                                                                                                      | '1' = Bit is set                        |       | '0' = Bit is cleared x = Bit is unknown |               |             |       |  |  |  |

|              |                                                                                                                                            |                                         |       |                                         |               |             |       |  |  |  |

| bit 15-14    | Unimplem                                                                                                                                   | ented: Read as '                        | 0'    |                                         |               |             |       |  |  |  |

| bit 13-8     |                                                                                                                                            | :0>: Peripheral C<br>11-3 for periphera | •     | on is Assigned to F<br>mbers)           | RP127 Outp    | ut Pin bits |       |  |  |  |

| bit 7-6      | Unimplemented: Read as '0'                                                                                                                 |                                         |       |                                         |               |             |       |  |  |  |

| bit 5-0      | <b>RP126R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP126 Output Pin bits (see Table 11-3 for peripheral function numbers) |                                         |       |                                         |               |             |       |  |  |  |

Note 1: This register is not available on dsPIC33EPXXXGM30X/604/706 devices.

NOTES:

# 19.0 INTER-INTEGRATED CIRCUIT<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70000195), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX family of devices contains two Inter-Integrated Circuit ( $I^2C$ ) modules: I2C1 and I2C2.

The  $I^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface. The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx pin is clock.

- The SDAx pin is data.

The  $I^2C$  module offers the following key features:

- I<sup>2</sup>C Interface Supporting both Master and Slave modes of Operation.

- I<sup>2</sup>C Slave mode Supports 7 and 10-Bit Addressing.

- I<sup>2</sup>C Master mode Supports 7 and 10-Bit Addressing.

- I<sup>2</sup>C Port Allows Bidirectional Transfers Between Master and Slaves.

- Serial Clock Synchronization for I<sup>2</sup>C Port can be used as a Handshake Mechanism to Suspend and Resume Serial Transfer (SCLREL control).

- I<sup>2</sup>C Supports Multi-Master Operation, Detects Bus Collision and Arbitrates Accordingly.

- Intelligent Platform Management Interface (IPMI)

Support

- System Management Bus (SMBus) Support

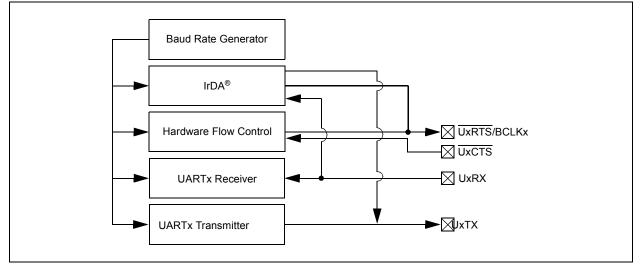

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX family of devices contains four UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGM3XX/6XX/7XX device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: Hardware flow control using UxRTS and UxCTS is not available on all pin count devices. See the "Pin Diagrams" section for availability.

The primary features of the UART module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop Bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for All UART Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA<sup>®</sup> Support

A simplified block diagram of the UART module is shown in Figure 20-1. The UART module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2013-2014 Microchip Technology Inc.

### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                              |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                       |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                      |