Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | -                                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | · ·                                                                              |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm310-h-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR<br>Name | Addr. | Bit 15 | Bit 14                | Bit 13               | Bit 12  | Bit 11  | Bit 10        | Bit 9   | Bit 8   | Bit 7    | Bit 6    | Bit 5    | Bit 4         | Bit 3         | Bit 2         | Bit 1     | Bit 0         | All<br>Resets |

|-------------|-------|--------|-----------------------|----------------------|---------|---------|---------------|---------|---------|----------|----------|----------|---------------|---------------|---------------|-----------|---------------|---------------|

| INTCON1     | 08C0  | NSTDIS | OVAERR                | OVBERR               | COVAERR | COVBERR | OVATE         | OVBTE   | COVTE   | SFTACERR | DIV0ERR  | DMACERR  | MATHERR       | ADDRERR       | STKERR        | OSCFAIL   | _             | 0000          |

| INTCON2     | 08C2  | GIE    | DISI                  | SWTRAP               | _       | _       | _             | _       | _       | —        | _        | _        | _             | —             | INT2EP        | INT1EP    | INT0EP        | 0000          |

| INTCON3     | 08C4  | _      | _                     | _                    | —       | _       | _             | _       | —       | —        | _        | DAE      | DOOVR         | —             | —             | —         | -             | 0000          |

| INTCON4     | 08C6  | —      | _                     | _                    | —       | _       | _             | _       | —       | —        | _        | _        | —             | —             | —             | —         | SGHT          | 0000          |

| IFS0        | 0800  | _      | DMA1IF                | AD1IF                | U1TXIF  | U1RXIF  | SPI1IF        | SPI1EIF | T3IF    | T2IF     | OC2IF    | IC2IF    | DMA0IF        | T1IF          | OC1IF         | IC1IF     | INTOIF        | 0000          |

| IFS1        | 0802  | U2TXIF | U2RXIF                | INT2IF               | T5IF    | T4IF    | OC4IF         | OC3IF   | DMA2IF  | IC8IF    | IC7IF    | AD2IF    | INT1IF        | CNIF          | CMPIF         | MI2C1IF   | SI2C1IF       | 0000          |

| IFS2        | 0804  | T6IF   | _                     | PMPIF <sup>(1)</sup> | OC8IF   | OC7IF   | OC6IF         | OC5IF   | IC6IF   | IC5IF    | IC4IF    | IC3IF    | DMA3IF        | _             | _             | SPI2IF    | SPI2EIF       | 0000          |

| IFS3        | 0806  | FLT1IF | RTCCIF <sup>(2)</sup> |                      | DCIIF   | DCIEIF  | <b>QEI1IF</b> | PSEMIF  | _       | _        | INT4IF   | INT3IF   | T9IF          | T8IF          | MI2C2IF       | SI2C2IF   | T7IF          | 0000          |

| IFS4        | 0808  | _      | _                     | CTMUIF               | FLT4IF  | QEI2IF  | FLT3IF        | PSESMIF | _       | _        | _        | _        | _             | CRCIF         | U2EIF         | U1EIF     | FLT2IF        | 0000          |

| IFS5        | 080A  | PWM2IF | PWM1IF                | _                    | _       | SPI3IF  | SPI3EIF       | U4TXIF  | U4RXIF  | U4EIF    | _        | _        | _             | U3TXIF        | <b>U3RXIF</b> | U3EIF     | -             | 0000          |

| IFS6        | 080C  | _      | _                     | _                    | —       | _       | _             | _       | —       | —        | _        | _        | —             | PWM6IF        | PWM5IF        | PWM4IF    | PWM3IF        | 0000          |

| IFS8        | 0810  | JTAGIF | ICDIF                 | _                    | _       | _       | -             | _       | _       | _        | -        | _        | _             | _             | _             | _         | _             | 0000          |

| IFS9        | 0812  | -      |                       | _                    | _       | _       | -             | _       | _       | _        | PTG3IF   | PTG2IF   | PTG1IF        | PTG0IF        | PTGWDTIF      | PTGSTEPIF | _             | 0000          |

| IEC0        | 0820  | _      | DMA1IE                | AD1IE                | U1TXIE  | U1RXIE  | SPI1IE        | SPI1EIE | T3IE    | T2IE     | OC2IE    | IC2IE    | DMA0IE        | T1IE          | OC1IE         | IC1IE     | <b>INTOIE</b> | 0000          |

| IEC1        | 0822  | U2TXIE | U2RXIE                | INT2IE               | T5IE    | T4IE    | OC4IE         | OC3IE   | DMA2IE  | IC8IE    | IC7IE    | AD2IE    | INT1IE        | CNIE          | CMPIE         | MI2C1IE   | SI2C1IE       | 0000          |

| IEC2        | 0824  | T6IE   | _                     | PMPIE <sup>(1)</sup> | OC8IE   | OC7IE   | OC6IE         | OC5IE   | IC6IE   | IC5IE    | IC4IE    | IC3IE    | <b>DMA3IE</b> | —             |               | SPI2IE    | SPI2EIE       | 0000          |

| IEC3        | 0826  | FLT1IE | RTCCIE <sup>(2)</sup> | -                    | DCIIE   | DCIEIE  | <b>QEI1IE</b> | PSEMIE  |         | _        | INT4IE   | INT3IE   | T9IE          | T8IE          | MI2C2IE       | SI2C2IE   | T7IE          | 0000          |

| IEC4        | 0828  | —      | _                     | CTMUIE               | FLT4IE  | QEI2IE  | FLT3IE        | PSESMIE |         | —        | _        | _        |               | CRCIE         | U2EIE         | U1EIE     | FLT2IE        | 0000          |

| IEC5        | 082A  | PWM2IE | PWM1IE                |                      | -       | SPI3IE  | SPI3EIE       | U4TXIE  | U4RXIE  | U4EIE    | _        | _        |               | <b>U3TXIE</b> | <b>U3RXIE</b> | U3EIE     |               | 0000          |

| IEC6        | 082C  | —      | _                     |                      | -       | —       | _             |         |         | —        | _        | _        |               | PWM6IE        | PWM5IE        | PWM4IE    | PWM3IE        | 0000          |

| IEC8        | 0830  | JTAGIE | ICDIE                 |                      | —       | —       | -             | -       | —       | —        | —        | —        | —             | -             | —             | —         | -             | 0000          |

| IEC9        | 0832  | —      | —                     |                      | —       | —       | -             | -       | —       | —        | PTG3IE   | PTG2IE   | PTG1IE        | PTG0IE        | PTGWDTIE      | PTGSTEPIE | -             | 0000          |

| IPC0        | 0840  | _      | T1IP2                 | T1IP1                | T1IP0   | —       | OC1IP2        | OC1IP1  | OC1IP0  | —        | IC1IP2   | IC1IP1   | IC1IP0        | —             | INT0IP2       | INT0IP1   | INT0IP2       | 4444          |

| IPC1        | 0842  | _      | T2IP2                 | T2IP1                | T2IP0   | —       | OC2IP2        | OC2IP1  | OC2IP0  | —        | IC2IP2   | IC2IP1   | IC2IP0        | —             | DMA0IP2       | DMA0IP1   | DMA0IP2       | 4444          |

| IPC2        | 0844  | _      | U1RXIP2               | U1RXIP1              | U1RXIP0 | —       | SPI1IP2       | SPI1IP1 | SPI1IP0 | —        | SPI1EIP2 | SPI1EIP1 | SPI1EIP0      | —             | T3IP2         | T3IP1     | T3IP0         | 4444          |

| IPC3        | 0846  | —      | _                     | _                    | —       | —       | DMA1IP2       | DMA1IP1 | DMA1IP0 | _        | AD1IP2   | AD1IP1   | AD1IP0        | —             | U1TXIP2       | U1TXIP1   | U1TXIP0       | 4444          |

| IPC4        | 0848  | _      | CNIP2                 | CNIP1                | CNIP0   | —       | CMPIP2        | CMPIP1  | CMPIP0  | —        | MI2C1IP2 | MI2C1IP1 | MI2C1IP0      | —             | SI2C1IP2      | SI2C1IP1  | SI2C1IP0      | 4444          |

| IPC5        | 084A  | —      | IC8IP2                | IC8IP1               | IC8IP0  | _       | IC7IP2        | IC7IP1  | IC7IP0  | _        | AD2IP2   | AD2IP1   | AD2IP0        | —             | INT1IP2       | INT1IP1   | INT1IP0       | 4444          |

| IPC6        | 084C  | —      | T4IP2                 | T4IP1                | T4IP0   | _       | OC4IP2        | OC4IP1  | OC4IP0  | _        | OC3IP2   | OC3IP1   | OC3IP0        | —             | DMA2IP2       | DMA2IP1   | DMA2IP0       | 4444          |

| IPC7        | 084E  | —      | U2TXIP2               | U2TXIP1              | U2TXIP0 | _       | U2RXIP2       | U2RXIP1 | U2RXIP0 | —        | INT2IP2  | INT2IP1  | INT2IP0       | —             | T5IP2         | T5IP1     | T5IP0         | 4444          |

| IPC8        | 0850  | —      | _                     | _                    | —       | _       |               | _       |         | _        | SPI2IP2  | SPI2IP1  | SPI2IP0       | —             | SPI2EIP2      | SPI2EIP1  | SPI2EIP0      | 4444          |

| IPC9        | 0852  | —      | IC5IP2                | IC5IP1               | IC5IP0  | —       | IC4IP2        | IC4IP1  | IC4IP0  | —        | IC3IP2   | IC3IP1   | IC3IP0        | —             | DMA3IP2       | DMA3IP1   | DMA3IP0       | 4444          |

| IPC10       | 0854  | —      | OC7IP2                | OC7IP1               | OC7IP0  | —       | OC6IP2        | OC6IP1  | OC6IP0  | —        | OC5IP2   | OC5IP1   | OC5IP0        | —             | IC6IP2        | IC6IP1    | IC6IP0        | 4444          |

#### TABLE 4-3: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGM3XX DEVICES

Note 1: The PMPIF/PMPIE/PMPIPx flags are not available on 44-pin devices.

2: The RTCCIF/RTCCIE/RTCCIPx flags are not available on 44-pin devices.

# TABLE 4-45: DMA CONTROLLER REGISTER MAP

| IADLE 4- | 4J.   |        |        |             |        |        |        | -     |        |         |         |         |         | -       |         | -       |         |               |

|----------|-------|--------|--------|-------------|--------|--------|--------|-------|--------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13      | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

| DMA0CON  | 0B00  | CHEN   | SIZE   | DIR         | HALF   | NULLW  | —      | _     | —      | —       | _       | AMODE1  | AMODE0  | —       | —       | MODE1   | MODE0   | 0000          |

| DMA0REQ  | 0B02  | FORCE  | _      | _           | _      | _      | _      | _     | _      | IRQSEL7 | IRQSEL6 | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA0STAL | 0B04  |        |        |             |        |        |        |       | STA<1  | 5:0>    |         |         |         |         |         |         |         | 0000          |

| DMA0STAH | 0B06  |        | _      | _           | _      | _      | _      | _     | _      |         |         |         | STA<2   | 3:16>   |         |         |         | 0000          |

| DMA0STBL | 0B08  |        |        |             |        |        |        |       | STB<1  | 5:0>    |         |         |         |         |         |         |         | 0000          |

| DMA0STBH | 0B0A  | —      | —      | _           | _      | —      | —      | —     | _      |         |         |         | STB<2   | 3:16>   |         |         |         | 0000          |

| DMA0PAD  | 0B0C  |        |        |             |        |        |        |       | PAD<1  | 5:0>    |         |         |         |         |         |         |         | 0000          |

| DMA0CNT  | 0B0E  |        | _      |             |        |        |        |       |        | CNT<1   | 3:0>    |         |         |         |         |         |         | 0000          |

| DMA1CON  | 0B10  | CHEN   | SIZE   | DIR         | HALF   | NULLW  | _      | _     | _      | _       | _       | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA1REQ  | 0B12  | FORCE  | _      | _           |        | _      | _      | _     | _      | IRQSEL7 | IRQSEL6 | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | 00FF          |

| DMA1STAL | 0B14  |        |        |             |        |        |        |       | STA<1  | 5:0>    |         |         |         |         |         |         |         | 0000          |

| DMA1STAH | 0B16  | Ι      | _      | _           | _      | —      | —      | —     | _      |         |         |         | STA<2   | 3:16>   |         |         |         | 0000          |

| DMA1STBL | 0B18  |        |        |             |        |        |        |       | STB<1  | 5:0>    |         |         |         |         |         |         |         | 0000          |

| DMA1STBH | 0B1A  |        | _      | _           | _      | _      | _      | _     | _      |         |         |         | STB<2   | 3:16>   |         |         |         | 0000          |

| DMA1PAD  | 0B1C  |        |        |             |        |        |        |       | PAD<1  | 5:0>    |         |         |         |         |         |         |         | 0000          |

| DMA1CNT  | 0B1E  | _      | _      |             |        |        |        |       |        | CNT<1   | 3:0>    |         |         |         |         |         |         | 0000          |

| DMA2CON  | 0B20  | CHEN   | SIZE   | DIR         | HALF   | NULLW  | _      | _     | _      | _       | _       | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA2REQ  | 0B22  | FORCE  | _      | _           | _      | _      | _      | —     | _      | IRQSEL7 | IRQSEL6 | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | 00FF          |

| DMA2STAL | 0B24  |        |        |             |        |        |        |       | STA<1  | 5:0>    |         |         |         |         |         |         |         | 0000          |

| DMA2STAH | 0B26  |        | _      | _           | _      | _      | _      | _     | _      |         |         |         | STA<2   | 3:16>   |         |         |         | 0000          |

| DMA2STBL | 0B28  |        |        |             |        |        |        |       | STB<1  | 5:0>    |         |         |         |         |         |         |         | 0000          |

| DMA2STBH | 0B2A  | _      | _      | _           | _      | _      | _      | _     | _      |         |         |         | STB<2   | 3:16>   |         |         |         | 0000          |

| DMA2PAD  | 0B2C  |        |        |             |        |        |        |       | PAD<1  | 5:0>    |         |         |         |         |         |         |         | 0000          |

| DMA2CNT  | 0B2E  | —      | —      |             |        |        |        |       |        | CNT<1   | 3:0>    |         |         |         |         |         |         | 0000          |

| DMA3CON  | 0B30  | CHEN   | SIZE   | DIR         | HALF   | NULLW  | _      | _     | _      | _       | _       | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA3REQ  | 0B32  | FORCE  | _      | -           | _      | -      | _      | -     | _      | IRQSEL7 | IRQSEL6 | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA3STAL | 0B34  |        |        |             |        |        |        |       | STA<1  | 5:0>    |         |         |         |         |         |         |         | 0000          |

| DMA3STAH | 0B36  |        | _      | _           | _      | _      | _      | _     | _      |         |         |         | STA<2   | 3:16>   |         |         |         | 0000          |

| DMA3STBL | 0B38  |        |        |             |        |        |        |       | STB<1  | 5:0>    |         |         |         |         |         |         |         | 0000          |

| DMA3STBH | 0B3A  | _      | _      | _           |        | _      | _      | _     | _      |         |         |         | STB<2   | 3:16>   |         |         |         | 0000          |

| DMA3PAD  | 0B3C  |        |        |             |        |        |        |       | PAD<1  | 5:0>    |         |         |         |         |         |         |         | 0000          |

| DMA3CNT  | 0B3E  | _      | _      |             |        |        |        |       |        | CNT<1   | 3:0>    |         |         |         |         |         |         | 0000          |

| DMAPWC   | 0BF0  | _      | _      | —           | —      | _      | —      | —     | —      | —       | —       | —       | _       | PWCOL3  | PWCOL2  | PWCOL1  | PWCOL0  | 0000          |

| DMARQC   | 0BF2  | _      | _      | _           |        | _      | —      | _     | _      | —       |         | _       | _       | RQCOL3  | RQCOL2  | RQCOL1  | RQCOL0  | 0000          |

| DMAPPS   | 0BF4  | _      | _      | _           | _      | _      | —      | _     | —      | —       | _       | —       | _       | PPST3   | PPST2   | PPST1   | PPST0   | 0000          |

| DMALCA   | 0BF6  | _      | _      | _           | _      | _      | -      | _     | —      | —       | —       | —       | _       |         | LSTCH   | 1<3:0>  |         | 000F          |

| DSADRL   | 0BF8  |        |        |             |        |        |        |       | DSADR< | 15:0>   |         |         |         | •       |         |         |         | 0000          |

| DSADRH   | 0BFA  | _      | _      | —           |        | —      | —      | _     | —      |         |         |         | DSADR<  | <23:16> |         |         |         | 0000          |

| Logond   |       |        |        | Posot valuo |        |        |        |       |        |         |         |         |         |         |         |         |         | <u>.</u>      |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-61: PORTG REGISTER MAP FOR dsPIC33EPXXXGM310/710 DEVICES

|          | • • • |        | • • • • • • • |        |        |         |        |       |                |       |       |       |       |       |        |        |       |               |

|----------|-------|--------|---------------|--------|--------|---------|--------|-------|----------------|-------|-------|-------|-------|-------|--------|--------|-------|---------------|

| SFR Name | Addr. | Bit 15 | Bit 14        | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9 | Bit 8          | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

| TRISG    | 0E60  |        |               |        |        | TRISG<1 | 5:6>   |       |                |       |       | -     | —     |       | TRISC  | 6<3:0> |       | 03C0          |

| PORTG    | 0E62  |        |               |        |        | RG<15:  | 6>     |       |                |       |       | _     | _     |       | RG<    | 3:0>   |       | xxxx          |

| LATG     | 0E64  |        |               |        |        | LATG<15 | 5:6>   |       |                |       |       | _     | _     |       | LATG   | <3:0>  |       | xxxx          |

| ODCG     | 0E66  |        |               |        |        | ODCG<1  | 5:6>   |       |                |       |       | _     | _     |       | ODCO   | G<3:0> |       | 0000          |

| CNENG    | 0E68  |        |               |        |        | CNIEG<1 | 5:6>   |       |                |       |       | —     | _     |       | CNIEC  | G<3:0> |       | 0000          |

| CNPUG    | 0E6A  |        |               |        |        | CNPUG<1 | 15:6>  |       |                |       |       | —     | _     |       | CNPU   | G<3:0> |       | 0000          |

| CNPDG    | 0E6C  |        |               |        |        | CNPDG<1 | 15:6>  |       |                |       |       | —     | _     |       | CNPD   | G<3:0> |       | 0000          |

| ANSELG   | 0E6E  | ANSG15 |               | _      | _      |         |        | ANSG< | 11:6>          |       |       | _     | _     | ANSG  | i<3:2> | _      |       | 0000          |

|          |       |        |               |        |        |         |        |       | and the second |       |       | •     | •     | •     |        | •      |       | •             |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-62: PORTG REGISTER MAP FOR dsPIC33EPXXXGM306/706 DEVICES

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISG    | 0E60  | _      | _      | _      | _      | _      |        |       | TRISC | 6<9:6> |       |       |       | —     | —     |       | —     | 03C0          |

| PORTG    | 0E62  | _      | _      | _      | _      | _      | _      |       | RG<   | 9:6>   |       | _     | _     | _     | _     | _     | _     | xxxx          |

| LATG     | 0E64  | —      | —      | _      | _      | —      | _      |       | LATG  | <9:6>  |       |       |       | —     | —     |       | —     | xxxx          |

| ODCG     | 0E66  | _      | _      | _      | _      | _      | _      |       | ODCO  | 6<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNENG    | 0E68  | _      | _      | _      | _      | _      | _      |       | CNIEC | G<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNPUG    | 0E6A  | —      | —      | _      | _      | —      | _      |       | CNPU  | G<9:6> |       |       |       | —     | —     |       | —     | 0000          |

| CNPDG    | 0E6C  | _      | _      | _      | _      | _      | _      |       | CNPD  | G<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| ANSELG   | 0E6E  | —      | _      | _      | _      | _      | _      |       | ANSO  | 6<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-63: PAD CONFIGURATION REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|----------|--------|---------------|

| PADCFG1   | 0EFE  | _      | _      |        | _      |        | _      | _     | _     | _     |       | _     | _     | _     | _     | RTSECSEL | PMPTTL | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

|                                                    | Vector | IRQ   |                   | Inte     | errupt Bit L | ocation      |

|----------------------------------------------------|--------|-------|-------------------|----------|--------------|--------------|

| Interrupt Source                                   | #      | #     | IVT Address       | Flag     | Enable       | Priority     |

| OC5 – Output Compare 5                             | 49     | 41    | 0x000066          | IFS2<9>  | IEC2<9>      | IPC10<6:4>   |

| OC6 – Output Compare 6                             | 50     | 42    | 0x000068          | IFS2<10> | IEC2<10>     | IPC10<10:8>  |

| OC7 – Output Compare 7                             | 51     | 43    | 0x00006A          | IFS2<11> | IEC2<11>     | IPC10<14:12> |

| OC8 – Output Compare 8                             | 52     | 44    | 0x00006C          | IFS2<12> | IEC2<12>     | IPC11<2:0>   |

| PMP – Parallel Master Port <sup>(2)</sup>          | 53     | 45    | 0x00006E          | IFS2<13> | IEC2<13>     | IPC11<6:4>   |

| Reserved                                           | 54     | 46    | 0x000070          | _        | _            | _            |

| T6 – Timer6                                        | 55     | 47    | 0x000072          | IFS2<15> | IEC2<15>     | IPC11<14:12> |

| T7 – Timer7                                        | 56     | 48    | 0x000074          | IFS3<0>  | IEC3<0>      | IPC12<2:0>   |

| SI2C2 – I2C2 Slave Event                           | 57     | 49    | 0x000076          | IFS3<1>  | IEC3<1>      | IPC12<6:4>   |

| MI2C2 – I2C2 Master Event                          | 58     | 50    | 0x000078          | IFS3<2>  | IEC3<2>      | IPC12<10:8>  |

| T8 – Timer8                                        | 59     | 51    | 0x00007A          | IFS3<3>  | IEC3<3>      | IPC12<14:12> |

| T9 – Timer9                                        | 60     | 52    | 0x00007C          | IFS3<4>  | IEC3<4>      | IPC13<2:0>   |

| INT3 – External Interrupt 3                        | 61     | 53    | 0x00007E          | IFS3<5>  | IEC3<5>      | IPC13<6:4>   |

| INT4 – External Interrupt 4                        | 62     | 54    | 0x000080          | IFS3<6>  | IEC3<6>      | IPC13<10:8>  |

| C2RX – CAN2 RX Data Ready <sup>(1)</sup>           | 63     | 55    | 0x000082          | IFS3<7>  | IEC3<7>      | IPC13<14:12> |

| C2 – CAN2 Event <sup>(1)</sup>                     | 64     | 56    | 0x000084          | IFS3<8>  | IEC3<8>      | IPC14<2:0>   |

| PSEM – PCPWM Primary Event                         | 65     | 57    | 0x000086          | IFS3<9>  | IEC3<9>      | IPC14<6:4>   |

| QEI1 – QEI1 Position Counter Compare               | 66     | 58    | 0x000088          | IFS3<10> | IEC3<10>     | IPC14<10:8>  |

| DCIE – DCI Fault Interrupt                         | 67     | 59    | 0x00008A          | IFS3<11> | IEC3<11>     | IPC14<14:12> |

| DCI – DCI Transfer Done                            | 68     | 60    | 0x00008C          | IFS3<12> | IEC3<12>     | IPC15<2:0>   |

| Reserved                                           | 69     | 61    | 0x00008E          | —        | —            | —            |

| RTCC – Real-Time Clock and Calendar <sup>(2)</sup> | 70     | 62    | 0x000090          | IFS3<14> | IEC3<14>     | IPC15<10:8>  |

| Reserved                                           | 71-72  | 63-64 | 0x000092-0x000094 | —        | _            | _            |

| U1E – UART1 Error Interrupt                        | 73     | 65    | 0x000096          | IFS4<1>  | IEC4<1>      | IPC16<6:4>   |

| U2E – UART2 Error Interrupt                        | 74     | 66    | 0x000098          | IFS4<2>  | IEC4<2>      | IPC16<10:8>  |

| CRC – CRC Generator Interrupt                      | 75     | 67    | 0x00009A          | IFS4<3>  | IEC4<3>      | IPC16<14:12> |

| Reserved                                           | 76-77  | 68-69 | 0x00009C-0x00009E | —        | —            | —            |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>         | 78     | 70    | 0x0000A0          | IFS4<6>  | IEC4<6>      | IPC17<10:8>  |

| C2TX – CAN2 TX Data Request <sup>(1)</sup>         | 79     | 71    | 0x0000A2          | IFS4<7>  | IEC4<7>      | IPC17<14:12> |

| Reserved                                           | 80     | 72    | 0x0000A4          | —        | —            | -            |

| PSESM – PCPWM Secondary Event                      | 81     | 73    | 0x0000A6          | IFS4<9>  | IEC4<9>      | IPC18<6:4>   |

| Reserved                                           | 82     | 74    | 0x0000A8          | —        | —            | -            |

| QEI2 – QEI2 Position Counter Compare               | 83     | 75    | 0x0000AA          | IFS4<11> | IEC4<11>     | IPC18<14:12> |

| Reserved                                           | 84     | 76    | 0x0000AC          | —        | —            | -            |

| CTMU – CTMU Interrupt                              | 85     | 77    | 0x0000AE          | IFS4<13> | IEC4<13>     | IPC19<6:4>   |

| Reserved                                           | 86-88  | 78-80 | 0x0000B0-0x0000B4 | —        | —            | -            |

| U3E – UART3 Error Interrupt                        | 89     | 81    | 0x0000B6          | IFS5<1>  | IEC5<1>      | IPC20<6:4>   |

| U3RX – UART3 Receiver                              | 90     | 82    | 0x0000B8          | IFS5<2>  | IEC5<2>      | IPC20<10:8>  |

| U3TX – UART3 Transmitter                           | 91     | 83    | 0x0000BA          | IFS5<3>  | IEC5<3>      | IPC20<14:12> |

| Reserved                                           | 92-94  | 84-86 | 0x0000BC-0x0000C0 |          |              | —            |

| U4E – UART4 Error Interrupt                        | 95     | 87    | 0x0000C2          | IFS5<7>  | IEC5<7>      | IPC21<14:12> |

| U4RX – UART4 Receiver                              | 96     | 88    | 0x0000C4          | IFS5<8>  | IEC5<8>      | IPC22<2:0>   |

| U4TX – UART4 Transmitter                           | 97     | 89    | 0x0000C6          | IFS5<9>  | IEC5<9>      | IPC22<6:4>   |

Note 1: This interrupt source is available on dsPIC33EPXXXGM6XX/7XX devices only.

2: This interrupt source is not available on 44-pin devices.

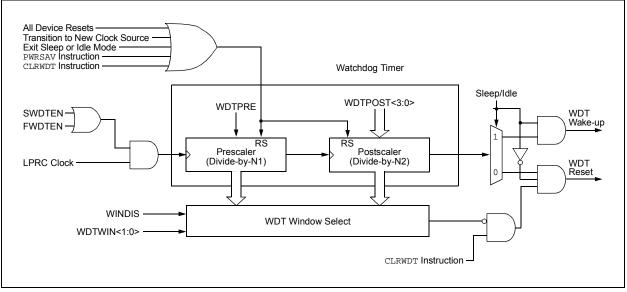

# 10.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To \_complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Watchdog Timer and Power-Saving Modes" (DS70615), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

The dsPIC33EPXXXGM3XX/6XX/7XX devices can manage power consumption in four ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- · Software-Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into Sleep mode

PWRSAV #IDLE\_MODE ; Put the device into Idle mode

## 10.1 Clock Frequency and Clock Switching

The dsPIC33EPXXXGM3XX/6XX/7XX devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

## 10.2 Instruction-Based Power-Saving Modes

The dsPIC33EPXXXGM3XX/6XX/7XX devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the Assembler Include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

# 13.1 Timer Control Registers

# REGISTER 13-1: TxCON (T2CON, T4CON, T6CON AND T8CON) CONTROL REGISTER

| R/W-0            | U-0                            | R/W-0                               | U-0            | U-0              | U-0             | U-0                | U-0   |

|------------------|--------------------------------|-------------------------------------|----------------|------------------|-----------------|--------------------|-------|

| TON              |                                | TSIDL                               | —              | —                | _               | —                  |       |

| bit 15           |                                |                                     |                |                  |                 |                    | bit 8 |

|                  |                                |                                     |                |                  |                 |                    |       |

| U-0              | R/W-0                          | R/W-0                               | R/W-0          | R/W-0            | U-0             | R/W-0              | U-0   |

|                  | TGATE                          | TCKPS1                              | TCKPS0         | T32              | _               | TCS <sup>(1)</sup> | _     |

| bit 7            |                                |                                     |                |                  |                 |                    | bit 0 |

|                  |                                |                                     |                |                  |                 |                    |       |

| Legend:          |                                |                                     |                |                  |                 |                    |       |

| R = Readable b   |                                | W = Writable                        |                | •                | nented bit, rea |                    |       |

| -n = Value at P0 | DR                             | '1' = Bit is set                    |                | '0' = Bit is cle | ared            | x = Bit is unkn    | iown  |

|                  |                                | 0.1.1                               |                |                  |                 |                    |       |

|                  | TON: Timerx                    |                                     |                |                  |                 |                    |       |

|                  | When T32 = 1<br>1 = Starts 32- |                                     |                |                  |                 |                    |       |

|                  | 0 = Stops 32-                  |                                     |                |                  |                 |                    |       |

|                  | When T32 =                     |                                     |                |                  |                 |                    |       |

|                  | 1 = Starts 16-                 |                                     |                |                  |                 |                    |       |

| bit 14           | 0 = Stops 16-                  | ted: Read as '                      | o'             |                  |                 |                    |       |

|                  | -                              | x Stop in Idle M                    |                |                  |                 |                    |       |

| bit 15           |                                | ues module op                       |                | device enters l  | dle mode        |                    |       |

|                  |                                | s module opera                      |                |                  |                 |                    |       |

| bit 12-7         | Unimplemen                     | ted: Read as '                      | 0'             |                  |                 |                    |       |

| bit 6            | TGATE: Time                    | erx Gated Time                      | Accumulation   | Enable bit       |                 |                    |       |

|                  | When TCS =                     |                                     |                |                  |                 |                    |       |

|                  | This bit is igno               |                                     |                |                  |                 |                    |       |

|                  | When TCS =<br>1 = Gated tim    | <u><i>u.</i></u><br>le accumulatior | n is enabled   |                  |                 |                    |       |

|                  |                                | e accumulation                      |                |                  |                 |                    |       |

| bit 5-4          | TCKPS<1:0>                     | : Timerx Input                      | Clock Prescal  | e Select bits    |                 |                    |       |

|                  | 11 = 1:256                     |                                     |                |                  |                 |                    |       |

|                  | 10 = 1:64<br>01 = 1:8          |                                     |                |                  |                 |                    |       |

|                  | 01 = 1.0<br>00 = 1.1           |                                     |                |                  |                 |                    |       |

| bit 3            | T32: 32-Bit Ti                 | mer Mode Sele                       | ect bit        |                  |                 |                    |       |

|                  | 1 = Timerx an                  | nd Timery form                      | a single 32-bi | t timer          |                 |                    |       |

|                  |                                | nd Timery act a                     |                | ners             |                 |                    |       |

|                  |                                | ted: Read as '                      |                |                  |                 |                    |       |

|                  |                                | Clock Source S                      |                |                  |                 |                    |       |

|                  |                                | clock is from pir                   | n, TxCK (on th | e rising edge)   |                 |                    |       |

|                  | 0 = Internal cl                |                                     |                |                  |                 |                    |       |

| bit 0            |                                | ted: Read as '                      | n'             |                  |                 |                    |       |

## REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = Capture timer is unsynchronized

- 11110 = Capture timer is unsynchronized

- 11101 = Capture timer is unsynchronized

- 11100 = CTMU trigger is the source for the capture timer synchronization

- 11011 = ADC1 interrupt is the source for the capture timer synchronization<sup>(5)</sup>

- 11010 = Analog Comparator 3 is the source for the capture timer synchronization<sup>(5)</sup>

- 11001 = Analog Comparator 2 is the source for the capture timer synchronization<sup>(5)</sup>

- 11000 = Analog Comparator 1 is the source for the capture timer synchronization<sup>(5)</sup>

- 10111 = Input Capture 8 interrupt is the source for the capture timer synchronization

- 10110 = Input Capture 7 interrupt is the source for the capture timer synchronization 10101 = Input Capture 6 interrupt is the source for the capture timer synchronization

- 10100 = Input Capture 5 interrupt is the source for the capture timer synchronization

- 10011 = Input Capture 4 interrupt is the source for the capture timer synchronization

- 10010 = Input Capture 3 interrupt is the source for the capture timer synchronization

- 10001 = Input Capture 2 interrupt is the source for the capture timer synchronization

- 10000 = Input Capture 1 interrupt is the source for the capture timer synchronization

- 01111 = GP Timer5 is the source for the capture timer synchronization

- 01110 = GP Timer4 is the source for the capture timer synchronization

- 01101 = GP Timer3 is the source for the capture timer synchronization 01100 = GP Timer2 is the source for the capture timer synchronization

- 01100 = GP Timer2 is the source for the capture timer synchronization 01011 = GP Timer1 is the source for the capture timer synchronization

- 01011 = OF Time is the source for the capture time synchronization (6)

- 01001 = Capture timer is unsynchronized

- 01000 = Output Compare 8 is the source for the capture timer synchronization

- 00111 = Output Compare 7 is the source for the capture timer synchronization

- 00110 = Output Compare 6 is the source for the capture timer synchronization

- 00101 = Output Compare 5 is the source for the capture timer synchronization

- 00100 = Output Compare 4 is the source for the capture timer synchronization

- 00011 = Output Compare 3 is the source for the capture timer synchronization

- 00010 = Output Compare 2 is the source for the capture timer synchronization

- 00001 = Output Compare 1 is the source for the capture timer synchronization

- 00000 = Capture timer is unsynchronized

- **Note 1:** The IC32 bit in both the Odd and Even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x module (ICx) has one PTG input source. See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1, IC5

PTGO9 = IC2, IC6

PTGO10 = IC3, IC7

PTGO11 = IC4, IC8

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits 11111 = OCxRS compare event is used for synchronization 11110 = INT2 is the source for compare timer synchronization 11101 = INT1 is the source for compare timer synchronization 11100 = CTMU trigger is the source for compare timer synchronization 11011 = ADC1 interrupt is the source for compare timer synchronization 11010 = Analog Comparator 3 is the source for compare timer synchronization 11001 = Analog Comparator 2 is the source for compare timer synchronization 11000 = Analog Comparator 1 is the source for compare timer synchronization 10111 = Input Capture 8 interrupt is the source for compare timer synchronization 10110 = Input Capture 7 interrupt is the source for compare timer synchronization 10101 = Input Capture 6 interrupt is the source for compare timer synchronization 10100 = Input Capture 5 interrupt is the source for compare timer synchronization 10011 = Input Capture 4 interrupt is the source for compare timer synchronization 10010 = Input Capture 3 interrupt is the source for compare timer synchronization 10001 = Input Capture 2 interrupt is the source for compare timer synchronization 10000 = Input Capture 1 interrupt is the source for compare timer synchronization 01111 = GP Timer5 is the source for compare timer synchronization 01110 = GP Timer4 is the source for compare timer synchronization 01101 = GP Timer3 is the source for compare timer synchronization 01100 = GP Timer2 is the source for compare timer synchronization 01011 = GP Timer1 is the source for compare timer synchronization 01010 = PTGx trigger is the source for compare timer synchronization<sup>(3)</sup> 01001 = Compare timer is unsynchronized 01000 = Output Compare 8 is the source for compare timer synchronization<sup>(1,2)</sup> 00111 = Output Compare 7 is the source for compare timer synchronization<sup>(1,2)</sup> 00110 = Output Compare 6 is the source for compare timer synchronization<sup>(1,2)</sup> 00101 = Output Compare 5 is the source for compare timer synchronization<sup>(1,2)</sup> 00100 = Output Compare 4 is the source for compare timer synchronization<sup>(1,2)</sup> 00011 = Output Compare 3 is the source for compare timer synchronization<sup>(1,2)</sup> 00010 = Output Compare 2 is the source for compare timer synchronization<sup>(1,2)</sup> 00001 = Output Compare 1 is the source for compare timer synchronization<sup>(1,2)</sup> 00000 = Compare timer is unsynchronized

- Note 1: Do not use the OCx module as its own synchronization or trigger source.

- 2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

- 3: Each Output Compare x module (OCx) has one PTG Trigger/Sync source. See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO4 = OC1, OC5 PTGO5 = OC2, OC6 PTGO6 = OC3, OC7 PTGO7 = OC4, OC8

# REGISTER 16-11: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7-6 | 6  | <b>DTC&lt;1:0&gt;:</b> Dead-Time Control bits<br>11 = Dead-Time Compensation mode                                                                                                                                                                                                                                                  |

|---------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |    | <ul> <li>10 = Dead-time function is disabled</li> <li>01 = Negative dead time is actively applied for Complementary Output mode</li> <li>00 = Positive dead time is actively applied for all Output modes</li> </ul>                                                                                                               |

| bit 5   |    | <b>DTCP:</b> Dead-Time Compensation Polarity bit <sup>(3)</sup>                                                                                                                                                                                                                                                                    |

|         |    | <u>When Set to '⊥':</u><br>If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.<br>If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                                                                                                                                                |

|         |    | <u>When Set to '<math>o</math>':</u><br>If DTCMPx = 0, PWMHx is shortened and PWMLx is lengthened.<br>If DTCMPx = 1, PWMLx is shortened and PWMHx is lengthened.                                                                                                                                                                   |

| bit 4   |    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                         |

| bit 3   |    | MTBS: Master Time Base Select bit                                                                                                                                                                                                                                                                                                  |

|         |    | <ul> <li>1 = PWMx generator uses the secondary master time base for synchronization and as the clock source for the PWMx generation logic (if secondary time base is available)</li> <li>0 = PWMx generator uses the primary master time base for synchronization and as the clock source for the PWMx generation logic</li> </ul> |

| bit 2   |    | <b>CAM:</b> Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                                                                                                                                                                                                        |

|         |    | 1 = Center-Aligned mode is enabled                                                                                                                                                                                                                                                                                                 |

| bit 1   |    | 0 = Edge-Aligned mode is enabled<br><b>XPRES:</b> External PWMx Reset Control bit <sup>(5)</sup>                                                                                                                                                                                                                                   |

| DILI    |    | <ul> <li>1 = Current-limit source resets the time base for this PWMx generator if it is in Independent Time Base<br/>mode</li> </ul>                                                                                                                                                                                               |

| bit 0   |    | <ul> <li>0 = External pins do not affect the PWMx time base</li> <li>IUE: Immediate Update Enable bit<sup>(2)</sup></li> </ul>                                                                                                                                                                                                     |

| DILU    |    | <ul> <li>1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate</li> <li>0 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the PWMx period boundary</li> </ul>                                                                                                          |

| Note    | 1: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.                                                                                                                                                                                                                       |

|         | 2: | These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                                                                                                                                                                                                                             |

|         | 3: | DTC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored.                                                                                                                                                                                                                                                                |

|         | 4: | The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.                                                                                                                                                                                                           |

|         |    |                                                                                                                                                                                                                                                                                                                                    |

**5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

# 19.0 INTER-INTEGRATED CIRCUIT<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70000195), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX family of devices contains two Inter-Integrated Circuit ( $I^2C$ ) modules: I2C1 and I2C2.

The  $I^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface. The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx pin is clock.

- The SDAx pin is data.

The  $I^2C$  module offers the following key features:

- I<sup>2</sup>C Interface Supporting both Master and Slave modes of Operation.

- I<sup>2</sup>C Slave mode Supports 7 and 10-Bit Addressing.

- I<sup>2</sup>C Master mode Supports 7 and 10-Bit Addressing.

- I<sup>2</sup>C Port Allows Bidirectional Transfers Between Master and Slaves.

- Serial Clock Synchronization for I<sup>2</sup>C Port can be used as a Handshake Mechanism to Suspend and Resume Serial Transfer (SCLREL control).

- I<sup>2</sup>C Supports Multi-Master Operation, Detects Bus Collision and Arbitrates Accordingly.

- Intelligent Platform Management Interface (IPMI)

Support

- System Management Bus (SMBus) Support

NOTES:

| REGISTER 20-2: | UxSTA: UARTx STATUS AND CONTROL REGISTER |  |

|----------------|------------------------------------------|--|

|                |                                          |  |

| R/W-0    | R/W-0  | R/W-0    | U-0 | R/W-0, HC | R/W-0                | R-0   | R-1   |

|----------|--------|----------|-----|-----------|----------------------|-------|-------|

| UTXISEL1 | UTXINV | UTXISEL0 | _   | UTXBRK    | UTXEN <sup>(1)</sup> | UTXBF | TRMT  |

| bit 15   |        |          |     |           |                      |       | bit 8 |

| R/W-0    | R/W-0    | R/W-0 | R-1   | R-0  | R-0  | R/C-0 | R-0   |

|----------|----------|-------|-------|------|------|-------|-------|

| URXISEL1 | URXISEL0 | ADDEN | RIDLE | PERR | FERR | OERR  | URXDA |

| bit 7    |          |       |       |      | •    |       | bit 0 |

| Legend: C = Clearable bit |                  | HC = Hardware Clearable bit |                    |  |

|---------------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit          | W = Writable bit | U = Unimplemented bit       | t, read as '0'     |  |

| -n = Value at POR         | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR), and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: UARTx Transmit Polarity Inversion bit

| If IREN = 0:              |    |

|---------------------------|----|

| 1 = UxTX Idle state is '0 | )' |

0 = UxTX Idle state is '1'

- If IREN = 1:

1 = IrDA encoded UxTX Idle state is '1'

0 = IrDA encoded UxTX Idle state is '0'

bit 12

Unimplemented: Read as '0'

bit 11

UTXBRK: UARTx Transmit Break bit

1 = Sends Sync Break on next transmission Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

0 = Sync Break transmission is disabled or has completed

bit 10

UTXEN: UARTx Transmit Enable bit<sup>(1)</sup>

1 = Transmit is enabled, UxTX pin is controlled by UARTx

0 = Transmit is disabled, any pending transmission is aborted and the buffer is reset; UxTX pin is

- controlled by the PORT

- bit 9 UTXBF: UARTx Transmit Buffer Full Status bit (read-only) 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 **TRMT:** Transmit Shift Register Empty bit (read-only)

- 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit Shift Register is not empty, a transmission is in progress or queued

- bit 7-6 URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits

- 11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)

- 10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)

- 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer; receive buffer has one or more characters

- Note 1: Refer to the "dsPIC33/PIC24 Family Reference Manual", "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) for information on enabling the UART module for transmit operation.

# REGISTER 21-26: CxTRmnCON: CANx TX/RX BUFFER mn CONTROL REGISTER (m = 0,2,4,6; n = 1,3,5,7)

| RW-0       R-0       R-0       R-0       R/W-0       R/W-0       R/W-0       R/W-0         TXENN       TXABTN       TXLARBN       TXERN       TXREQN       RTRENN       TXNPRI1         bit 15       Image: stress of the stresst of the stress of the stress of the stress o                                                                                                            |                  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|--|--|

| bit 15          R/W-0       R-0       R-0       R/W-0       R/W-0       R/W-0         TXENm       TXABTm <sup>(1)</sup> TXLARBm <sup>(1)</sup> TXERm <sup>(1)</sup> TXERQm       RTRENm       TXmPRI1         bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is un         bit 15-8       See Definition for bits 7-0, controls Buffer n       bit 1       = Buffer, TRBn, is a transmit buffer         0 = Buffer, TRBn, is a transmit buffer       0 = Buffer, TRBn, is a receive buffer       bit 6       TXABTm: Message Aborted bit <sup>(1)</sup> 1 = Message was aborted       0 = Message completed transmission successfully       bit 5       TXLARBm: Message Lost Arbitration bit <sup>(1)</sup> 1 = Message lost arbitration while being sent       0 = Message lost arbitration while being sent       0 = Message did not lose arbitration while being sent         bit 4       TXERm: Error Detected During Transmission bit <sup>(1)</sup> 1 = A bus error did not occur while the message was being sent       0 = A bus error did not occur while the message was being sent         bit 3       TXREQm: Message Send Request bit       1 = Requests that a message be sent; the bit automatically clears when the message is 0 = Clearing the bit to '0' while set requests a message abort         bit 2<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0            |  |  |  |  |  |

| R/W-0       R-0       R-0       R/W-0       R/W-0       R/W-0       R/W-0         TXENm       TXABTm <sup>(1)</sup> TXLARBm <sup>(1)</sup> TXERm <sup>(1)</sup> TXREQm       RTRENm       TXmPRI1         bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is ur         bit 15-8       See Definition for bits 7-0, controls Buffer n       bit 7       TXENm: TX/RX Buffer Selection bit         1 = Buffer, TRBn, is a transmit buffer       0 = Buffer, TRBn, is a receive buffer       bit 6       TXABTm: Message Aborted bit <sup>(1)</sup> 1 = Message was aborted       0 = Message completed transmission successfully       bit 5       TLLARBm: Message Lost Arbitration bit <sup>(1)</sup> 1 = Message lost arbitration while being sent       0 = Message lost arbitration while being sent       0 = Message lost arbitration while being sent         1 = Message lost arbitration while the message was being sent       0 = A bus error ccurred while the message was being sent         1 = A bus error did not lose arbitration while being sent       0 = A bus error did not occur while the message was being sent         1 = A bus error did not occur while the message was being sent       0 = Clearing the bit to '0' while set requests a message abort                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TXnPRI0          |  |  |  |  |  |

| TXENM       TXABTm <sup>(1)</sup> TXLARBm <sup>(1)</sup> TXERRm <sup>(1)</sup> TXREQm       RTRENM       TXmPRI1         bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unit is unit is the set is                                                                                                                         | bit 8            |  |  |  |  |  |

| bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is un         bit 15-8       See Definition for bits 7-0, controls Buffer n         bit 7       TXENm: TX/RX Buffer Selection bit         1 = Buffer, TRBn, is a transmit buffer       0 = Buffer, TRBn, is a receive buffer         bit 6       TXABTm: Message Aborted bit <sup>(1)</sup> 1 = Message was aborted       0 = Message completed transmission successfully         bit 5       TXLARBm: Message Lost Arbitration bit <sup>(1)</sup> 1 = Message idd not lose arbitration while being sent       0 = Message idd not lose arbitration while being sent         bit 4       TXERRm: Error Detected During Transmission bit <sup>(1)</sup> 1 = A bus error occurred while the message was being sent         0 = A bus error did not occur while the message was being sent         bit 3       TXREQm: Message Send Request bit         1 = Requests that a message be sent; the bit automatically clears when the message is 0 = Clearing the bit to '0' while set requests a message abort         bit 2       RTRENm: Auto-Remote Transmit Enable bit         1 = When a remote transmit is received, TXREQx will be set         0 = When a remote transmit is received, TXREQx will be unaffected         bit 1-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0            |  |  |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is un         bit 15-8       See Definition for bits 7-0, controls Buffer n         bit 7       TXENm: TX/RX Buffer Selection bit         1 = Buffer, TRBn, is a transmit buffer       0 = Buffer, TRBn, is a transmit buffer         0 = Buffer, TRBn, is a receive buffer         bit 6       TXABTm: Message Aborted bit <sup>(1)</sup> 1 = Message was aborted       0 = Message completed transmission successfully         bit 5       TXLARBm: Message Lost Arbitration bit <sup>(1)</sup> 1 = Message did not lose arbitration while being sent         0 = Message did not lose arbitration while being sent         bit 4       TXERRm: Error Detected During Transmission bit <sup>(1)</sup> 1 = A bus error occurred while the message was being sent         0 = A bus error did not occur while the message was being sent         0 = Clearing the bit to '0' while set requests a message abort         bit 3       TXREQm: Message Send Request bit         1 = Requests that a message be sent; the bit automatically clears when the message is 0 = Clearing the bit to '0' while set requests a message abort         bit 2       RTRENm: Auto-Remote Transmit is received, TXREQx will be set         0 = When a remote transmit is recec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I TXmPRI0        |  |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is units of the set is units of t | bit (            |  |  |  |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is un         bit 15-8       See Definition for bits 7-0, controls Buffer n         bit 7       TXENm: TX/RX Buffer Selection bit         1 = Buffer, TRBn, is a transmit buffer       0 = Buffer, TRBn, is a receive buffer         bit 6       TXABTm: Message Aborted bit <sup>(1)</sup> 1 = Message was aborted       0 = Message completed transmission successfully         bit 5       TXLARBm: Message Lost Arbitration bit <sup>(1)</sup> 1 = Message lost arbitration while being sent       0 = Message did not lose arbitration while being sent         bit 4       TXERRm: Error Detected During Transmission bit <sup>(1)</sup> 1 = A bus error occurred while the message was being sent       0 = A bus error did not occur while the message was being sent         bit 3       TXREQm: Message Send Request bit       1 = Requests that a message be sent; the bit automatically clears when the message is 0 = Clearing the bit to '0' while set requests a message abort         bit 2       RTRENm: Auto-Remote Transmit Enable bit       1 = When a remote transmit is received, TXREQx will be set         0 = When a remote transmit is received, TXREQx will be unaffected       bit 1-0       TXmPRI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |  |  |  |  |  |

| bit 15-8 See Definition for bits 7-0, controls Buffer n<br>bit 7 <b>TXENm</b> : TX/RX Buffer Selection bit<br>1 = Buffer, TRBn, is a transmit buffer<br>0 = Buffer, TRBn, is a receive buffer<br>bit 6 <b>TXABTm</b> : Message Aborted bit <sup>(1)</sup><br>1 = Message was aborted<br>0 = Message completed transmission successfully<br>bit 5 <b>TXLARBm</b> : Message Lost Arbitration bit <sup>(1)</sup><br>1 = Message lost arbitration while being sent<br>0 = Message did not lose arbitration while being sent<br>bit 4 <b>TXERRm</b> : Error Detected During Transmission bit <sup>(1)</sup><br>1 = A bus error occurred while the message was being sent<br>0 = A bus error did not occur while the message was being sent<br>bit 3 <b>TXREQm</b> : Message Send Request bit<br>1 = Requests that a message be sent; the bit automatically clears when the message is<br>0 = Clearing the bit to '0' while set requests a message abort<br>bit 2 <b>RTRENm</b> : Auto-Remote Transmit Enable bit<br>1 = When a remote transmit is received, TXREQx will be set<br>0 = When a remote transmit is received, TXREQx will be unaffected<br>bit 1-0 <b>TXmPRI&lt;1:0&gt;</b> : Message Transmission Priority bits<br>11 = Highest message priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |  |  |  |  |  |