Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm310-i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| <b>TABLE 4-17:</b> | I2C1 AND I2C2 REGISTER MAP |

|--------------------|----------------------------|

|--------------------|----------------------------|

| SFR<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                        | Bit 8      | Bit 7                 | Bit 6   | Bit 5       | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|---------|--------|---------|--------|--------|--------|------------------------------|------------|-----------------------|---------|-------------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV     | 0200  | —       | _      | —       | -      | —      | _      | —                            | _          | I2C1 Receive Register |         |             |              |              |       |       | 0000  |               |

| I2C1TRN     | 0202  | _       | _      | _       | _      | —      | _      | —                            | _          |                       |         |             | I2C1 Transr  | nit Register |       |       |       | OOFF          |

| I2C1BRG     | 0204  |         |        |         |        |        |        | В                            | aud Rate C | Generator R           | egister |             |              |              |       |       |       | 0000          |

| I2C1CON     | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                       | SMEN       | GCEN                  | STREN   | ACKDT       | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT    | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                       | ADD10      | IWCOL                 | I2COV   | D_A         | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD     | 020A  | _       | _      | _       | _      | _      | _      |                              |            |                       |         | I2C1 Addre  | ess Register |              |       |       |       | 0000          |

| I2C1MSK     | 020C  | _       | _      | _       | _      | _      | _      |                              |            |                       | 12      | 2C1 Address | Mask Regis   | ster         |       |       |       | 0000          |

| I2C2RCV     | 0210  | _       | _      | _       | _      | _      | _      | _                            | -          |                       |         |             | I2C2 Receiv  | ve Register  |       |       |       | 0000          |

| I2C2TRN     | 0212  | _       | _      | _       | _      | _      | _      | _                            | -          |                       |         |             | I2C2 Transr  | nit Register |       |       |       | OOFF          |

| I2C2BRG     | 0214  |         |        |         |        |        |        | В                            | aud Rate C | Generator R           | egister |             |              |              |       |       |       | 0000          |

| I2C2CON     | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                       | SMEN       | GCEN                  | STREN   | ACKDT       | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT    | 0218  | ACKSTAT | TRSTAT | —       | _      | —      | BCL    | GCSTAT                       | ADD10      | IWCOL                 | I2COV   | D_A         | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD     | 021A  | _       | _      | _       | _      | —      | _      | I2C2 Address Register 0      |            |                       |         |             |              |              | 0000  |       |       |               |

| I2C2MSK     | 021C  |         | _      | —       | —      | —      | _      | I2C2 Address Mask Register 0 |            |                       |         |             |              | 0000         |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-18: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                           | Bit 7         | Bit 6    | Bit 5 | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|----------|--------|----------|--------|--------|--------|-------|---------------------------------|---------------|----------|-------|-------------|--------|--------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0                            | WAKE          | LPBACK   | ABAUD | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1 | UTXINV | UTXISEL0 |        | UTXBRK | UTXEN  | UTXBF | TRMT                            | URXISEL1      | URXISEL0 | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _        |        | —        |        | —      | —      | —     |                                 |               |          | UART1 | Fransmit Re | gister |        |        |       | xxxx          |

| U1RXREG     | 0226  | _        | _      | _        | _      | _      | _      | _     |                                 |               |          | UART1 | Receive Re  | gister |        |        |       | 0000          |

| U1BRG       | 0228  |          |        |          |        |        |        | Ba    | ud Rate C                       | Generator Pre | scaler   |       |             |        |        |        |       | 0000          |

| U2MODE      | 0230  | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0                            | WAKE          | LPBACK   | ABAUD | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                            | URXISEL1      | URXISEL0 | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _        | _      | _        | _      | _      | _      | _     |                                 |               |          | UART2 | Fransmit Re | gister |        |        |       | xxxx          |

| U2RXREG     | 0236  | _        | _      | _        | _      | —      | _      | —     | UART2 Receive Register 0        |               |          |       |             |        | 0000   |        |       |               |

| U2BRG       | 0238  |          |        |          |        |        |        | Ba    | aud Rate Generator Prescaler 00 |               |          |       |             |        | 0000   |        |       |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IADLL       | TABLE 4-32. FERIFIERAL FIN SELECT OUTFUT REGISTER MAP FOR USPIC33EFAAAGMISTU//TU DEVICES |        |        |        |                             |        |         |       |       |       |       |                |       |       |        |       |       |               |

|-------------|------------------------------------------------------------------------------------------|--------|--------|--------|-----------------------------|--------|---------|-------|-------|-------|-------|----------------|-------|-------|--------|-------|-------|---------------|

| SFR<br>Name | Addr.                                                                                    | Bit 15 | Bit 14 | Bit 13 | Bit 12                      | Bit 11 | Bit 10  | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5          | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| RPOR0       | 0680                                                                                     | _      | _      |        | RP35R<5:0>                  |        |         |       |       | —     | _     | RP20R<5:0>     |       |       |        |       |       | 0000          |

| RPOR1       | 0682                                                                                     | _      | _      |        |                             | RP37F  | R<5:0>  |       |       | —     |       |                |       | RP36  | R<5:0> |       |       | 0000          |

| RPOR2       | 0684                                                                                     | _      | _      |        |                             | RP39F  | R<5:0>  |       |       | —     |       |                |       | RP38  | R<5:0> |       |       | 0000          |

| RPOR3       | 0686                                                                                     | _      | _      |        |                             | RP41   | R<5:0>  |       |       | —     |       |                |       | RP40  | R<5:0> |       |       | 0000          |

| RPOR4       | 0688                                                                                     | _      | _      |        |                             | RP43   | R<5:0>  |       |       | —     |       |                |       | RP42  | R<5:0> |       |       | 0000          |

| RPOR5       | 068A                                                                                     | _      | _      |        |                             | RP49   | R<5:0>  |       |       | —     |       | RP48R<5:0>     |       |       |        |       |       | 0000          |

| RPOR6       | 068C                                                                                     | _      | _      |        |                             | RP55F  | R<5:0>  |       |       | —     |       | RP54R<5:0>     |       |       |        |       |       | 0000          |

| RPOR7       | 068E                                                                                     | _      | _      |        |                             | RP57F  | R<5:0>  |       |       | —     |       |                |       | RP56  | R<5:0> |       |       | 0000          |

| RPOR8       | 0690                                                                                     | _      | _      |        |                             | RP70F  | R<5:0>  |       |       | —     |       |                |       | RP69  | R<5:0> |       |       | 0000          |

| RPOR9       | 0692                                                                                     | _      | _      |        |                             | RP97F  | R<5:0>  |       |       | —     |       |                |       | RP81  | R<5:0> |       |       | 0000          |

| RPOR10      | 0694                                                                                     | _      | _      |        | RP118R<5:0> — — RP113R<5:0> |        |         |       |       |       | 0000  |                |       |       |        |       |       |               |

| RPOR11      | 0696                                                                                     | _      | _      |        |                             | RPR12  | 5R<5:0> |       |       | —     |       | - RPR120R<5:0> |       |       |        |       | 0000  |               |

| RPOR12      | 0698                                                                                     | _      | —      |        |                             | RPR12  | ′R<5:0> |       |       | —     |       | RPR126R<5:0>   |       |       |        |       | 0000  |               |

## TABLE 4-32: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGM310/710 DEVICES

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXXGM3XX/6XX/7XX

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Interrupts" (DS70000600), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGM3XX/6XX/7XX CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- · Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- · Fixed priority within a specified user priority level

- · Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The dsPIC33EPXXXGM3XX/6XX/7XX Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory, starting at location, 000004h. The IVT contains seven non-maskable trap vectors and up to 151 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGM3XX/6XX/7XX devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme, based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-increment Addressing mode

- Register Indirect without Post-increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- · CPU interrupt after half or full block transfer complete

- · Byte or word transfers

- Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM Start addresses after each block transfer complete)

- DMA request for each channel can be selected from any supported interrupt source

- · Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA<br>Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|----------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0      | 00000000                             | _                                                       | _                                                      |

| IC1 – Input Capture 1            | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2            | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3            | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4            | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1           | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2           | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3           | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4           | 00011010                             | _                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                    | 00000111                             | —                                                       | —                                                      |

| TMR3 – Timer3                    | 00001000                             | —                                                       | —                                                      |

| TMR4 – Timer4                    | 00011011                             | —                                                       | _                                                      |

| TMR5 – Timer5                    | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done               | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done               | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| SPI3 Transfer Done               | 01011011                             | 0x02A8(SPI3BUF)                                         | 0x02A8(SPI3BUF)                                        |

| UART1RX – UART1 Receiver         | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter      | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver         | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter      | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |

| UART3RX – UART3 Receiver         | 01010010                             | 0X0256(U3RXREG)                                         |                                                        |

| UART3TX – UART3 Transmitter      | 01010011                             | _                                                       | 0X0254(U3TXREG)                                        |

| UART4RX – UART4 Receiver         | 01011000                             | 0X02B6(U4RXREG)                                         |                                                        |

| UART4TX – UART4 Transmitter      | 01011001                             |                                                         | 0X02B4(U4TXREG)                                        |

#### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

### REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

| U-0          | U-0                            | U-0                                                              | U-0                            | U-0                    | U-0              | U-0             | U-0   |

|--------------|--------------------------------|------------------------------------------------------------------|--------------------------------|------------------------|------------------|-----------------|-------|

| _            | _                              | —                                                                | _                              | —                      | _                | _               | _     |

| bit 15       | ·                              |                                                                  |                                |                        |                  |                 | bit 8 |

|              |                                |                                                                  |                                |                        |                  |                 |       |

| U-0          | U-0                            | U-0                                                              | U-0                            | R-1                    | R-1              | R-1             | R-1   |

| —            | —                              | —                                                                | _                              |                        | LSTCH            | <3:0>           |       |

| bit 7        |                                |                                                                  |                                |                        |                  |                 | bit 0 |

|              |                                |                                                                  |                                |                        |                  |                 |       |

| Legend:      |                                |                                                                  |                                |                        |                  |                 |       |

| R = Readab   | ole bit                        | W = Writable                                                     | bit                            | U = Unimpler           | mented bit, read | as '0'          |       |

| -n = Value a | at POR                         | '1' = Bit is set                                                 |                                | '0' = Bit is cle       | ared             | x = Bit is unkr | nown  |

|              |                                |                                                                  |                                |                        |                  |                 |       |

| bit 15-4     | Unimplemen                     | ted: Read as 'o                                                  | o'                             |                        |                  |                 |       |

| bit 3-0      | LSTCH<3:0>                     | : Last DMA Co                                                    | ntroller Chanr                 | nel Active Statu       | is bits          |                 |       |

|              | 1111 = No DI<br>1110 = Rese    | MA transfer has<br>rved                                          | s occurred sin                 | ice system Res         | set              |                 |       |

|              | •                              |                                                                  |                                |                        |                  |                 |       |

|              | •                              |                                                                  |                                |                        |                  |                 |       |

|              | •                              |                                                                  |                                |                        |                  |                 |       |

|              | 0010 = Last o<br>0001 = Last o | rved<br>data transfer wa<br>data transfer wa<br>data transfer wa | as handled by<br>as handled by | Channel 2<br>Channel 1 |                  |                 |       |

0000 = Last data transfer was handled by Channel 0

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Secondary (Timer1) Oscillator (SOSC)                       | Secondary         | xx          | 100        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 00          | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

| Input Name <sup>(1)</sup>    | Function Name | Register | Configuration Bits |

|------------------------------|---------------|----------|--------------------|

| PWM Sync Input 1             | SYNCI1        | RPINR37  | SYNCI1R<6:0>       |

| PWM Dead-Time Compensation 1 | DTCMP1        | RPINR38  | DTCMP1R<6:0>       |

| PWM Dead-Time Compensation 2 | DTCMP2        | RPINR39  | DTCMP2R<6:0>       |

| PWM Dead-Time Compensation 3 | DTCMP3        | RPINR39  | DTCMP3R<6:0>       |

| PWM Dead-Time Compensation 4 | DTCMP4        | RPINR40  | DTCMP4R<6:0>       |

| PWM Dead-Time Compensation 5 | DTCMP5        | RPINR40  | DTCMP5R<6:0>       |

| PWM Dead-Time Compensation 6 | DTCMP6        | RPINR41  | DTCMP6R<6:0>       |

### TABLE 11-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION) (CONTINUED)

**Note 1:** Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

2: This input is available on dsPIC33EPXXXGM6XX/7XX devices only.

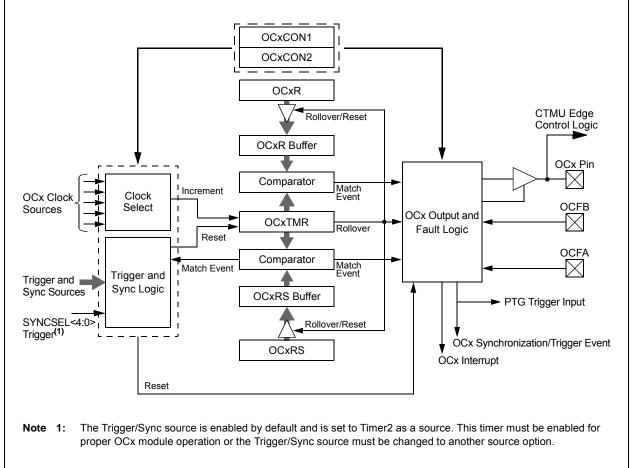

# 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24EFamily Reference Manual", "Output Compare" (DS70005157), which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The output compare module can select one of eight available clock sources for its time base. The module compares the value of the timer with the value of one or two Compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Note: See the *"dsPIC33/PIC24 Family Reference Manual"*, **"Output Compare"** (DS70005157) for OCxR and OCxRS register restrictions.

#### REGISTER 16-5: STCON: PWMx SECONDARY TIME BASE CONTROL REGISTER (CONTINUED)

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

| U-0                   | U-0                            | HS, R/C-0                              | R/W-0           | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

|-----------------------|--------------------------------|----------------------------------------|-----------------|------------------|------------------|-----------------------|----------|

| _                     |                                | PCHEQIRQ                               | PCHEQIEN        | PCLEQIRQ         | PCLEQIEN         | POSOVIRQ              | POSOVIEN |

| bit 15                |                                |                                        |                 |                  |                  |                       | bit 8    |

|                       |                                |                                        |                 |                  |                  |                       |          |

| HS, R/C-0             | R/W-0                          | HS, R/C-0                              | R/W-0           | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

| PCIIRQ <sup>(1)</sup> | PCIIEN                         | VELOVIRQ                               | VELOVIEN        | HOMIRQ           | HOMIEN           | IDXIRQ                | IDXIEN   |

| bit 7                 |                                |                                        |                 |                  |                  |                       | bit 0    |

|                       |                                |                                        |                 |                  |                  |                       |          |

| Legend:               |                                | HS = Hardware                          |                 | C = Clearable    |                  |                       |          |

| R = Readable          |                                | W = Writable b                         | bit             |                  | nented bit, read |                       |          |

| -n = Value at         | POR                            | '1' = Bit is set                       |                 | '0' = Bit is cle | ared             | x = Bit is unki       | nown     |

| bit 15-14             | Unimplome                      | ntad. Dood oo '                        | <b>,</b>        |                  |                  |                       |          |

| bit 13                | -                              | nted: Read as '(                       |                 |                  | nnara Statua hi  |                       |          |

| DIL IO                |                                | Position Counter<br>IT ≥ QEIxGEC       | er Greater i Na |                  | npare Status DI  | ι                     |          |

|                       |                                | IT < QEIXGEC                           |                 |                  |                  |                       |          |

| bit 12                | PCHEQIEN:                      | Position Counter                       | er Greater Tha  | n or Equal Con   | npare Interrupt  | Enable bit            |          |

|                       | 1 = Interrupt                  |                                        |                 |                  |                  |                       |          |

|                       | 0 = Interrupt                  |                                        |                 |                  | o                |                       |          |

| bit 11                |                                | Position Counter<br>$T \leq QEIxLEC$   | er Less Than o  | r Equal Compa    | are Status bit   |                       |          |

|                       |                                | $T \ge QEIXLEC$                        |                 |                  |                  |                       |          |

| bit 10                | PCLEQIEN:                      | Position Counte                        | er Less Than o  | r Equal Compa    | re Interrupt En  | able bit              |          |

|                       | 1 = Interrupt                  |                                        |                 |                  |                  |                       |          |

|                       | 0 = Interrupt                  |                                        |                 |                  |                  |                       |          |

| bit 9                 |                                | Position Counter                       | er Overflow Sta | atus bit         |                  |                       |          |

|                       |                                | has occurred                           | d               |                  |                  |                       |          |

| bit 8                 |                                | Position Counte                        |                 | errupt Enable b  | bit              |                       |          |

|                       | 1 = Interrupt                  |                                        |                 | I                |                  |                       |          |

|                       | 0 = Interrupt                  |                                        |                 |                  |                  | <i></i>               |          |

| bit 7                 |                                | sition Counter (H                      | ÷.              | ation Process    | Complete Statu   | us bit <sup>(1)</sup> |          |

|                       |                                | IT was reinitializ                     |                 |                  |                  |                       |          |

| bit 6                 |                                | IT was not reinit<br>sition Counter (H |                 | ation Process    | Complete inter   | runt Enable bit       |          |

| DILO                  | 1 = Interrupt                  | -                                      | oming) mitianz  | auoniniocess     |                  |                       |          |

|                       | 0 = Interrupt                  |                                        |                 |                  |                  |                       |          |

| bit 5                 | VELOVIRQ:                      | Velocity Counter                       | r Overflow Sta  | tus bit          |                  |                       |          |

|                       |                                | has occurred                           |                 |                  |                  |                       |          |

|                       |                                | low has occurre                        |                 |                  | .,               |                       |          |

| bit 4                 |                                | Velocity Counte                        | r Overflow Inte | errupt Enable b  | It               |                       |          |

|                       | 1 = Interrupt<br>0 = Interrupt |                                        |                 |                  |                  |                       |          |

| bit 3                 | -                              | atus Flag for Ho                       | me Event Stat   | us bit           |                  |                       |          |

|                       |                                | ent has occurre                        |                 |                  |                  |                       |          |

|                       | 0 = No home                    | e event has occu                       | irred           |                  |                  |                       |          |

|                       |                                |                                        |                 |                  |                  |                       |          |

#### REGISTER 17-3: QEIxSTAT: QEIx STATUS REGISTER

**Note 1:** This status bit is only applicable to PIMOD<2:0> = 011 and 100 modes.

| U-0                 | U-0                                      | U-0                                   | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                                  | R/W-0                            |  |  |  |  |  |

|---------------------|------------------------------------------|---------------------------------------|----------------------|----------------------------------------|----------------------|----------------------------------------|----------------------------------|--|--|--|--|--|

| _                   | —                                        | _                                     | DISSCK               | DISSDO                                 | MODE16               | SMP                                    | CKE <sup>(1)</sup>               |  |  |  |  |  |

| bit 15              |                                          | •                                     |                      |                                        |                      |                                        | bit                              |  |  |  |  |  |

|                     |                                          |                                       |                      |                                        |                      |                                        |                                  |  |  |  |  |  |

| R/W-0               | R/W-0                                    | R/W-0                                 | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                                  | R/W-0                            |  |  |  |  |  |

| SSEN <sup>(2)</sup> | CKP                                      | MSTEN                                 | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup>                   | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup>                   | PPRE0 <sup>(3)</sup>             |  |  |  |  |  |

| bit 7               |                                          |                                       |                      |                                        |                      |                                        | bit                              |  |  |  |  |  |

| Legend:             |                                          |                                       |                      |                                        |                      |                                        |                                  |  |  |  |  |  |

| R = Readabl         | e bit                                    | W = Writable                          | bit                  | U = Unimplem                           | nented bit, read     | l as '0'                               |                                  |  |  |  |  |  |

| -n = Value at       | POR                                      | '1' = Bit is set                      |                      | '0' = Bit is clea                      | ared                 | x = Bit is unkr                        | iown                             |  |  |  |  |  |

|                     |                                          |                                       |                      |                                        |                      |                                        |                                  |  |  |  |  |  |

| bit 15-13           | Unimplemer                               | nted: Read as '                       | 0'                   |                                        |                      |                                        |                                  |  |  |  |  |  |

| bit 12              | DISSCK: Dis                              | able SCKx Pin                         | bit (SPI Maste       | er modes only)                         |                      |                                        |                                  |  |  |  |  |  |

|                     |                                          | SPI clock is disa                     |                      | tions as I/O                           |                      |                                        |                                  |  |  |  |  |  |

|                     |                                          | SPI clock is ena                      |                      |                                        |                      |                                        |                                  |  |  |  |  |  |

| bit 11              |                                          | able SDOx Pir                         |                      |                                        |                      |                                        |                                  |  |  |  |  |  |

|                     |                                          | n is not used by<br>n is controlled b |                      | oin functions as                       | I/O                  |                                        |                                  |  |  |  |  |  |

| bit 10              | •                                        | ord/Byte Comm                         | -                    | ect bit                                |                      |                                        |                                  |  |  |  |  |  |

|                     | 1 = Communication is word-wide (16 bits) |                                       |                      |                                        |                      |                                        |                                  |  |  |  |  |  |

|                     | 0 = Commun                               | ication is byte-                      | wide (8 bits)        |                                        |                      |                                        |                                  |  |  |  |  |  |

| bit 9               | SMP: SPIx D                              | ata Input Sam                         | ole Phase bit        |                                        |                      |                                        |                                  |  |  |  |  |  |

|                     | Master mode                              |                                       |                      |                                        |                      |                                        |                                  |  |  |  |  |  |

|                     |                                          | a is sampled at<br>a is sampled at    |                      | ta output time<br>data output tim      | e                    |                                        |                                  |  |  |  |  |  |

|                     | Slave mode:                              | e cleared when                        | SPIx is used i       | n Slave mode                           |                      |                                        |                                  |  |  |  |  |  |

| bit 8               |                                          | lock Edge Sele                        |                      | n olave mode.                          |                      |                                        |                                  |  |  |  |  |  |

|                     | 1 = Serial ou                            | tput data chang                       | jes on transitio     | on from active on from Idle clo        | lock state to Id     | le clock state (r<br>/e clock state (r | efer to bit 6)<br>efer to bit 6) |  |  |  |  |  |

| bit 7               |                                          | Select Enable                         |                      |                                        |                      | · ·                                    | ,                                |  |  |  |  |  |

|                     |                                          | s used for Slav                       |                      | ,                                      |                      |                                        |                                  |  |  |  |  |  |

|                     | $0 = \overline{SSx}$ pin i               | s not used by t                       | ne module; pir       | n is controlled b                      | y port function      |                                        |                                  |  |  |  |  |  |

| bit 6               | CKP: Clock F                             | Polarity Select                       | oit                  |                                        |                      |                                        |                                  |  |  |  |  |  |

|                     |                                          |                                       |                      | ve state is a low<br>e state is a high |                      |                                        |                                  |  |  |  |  |  |

| bit 5               | MSTEN: Mas                               | ster Mode Enat                        | ole bit              |                                        |                      |                                        |                                  |  |  |  |  |  |

|                     | 1 = Master m<br>0 = Slave mo             |                                       |                      |                                        |                      |                                        |                                  |  |  |  |  |  |

|                     |                                          |                                       |                      | D                                      |                      |                                        |                                  |  |  |  |  |  |

| Note 1: Th          | IE CKE DILIS NOL                         | used in Frame                         | a SPI modes. I       | Program this bit                       | to 10° for Frame     | ea SPI moaes (                         | FRMEN = 1                        |  |  |  |  |  |

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

**3:** Do not set both primary and secondary prescalers to the value of 1:1.

| R/W-0         | R/W-0                                                                     | R/W-0            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

|---------------|---------------------------------------------------------------------------|------------------|------------------|------------------|------------------|-----------------|-------|--|--|

| F7BP3         | F7BP2                                                                     | F7BP1            | F7BP0            | F6BP3            | F6BP2            | F6BP1           | F6BP0 |  |  |

| bit 15        |                                                                           |                  |                  |                  |                  |                 | bit 8 |  |  |

|               |                                                                           |                  |                  |                  |                  |                 |       |  |  |

| R/W-0         | R/W-0                                                                     | R/W-0            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

| F5BP3         | F5BP2                                                                     | F5BP1            | F5BP0            | F4BP3            | F4BP2            | F4BP1           | F4BP0 |  |  |

| bit 7         |                                                                           |                  |                  |                  |                  |                 | bit 0 |  |  |

| [             |                                                                           |                  |                  |                  |                  |                 |       |  |  |

| Legend:       |                                                                           |                  |                  |                  |                  |                 |       |  |  |

| R = Readable  | e bit                                                                     | W = Writable     | bit              | U = Unimpler     | mented bit, read | d as '0'        |       |  |  |

| -n = Value at | POR                                                                       | '1' = Bit is set |                  | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |  |  |

|               |                                                                           |                  |                  |                  |                  |                 |       |  |  |

| bit 15-12     |                                                                           | RX Buffer Masl   |                  |                  |                  |                 |       |  |  |

|               |                                                                           | hits received in |                  | -                |                  |                 |       |  |  |

|               | 1110 = Filter                                                             | hits received ir | NRX Buffer 14    | 4                |                  |                 |       |  |  |

|               | •                                                                         |                  |                  |                  |                  |                 |       |  |  |

|               | •                                                                         |                  |                  |                  |                  |                 |       |  |  |

|               | 0001 <b>= Filter</b>                                                      | hits received in | NRX Buffer 1     |                  |                  |                 |       |  |  |

|               | 0000 = Filter                                                             | hits received in | n RX Buffer 0    |                  |                  |                 |       |  |  |

| bit 11-8      | F6BP<3:0>:                                                                | RX Buffer Masl   | k for Filter 6 b | oits (same value | es as bits 15-12 |                 |       |  |  |

| bit 7-4       | 4 F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits 15-12) |                  |                  |                  |                  |                 |       |  |  |

|               |                                                                           |                  |                  |                  |                  |                 |       |  |  |

### REGISTER 21-13: CxBUFPNT2: CANx FILTERS 4-7 BUFFER POINTER REGISTER 2

#### REGISTER 21-14: CxBUFPNT3: CANx FILTERS 8-11 BUFFER POINTER REGISTER 3

F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits 15-12)

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| F11BP3 | F11BP2 | F11BP1 | F11BP0 | F10BP3 | F10BP2 | F10BP1 | F10BP0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-0  |

| F9BP3  | F9BP2  | F9BP1  | F9BP0  | F8BP3  | F8BP2  | F8BP1  | F8BP0  |

| bit 7  |        |        |        |        |        |        | bit 0  |

|        |        |        |        |        |        |        |        |

| Logond |        |        |        |        |        |        |        |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-12 | F11BP<3:0>: RX Buffer Mask for Filter 11 bits<br>1111 = Filter hits received in RX FIFO buffer<br>1110 = Filter hits received in RX Buffer 14<br>• |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 0001 = Filter hits received in RX Buffer 1<br>0000 = Filter hits received in RX Buffer 0                                                           |

| bit 11-8  | F10BP<3:0>: RX Buffer Mask for Filter 10 bits (same values as bits 15-12)                                                                          |

| bit 7-4   | F9BP<3:0>: RX Buffer Mask for Filter 9 bits (same values as bits 15-12)                                                                            |

| bit 3-0   | F8BP<3:0>: RX Buffer Mask for Filter 8 bits (same values as bits 15-12)                                                                            |

© 2013-2014 Microchip Technology Inc.

bit 3-0

#### REGISTER 30-1: DEVID: DEVICE ID REGISTER

| R       | R                                            | R | R      | R                    | R | R | R      |

|---------|----------------------------------------------|---|--------|----------------------|---|---|--------|

|         |                                              |   | DEVID< | 23:16> <b>(1)</b>    |   |   |        |

| bit 23  |                                              |   |        |                      |   |   | bit 16 |

|         |                                              |   |        |                      |   |   |        |

| R       | R                                            | R | R      | R                    | R | R | R      |

|         |                                              |   | DEVID< | :15:8> <b>(1)</b>    |   |   |        |

| bit 15  |                                              |   |        |                      |   |   | bit 8  |

|         |                                              |   |        |                      |   |   |        |

| R       | R                                            | R | R      | R                    | R | R | R      |

|         |                                              |   | DEVID  | <7:0> <sup>(1)</sup> |   |   |        |

| bit 7   |                                              |   |        |                      |   |   | bit 0  |

|         |                                              |   |        |                      |   |   |        |

| Legend: | end: R = Read-Only bit U = Unimplemented bit |   |        |                      |   |   |        |

bit 23-0 **DEVID<23:0>:** Device Identifier bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device ID values.

#### **REGISTER 30-2: DEVREV: DEVICE REVISION REGISTER**

| R       | R                 | R | R      | R                     | R          | R | R      |

|---------|-------------------|---|--------|-----------------------|------------|---|--------|

|         |                   |   | DEVREV |                       |            |   |        |

| bit 23  |                   |   |        |                       |            |   | bit 16 |

|         |                   |   |        |                       |            |   |        |

| R       | R                 | R | R      | R                     | R          | R | R      |

|         |                   |   | DEVREV | <15:8> <sup>(1)</sup> |            |   |        |

| bit 15  |                   |   |        |                       |            |   | bit 8  |

| R       | R                 | R | R      | R                     | R          | R | R      |

|         |                   |   | DEVRE  |                       |            |   |        |

| bit 7   |                   |   |        |                       |            |   | bit 0  |

| Legend: | R = Read-only bit |   |        | U = Unimplen          | nented bit |   |        |

### bit 23-0 **DEVREV<23:0>:** Device Revision bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration *Bits*" (DS70663) for the list of device revision values.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax | Description                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------|-----------------|---------------------------------------------------|---------------|----------------|--------------------------|

| 53                 | NEG                  | NEG    | Acc             | Negate Accumulator                                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG    | f               | $f = \overline{f} + 1$                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG    | f,WREG          | WREG = $\overline{f}$ + 1                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG    | Ws,Wd           | $Wd = \overline{Ws} + 1$                          | 1             | 1              | C,DC,N,OV,Z              |

| 54                 | NOP                  | NOP    |                 | No Operation                                      | 1             | 1              | None                     |

|                    |                      | NOPR   |                 | No Operation                                      | 1             | 1              | None                     |

| 55                 | POP                  | POP    | f               | Pop f from Top-of-Stack (TOS)                     | 1             | 1              | None                     |

|                    |                      | POP    | Wdo             | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1              | None                     |

|                    |                      | POP.D  | Wnd             | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2              | None                     |

|                    |                      | POP.S  |                 | Pop Shadow Registers                              | 1             | 1              | All                      |

| 56                 | PUSH                 | PUSH   | f               | Push f to Top-of-Stack (TOS)                      | 1             | 1              | None                     |

|                    |                      | PUSH   | Wso             | Push Wso to Top-of-Stack (TOS)                    | 1             | 1              | None                     |

|                    |                      | PUSH.D | Wns             | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)     | 1             | 2              | None                     |

|                    |                      | PUSH.S |                 | Push Shadow Registers                             | 1             | 1              | None                     |

| 57                 | PWRSAV               | PWRSAV | #lit1           | Go into Sleep or Idle mode                        | 1             | 1              | WDTO,Sleep               |

| 58                 | RCALL                | RCALL  | Expr            | Relative Call                                     | 1             | 4              | SFA                      |

|                    |                      | RCALL  | Wn              | Computed Call                                     | 1             | 4              | SFA                      |

| 59                 | REPEAT               | REPEAT | #lit15          | Repeat Next Instruction lit15 + 1 times           | 1             | 1              | None                     |

|                    |                      | REPEAT | Wn              | Repeat Next Instruction (Wn) + 1 times            | 1             | 1              | None                     |

| 60                 | RESET                | RESET  |                 | Software device Reset                             | 1             | 1              | None                     |

| 61                 | RETFIE               | RETFIE |                 | Return from interrupt                             | 1             | 6 (5)          | SFA                      |

| 62                 | RETLW                | RETLW  | #lit10,Wn       | Return with literal in Wn                         | 1             | 6 (5)          | SFA                      |

| 63                 | RETURN               | RETURN |                 | Return from Subroutine                            | 1             | 6 (5)          | SFA                      |

| 64                 | RLC                  | RLC    | f               | f = Rotate Left through Carry f                   | 1             | 1              | C,N,Z                    |

|                    |                      | RLC    | f,WREG          | WREG = Rotate Left through Carry f                | 1             | 1              | C,N,Z                    |

|                    |                      | RLC    | Ws,Wd           | Wd = Rotate Left through Carry Ws                 | 1             | 1              | C,N,Z                    |

| 65                 | RLNC                 | RLNC   | f               | f = Rotate Left (No Carry) f                      | 1             | 1              | N,Z                      |

|                    |                      | RLNC   | f,WREG          | WREG = Rotate Left (No Carry) f                   | 1             | 1              | N,Z                      |

|                    |                      | RLNC   | Ws,Wd           | Wd = Rotate Left (No Carry) Ws                    | 1             | 1              | N,Z                      |

| 66                 | RRC                  | RRC    | f               | f = Rotate Right through Carry f                  | 1             | 1              | C,N,Z                    |

|                    |                      | RRC    | f,WREG          | WREG = Rotate Right through Carry f               | 1             | 1              | C,N,Z                    |

|                    |                      | RRC    | Ws,Wd           | Wd = Rotate Right through Carry Ws                | 1             | 1              | C,N,Z                    |

| 67                 | RRNC                 | RRNC   | f               | f = Rotate Right (No Carry) f                     | 1             | 1              | N,Z                      |

|                    |                      | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f                  | 1             | 1              | N,Z                      |

| <u></u>            | a. a                 | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws                   | 1             | 1              | N,Z                      |

| 68                 | SAC                  | SAC    | Acc,#Slit4,Wdo  | Store Accumulator                                 | 1             | 1              | None                     |

| 60                 | 0.5                  | SAC.R  | Acc,#Slit4,Wdo  | Store Rounded Accumulator                         | 1             | 1              | None                     |

| 69<br>70           | SE                   | SE     | Ws,Wnd          | Wnd = sign-extended Ws<br>f = 0xFFFF              | 1             | 1<br>1         | C,N,Z                    |

| 10                 | SETM                 | SETM   | f               |                                                   | 1             | 1              | None                     |

|                    |                      | SETM   | WREG            | WREG = 0xFFFF<br>Ws = 0xFFFF                      | 1             | 1              | None<br>None             |

| 71                 | SFTAC                | SETM   | Ws<br>Acc,Wn    | Arithmetic Shift Accumulator by (Wn)              | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | SFTAC  | Acc,#Slit6      | Arithmetic Shift Accumulator by Slit6             | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

### TABLE 31-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

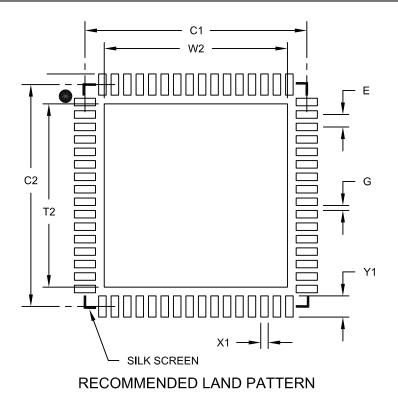

64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS     |      |          |      |  |

|----------------------------|-----------------|------|----------|------|--|

| Dimension Limits           |                 | MIN  | NOM      | MAX  |  |

| Contact Pitch              | Contact Pitch E |      | 0.50 BSC |      |  |

| Optional Center Pad Width  | W2              |      |          | 7.35 |  |

| Optional Center Pad Length | T2              |      |          | 7.35 |  |

| Contact Pad Spacing        | C1              |      | 8.90     |      |  |

| Contact Pad Spacing        | C2              |      | 8.90     |      |  |

| Contact Pad Width (X64)    | X1              |      |          | 0.30 |  |

| Contact Pad Length (X64)   | Y1              |      |          | 0.85 |  |

| Distance Between Pads      | G               | 0.20 |          |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2149A

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Program Memo<br>Product Group<br>Pin Count<br>Tape and Reel I<br>Temperature Ra<br>Package |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Example:<br>dsPIC33EP512GM710-I/PT:<br>dsPIC33, Enhanced Performance,<br>512-Kbyte program memory, 100-pin,<br>Industrial temperature, TQFP package. |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture:                                                                              | 33 = 16-Bit Digital Signal Controller                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                      |

| Family:                                                                                    | EP = Enhanced Performance                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                      |

| Product Group:                                                                             | GM7 = General Purpose plus Motor Control Family                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                      |