Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

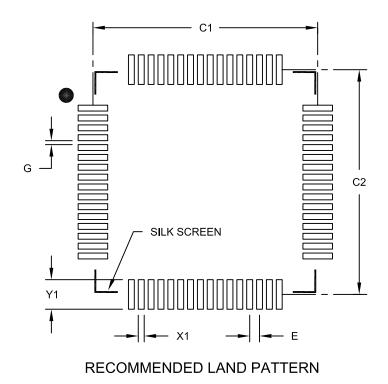

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm604-e-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

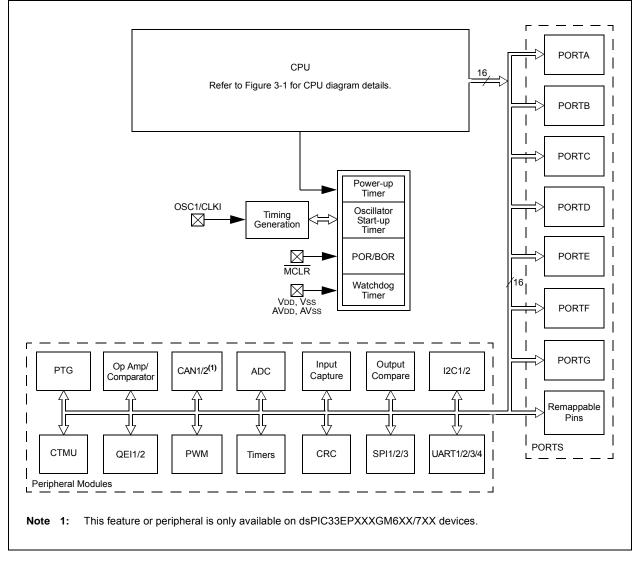

This document contains device-specific information for the dsPIC33EPXXXGM3XX/6XX/7XX Digital Signal Controller (DSC) devices.

dsPIC33EPXXXGM3XX/6XX/7XX devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

#### FIGURE 1-1: dsPIC33EPXXXGM3XX/6XX/7XX BLOCK DIAGRAM

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

## 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

## 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EPXXXGM3XX/ 6XX/7XX devices is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, the dsPIC33EPXXXGM3XX/ 6XX/7XX devices contain control registers for Modulo

Addressing and Bit-Reversed Addressing, and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Table 4-1.

| Register(s) Name                                  | Description                                               |

|---------------------------------------------------|-----------------------------------------------------------|

| W0 through W15                                    | Working Register Array                                    |

| ACCA, ACCB                                        | 40-Bit DSP Accumulators                                   |

| PC                                                | 23-Bit Program Counter                                    |

| SR                                                | ALU and DSP Engine Status register                        |

| SPLIM                                             | Stack Pointer Limit Value register                        |

| TBLPAG                                            | Table Memory Page Address register                        |

| DSRPAG                                            | Extended Data Space (EDS) Read Page register              |

| DSWPAG                                            | Extended Data Space (EDS) Write Page register             |

| RCOUNT                                            | REPEAT Loop Count register                                |

| DCOUNT                                            | DO Loop Count register                                    |

| DOSTARTH <sup>(1)</sup> , DOSTARTL <sup>(1)</sup> | DO Loop Start Address register (High and Low)             |

| DOENDH, DOENDL                                    | DO Loop End Address register (High and Low)               |

| CORCON                                            | Contains DSP Engine, DO Loop Control and Trap Status bits |

#### TABLE 3-1: PROGRAMMER'S MODEL REGISTER DESCRIPTIONS

**Note 1:** The DOSTARTH and DOSTARTL registers are read-only.

| <b>TABLE 4-17:</b> | I2C1 AND I2C2 REGISTER MAP |

|--------------------|----------------------------|

|--------------------|----------------------------|

| SFR<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                                                | Bit 8                      | Bit 7       | Bit 6   | Bit 5       | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|---------|--------|---------|--------|--------|--------|------------------------------------------------------|----------------------------|-------------|---------|-------------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV     | 0200  | —       | _      | —       | -      | —      | _      | —                                                    | _                          |             |         |             | I2C1 Receiv  | ve Register  |       |       |       | 0000          |

| I2C1TRN     | 0202  | _       | _      | _       | _      | —      | _      | —                                                    | _                          |             |         |             | I2C1 Transr  | nit Register |       |       |       | OOFF          |

| I2C1BRG     | 0204  |         |        |         |        |        |        | В                                                    | aud Rate C                 | Generator R | egister |             |              |              |       |       |       | 0000          |

| I2C1CON     | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW SMEN GCEN STREN ACKDT ACKEN RCEN PEN RSEN SEN |                            |             |         |             |              |              |       | 1000  |       |               |

| I2C1STAT    | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT ADD10 IWCOL I2COV D_A P S R_W RBF TBF         |                            |             |         |             |              |              |       | 0000  |       |               |

| I2C1ADD     | 020A  | _       | _      | _       | _      | _      | _      | I2C1 Address Register                                |                            |             |         |             |              |              | 0000  |       |       |               |

| I2C1MSK     | 020C  | _       | _      | _       | _      | _      | _      |                                                      |                            |             | 12      | 2C1 Address | Mask Regis   | ster         |       |       |       | 0000          |

| I2C2RCV     | 0210  | _       | _      | _       | _      | _      | _      | _                                                    | -                          |             |         |             | I2C2 Receiv  | ve Register  |       |       |       | 0000          |

| I2C2TRN     | 0212  | _       | _      | _       | _      | _      | _      | _                                                    | -                          |             |         |             | I2C2 Transr  | nit Register |       |       |       | OOFF          |

| I2C2BRG     | 0214  |         |        |         |        |        |        | В                                                    | aud Rate C                 | Generator R | egister |             |              |              |       |       |       | 0000          |

| I2C2CON     | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                                               | SMEN                       | GCEN        | STREN   | ACKDT       | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT    | 0218  | ACKSTAT | TRSTAT | —       | _      | —      | BCL    | GCSTAT                                               | ADD10                      | IWCOL       | I2COV   | D_A         | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD     | 021A  | _       | _      | _       | _      | —      | _      |                                                      |                            |             |         | I2C2 Addr   | ess Register |              |       |       |       | 0000          |

| I2C2MSK     | 021C  |         | _      | —       | —      | —      | _      |                                                      | I2C2 Address Mask Register |             |         |             |              |              |       | 0000  |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-18: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14                                                                     | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7         | Bit 6    | Bit 5 | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|----------|----------------------------------------------------------------------------|----------|--------|--------|--------|-------|-----------|---------------|----------|-------|-------------|--------|--------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN   | —                                                                          | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0      | WAKE          | LPBACK   | ABAUD | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1 | UTXINV                                                                     | UTXISEL0 |        | UTXBRK | UTXEN  | UTXBF | TRMT      | URXISEL1      | URXISEL0 | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _        |                                                                            | —        |        | —      | —      | —     |           |               |          | UART1 | Fransmit Re | gister |        |        |       | xxxx          |

| U1RXREG     | 0226  | _        | —         —         —         —         UART1 Receive Register         000 |          |        |        |        |       |           |               |          |       | 0000        |        |        |        |       |               |

| U1BRG       | 0228  |          |                                                                            |          |        |        |        | Ba    | ud Rate C | Generator Pre | scaler   |       |             |        |        |        |       | 0000          |

| U2MODE      | 0230  | UARTEN   | _                                                                          | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0      | WAKE          | LPBACK   | ABAUD | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1 | UTXINV                                                                     | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT      | URXISEL1      | URXISEL0 | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _        | _                                                                          | _        | _      | _      | _      | _     |           |               |          | UART2 | Fransmit Re | gister |        |        |       | xxxx          |

| U2RXREG     | 0236  | _        | —                                                                          | _        | _      | —      | _      | —     |           |               |          | UART2 | Receive Re  | gister |        |        |       | 0000          |

| U2BRG       | 0238  |          |                                                                            |          |        |        |        | Ba    | ud Rate C | Generator Pre | scaler   |       |             |        |        |        |       | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-23: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 OR 1 FOR dsPIC33EPXXXGM60X/7XX DEVICES<sup>(1)</sup>

|             |       |          |          |          |          |          |          | - , , -  |          |          |          |          |          |          |            |          |          |               |

|-------------|-------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|------------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2      | Bit 1    | Bit 0    | All<br>Resets |

| C1CTRL1     | 0400  | _        | _        | CSIDL    | ABAT     | CANCKS   | REQOP2   | REQOP1   | REQOP0   | OPMODE2  | OPMODE1  | OPMODE0  | —        | CANCAP   | -          | —        | WIN      | 0480          |

| C1CTRL2     | 0402  | _        |          | _        | _        | _        | _        | _        | _        | _        | _        | _        |          |          | DNCNT<4:0> |          | -        | 0000          |

| C1VEC       | 0404  | _        |          | _        | FILHIT4  | FILHIT3  | FILHIT2  | FILHIT1  | FILHIT0  | _        | ICODE6   | ICODE5   | ICODE4   | ICODE3   | ICODE2     | ICODE1   | ICODE0   | 0040          |

| C1FCTRL     | 0406  | DMABS2   | DMABS1   | DMABS0   | —        |          |          | —        | —        | —        | —        | _        | FSA4     | FSA3     | FSA2       | FSA1     | FSA0     | 0000          |

| C1FIFO      | 0408  | _        |          | FBP5     | FBP4     | FBP3     | FBP2     | FBP1     | FBP0     | —        | —        | FNRB5    | FNRB4    | FNRB3    | FNRB2      | FNRB1    | FNRB0    | 0000          |

| C1INTF      | 040A  | _        |          | TXBO     | TXBP     | RXBP     | TXWAR    | RXWAR    | EWARN    | IVRIF    | WAKIF    | ERRIF    | _        | FIFOIF   | RBOVIF     | RBIF     | TBIF     | 0000          |

| C1INTE      | 040C  | _        |          | —        | —        |          |          | —        | —        | IVRIE    | WAKIE    | ERRIE    | _        | FIFOIE   | RBOVIE     | RBIE     | TBIE     | 0000          |

| C1EC        | 040E  | TERRCNT7 | TERRCNT6 | TERRCNT5 | TERRCNT4 | TERRCNT3 | TERRCNT2 | TERRCNT1 | TERRCNT0 | RERRCNT7 | RERRCNT6 | RERRCNT5 | RERRCNT4 | RERRCNT3 | RERRCNT2   | RERRCNT1 | RERRCNT0 | 0000          |

| C1CFG1      | 0410  | _        |          | —        | —        |          |          | —        | —        | SJW1     | SJW0     | BRP5     | BRP4     | BRP3     | BRP2       | BRP1     | BRP0     | 0000          |

| C1CFG2      | 0412  | _        | WAKFIL   | —        | —        |          | SEG2PH2  | SEG2PH1  | SEG2PH0  | SEG2PHTS | SAM      | SEG1PH2  | SEG1PH1  | SEG1PH0  | PRSEG2     | PRSEG1   | PRSEG0   | 0000          |

| C1FEN1      | 0414  |          |          |          |          |          |          |          | FLTE     | N<15:0>  |          |          |          |          |            |          |          | FFFF          |

| C1FMSKSEL1  | 0418  | F7MSK1   | F7MSK0   | F6MSK1   | F6MSK0   | F5MSK1   | F5MSK0   | F4MSK1   | F4MSK0   | F3MSK1   | F3MSK0   | F2MSK1   | F2MSK0   | F1MSK1   | F1MSK0     | F0MSK1   | F0MSK0   | 0000          |

| C1FMSKSEL2  | 041A  | F15MSK1  | F15MSK0  | F14MSK1  | F14MSK0  | F13MSK1  | F13MSK0  | F12MSK1  | F12MSK0  | F11MSK1  | F11MSK0  | F10MSK1  | F10MSK0  | F9MSK1   | F9MSK0     | F8MSK1   | F8MSK0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers are not present on dsPIC33EPXXXGM3XX devices.

# TABLE 4-24: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 FOR dsPIC33EPXXXGM60X/7XX DEVICES<sup>(1)</sup>

| SFR<br>Name | Addr.         | Bit 15 | Bit 14          | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8        | Bit 7       | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0   | All<br>Resets |

|-------------|---------------|--------|-----------------|---------|--------|--------|--------|---------|--------------|-------------|---------|---------|--------|--------|--------|---------|---------|---------------|

|             | 0400-<br>041E |        |                 |         |        |        |        | Se      | e definition | when WIN :  | ×       |         |        |        |        |         |         |               |

| C1RXFUL1    | 0420          |        |                 |         |        |        |        |         | RXFUL        | <15:0>      |         |         |        |        |        |         |         | 0000          |

| C1RXFUL2    | 0422          |        |                 |         |        |        |        |         | RXFUL        | <31:16>     |         |         |        |        |        |         |         | 0000          |

| C1RXOVF1    | 0428          |        | RXOVF<15:0> 000 |         |        |        |        |         |              |             |         |         | 0000   |        |        |         |         |               |

| C1RXOVF2    | 042A          |        |                 |         |        |        |        |         | RXOVF        | <31:16>     |         |         |        |        |        |         |         | 0000          |

| C1TR01CON   | 0430          | TXEN1  | TXABT1          | TXLARB1 | TXERR1 | TXREQ1 | RTREN1 | TX1PRI1 | TX1PRI0      | TXEN0       | TXABAT0 | TXLARB0 | TXERR0 | TXREQ0 | RTREN0 | TX0PRI1 | TX0PRI0 | 0000          |

| C1TR23CON   | 0432          | TXEN3  | TXABT3          | TXLARB3 | TXERR3 | TXREQ3 | RTREN3 | TX3PRI1 | TX3PRI0      | TXEN2       | TXABAT2 | TXLARB2 | TXERR2 | TXREQ2 | RTREN2 | TX2PRI1 | TX2PRI0 | 0000          |

| C1TR45CON   | 0434          | TXEN5  | TXABT5          | TXLARB5 | TXERR5 | TXREQ5 | RTREN5 | TX5PRI1 | TX5PRI0      | TXEN4       | TXABAT4 | TXLARB4 | TXERR4 | TXREQ4 | RTREN4 | TX4PRI1 | TX4PRI0 | 0000          |

| C1TR67CON   | 0436          | TXEN7  | TXABT7          | TXLARB7 | TXERR7 | TXREQ7 | RTREN7 | TX7PRI1 | TX7PRI0      | TXEN6       | TXABAT6 | TXLARB6 | TXERR6 | TXREQ6 | RTREN6 | TX6PRI1 | TX6PRI0 | xxxx          |

| C1RXD       | 0440          |        |                 |         |        |        |        | C       | AN1 Receiv   | e Data Wo   | rd      |         |        |        |        |         |         | xxxx          |

| C1TXD       | 0442          |        |                 |         |        |        |        | C       | AN1 Transn   | nit Data Wo | rd      |         |        |        |        |         |         | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** These registers are not present on dsPIC33EPXXXGM3XX devices.

#### REGISTER 5-2: NVMADRU: NONVOLATILE MEMORY UPPER ADDRESS REGISTER

| U-0    | U-0   | U-0   | U-0    | U-0      | U-0   | U-0   | U-0   |

|--------|-------|-------|--------|----------|-------|-------|-------|

| —      | —     | —     | _      | —        | —     | —     | —     |

| bit 15 |       |       |        |          |       |       | bit 8 |

|        |       |       |        |          |       |       |       |

| R/W-x  | R/W-x | R/W-x | R/W-x  | R/W-x    | R/W-x | R/W-x | R/W-x |

|        |       |       | NVMADR | U<23:16> |       |       |       |

| bit 7  |       |       |        |          |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADRU<23:16>:** Nonvolatile Memory Upper Write Address bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written to by the user application.

## REGISTER 5-3: NVMADR: NONVOLATILE MEMORY LOWER ADDRESS REGISTER

'1' = Bit is set

| R/W-x          | R/W-x | R/W-x            | R/W-x | R/W-x        | R/W-x            | R/W-x    | R/W-x |

|----------------|-------|------------------|-------|--------------|------------------|----------|-------|

|                |       |                  | NVMAE | )R<15:8>     |                  |          |       |

| bit 15         |       |                  |       |              |                  |          | bit 8 |

|                |       |                  |       |              |                  |          |       |

| R/W-x          | R/W-x | R/W-x            | R/W-x | R/W-x        | R/W-x            | R/W-x    | R/W-x |

|                |       |                  | NVMA  | DR<7:0>      |                  |          |       |

| bit 7          |       |                  |       |              |                  |          | bit 0 |

|                |       |                  |       |              |                  |          |       |

| Legend:        |       |                  |       |              |                  |          |       |

| R = Readable b | it    | W = Writable bit | t     | U = Unimpler | mented bit, read | l as '0' |       |

bit 15-0 **NVMADR<15:0>:** Nonvolatile Memory Lower Write Address bits Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written to by the user application.

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

| R/W-0        | R/W-0                                   | R/W-1                           | R/W-1                | R/W-0                                 | R/W-0              | R/W-0           | R/W-0     |

|--------------|-----------------------------------------|---------------------------------|----------------------|---------------------------------------|--------------------|-----------------|-----------|

| ROI          | DOZE2 <sup>(3)</sup>                    | DOZE1 <sup>(3)</sup>            | DOZE0 <sup>(3)</sup> | DOZEN <sup>(1,4)</sup>                | FRCDIV2            | FRCDIV1         | FRCDIV0   |

| bit 15       |                                         |                                 |                      |                                       |                    |                 | bit 8     |

|              |                                         |                                 |                      |                                       |                    |                 |           |

| R/W-0        | R/W-1                                   | U-0                             | R/W-0                | R/W-0                                 | R/W-0              | R/W-0           | R/W-0     |

| PLLPOST      | 1 PLLPOST0                              |                                 | PLLPRE4              | PLLPRE3                               | PLLPRE2            | PLLPRE1         | PLLPRE0   |

| bit 7        |                                         |                                 |                      |                                       |                    |                 | bit (     |

| <del></del>  |                                         |                                 |                      |                                       |                    |                 |           |

| Legend:      | la hit                                  |                                 | L:4                  | II — Ilucius da un                    | antad bit was      | L == (0'        |           |

| R = Readab   |                                         | W = Writable                    |                      | •                                     | nented bit, read   |                 |           |

| -n = Value a | IL POR                                  | '1' = Bit is set                |                      | '0' = Bit is clea                     | ared               | x = Bit is unkr | IOWI      |

| bit 15       | ROI: Recover                            | on Interrupt b                  | it                   |                                       |                    |                 |           |

|              |                                         | will clear the D                |                      |                                       |                    |                 |           |

|              |                                         | will have no ef                 |                      | OZEN bit                              |                    |                 |           |

| bit 14-12    | DOZE<2:0>:                              | Processor Clo                   | ck Reduction         | Select bits <sup>(3)</sup>            |                    |                 |           |

|              | 111 = Fcy div                           |                                 |                      |                                       |                    |                 |           |

|              | 110 = Fcy div                           | •                               |                      |                                       |                    |                 |           |

|              | 101 = FCY div                           |                                 |                      |                                       |                    |                 |           |

|              | 100 = FCY div<br>011 = FCY div          | /ided by 16<br>/ided by 8 (defa | ault)                |                                       |                    |                 |           |

|              | 010 = FCY div                           |                                 |                      |                                       |                    |                 |           |

|              | 001 = Fcy div                           |                                 |                      |                                       |                    |                 |           |

|              | 000 = FCY div                           | •                               |                      |                                       |                    |                 |           |

| bit 11       |                                         | e Mode Enable                   |                      |                                       |                    |                 |           |

|              |                                         |                                 |                      | etween the perip                      |                    | nd the processo | or clocks |

| hit 10 0     |                                         | •                               | •                    | ratio are forced<br>r Postscaler bits |                    |                 |           |

| bit 10-8     |                                         |                                 | RC Oscillator        | Posiscaler bits                       | 5                  |                 |           |

|              | 111 = FRC di<br>110 = FRC di            |                                 |                      |                                       |                    |                 |           |

|              | 101 <b>= FRC di</b>                     | •                               |                      |                                       |                    |                 |           |

|              | 100 <b>= FRC di</b>                     |                                 |                      |                                       |                    |                 |           |

|              | 011 = FRC di                            |                                 |                      |                                       |                    |                 |           |

|              | 010 = FRC di<br>001 = FRC di            | •                               |                      |                                       |                    |                 |           |

|              |                                         | ivided by 1 (de                 | fault)               |                                       |                    |                 |           |

| bit 7-6      |                                         | •                               |                      | r Select bits (als                    | so denoted as      | N2', PLL posts  | caler)    |

|              | 11 = Output o                           | livided by 8                    | -                    |                                       |                    | -               | ·         |

|              | 10 = Reserve                            |                                 |                      |                                       |                    |                 |           |

|              | 01 = Output c<br>00 = Output c          | livided by 4 (de                | efault)              |                                       |                    |                 |           |

| bit 5        | -                                       | ted: Read as '                  | 0'                   |                                       |                    |                 |           |

|              | -                                       |                                 |                      | n interment a                         |                    |                 |           |

|              | This bit is cleared                     |                                 |                      |                                       | uis.               |                 |           |

|              | This register resets<br>The DOZE<2:0> b | -                               |                      |                                       | hit is clear. If D |                 | writes to |

|              | OZE<2:0> b<br>OZE<2:0> are ig           | -                               |                      |                                       | on is oreal. If D  | ∪∠∟iv – ⊥, ally |           |

|              |                                         |                                 |                      |                                       |                    |                 | -         |

## REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup>

4: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| U-0       U-0       R/W-0       R/W-0       U-0       U-0       U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |                                                                |                                                                         |                                            |                   |      |                 |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------|-------------------|------|-----------------|-------|

| U-0       U-0       U-0       R/W-0       R/W-0       U-0       U-0       U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0          | U-0                                                            | U-0                                                                     | U-0                                        | U-0               | U-0  | U-0             | U-0   |

| U-0       U-0       R/W-0       R/W-0       U-0       U-0       U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | —            | —                                                              | —                                                                       | _                                          | —                 |      | _               | —     |

| Image: Section of the section of th | bit 15       |                                                                |                                                                         |                                            |                   |      |                 | bit 8 |

| Image: Construction of the construc | 11-0         | 11-0                                                           | 11-0                                                                    |                                            | P/M/ 0            | 11-0 | 11-0            | 11-0  |

| -       -       DMA1MD <sup>(1)</sup><br>DMA2MD <sup>(1)</sup><br>DMA3MD <sup>(1)</sup> PTGMD       -       -       -         egend:<br>R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       Unimplemented: Read as '0'       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       Unimplemented: Read as '0'       '0' = Bit is cleared       x = Bit is unknown         bit 4       DMA0MD: DMA0 Module Disable bit <sup>(1)</sup> 1       = DMA0 module is disabled         0 = DMA0 module is disabled       0       = DMA1 module is disabled       0         0 = DMA1 module is disabled       0       = DMA1 module is disabled       0         0 = DMA2 module is disabled       0       = DMA2 module is disabled       0         0 = DMA2 module is disabled       0       = DMA3 module is disabled       0         0 = DMA3 module is disabled       0       = DMA3 module is disabled       0         0 = DMA3 module is disabled       0       = DMA3 module is disabled       0         0 = DMA3 module is disabled       0       = DMA3 module is disabled       0         0 = DMA3 module is disabled       0       = PTG module is enabled       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0-0          | 0-0                                                            | 0-0                                                                     |                                            | 10,00-0           | 0-0  | 0-0             | 0-0   |

| Image: Constraint of the second se |              |                                                                |                                                                         |                                            |                   |      |                 |       |

| DMA3MD <sup>(1)</sup> bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         on = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       Unimplemented: Read as '0'       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       Unimplemented: Read as '0'       '0' = Bit is cleared       x = Bit is unknown         bit 14       DMA0MD: DMA0 Module Disable bit <sup>(1)</sup> 1 = DMA0 module is disabled       0 = DMA0 module is disabled         0 = DMA0 module is disabled       0 = DMA1 module is disabled       0 = DMA1 module is disabled       0 = DMA1 module is disabled         0 = DMA1 module is disabled       0 = DMA2 module is disabled       0 = DMA2 module is disabled       0 = DMA2 module is disabled         0 = DMA2 module is disabled       0 = DMA3 module is disabled       0 = DMA3 module is disabled       0 = DMA3 module is disabled         0 = DMA3 module is disabled       0 = DMA3 module is disabled       0 = DMA3 module is disabled       0 = DMA3 module is disabled         0 = DMA3 module is disabled       0 = PTG module is disabled       0 = PTG module is disabled       0 = PTG module is enabled         bit 3       PTGMD: PTG Module Disable bit       1 = PTG module is enabled       0 = PTG module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | —            | -                                                              | —                                                                       |                                            | PTGMD             | —    | —               | —     |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         in = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       Unimplemented: Read as '0'           bit 15-5       Unimplemented: Read as '0'          bit 15-5       Unimplemented: Read as '0'          bit 14       DMA0MD: DMA0 Module Disable bit <sup>(1)</sup> 1 = DMA0 module is disabled       0 = DMA0 module is disabled          0 = DMA1 module is disabled       0 = DMA1 module is disabled          0 = DMA1 module is disabled       0 = DMA2 module is disabled          0 = DMA2 module is disabled       0 = DMA2 module is disabled          0 = DMA2 module is disabled       0 = DMA3 module is disabled          0 = DMA3 module is disabled       0 = DMA3 module is disabled          0 = DMA3 module is disabled       0 = DMA3 module is disabled          0 = DMA3 module is disabled       0 = DMA3 module is disabled          0 = DMA3 module is disabled       0 = PTG module is disabled          0 = DTG module is disabled       0 = PTG module is enabled          bit 2-0       Unimplemented: Read as '0' <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |                                                                |                                                                         |                                            |                   |      |                 |       |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         .n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       Unimplemented: Read as '0'        bit 4       DMA0MD: DMA0 Module Disable bit <sup>(1)</sup> 1 = DMA0 module is disabled       0 = DMA0 module is disabled            0 = DMA1 module is disabled       0 = DMA1 module is disabled            0 = DMA1 module is disabled       0 = DMA1 module is disabled            0 = DMA2 module is disabled       0 = DMA2 module is disabled            0 = DMA2 module is disabled       0 = DMA2 module is disabled            0 = DMA2 module is disabled       0 = DMA3 module is disabled            0 = DMA3 module is disabled       0 = DMA3 module is disabled             0 = DMA3 module is disabled       0 = DMA3 module is enabled             0 = DMA3 module is disabled       0 = DMA3 module is enabled              bit 3       TGMD: PTG module is disabled </td <td>oit 7</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>bit C</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | oit 7        |                                                                |                                                                         |                                            |                   |      |                 | bit C |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'        n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       Unimplemented: Read as '0'        bit 4       DMA0MD: DMA0 Module Disable bit <sup>(1)</sup> 1 = DMA0 module is disabled       0 = DMA0 module is disabled           0 = DMA1 module is disabled       0 = DMA1 module is disabled          0 = DMA1 module is disabled       0 = DMA2 module is enabled          DMA2MD: DMA2 Module Disable bit <sup>(1)</sup> 1 = DMA2 module is disabled          0 = DMA2 module is disabled       0 = DMA2 module is disabled          0 = DMA2 module is disabled       0 = DMA2 module is disabled          0 = DMA3 module is disabled       0 = DMA3 module is disabled          0 = DMA3 module is disabled       0 = DMA3 module is disabled          0 = DMA3 module is disabled       0 = DMA3 module is disabled          0 = DMA3 module is disabled       0 = PTG module is disabled          0 = PTG module is disabled       0 = PTG module is enabled          bit 2-0       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                                                                |                                                                         |                                            |                   |      |                 |       |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       Unimplemented: Read as '0'       DMA0MD: DMA0 Module Disable bit <sup>(1)</sup> 1         1 = DMA0 module is disabled       0 = DMA0 module is disabled       0         0 = DMA1 module is disabled       0 = DMA1 module is disabled       0         0 = DMA1 module is disabled       0 = DMA1 module is disabled       0         0 = DMA1 module is disabled       0 = DMA2 module is disabled       0         0 = DMA2 module is disabled       0 = DMA2 module is disabled       0         0 = DMA2 module is disabled       0 = DMA2 module is disabled       0         0 = DMA2 module is disabled       0 = DMA3 module is disabled       0         0 = DMA3 module is disabled       0 = DMA3 module is disabled       0         0 = DMA3 module is disabled       0 = DMA3 module is disabled       0 = DMA3 module is disabled         0 = DMA3 module is enabled       0 = DMA3 module is disabled       0 = DTG module is disabled         0 = PTG module is disabled       0 = PTG module is disabled       0 = PTG module is enabled         bit 2-0       Unimplemented: Read as '0'       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -            |                                                                |                                                                         |                                            |                   |      |                 |       |

| bit 15-5 Unimplemented: Read as '0'<br>bit 4 DMA0MD: DMA0 Module Disable bit <sup>(1)</sup><br>1 = DMA0 module is disabled<br>0 = DMA0 module is enabled<br>DMA1MD: DMA1 Module Disable bit <sup>(1)</sup><br>1 = DMA1 module is disabled<br>0 = DMA1 module is enabled<br>DMA2MD: DMA2 Module Disable bit <sup>(1)</sup><br>1 = DMA2 module is disabled<br>0 = DMA2 module is disabled<br>0 = DMA3 module is enabled<br>DMA3MD: DMA3 Module Disable bit <sup>(1)</sup><br>1 = DMA3 module is disabled<br>0 = DMA3 module is disabled<br>0 = DMA3 module is disabled<br>0 = DMA3 module is enabled<br>bit 3 PTGMD: PTG Module Disable bit<br>1 = PTG module is disabled<br>0 = PTG module is enabled<br>bit 2-0 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                                                                |                                                                         |                                            | •                 |      |                 |       |

| bit 4 DMA0MD: DMA0 Module Disable bit <sup>(1)</sup> 1 = DMA0 module is disabled 0 = DMA0 module is enabled DMA1MD: DMA1 Module Disable bit <sup>(1)</sup> 1 = DMA1 module is disabled 0 = DMA1 module is disabled 0 = DMA1 module is enabled DMA2MD: DMA2 Module Disable bit <sup>(1)</sup> 1 = DMA2 module is disabled 0 = DMA2 module is disabled 0 = DMA2 module is disabled 0 = DMA3 module is enabled DMA3MD: DMA3 Module Disable bit <sup>(1)</sup> 1 = DMA3 module is disabled 0 = PTG module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -n = Value a | at POR                                                         | '1' = Bit is set                                                        |                                            | '0' = Bit is clea | ared | x = Bit is unkn | iown  |

| DMA2MD: DMA2 Module Disable bit <sup>(1)</sup> 1 = DMA2 module is disabled         0 = DMA2 module is enabled         DMA3MD: DMA3 Module Disable bit <sup>(1)</sup> 1 = DMA3 module is disabled         0 = DMA3 module is enabled         bit 3       PTGMD: PTG Module Disable bit         1 = PTG module is disabled         0 = PTG module is enabled         bit 2-0       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 4        | 1 = DMA0 mc<br>0 = DMA0 mc<br><b>DMA1MD:</b> DM<br>1 = DMA1 mc | odule is disable<br>odule is enable<br>MA1 Module D<br>odule is disable | ed<br>d<br>isable bit <sup>(1)</sup><br>ed |                   |      |                 |       |

| <ul> <li>1 = DMA2 module is disabled</li> <li>0 = DMA2 module is enabled</li> <li>DMA3MD: DMA3 Module Disable bit<sup>(1)</sup></li> <li>1 = DMA3 module is disabled</li> <li>0 = DMA3 module is enabled</li> <li>0 = DMA3 module Disable bit</li> <li>1 = PTG Module Disable bit</li> <li>1 = PTG module is disabled</li> <li>0 = PTG module is enabled</li> <li>0 = PTG module is enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                                                                |                                                                         |                                            |                   |      |                 |       |

| 1 = DMA3 module is disabled         0 = DMA3 module is enabled         bit 3       PTGMD: PTG Module Disable bit         1 = PTG module is disabled         0 = PTG module is enabled         bit 2-0       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | 1 = DMA2 mc                                                    | odule is disable                                                        | d                                          |                   |      |                 |       |

| bit 3       PTGMD: PTG Module Disable bit         1 = PTG module is disabled         0 = PTG module is enabled         bit 2-0       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | 1 = DMA3 mc                                                    | odule is disable                                                        | d                                          |                   |      |                 |       |

| 1 = PTG module is disabled         0 = PTG module is enabled         bit 2-0       Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |                                                                |                                                                         |                                            |                   |      |                 |       |

| bit 2-0 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DIT 3        | 1 = PTG mod                                                    | ule is disabled                                                         | die dit                                    |                   |      |                 |       |