Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, Motor Control PWM, POR, PWM, WDT               |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

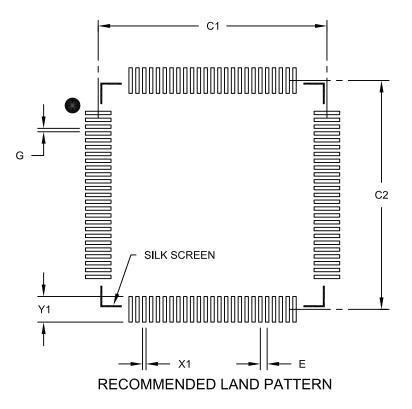

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm604-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IABLE 4     | 4-0:  | 00                                    | IPUIC                                                                                                   |          |         | SIER W  | AP      |       |            |             |               |        |          |          |          |          |          |               |

|-------------|-------|---------------------------------------|---------------------------------------------------------------------------------------------------------|----------|---------|---------|---------|-------|------------|-------------|---------------|--------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15                                | Bit 14                                                                                                  | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8      | Bit 7       | Bit 6         | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| OC1CON1     | 0900  | _                                     | —                                                                                                       | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | ENFLTB     | ENFLTA      | —             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2     | 0902  | FLTMD                                 | FLTOUT                                                                                                  | FLTTRIEN | OCINV   | —       | _       | _     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS       | 0904  |                                       | Output Compare 1 Secondary Register                                                                     |          |         |         |         |       |            |             |               |        |          |          |          | xxxx     |          |               |

| OC1R        | 0906  |                                       | Output Compare 1 Register                                                                               |          |         |         |         |       |            |             |               |        |          |          | xxxx     |          |          |               |

| OC1TMR      | 0908  |                                       | Output Compare 1 Timer Value Register x                                                                 |          |         |         |         |       |            |             |               |        |          | xxxx     |          |          |          |               |

| OC2CON1     | 090A  | _                                     | —                                                                                                       | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | ENFLTB     | ENFLTA      | -             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC2CON2     | 090C  | FLTMD                                 | FLTOUT                                                                                                  | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS       | 090E  |                                       |                                                                                                         |          |         |         |         | Ou    | Itput Comp | oare 2 Seco | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC2R        | 0910  |                                       |                                                                                                         |          |         |         |         |       | Output     | Compare 2   | 2 Register    |        |          |          |          |          |          | xxxx          |

| OC2TMR      | 0912  |                                       |                                                                                                         |          |         |         | -       | Ou    | tput Comp  | are 2 Time  | r Value Regis | ster   |          | -        |          |          |          | xxxx          |

| OC3CON1     | 0914  | —                                     | _                                                                                                       | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2     | 0916  | FLTMD                                 | FLTOUT                                                                                                  | FLTTRIEN | OCINV   | _       | —       | _     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS       | 0918  |                                       |                                                                                                         |          |         |         |         | Ou    | tput Comp  | are 3 Seco  | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC3R        | 091A  |                                       |                                                                                                         |          |         |         |         |       | Output     | Compare 3   | 3 Register    |        |          |          |          |          |          | xxxx          |

| OC3TMR      | 091C  |                                       |                                                                                                         |          |         |         | -       | Ou    | tput Comp  | are 3 Time  | r Value Regis | ster   |          | -        |          |          |          | xxxx          |

| OC4CON1     | 091E  | —                                     | _                                                                                                       | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC4CON2     | 0920  | FLTMD                                 | FLTOUT                                                                                                  | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC4RS       | 0922  |                                       |                                                                                                         |          |         |         |         | Ou    | tput Comp  | oare 4 Seco | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC4R        | 0924  |                                       |                                                                                                         |          |         |         |         |       | Output     | Compare 4   | 4 Register    |        |          |          |          |          |          | xxxx          |

| OC4TMR      | 0926  |                                       |                                                                                                         |          |         |         |         | Ou    | tput Comp  | are 4 Time  | r Value Regis | ster   |          |          |          |          |          | xxxx          |

| OC5CON1     | 0928  |                                       | _                                                                                                       | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC5CON2     | 092A  | FLTMD                                 | FLTOUT                                                                                                  | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC5RS       | 092C  |                                       |                                                                                                         |          |         |         |         | Ou    | tput Comp  | are 5 Seco  | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC5R        | 092E  |                                       |                                                                                                         |          |         |         |         |       | Output     | Compare &   | 5 Register    |        |          |          |          |          |          | xxxx          |

| OC5TMR      | 0930  |                                       |                                                                                                         |          |         |         |         | Ou    | tput Comp  | are 5 Time  | r Value Regis | ster   |          |          |          |          |          | xxxx          |

| OC6CON1     | 0932  | —                                     | —                                                                                                       | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC6CON2     | 0934  | FLTMD                                 | FLTMD FLTOUT FLTTRIEN OCINV OC32 OCTRIG TRIGSTAT OCTRIS SYNCSEL4 SYNCSEL3 SYNCSEL2 SYNCSEL1 SYNCSEL0 00 |          |         |         |         |       |            |             |               |        | 000C     |          |          |          |          |               |

| OC6RS       | 0936  | Output Compare 6 Secondary Register x |                                                                                                         |          |         |         |         |       |            |             |               |        | xxxx     |          |          |          |          |               |

| OC6R        | 0938  |                                       | Output Compare 6 Register xx                                                                            |          |         |         |         |       |            |             |               |        |          | xxxx     |          |          |          |               |

| OC6TMR      | 093A  |                                       |                                                                                                         |          |         |         |         | Out   | tput Comp  | are 6 Time  | r Value Regis | ster   |          |          |          |          |          | xxxx          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-35: NVM REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7   | Bit 6 | Bit 5 | Bit 4   | Bit 3     | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|--------|--------|--------|---------|--------|--------|-------|---------|---------|-------|-------|---------|-----------|--------|--------|--------|---------------|

| NVMCON      | 0728  | WR     | WREN   | WRERR  | NVMSIDL |        | —      | RPDF  | URERR   | -       | -     |       | _       | NVMOP3    | NVMOP2 | NVMOP1 | NVMOP0 | 0000          |

| NVMADR      | 072A  |        |        |        |         |        |        |       | NVMAD   | R<15:0> |       |       |         |           |        |        |        | 0000          |

| NVMADRU     | 072C  | _      | _      | _      | _       | _      | _      | _     | _       |         |       |       | NVMAD   | RU<23:16> |        |        |        | 0000          |

| NVMKEY      | 072E  | _      | _      | _      | _       | _      | _      | _     | _       |         |       |       | NVM     | (EY<7:0>  |        |        |        | 0000          |

| NVMSRCADRL  | 0730  |        |        |        |         |        |        | NVMS  | SRCADR< | 15:1>   |       |       |         |           |        |        | 0      | 0000          |

| NVMSRCADRH  | 0732  |        |        |        |         |        |        |       |         |         |       |       | NVMSRCA | ADRH<23:1 | 6>     |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-36: SYSTEM CONTROL REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7    | Bit 6    | Bit 5  | Bit 4     | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|---------|---------|---------|----------|----------|--------|-----------|---------|---------|---------|---------|---------------|

| RCON        | 0740  | TRAPR  | IOPUWR |        | —      | VREGSF |         | СМ      | VREGS   | EXTR     | SWR      | SWDTEN | WDTO      | SLEEP   | IDLE    | BOR     | POR     | Note 1        |

| OSCCON      | 0742  | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2   | NOSC1   | NOSC0   | CLKLOCK  | IOLOCK   | LOCK   | _         | CF      | _       | LPOSCEN | OSWEN   | Note 2        |

| CLKDIV      | 0744  | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | FRCDIV2 | FRCDIV1 | FRCDIV0 | PLLPOST1 | PLLPOST0 | _      | PLLPRE4   | PLLPRE3 | PLLPRE2 | PLLPRE1 | PLLPRE0 | 0030          |

| PLLFBD      | 0746  | _      | _      | _      | —      |        |         | —       |         |          |          | PL     | LDIV<8:0> |         |         |         |         | 0030          |

| OSCTUN      | 0748  | _      | _      |        | _      |        |         | _       |         |          |          |        |           | TUN     | <5:0>   |         |         | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the configuration fuses.

## TABLE 4-37: REFERENCE CLOCK REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON     | 074E  | ROON   |        | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _     |       |       |       |       |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.5.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed, but the contents of the register remain unchanged.

## 4.6 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms; it is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.6.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all of these conditions are met:

- BWM bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume       |

|-------|-----------------------------------------------|

|       | word-sized data (LSb of every EA is always    |

|       | clear). The XB value is scaled accordingly to |

|       | generate compatible (byte) addresses.         |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo                                      | Addressing     | and     | Bit-Rev   | ersed |  |  |  |  |  |  |  |

|-------|---------------------------------------------|----------------|---------|-----------|-------|--|--|--|--|--|--|--|

|       | Addressi                                    | ing can be er  | abled s | simultane | ously |  |  |  |  |  |  |  |

|       | using the same W register, but Bit-Reversed |                |         |           |       |  |  |  |  |  |  |  |

|       | Addressi                                    | ing operatio   | n will  | always    | take  |  |  |  |  |  |  |  |

|       | preceder                                    | nce for data w | rites w | hen enab  | led.  |  |  |  |  |  |  |  |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

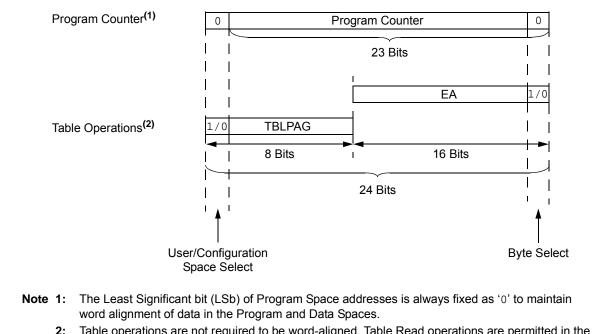

## 4.7 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXXGM3XX/6XX/7XX architecture uses a 24-bit-wide Program Space and a 16-bit-wide Data Space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGM3XX/6XX/7XX devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

#### TABLE 4-68: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access        | Program Space Address        |           |          |               |     |  |  |  |  |  |

|------------------------|---------------|------------------------------|-----------|----------|---------------|-----|--|--|--|--|--|

| Access Type            | Space         | <23>                         | <22:16>   | <15>     | <14:1>        | <0> |  |  |  |  |  |

| Instruction Access     | User          | 0                            |           | PC<22:1> |               | 0   |  |  |  |  |  |

| (Code Execution)       |               | 0xx xxxx xxxx xxxx xxxx xxx0 |           |          |               |     |  |  |  |  |  |

| TBLRD/TBLWT            | User          | TB                           | LPAG<7:0> |          | Data EA<15:0> |     |  |  |  |  |  |

| (Byte/Word Read/Write) |               | 0                            | xxx xxxx  | xxxx xxx | x xxxx xxxx   |     |  |  |  |  |  |

|                        | Configuration | TB                           | LPAG<7:0> |          | Data EA<15:0> |     |  |  |  |  |  |

|                        |               | 1                            | xxx xxxx  | xxxx xx  | xx xxxx xxxx  |     |  |  |  |  |  |

#### FIGURE 4-16: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

**2:** Table operations are not required to be word-aligned. Table Read operations are permitted in the configuration memory space.

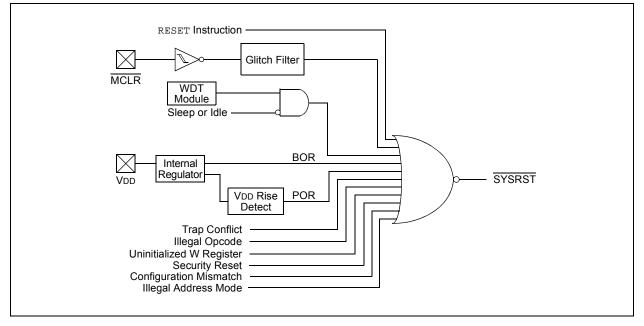

## 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Reset" (DS70602), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Illegal Address Mode Reset

- Uninitialized W Register Reset

- Security Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>) that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

Note: In all types of Resets, to select the device clock source, the contents of OSCCON are initialized from the FNOSCx Configuration bits in the FOSCSEL Configuration register.

#### FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

## dsPIC33EPXXXGM3XX/6XX/7XX

FIGURE 7-1: dsPIC33EPXXXGM3XX/6XX/7XX INTERRUPT VECTOR TABLE

| <b>▲</b>                          | Reset – GOTO Instruction         | 0x000000 |                          |

|-----------------------------------|----------------------------------|----------|--------------------------|

|                                   | Reset – GOTO Address             | 0x000002 |                          |

| £                                 | Oscillator Fail Trap Vector      | 0x000004 |                          |

| rior                              | Address Error Trap Vector        | 0x000006 |                          |

| ር<br>አ                            | Generic Hard Trap Vector         | 0x000008 |                          |

| Orde                              | Stack Error Trap Vector          | 0x00000A |                          |

| ផ្ទ                               | Math Error Trap Vector           | 0x00000C |                          |

| atur                              | DMA Controller Error Trap Vector | 0x00000E |                          |

| ž b                               | Generic Soft Trap Vector         | 0x000010 |                          |

| Decreasing Natural Order Priority | Reserved                         | 0x000012 |                          |

| crea                              | Interrupt Vector 0               | 0x000014 |                          |

| Dec                               | Interrupt Vector 1               | 0x000016 |                          |

|                                   | :                                | :        |                          |

| ,                                 | :                                | :        |                          |

| ĭ                                 | :                                | :        |                          |

| 2                                 | Interrupt Vector 52              | 0x00007C |                          |

|                                   | Interrupt Vector 53              | 0x00007E |                          |

|                                   | Interrupt Vector 54              | 0x000080 | $\backslash$             |

|                                   | :                                | :        | See Table 7-1 for        |

|                                   | :                                | :        | Interrupt Vector Details |

|                                   | :                                | :        |                          |

|                                   | Interrupt Vector 116             | 0x0000FC |                          |

|                                   | Interrupt Vector 117             | 0x0000FE |                          |

|                                   | Interrupt Vector 118             | 0x000100 |                          |

|                                   | Interrupt Vector 119             | 0x000102 |                          |

|                                   | Interrupt Vector 120             | 0x000104 |                          |

|                                   | :                                | :        |                          |

|                                   | :                                | :        |                          |

|                                   | :                                | :        |                          |

| V                                 | Interrupt Vector 244             | 0x0001FC |                          |

|                                   | Interrupt Vector 245             | 0x0001FE | /                        |

|                                   | START OF CODE                    | 0x000200 |                          |

| U-0              | U-0 | U-0              | U-0 | U-0              | U-0              | U-0             | U-0    |

|------------------|-----|------------------|-----|------------------|------------------|-----------------|--------|

| —                | —   | —                |     | —                |                  | —               | —      |

| bit 15           |     |                  |     |                  |                  |                 | bit 8  |

|                  |     |                  |     |                  |                  |                 |        |

| U-0              | U-0 | U-0              | U-0 | R-0              | R-0              | R-0             | R-0    |

| —                |     | —                | _   | PWCOL3           | PWCOL2           | PWCOL1          | PWCOL0 |

| bit 7            |     |                  |     |                  |                  |                 | bit (  |

|                  |     |                  |     |                  |                  |                 |        |

| Legend:          |     |                  |     |                  |                  |                 |        |

| R = Readable b   | bit | W = Writable I   | bit | U = Unimplen     | nented bit, read | as '0'          |        |

| -n = Value at PO | OR  | '1' = Bit is set |     | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

## REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

| bit 15-4 | Unimplemented: Read as '0'                                                                   |

|----------|----------------------------------------------------------------------------------------------|

| bit 3    | PWCOL3: Channel 3 Peripheral Write Collision Flag bit                                        |

|          | <ul><li>1 = Write collision is detected</li><li>0 = No write collision is detected</li></ul> |

| bit 2    | PWCOL2: Channel 2 Peripheral Write Collision Flag bit                                        |

|          | 1 = Write collision is detected                                                              |

|          | 0 = No write collision is detected                                                           |

| bit 1    | <b>PWCOL1:</b> Channel 1 Peripheral Write Collision Flag bit                                 |

|          | 1 = Write collision is detected                                                              |

|          | 0 = No write collision is detected                                                           |

| bit 0    | PWCOL0: Channel 0 Peripheral Write Collision Flag bit                                        |

|          | 1 = Write collision is detected                                                              |

|          | 0 = No write collision is detected                                                           |

## 12.1 Timer1 Control Register

## REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0              | U-0                               | R/W-0                              | U-0                       | U-0              | U-0                       | U-0                | U-0         |

|--------------------|-----------------------------------|------------------------------------|---------------------------|------------------|---------------------------|--------------------|-------------|

| TON <sup>(1)</sup> | —                                 | TSIDL                              | _                         | —                | —                         | —                  | —           |

| bit 15             |                                   |                                    |                           |                  |                           |                    | bit 8       |

|                    |                                   |                                    |                           |                  |                           |                    |             |

| U-0                | R/W-0                             | R/W-0                              | R/W-0                     | U-0              | R/W-0                     | R/W-0              | U-0         |

| _                  | TGATE                             | TCKPS1                             | TCKPS1                    |                  | TSYNC <sup>(1)</sup>      | TCS <sup>(1)</sup> | —           |

| bit 7              |                                   |                                    |                           |                  |                           |                    | bit 0       |

| r                  |                                   |                                    |                           |                  |                           |                    |             |

| Legend:            |                                   |                                    |                           |                  |                           |                    |             |

| R = Readable       |                                   | W = Writable                       |                           | -                | mented bit, read          |                    |             |

| -n = Value at F    | POR                               | '1' = Bit is set                   |                           | '0' = Bit is cle | ared                      | x = Bit is unkr    | IOWN        |

|                    | TON: Timer1                       | o                                  |                           |                  |                           |                    |             |

| bit 15             | 1 = Starts 16-                    |                                    |                           |                  |                           |                    |             |

|                    | 1 = Starts 16-<br>0 = Stops 16-   |                                    |                           |                  |                           |                    |             |

| bit 14             | •                                 | ted: Read as '                     | )'                        |                  |                           |                    |             |

| bit 13             | -                                 | 1 Stop in Idle N                   |                           |                  |                           |                    |             |

|                    | 1 = Discontine                    | ues module op                      | eration when              | device enters I  | dle mode                  |                    |             |

|                    |                                   | s module opera                     |                           | ode              |                           |                    |             |

| bit 12-7           | -                                 | ted: Read as '                     |                           |                  |                           |                    |             |

| bit 6              |                                   | er1 Gated Time                     | Accumulation              | Enable bit       |                           |                    |             |

|                    | When TCS =<br>This bit is igno    |                                    |                           |                  |                           |                    |             |

|                    | When TCS =                        |                                    |                           |                  |                           |                    |             |

|                    |                                   | e accumulatior                     | n is enabled              |                  |                           |                    |             |

|                    | 0 = Gated tim                     | e accumulatior                     | n is disabled             |                  |                           |                    |             |

| bit 5-4            |                                   | : Timer1 Input                     | Clock Prescal             | e Select bits    |                           |                    |             |

|                    | 11 = 1:256<br>10 = 1:64           |                                    |                           |                  |                           |                    |             |

|                    | 01 = 1:8                          |                                    |                           |                  |                           |                    |             |

|                    | 00 = 1:1                          |                                    |                           |                  |                           |                    |             |

| bit 3              | Unimplemen                        | ted: Read as '                     | )'                        |                  |                           |                    |             |

| bit 2              |                                   | er1 External Clo                   | ock Input Synd            | chronization Se  | elect bit <sup>(1)</sup>  |                    |             |

|                    | When TCS = $\frac{1}{1}$          |                                    | a al ciana ut             |                  |                           |                    |             |

|                    |                                   | izes external cl<br>synchronize ex |                           | nout             |                           |                    |             |

|                    | When TCS =                        | •                                  |                           | iput             |                           |                    |             |

|                    | This bit is igno                  |                                    |                           |                  |                           |                    |             |

| bit 1              | TCS: Timer1                       | Clock Source S                     | Select bit <sup>(1)</sup> |                  |                           |                    |             |

|                    |                                   | clock is from pir                  | n, T1CK (on th            | ne rising edge)  |                           |                    |             |

| hit 0              | 0 = Internal cl                   |                                    | ۰ <b>۲</b>                |                  |                           |                    |             |

| bit 0              | ommplemen                         | ted: Read as '                     | J                         |                  |                           |                    |             |

|                    | en Timer1 is en<br>mpts by user s |                                    |                           |                  | ode (TCS = 1, T<br>nored. | SYNC = 1, TO       | N = 1), any |

| R/W-0              | R/W-0                                                                                                     | R/W-0                                                                                                                             | R/W-0                                                                                   | R/W-0                                                        | R/W-0                 | R/W-0           | R/W-0    |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------|-----------------|----------|--|--|--|--|

| ALRMEN             | CHIME                                                                                                     | AMASK3                                                                                                                            | AMASK2                                                                                  | AMASK1                                                       | AMASK0                | ALRMPTR1        | ALRMPTR0 |  |  |  |  |

| bit 15             |                                                                                                           |                                                                                                                                   | 1                                                                                       | 1                                                            |                       |                 | bit 8    |  |  |  |  |

|                    |                                                                                                           |                                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

| R/W-0              | R/W-0                                                                                                     | R/W-0                                                                                                                             | R/W-0                                                                                   | R/W-0                                                        | R/W-0                 | R/W-0           | R/W-0    |  |  |  |  |

| ARPT7              | ARPT6                                                                                                     | ARPT5                                                                                                                             | ARPT4                                                                                   | ARPT3                                                        | ARPT2                 | ARPT1           | ARPT0    |  |  |  |  |

| bit 7              |                                                                                                           |                                                                                                                                   |                                                                                         |                                                              |                       |                 | bit (    |  |  |  |  |

| Legend:            |                                                                                                           |                                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

| R = Readable bit   |                                                                                                           | W = Writable                                                                                                                      | bit                                                                                     | U = Unimplem                                                 | nented bit, rea       | d as '0'        |          |  |  |  |  |

| -n = Value at POR  |                                                                                                           | '1' = Bit is set                                                                                                                  |                                                                                         | '0' = Bit is clea                                            | ared                  | x = Bit is unkr | nown     |  |  |  |  |

|                    |                                                                                                           |                                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

| bit 15             |                                                                                                           | larm Enable bit                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

|                    | 1 = Alarm is enabled (cleared automatically after an alarm event whenever ARPT<7:0> = 0x00 and CHIME = 0) |                                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

|                    | 0 = Alarm is                                                                                              | ,                                                                                                                                 |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

| bit 14             | CHIME: Chime Enable bit                                                                                   |                                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

|                    | 1 = Chime is enabled; ARPT<7:0> bits are allowed to roll over from 0x00 to 0xFF                           |                                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

|                    | 0 = Chime is                                                                                              | s disabled; ARP                                                                                                                   | T<7:0> bits st                                                                          | op once they re                                              | each 0x00             |                 |          |  |  |  |  |

| bit 13-10          | AMASK<3:0>: Alarm Mask Configuration bits                                                                 |                                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

|                    | 0000 = Every half second                                                                                  |                                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

|                    | 0001 = Every second<br>0010 = Every 10 seconds                                                            |                                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

|                    | 0011 = Every minute                                                                                       |                                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

|                    |                                                                                                           | y 10 minutes                                                                                                                      |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

|                    | 0101 = Ever                                                                                               |                                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

|                    | 0110 = Once a day<br>0111 = Once a week                                                                   |                                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

|                    | 1000 = Once a month                                                                                       |                                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

|                    | 1001 = Once a year (except when configured for February 29th, once every 4 years)                         |                                                                                                                                   |                                                                                         |                                                              |                       |                 |          |  |  |  |  |

|                    |                                                                                                           | e a year (except                                                                                                                  |                                                                                         | ired for Februa                                              | ry 29th, once e       | every 4 years)  |          |  |  |  |  |

|                    | 101x = Rese                                                                                               | e a year (except<br>erved – do not u                                                                                              | se                                                                                      | ired for Februa                                              | ry 29th, once e       | every 4 years)  |          |  |  |  |  |

| hit 9-8            | 101x = Rese<br>11xx = Rese                                                                                | e a year (except<br>erved – do not u<br>erved – do not u                                                                          | ise                                                                                     |                                                              |                       | every 4 years)  |          |  |  |  |  |

| bit 9-8            | 101x = Rese<br>11xx = Rese<br>ALRMPTR<                                                                    | e a year (except<br>erved – do not u<br>erved – do not u<br><b>1:0&gt;:</b> Alarm Val                                             | ise<br>ise<br>ue Register W                                                             | indow Pointer                                                | bits                  |                 | The      |  |  |  |  |

| bit 9-8            | 101x = Rese<br>11xx = Rese<br>ALRMPTR<<br>Points to the                                                   | e a year (except<br>erved – do not u<br>erved – do not u                                                                          | ise<br>lise<br>ue Register W<br>Alarm Value re                                          | indow Pointer l<br>egisters when r                           | bits<br>eading the AL | RMVAL register  |          |  |  |  |  |

|                    | 101x = Rese<br>11xx = Rese<br>ALRMPTR<<br>Points to the<br>ALRMPTR<                                       | e a year (except<br>erved – do not u<br>erved – do not u<br>fros: Alarm Val<br>corresponding                                      | ise<br>ise<br>ue Register W<br>Alarm Value re<br>ements on eve                          | indow Pointer<br>egisters when r<br>ery read or write        | bits<br>eading the AL | RMVAL register  |          |  |  |  |  |

|                    | 101x = Rese<br>11xx = Rese<br>ALRMPTR<<br>Points to the<br>ALRMPTR<<br>ARPT<7:0>:                         | e a year (except<br>erved – do not u<br>erved – do not u<br>1:0>: Alarm Val<br>corresponding<br>1:0> value decre                  | ise<br>ue Register W<br>Alarm Value re<br>ements on eve<br>Counter Value                | indow Pointer<br>egisters when r<br>ry read or write<br>bits | bits<br>eading the AL | RMVAL register  |          |  |  |  |  |

|                    | 101x = Rese<br>11xx = Rese<br>ALRMPTR<<br>Points to the<br>ALRMPTR<<br>ARPT<7:0>:                         | e a year (except<br>erved – do not u<br>erved – do not u<br>1:0>: Alarm Valu<br>corresponding<br>1:0> value decre<br>Alarm Repeat | ise<br>ue Register W<br>Alarm Value re<br>ements on eve<br>Counter Value                | indow Pointer<br>egisters when r<br>ry read or write<br>bits | bits<br>eading the AL | RMVAL register  |          |  |  |  |  |

|                    | 101x = Rese<br>11xx = Rese<br>ALRMPTR<<br>Points to the<br>ALRMPTR<<br>ARPT<7:0>:                         | e a year (except<br>erved – do not u<br>erved – do not u<br>1:0>: Alarm Valu<br>corresponding<br>1:0> value decre<br>Alarm Repeat | ise<br>ue Register W<br>Alarm Value re<br>ements on eve<br>Counter Value                | indow Pointer<br>egisters when r<br>ry read or write<br>bits | bits<br>eading the AL | RMVAL register  |          |  |  |  |  |

| bit 9-8<br>bit 7-0 | 101x = Rese<br>11xx = Rese<br>ALRMPTR<<br>Points to the<br>ALRMPTR<7<br>ARPT<7:0>:<br>11111111 =          | e a year (except<br>erved – do not u<br>erved – do not u<br>1:0>: Alarm Valu<br>corresponding<br>1:0> value decre<br>Alarm Repeat | use<br>Register W<br>Alarm Value re<br>ements on eve<br>Counter Value<br>at 255 more ti | indow Pointer<br>egisters when r<br>ry read or write<br>bits | bits<br>eading the AL | RMVAL register  |          |  |  |  |  |

## REGISTER 27-3: ALCFGRPT: ALARM CONFIGURATION REGISTER

## **REGISTER 28-1: PMCON: PARALLEL MASTER PORT CONTROL REGISTER<sup>(3)</sup> (CONTINUED)**

- bit 3 **CS1P:** Chip Select 0 Polarity bit<sup>(1)</sup> 1 = Active-high (PMCS1/PMCS)<sup>(2)</sup> 0 = Active-low (PMCS1/PMCS)

- bit 2 **BEP:** Byte Enable Polarity bit

- 1 = Byte enable is active-high (PMBE)

- 0 = Byte enable is active-low (PMBE)

- bit 1

WRSP: Write Strobe Polarity bit

For Slave Modes and Master Mode 2 (PMMODE<9:8> = 00, 01, 10):

1 = Write strobe is active-high (PMWR)

0 = Write strobe is active-low (PMWR)

For Master Mode 1 (PMMODE<9:8> = 11):

1 = Enables strobe active-high (PMENB)

0 = Enables strobe active-low (PMENB)

0 = Enables strobe active-low (PMENB)

bit 0

RDSP: Read Strobe Polarity bit

For Slave Modes and Master Mode 2 (PMMODE<9:8> = 00, 01, 10):

1 = Read strobe is active-high (PMRD)

- 0 = Read strobe is active-ligh (PMRD)

- 0 Read Strobe is active-low (FIVIRD)

- For Master Mode 1 (PMMODE<9:8> = 11):

- 1 = Enables strobe active-high (PMRD/PMWR)

- 0 = Enables strobe active-low (PMRD/PMWR)

- **Note 1:** These bits have no effect when their corresponding pins are used as address lines.

- 2: PMCS1 applies to Master mode and PMCS applies to Slave mode.

- 3: This register is not available on 44-pin devices.

| R-0                            | R/W-0                                     | R/W-0                             | R/W-0                    | R/W-0             | R/W-0                                                                  | R/W-0                              | R/W-0                             |  |  |

|--------------------------------|-------------------------------------------|-----------------------------------|--------------------------|-------------------|------------------------------------------------------------------------|------------------------------------|-----------------------------------|--|--|

| BUSY                           | IRQM1                                     | IRQM0                             | INCM1                    | INCM0             | MODE16                                                                 | MODE1                              | MODE0                             |  |  |

| bit 15                         |                                           |                                   |                          |                   |                                                                        |                                    | bit 8                             |  |  |

| D/// 0                         |                                           |                                   | DAMA                     | DAMA              | DAALO                                                                  | DAMO                               | DAMA                              |  |  |

| R/W-0<br>WAITB1 <sup>(1,</sup> | R/W-0<br>2,3)   WAITB0 <sup>(1,2,3)</sup> | R/W-0                             | R/W-0                    | R/W-0             | R/W-0                                                                  | R/W-0<br>WAITE1 <sup>(1,2,3)</sup> | R/W-0<br>WAITE0 <sup>(1,2,3</sup> |  |  |

|                                | 2,3) VVAITB0(1,2,3)                       | WAITM3                            | WAITM2                   | WAITM1            | WAITM0                                                                 | VVAITE1(1,2,3)                     |                                   |  |  |

| bit 7                          |                                           |                                   |                          |                   |                                                                        |                                    | bit                               |  |  |

| Legend:                        |                                           |                                   |                          |                   |                                                                        |                                    |                                   |  |  |

| R = Reada                      | able bit                                  | W = Writable                      | bit                      | U = Unimplen      | nented bit, rea                                                        | ıd as '0'                          |                                   |  |  |

| -n = Value at Reset            |                                           | '1' = Bit is set                  |                          | '0' = Bit is clea | ared                                                                   | x = Bit is unkr                    | nown                              |  |  |

|                                |                                           |                                   |                          |                   |                                                                        |                                    |                                   |  |  |

| bit 15                         |                                           | oit (Master mod                   | de only)                 |                   |                                                                        |                                    |                                   |  |  |

|                                | 1 = Port is bus<br>0 = Port is not        |                                   |                          |                   |                                                                        |                                    |                                   |  |  |

| bit 14-13                      |                                           | nterrupt Reque                    | est Mode bits            |                   |                                                                        |                                    |                                   |  |  |

|                                |                                           | • •                               |                          | uffer 3 is read   | or Write Buff                                                          | er 3 is written                    | (Buffered PS                      |  |  |

|                                |                                           |                                   | ite operation w          | /hen PMA<1:0>     | > = 11 (Addres                                                         | sable PSP mod                      | de only)                          |  |  |

|                                | 10 = Reserve                              |                                   |                          | a read/write av   | -l                                                                     |                                    |                                   |  |  |

|                                |                                           | rupt is generated a               |                          | e read/write cy   | cie                                                                    |                                    |                                   |  |  |

| bit 12-11                      |                                           | ncrement Mod                      |                          |                   |                                                                        |                                    |                                   |  |  |

|                                | 11 = PSP rea                              | d and write but                   | ffers auto-incre         | ement (Legacy     | acy PSP mode only)                                                     |                                    |                                   |  |  |

|                                |                                           | ent ADDR by 1                     | •                        | •                 |                                                                        |                                    |                                   |  |  |

|                                |                                           | nt ADDR by 1 of<br>ment or decrer | •                        | •                 |                                                                        |                                    |                                   |  |  |

| bit 10                         |                                           | 6-Bit Mode bit                    | nent of addres           | 5                 |                                                                        |                                    |                                   |  |  |

|                                |                                           |                                   | er is 16 hits a          | read/write to th  | na Nata regista                                                        | er invokes two 8                   | -hit transfers                    |  |  |

|                                |                                           |                                   |                          |                   |                                                                        | nvokes one 8-b                     |                                   |  |  |

| bit 9-8                        | MODE<1:0>:                                | Parallel Slave                    | Port Mode Se             | lect bits         |                                                                        |                                    |                                   |  |  |

|                                | 11 = Master N                             | Node 1 (PMCS                      | x, PMRD/ <del>PM</del> V | VR, PMENB, PI     | MBE, PMA <x:< td=""><td>0&gt; and PMD&lt;7:</td><td>:0&gt;)</td></x:<> | 0> and PMD<7:                      | :0>)                              |  |  |

|                                |                                           |                                   |                          | NR, PMBE, PM      |                                                                        |                                    | <b>.</b> .                        |  |  |

|                                |                                           |                                   |                          |                   |                                                                        | 0> and PMA<1:0<br>5x and PMD<7:0   |                                   |  |  |

| bit 7-6                        |                                           |                                   |                          | -                 |                                                                        | figuration bits <sup>(1</sup>      | -                                 |  |  |

| bit 7-0                        |                                           |                                   |                          |                   |                                                                        | TP (multiplexed                    |                                   |  |  |

|                                |                                           |                                   |                          |                   |                                                                        | TP (multiplexed                    |                                   |  |  |

|                                | 01 <b>= Data Wa</b>                       | it of 2 TP (dem                   | ultiplexed/mul           | tiplexed); addre  | ess phase of 2                                                         | TP (multiplexed                    | Í)                                |  |  |

|                                | 00 <b>= Data Wa</b>                       | it of 1 TP (dem                   | ultiplexed/mul           | tiplexed); addre  | ess phase of 1                                                         | TP (multiplexed                    | 1)                                |  |  |

| Note 1:                        | The applied Wait                          |                                   |                          |                   |                                                                        |                                    |                                   |  |  |

|                                | Section 4.1.8 "W<br>Family Reference      |                                   |                          |                   | <b>MP)</b> " (DS7057                                                   | 6) in the <i>"dsPIC</i>            | 33/PIC24                          |  |  |

| 2:                             | WAITB<1:0> and                            |                                   |                          |                   | ITM<3·0> = ∩                                                           | 000                                |                                   |  |  |

| 2.<br>3:                       | $T_P = 1/F_P$ .                           |                                   |                          |                   |                                                                        | 000.                               |                                   |  |  |

| 0.                             |                                           |                                   |                          |                   |                                                                        |                                    |                                   |  |  |

## REGISTER 28-2: PMMODE: PARALLEL MASTER PORT MODE REGISTER<sup>(4)</sup>

### 30.6 JTAG Interface

dsPIC33EPXXXGM3XX/6XX/7XX devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface is provided in future revisions of the document.

| Note: | Refer to the "dsPIC33/PIC24 Family      |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | Reference Manual", "Programming and     |  |  |  |  |  |  |

|       | Diagnostics" (DS70608) for further      |  |  |  |  |  |  |

|       | information on usage, configuration and |  |  |  |  |  |  |

|       | operation of the JTAG interface.        |  |  |  |  |  |  |

## 30.7 In-Circuit Serial Programming

The dsPIC33EPXXXGM3XX/6XX/7XX devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for details about In-Circuit Serial Programming (ICSP).

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

## 30.8 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or the REAL ICE<sup>™</sup> in-circuit emulator is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB X IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, Vss and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

## 30.9 Code Protection and CodeGuard™ Security

The dsPIC33EPXXXGM3XX/6XX/7XX devices offer basic implementation of CodeGuard Security that supports only General Segment (GS) security. This feature helps protect individual Intellectual Property.

Note: Refer to the "dsPIC33/PIC24 Family Reference Manual", "CodeGuard™ Security" (DS70634) for further information on usage, configuration and operation of CodeGuard Security.

| DC CHARACTER      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |                                |    |        |      |         |

|-------------------|-------------------------------------------------------|------|--------------------------------|----|--------|------|---------|

| Parameter No.     | Тур. <sup>(2)</sup>                                   | Max. | Doze<br>Ratio Units Conditions |    |        |      |         |

| Doze Current (IDC | DZE) <sup>(1)</sup>                                   |      |                                |    |        |      |         |