Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Betalls                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | -                                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | -                                                                                |

| Data Converters            | A/D 30x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

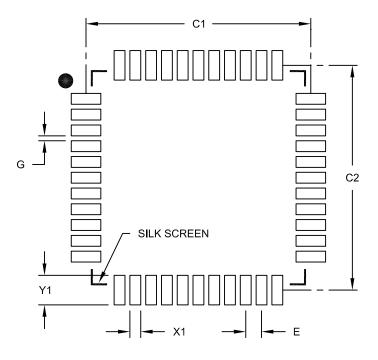

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm706-h-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXXGM3XX/6XX/7XX family requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins (regardless if ADC module is not used)

- (see Section 2.2 "Decoupling Capacitors")

VCAP

- (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for ADC module is implemented

| Note: | The       | AVdd    | and   | AVss    | pins | mu  | st be |

|-------|-----------|---------|-------|---------|------|-----|-------|

|       | connected |         | indep | endent  | of   | the | ADC   |

|       | volta     | ge refe | rence | source. |      |     |       |

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

| IABLE 4-    | <b>ZZ</b> . | ADO          |                          |           | REGIST   |          |          | NOLD)    |          |              |       |           |          |          |          |          |          |               |

|-------------|-------------|--------------|--------------------------|-----------|----------|----------|----------|----------|----------|--------------|-------|-----------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr.       | Bit 15       | Bit 14                   | Bit 13    | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7        | Bit 6 | Bit 5     | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| ADC2BUF9    | 0352        |              | ADC2 Data Buffer 9 xxxx  |           |          |          |          |          |          |              |       |           | xxxx     |          |          |          |          |               |

| ADC2BUFA    | 0354        |              | ADC2 Data Buffer 10 xxxx |           |          |          |          |          |          |              |       |           |          |          |          |          |          |               |

| ADC2BUFB    | 0356        |              |                          |           |          |          |          |          | ADC2 Da  | ta Buffer ´  | 11    |           |          |          |          |          |          | xxxx          |

| ADC2BUFC    | 0358        |              | ADC2 Data Buffer 12 xxxx |           |          |          |          |          |          |              |       |           |          |          |          |          |          |               |

| ADC2BUFD    | 035A        |              | ADC2 Data Buffer 13 xxxx |           |          |          |          |          |          |              |       |           |          |          |          |          |          |               |

| ADC2BUFE    | 035C        |              |                          |           |          |          |          |          | ADC2 Da  | ta Buffer 1  | 14    |           |          |          |          |          |          | xxxx          |

| ADC2BUFF    | 035E        |              |                          |           |          |          |          |          | ADC2 Da  | ta Buffer 1  | 15    |           |          |          |          |          |          | xxxx          |

| AD2CON1     | 0360        | ADON         | _                        | ADSIDL    | ADDMABM  |          | AD12B    | FORM1    | FORM0    | SSRC2        | SSRC1 | SSRC0     | SSRCG    | SIMSAM   | ASAM     | SAMP     | DONE     | 0000          |

| AD2CON2     | 0362        | VCFG2        | VCFG1                    | VCFG0     | OFFCAL   |          | CSCNA    | CHPS1    | CHPS0    | BUFS         | SMPI4 | SMPI3     | SMPI2    | SMPI1    | SMPI0    | BUFM     | ALTS     | 0000          |

| AD2CON3     | 0364        | ADRC         | -                        | _         | SAMC4    | SAMC3    | SAMC2    | SAMC1    | SAMC0    | ADCS7        | ADCS6 | ADCS5     | ADCS4    | ADCS3    | ADCS2    | ADCS1    | ADCS0    | 0000          |

| AD2CHS123   | 0366        | —            | -                        | _         | CH123SB2 | CH123SB1 | CH123NB1 | CH123NB0 | CH123SB0 | _            | _     | _         | CH123SA2 | CH123SA1 | CH123NA1 | CH123NA0 | CH123SA0 | 0000          |

| AD2CHS0     | 0368        | <b>CH0NB</b> | -                        | CH0SB5(1) | CH0SB4   | CH0SB3   | CH0SB2   | CH0SB1   | CH0SB0   | <b>CH0NA</b> | _     | CH0SA5(1) | CH0SA4   | CH0SA3   | CH0SA2   | CH0SA1   | CH0SA0   | 0000          |

| AD2CSSH     | 036E        |              |                          |           |          |          |          |          | CSS<     | :31:16>      |       |           |          |          |          |          |          | 0000          |

| AD2CSSL     | 0370        |              | CSS<15:0> 0000           |           |          |          |          |          |          |              |       |           |          |          |          |          |          |               |

| AD2CON4     | 0372        | —            | _                        | —         | —        | —        | —        | —        | ADDMAEN  | _            |       | _         | _        | _        | DMABL2   | DMABL1   | DMABL0   | 0000          |

#### TABLE 4-22: ADC1 AND ADC2 REGISTER MAP (CONTINUED)

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Bits 13 and bit 5 are reserved in the AD2CHS0 register, unlike the AD1CHS0 register.

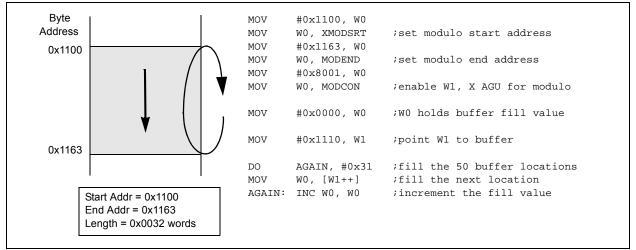

## 4.5 Modulo Addressing

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a Bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.5.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word-sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.5.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register bits, MODCON<15:0>, contain enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM) to which Modulo Addressing is to be applied is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set (MODCON<14>).

#### FIGURE 4-14: MODULO ADDRESSING OPERATION EXAMPLE

NOTES:

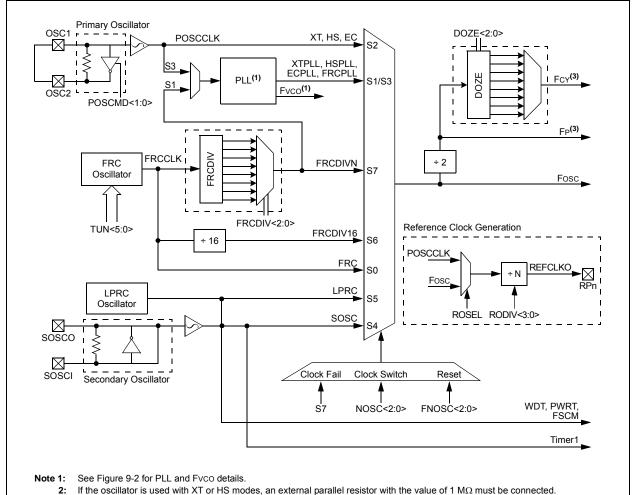

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Oscillator" (DS70580), which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this

document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze

## FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

© 2013-2014 Microchip Technology Inc.

mode is used with a doze ratio of 1:2 or lower.

3:

## 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation. For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## **10.4** Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled, using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

Note: If a PMD bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

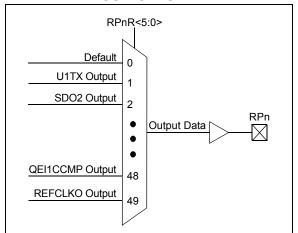

## 11.4.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-30 through Register 11-42). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-to-one and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

## 11.5 High-Voltage Detect

The dsPIC33EPXXXGM3XX/6XX/7XX devices contain High-Voltage Detection (HVD) which monitors the VCAP voltage. The HVD is used to monitor the VCAP supply voltage to ensure that an external connection does not raise the value above a safe level (~2.4V). If high core voltage is detected, all I/Os are disabled and put in a tri-state condition. The device remains in this I/O tristate condition as long as the high-voltage condition is present.

## 11.6 I/O Helpful Tips

- In some cases, certain pins, as defined in Table 33-10 under "Injection Current", have internal protection diodes to VDD and VSs. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD – 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specifications. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in **Section 33.0 "Electrical Characteristics"** for additional information.

| U-0                          | R/W-0                                                                                                                    | R/W-0                                                                                                                                                                                                                                          | R/W-0                                                               | R/W-0                       | R/W-0           | R/W-0            | R/W-0 |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------|-----------------|------------------|-------|

| _                            |                                                                                                                          |                                                                                                                                                                                                                                                |                                                                     | SCK3R<6:0>                  | •               |                  |       |

| bit 15                       |                                                                                                                          |                                                                                                                                                                                                                                                |                                                                     |                             |                 |                  | bit 8 |

|                              |                                                                                                                          |                                                                                                                                                                                                                                                |                                                                     |                             |                 |                  |       |

| U-0                          | R/W-0                                                                                                                    | R/W-0                                                                                                                                                                                                                                          | R/W-0                                                               | R/W-0                       | R/W-0           | R/W-0            | R/W-0 |

| _                            |                                                                                                                          |                                                                                                                                                                                                                                                |                                                                     | SDI3R<6:0>                  |                 |                  |       |

| bit 7                        |                                                                                                                          |                                                                                                                                                                                                                                                |                                                                     |                             |                 |                  | bit 0 |

|                              |                                                                                                                          |                                                                                                                                                                                                                                                |                                                                     |                             |                 |                  |       |

| Legend:                      |                                                                                                                          |                                                                                                                                                                                                                                                |                                                                     |                             |                 |                  |       |

| R = Readab                   | le bit                                                                                                                   | W = Writable                                                                                                                                                                                                                                   | bit                                                                 | U = Unimplen                | nented bit, rea | ad as '0'        |       |

| -n = Value a                 | t POR                                                                                                                    | '1' = Bit is set                                                                                                                                                                                                                               |                                                                     | '0' = Bit is clea           | ared            | x = Bit is unkr  | nown  |

| bit 14-8<br>bit 7<br>bit 6-0 | (see Table 1<br>1111111 =<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | <ul> <li>Assign SPI3</li> <li>1-2 for input pin</li> <li>Input tied to RP</li> <li>Input tied to CM</li> <li>Input tied to Vss</li> <li>nted: Read as '</li> <li>Assign SPI3 D</li> <li>1-2 for input pin</li> <li>Input tied to RP</li> </ul> | selection nur<br>124<br>P1<br>0'<br>Pata Input (SE<br>selection nur | nbers)<br>DI3) to the Corre |                 | RPn/RPIn Pin bit | is    |

|                              |                                                                                                                          | Input tied to CM<br>Input tied to Vss                                                                                                                                                                                                          |                                                                     |                             |                 |                  |       |

### REGISTER 11-23: RPINR29: PERIPHERAL PIN SELECT INPUT REGISTER 29

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0               |

|--------|-----|-----|-----|-----|-----|-----|---------------------|

| —      | —   | —   | —   | —   | —   | —   | IC32 <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8               |

| R/W-0                 | R/W/HS-0                | U-0 | R/W-0       | R/W-1       | R/W-1       | R/W-0       | R/W-1       |

|-----------------------|-------------------------|-----|-------------|-------------|-------------|-------------|-------------|

| ICTRIG <sup>(2)</sup> | TRIGSTAT <sup>(3)</sup> | _   | SYNCSEL4(4) | SYNCSEL3(4) | SYNCSEL2(4) | SYNCSEL1(4) | SYNCSEL0(4) |

| bit 7 bit 0           |                         |     |             |             |             |             |             |

| Legend:           | HS = Hardware Settable<br>bit |                             |                    |

|-------------------|-------------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit              | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-9 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

- bit 8 IC32: Input Capture x 32-Bit Timer Mode Select bit (Cascade mode)<sup>(1)</sup>

- 1 = Odd ICx and Even ICx form a single 32-bit input capture module

0 = Cascade module operation is disabled

- bit 7 ICTRIG: Input Capture x Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source is used to trigger the input capture timer (Trigger mode)

- Input source is used to synchronize the input capture timer to the timer of another module (Synchronization mode)

#### bit 6 TRIGSTAT: Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

- bit 5 Unimplemented: Read as '0'

- **Note 1:** The IC32 bit in both the Odd and Even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- **4:** Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x module (ICx) has one PTG input source. See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1, IC5

PTGO9 = IC2, IC6

PTGO10 = IC3, IC7

PTGO10 = IC3, IC7PTGO11 = IC4, IC8

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = Capture timer is unsynchronized

- 11110 = Capture timer is unsynchronized

- 11101 = Capture timer is unsynchronized

- 11100 = CTMU trigger is the source for the capture timer synchronization

- 11011 = ADC1 interrupt is the source for the capture timer synchronization<sup>(5)</sup>

- 11010 = Analog Comparator 3 is the source for the capture timer synchronization<sup>(5)</sup>

- 11001 = Analog Comparator 2 is the source for the capture timer synchronization<sup>(5)</sup>

- 11000 = Analog Comparator 1 is the source for the capture timer synchronization<sup>(5)</sup>

- 10111 = Input Capture 8 interrupt is the source for the capture timer synchronization

- 10110 = Input Capture 7 interrupt is the source for the capture timer synchronization 10101 = Input Capture 6 interrupt is the source for the capture timer synchronization

- 10100 = Input Capture 5 interrupt is the source for the capture timer synchronization

- 10011 = Input Capture 4 interrupt is the source for the capture timer synchronization

- 10010 = Input Capture 3 interrupt is the source for the capture timer synchronization

- 10001 = Input Capture 2 interrupt is the source for the capture timer synchronization

- 10000 = Input Capture 1 interrupt is the source for the capture timer synchronization

- 01111 = GP Timer5 is the source for the capture timer synchronization

- 01110 = GP Timer4 is the source for the capture timer synchronization

- 01101 = GP Timer3 is the source for the capture timer synchronization 01100 = GP Timer2 is the source for the capture timer synchronization

- 01100 = GP Timer2 is the source for the capture timer synchronization 01011 = GP Timer1 is the source for the capture timer synchronization

- 01011 = Of Timer 1's the source for the capture timer synchronization<sup>(6)</sup>

- 01001 = Capture timer is unsynchronized

- 01000 = Output Compare 8 is the source for the capture timer synchronization

- 00111 = Output Compare 7 is the source for the capture timer synchronization

- 00110 = Output Compare 6 is the source for the capture timer synchronization

- 00101 = Output Compare 5 is the source for the capture timer synchronization

- 00100 = Output Compare 4 is the source for the capture timer synchronization

- 00011 = Output Compare 3 is the source for the capture timer synchronization

- 00010 = Output Compare 2 is the source for the capture timer synchronization

- 00001 = Output Compare 1 is the source for the capture timer synchronization

- 00000 = Capture timer is unsynchronized

- **Note 1:** The IC32 bit in both the Odd and Even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x module (ICx) has one PTG input source. See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1, IC5

PTGO9 = IC2, IC6

PTGO10 = IC3, IC7

PTGO11 = IC4, IC8

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXGM3XX/6XX/7XX devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring: PWMLOCK = 0.

To gain write access to these locked registers, the user application must write two consecutive values of 0xABCD and 0x4321 to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWM1 WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

| 1                                                                                                            | pulled high externally in order to clear and disable the fault<br>register requires unlock sequence                                                                                                                                                                                               |  |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <pre>mov #0xabcd, w10 mov #0x4321, w11 mov #0x0000, w0 mov w10, PWMKEY mov w11, PWMKEY mov w0, FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |  |

| -                                                                                                            | and polarity using the IOCON1 register<br>register requires unlock sequence                                                                                                                                                                                                                       |  |

| <pre>mov #0xabcd, w10 mov #0x4321, w11 mov #0xF000, w0 mov w10, PWMKEY mov w11, PWMKEY mov w0, IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |  |

## **REGISTER 17-6: POSxHLD: POSITION COUNTER x HOLD REGISTER**

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|----------------------------------------------------------------------------|-------|-------|-------|------------------------------------|-------|-------|-------|--|

|                                                                            |       |       | POSH  | LD<15:8>                           |       |       |       |  |

| bit 15                                                                     |       |       |       |                                    |       |       | bit 8 |  |

|                                                                            |       |       |       |                                    |       |       |       |  |

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|                                                                            |       |       | POSH  | ILD<7:0>                           |       |       |       |  |

| bit 7                                                                      |       |       |       |                                    |       |       | bit 0 |  |

|                                                                            |       |       |       |                                    |       |       |       |  |

| Legend:                                                                    |       |       |       |                                    |       |       |       |  |

| R = Readable bit W = Writable bit                                          |       |       | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |       |       |                                    |       | nown  |       |  |

bit 15-0 **POSHLD<15:0>:** Holding Register for Reading and Writing POSxCNT bits

## REGISTER 17-7: VELxCNT: VELOCITY COUNTER x REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                  | R/W-0 | R/W-0 | R/W-0 |  |

|------------------------------------|-------|-------|-------|----------------------------------------|-------|-------|-------|--|

|                                    |       |       | VELC  | NT<15:8>                               |       |       |       |  |

| bit 15                             |       |       |       |                                        |       |       | bit 8 |  |

|                                    |       |       |       |                                        |       |       |       |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                  | R/W-0 | R/W-0 | R/W-0 |  |

|                                    |       |       | VELC  | NT<7:0>                                |       |       |       |  |

| bit 7                              |       |       |       |                                        |       |       | bit 0 |  |

|                                    |       |       |       |                                        |       |       |       |  |

| Legend:                            |       |       |       |                                        |       |       |       |  |

| R = Readable bit W = Writable bit  |       |       | oit   | U = Unimplemented bit, read as '0'     |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknow |       |       | nown  |  |

| L                                  |       |       |       |                                        |       |       |       |  |

bit 15-0 VELCNT<15:0>: Velocity Counter x bits

# dsPIC33EPXXXGM3XX/6XX/7XX

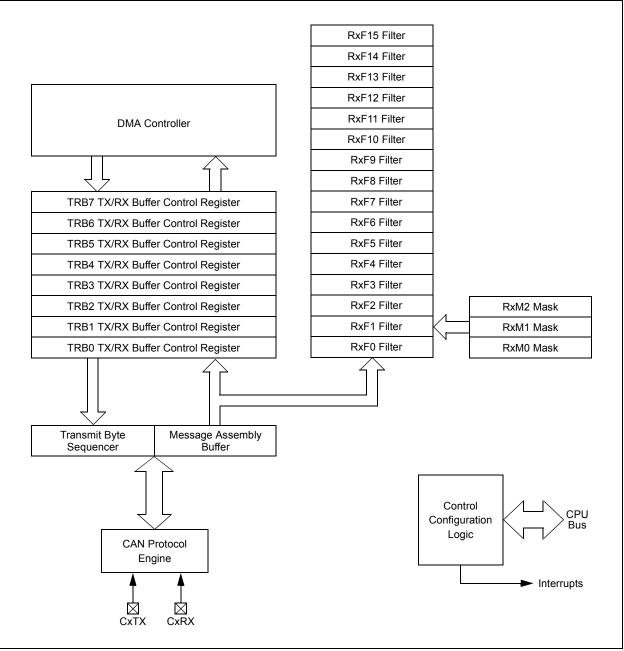

## FIGURE 21-1: CANX MODULE BLOCK DIAGRAM

## 21.2 Modes of Operation

The CANx module can operate in one of several operation modes selected by the user. These modes include:

- · Initialization mode

- · Disable mode

- Normal Operation mode

- · Listen Only mode

- Listen All Messages mode

- · Loopback mode

Modes are requested by setting the REQOP<2:0> bits (CxCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CxCTRL1<7:5>). The module does not change the mode and the OPMODEx bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

## 28.1 PMP Control Registers

## REGISTER 28-1: PMCON: PARALLEL MASTER PORT CONTROL REGISTER<sup>(3)</sup>

| R/W-0         | U-0                                                                                                                                  | R/W-0                     | R/W-0                | R/W-0                | R/W-0            | R/W-0           | R/W-0  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------|----------------------|------------------|-----------------|--------|--|--|--|

| PMPEN         | _                                                                                                                                    | PSIDL                     | ADRMUX1              | ADRMUX0              | PTBEEN           | PTWREN          | PTRDEN |  |  |  |

| bit 15        | •                                                                                                                                    |                           |                      |                      |                  |                 | bit 8  |  |  |  |

|               |                                                                                                                                      |                           |                      |                      |                  |                 |        |  |  |  |

| R/W-0         | R/W-0                                                                                                                                | R/W-0 <sup>(1)</sup>      | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0            | R/W-0           | R/W-0  |  |  |  |

| CSF1          | CSF0                                                                                                                                 | ALP                       | CS2P                 | CS1P                 | BEP              | WRSP            | RDSP   |  |  |  |

| bit 7         |                                                                                                                                      |                           |                      |                      |                  |                 | bit C  |  |  |  |

| Legend:       |                                                                                                                                      |                           |                      |                      |                  |                 |        |  |  |  |

| R = Readabl   | e bit                                                                                                                                | W = Writable              | bit                  | U = Unimplen         | nented bit, read | d as '0'        |        |  |  |  |

| -n = Value at | Reset                                                                                                                                | '1' = Bit is set          | +                    | '0' = Bit is clea    |                  | x = Bit is unkr | nown   |  |  |  |

|               |                                                                                                                                      |                           | ·                    |                      |                  |                 |        |  |  |  |

| bit 15        | PMPEN: Par                                                                                                                           | allel Master Po           | rt Enable bit        |                      |                  |                 |        |  |  |  |

|               | 1 = PMP mo                                                                                                                           | 1 = PMP module is enabled |                      |                      |                  |                 |        |  |  |  |

|               | 0 = PMP mo                                                                                                                           | dule is disabled          | l, no off-chip ac    | cess is perform      | ned              |                 |        |  |  |  |

| bit 14        | Unimpleme                                                                                                                            | nted: Read as '           | 0'                   |                      |                  |                 |        |  |  |  |

| bit 13        | PSIDL: PMP                                                                                                                           | Stop in Idle Mo           | ode bit              |                      |                  |                 |        |  |  |  |

|               |                                                                                                                                      | nues module op            |                      |                      | le mode          |                 |        |  |  |  |

| bit 12-11     | <ul> <li>0 = Continues module operation in Idle mode</li> <li>ADRMUX&lt;1:0&gt;: Address/Data Multiplexing Selection bits</li> </ul> |                           |                      |                      |                  |                 |        |  |  |  |

| 51(12)11      | 11 = Reserved                                                                                                                        |                           |                      |                      |                  |                 |        |  |  |  |

|               | 10 = All 16 bits of address are multiplexed on PMD<7:0> pins                                                                         |                           |                      |                      |                  |                 |        |  |  |  |

|               | 01 = Lower eight bits of address are multiplexed on PMD<7:0> pins, upper eight bits are on PMA<15:8>                                 |                           |                      |                      |                  |                 |        |  |  |  |

|               | 00 = Address and data appear on separate pins                                                                                        |                           |                      |                      |                  |                 |        |  |  |  |

| bit 10        | PTBEEN: Byte Enable Port Enable bit (16-Bit Master mode)                                                                             |                           |                      |                      |                  |                 |        |  |  |  |

|               |                                                                                                                                      | ort is enabled            |                      |                      |                  |                 |        |  |  |  |

| <b>h</b> # 0  |                                                                                                                                      | ort is disabled           | aha Dart Enabl       | - h:t                |                  |                 |        |  |  |  |

| bit 9         | PTWREN: Write Enable Strobe Port Enable bit                                                                                          |                           |                      |                      |                  |                 |        |  |  |  |

|               | 1 = PMWR/PMENB port is enabled<br>0 = PMWR/PMENB port is disabled                                                                    |                           |                      |                      |                  |                 |        |  |  |  |

| bit 8         |                                                                                                                                      | ead/Write Strob           |                      | oit                  |                  |                 |        |  |  |  |

|               |                                                                                                                                      | MWR port is er            |                      |                      |                  |                 |        |  |  |  |

|               | 0 = PMRD/P                                                                                                                           | MWR port is di            | sabled               |                      |                  |                 |        |  |  |  |

| bit 7-6       | CSF<1:0>: (                                                                                                                          | Chip Select Fun           | ction bits           |                      |                  |                 |        |  |  |  |

|               | 11 = Reserved                                                                                                                        |                           |                      |                      |                  |                 |        |  |  |  |

|               | 10 = PMCS1 and PMCS2 function as Chip Select                                                                                         |                           |                      |                      |                  |                 |        |  |  |  |

|               | 01 = PMCS2 functions as Chip Select, PMCS1 functions as Address Bit 14<br>00 = PMCS1 and PMCS2 function as Address Bits 15 and 14    |                           |                      |                      |                  |                 |        |  |  |  |

| bit 5         |                                                                                                                                      |                           |                      |                      | 1 14             |                 |        |  |  |  |

| bit 5         | ALP: Address Latch Polarity bit <sup>(1)</sup><br>1 = Active-high (PMALL and PMALH)                                                  |                           |                      |                      |                  |                 |        |  |  |  |

|               |                                                                                                                                      | w (PMALL and              |                      |                      |                  |                 |        |  |  |  |

| bit 4         |                                                                                                                                      | Select 1 Polarit          |                      |                      |                  |                 |        |  |  |  |

|               | 1 = Active-hi                                                                                                                        |                           | -                    |                      |                  |                 |        |  |  |  |

|               | 0 = Active-lo                                                                                                                        | w (PMCS2)                 |                      |                      |                  |                 |        |  |  |  |

| Note 1: T     |                                                                                                                                      | no effect when            | their correspor      | iding pins are u     | sed as addres    | s lines.        |        |  |  |  |

- **2:** PMCS1 applies to Master mode and PMCS applies to Slave mode.

- **3:** This register is not available on 44-pin devices.

# TABLE 33-39:SPI2 AND SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                          |    |       |                             |  |

|--------------------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----|-------|-----------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                    | Min. Typ. <sup>(2)</sup> |    | Units | Conditions                  |  |

| SP70               | FscP                  | Maximum SCKx Input Frequency                 | —                                                                                                                                                                                                                                                                                       |                          | 11 | MHz   | (Note 3)                    |  |

| SP72               | TscF                  | SCKx Input Fall Time                         | —                                                                                                                                                                                                                                                                                       | —                        | _  | ns    | See Parameter DO32 (Note 4) |  |

| SP73               | TscR                  | SCKx Input Rise Time                         | —                                                                                                                                                                                                                                                                                       | —                        | _  | ns    | See Parameter DO31 (Note 4) |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                   | —                                                                                                                                                                                                                                                                                       | —                        | _  | ns    | See Parameter DO32 (Note 4) |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                       | —                        | _  | ns    | See Parameter DO31 (Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    | —                                                                                                                                                                                                                                                                                       | 6                        | 20 | ns    |                             |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge | 30                                                                                                                                                                                                                                                                                      | —                        | _  | ns    |                             |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge   | 30                                                                                                                                                                                                                                                                                      | —                        | _  | ns    |                             |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge    | 30                                                                                                                                                                                                                                                                                      | _                        | _  | ns    |                             |  |

| SP50               | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↑ or SCKx ↓<br>Input           | 120                                                                                                                                                                                                                                                                                     | _                        |    | ns    |                             |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance       | 10                                                                                                                                                                                                                                                                                      | —                        | 50 | ns    | (Note 4)                    |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                        | 1.5 TCY + 40                                                                                                                                                                                                                                                                            | —                        | —  | ns    | (Note 4)                    |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

| AC CHARACTERISTICS |                           |                                   |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |                  |                        |  |  |

|--------------------|---------------------------|-----------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------|------------------------|--|--|

| Param<br>No.       | Symbol ("boroctorictic)"/ |                                   | eristic <sup>(4)</sup>    | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                               | Max. | Units            | Conditions             |  |  |

| IM10               | TLO:SCL                   | Clock Low Time                    | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                   |      | μS               |                        |  |  |

|                    |                           |                                   | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                   |      | μS               |                        |  |  |

|                    |                           |                                   | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                   | _    | μS               |                        |  |  |

| IM11               | THI:SCL                   | Clock High Time                   | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                   | —    | μS               |                        |  |  |

|                    |                           | -                                 | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                   | _    | μS               |                        |  |  |

|                    |                           |                                   | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                   | _    | μS               |                        |  |  |

| IM20               | TF:SCL                    | SDAx and SCLx                     | 100 kHz mode              | _                                                                                                                                                                                                                                                                                 | 300  | ns               | CB is specified to be  |  |  |

|                    |                           | Fall Time                         | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                       | 300  | ns               | from 10 to 400 pF      |  |  |

|                    |                           |                                   | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                                                                                                                                 | 100  | ns               | -                      |  |  |

| IM21               | TR:SCL                    | SDAx and SCLx                     | 100 kHz mode              | _                                                                                                                                                                                                                                                                                 | 1000 | ns               | CB is specified to be  |  |  |

|                    |                           | Rise Time                         | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                       | 300  | ns               | from 10 to 400 pF      |  |  |

|                    |                           |                                   | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                                                                                                                                 | 300  | ns               | -                      |  |  |

| IM25               | TSU:DAT                   | Data Input<br>Setup Time          | 100 kHz mode              | 250                                                                                                                                                                                                                                                                               |      | ns               |                        |  |  |

|                    |                           |                                   | 400 kHz mode              | 100                                                                                                                                                                                                                                                                               |      | ns               |                        |  |  |

|                    |                           |                                   | 1 MHz mode <sup>(2)</sup> | 40                                                                                                                                                                                                                                                                                |      | ns               |                        |  |  |

| IM26 THD:DA        | THD:DAT                   | Data Input<br>Hold Time           | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                 |      | μS               |                        |  |  |

|                    |                           |                                   | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                 | 0.9  | μS               | -                      |  |  |

|                    |                           |                                   | 1 MHz mode <sup>(2)</sup> | 0.2                                                                                                                                                                                                                                                                               | _    | μS               |                        |  |  |

| IM30               | TSU:STA                   | STA Start Condition<br>Setup Time | 100 kHz mode              | TCY/2 (BRG + 2)                                                                                                                                                                                                                                                                   |      | μS               | Only relevant for      |  |  |

|                    |                           |                                   | 400 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                   |      | μS               | Repeated Start         |  |  |

|                    |                           |                                   | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                   | _    | μs               | condition              |  |  |

| IM31               | THD:STA                   | TA Start Condition<br>Hold Time   | 100 kHz mode              | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                   | _    | μS               | After this period, the |  |  |

|                    |                           |                                   | 400 kHz mode              | Tcy/2 (BRG +2)                                                                                                                                                                                                                                                                    |      | μS               | first clock pulse is   |  |  |

|                    |                           |                                   | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                                                                                                                                                                                                                                                   |      | μs               | generated              |  |  |