Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

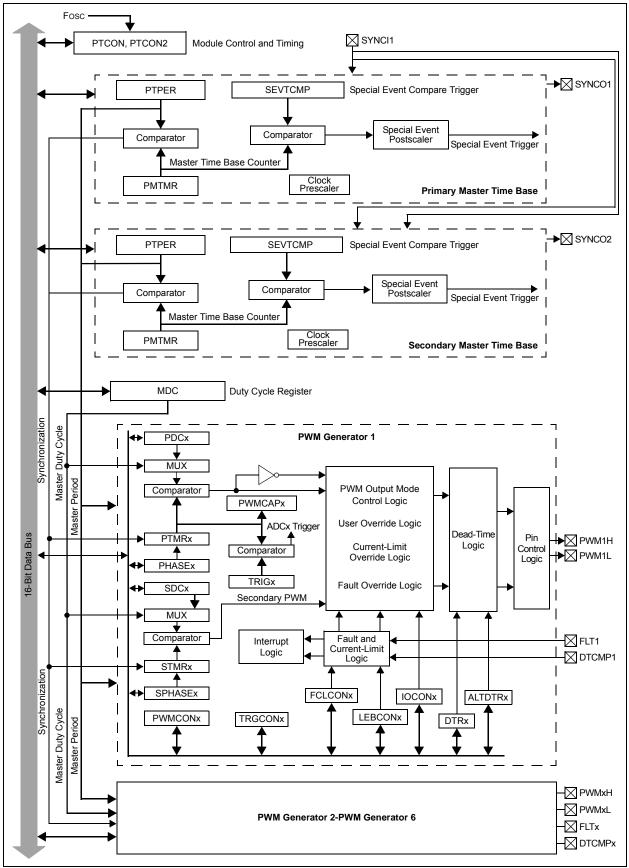

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 30x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm706-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-42: CTMU REGISTER MAP

| SFR<br>Name | Addr.  | Bit 15  | Bit 14  | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

|-------------|--------|---------|---------|----------|----------|----------|----------|----------|----------|---------|---------|----------|----------|----------|----------|-------|-------|---------------|

| CTMUCON1    | 033A   | CTMUEN  | —       | CTMUSIDL | TGEN     | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   |         | —       |          | -        | _        | —        | -     | -     | 0000          |

| CTMUCON2    | 2 033C | EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 | -     | —     | 0000          |

| CTMUICON    | 033E   | ITRIM5  | ITRIM4  | ITRIM3   | ITRIM2   | ITRIM1   | ITRIM0   | IRNG1    | IRNG0    |         | -       |          |          | _        | —        |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-43: JTAG INTERFACE REGISTER MAP

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10        | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------|--------|--------|--------|--------|--------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| JDATAH   | 0FF0  | —      | _      | _      | _      |        | JDATAH<27:16> |       |       |       |       |       | xxxx  |       |       |       |       |               |

| JDATAL   | 0FF2  |        |        |        |        |        | JDATAL<15:0>  |       |       |       |       |       | 0000  |       |       |       |       |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-44: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14                                             | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9    | Bit 8    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|----------------------------------------------------|---------|---------|---------|--------|----------|----------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ALRMVAL   | 0620  |        | Alarm Value Register Window Based on ALRMPTR<1:0>  |         |         |         |        |          |          |       |       |       | xxxx  |       |       |       |       |               |

| ALCFGRPT  | 0622  | ALRMEN | CHIME                                              | AMASK3  | AMASK2  | AMASK1  | AMASK0 | ALRMPTR1 | ALRMPTR0 | ARPT7 | ARPT6 | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 | 0000          |

| RTCVAL    | 0624  |        | RTCC Value Register Window Based on RTCPTR<1:0> xx |         |         |         |        |          |          |       | xxxx  |       |       |       |       |       |       |               |

| RCFGCAL   | 0626  | RTCEN  | —                                                  | RTCWREN | RTCSYNC | HALFSEC | RTCOE  | RTCPTR1  | RTCPTR0  | CAL7  | CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 5-6: NVMSRCADRL: NONVOLATILE DATA MEMORY LOWER ADDRESS REGISTER

| R/W-x                              | R/W-x | R/W-x        | R/W-x     | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|------------------------------------|-------|--------------|-----------|------------------|-----------------|-----------------|-------|

|                                    |       |              | NVMSRC    | ADRL<15:8>       |                 |                 |       |

| bit 15                             |       |              |           |                  |                 |                 | bit 8 |

| R/W-x                              | R/W-x | R/W-x        | R/W-x     | R/W-x            | R/W-x           | R/W-x           | r-0   |

|                                    |       | NVI          | MSRCADRL< | <7:1>            |                 |                 | 0     |

| bit 7                              |       |              |           |                  |                 |                 | bit 0 |

| Legend:                            |       | r = Reserved | bit       |                  |                 |                 |       |

| R = Readable                       | bit   | W = Writable | bit       | U = Unimplen     | nented bit, rea | d as '0'        |       |

| -n = Value at POR '1' = Bit is set |       |              |           | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-1 NVMSRCADRL<15:1>: Nonvolatile Data Memory Lower Address bits

bit 0 Reserved: Maintain as '0'

| Input Name <sup>(1)</sup>    | Function Name | Register | Configuration Bits |

|------------------------------|---------------|----------|--------------------|

| PWM Sync Input 1             | SYNCI1        | RPINR37  | SYNCI1R<6:0>       |

| PWM Dead-Time Compensation 1 | DTCMP1        | RPINR38  | DTCMP1R<6:0>       |

| PWM Dead-Time Compensation 2 | DTCMP2        | RPINR39  | DTCMP2R<6:0>       |

| PWM Dead-Time Compensation 3 | DTCMP3        | RPINR39  | DTCMP3R<6:0>       |

| PWM Dead-Time Compensation 4 | DTCMP4        | RPINR40  | DTCMP4R<6:0>       |

| PWM Dead-Time Compensation 5 | DTCMP5        | RPINR40  | DTCMP5R<6:0>       |

| PWM Dead-Time Compensation 6 | DTCMP6        | RPINR41  | DTCMP6R<6:0>       |

## TABLE 11-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION) (CONTINUED)

**Note 1:** Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

2: This input is available on dsPIC33EPXXXGM6XX/7XX devices only.

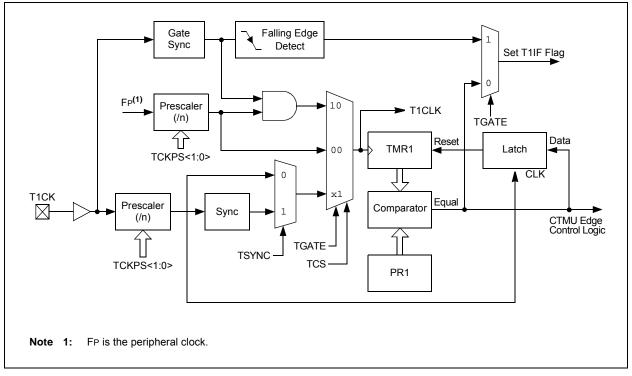

## 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Timers" (DS70362), which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running, interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit settings for different operating modes are given in the Table 12-1.

| TABLE 12-1: TIMEF | MODE SETTINGS |

|-------------------|---------------|

|-------------------|---------------|

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | x     |

| Gated Timer             | 0   | 1     | х     |

| Synchronous<br>Counter  | 1   | x     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

#### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

© 2013-2014 Microchip Technology Inc.

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0               |

|--------|-----|-----|-----|-----|-----|-----|---------------------|

| —      | —   | —   | —   | —   | —   | —   | IC32 <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8               |

| R/W-0                 | R/W/HS-0                | U-0 | R/W-0       | R/W-1       | R/W-1       | R/W-0       | R/W-1       |

|-----------------------|-------------------------|-----|-------------|-------------|-------------|-------------|-------------|

| ICTRIG <sup>(2)</sup> | TRIGSTAT <sup>(3)</sup> |     | SYNCSEL4(4) | SYNCSEL3(4) | SYNCSEL2(4) | SYNCSEL1(4) | SYNCSEL0(4) |

| bit 7                 |                         |     |             |             |             |             | bit 0       |

| Legend:           | HS = Hardware Settable<br>bit |                             |                    |

|-------------------|-------------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit              | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-9 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

- bit 8 IC32: Input Capture x 32-Bit Timer Mode Select bit (Cascade mode)<sup>(1)</sup>

- 1 = Odd ICx and Even ICx form a single 32-bit input capture module

0 = Cascade module operation is disabled

- bit 7 ICTRIG: Input Capture x Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source is used to trigger the input capture timer (Trigger mode)

- Input source is used to synchronize the input capture timer to the timer of another module (Synchronization mode)

#### bit 6 TRIGSTAT: Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

- bit 5 Unimplemented: Read as '0'

- **Note 1:** The IC32 bit in both the Odd and Even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- **4:** Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x module (ICx) has one PTG input source. See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1, IC5

PTGO9 = IC2, IC6

PTGO10 = IC3, IC7

PTGO10 = IC3, IC7PTGO11 = IC4, IC8

## REGISTER 16-7: STPER: PWMx SECONDARY MASTER TIME BASE PERIOD REGISTER

| R/W-1                                                           | R/W-1 | R/W-1           | R/W-1                              | R/W-1   | R/W-1 | R/W-1 | R/W-1 |

|-----------------------------------------------------------------|-------|-----------------|------------------------------------|---------|-------|-------|-------|

|                                                                 |       |                 | STPE                               | R<15:8> |       |       |       |

| bit 15                                                          |       |                 |                                    |         |       |       | bit 8 |

| R/W-1                                                           | R/W-1 | R/W-1           | R/W-1                              | R/W-1   | R/W-0 | R/W-0 | R/W-0 |

|                                                                 |       |                 | STPE                               | R<7:0>  |       |       |       |

| bit 7                                                           |       |                 |                                    |         |       |       | bit 0 |

| Legend:                                                         |       |                 |                                    |         |       |       |       |

| R = Readable bit W = Writable bit                               |       | it              | U = Unimplemented bit, read as '0' |         |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit |       | x = Bit is unkr | nown                               |         |       |       |       |

bit 15-0 STPER<15:0>: PWMx Secondary Master Time Base (PMTMR) Period Value bits

#### REGISTER 16-8: SSEVTCMP: PWMx SECONDARY SPECIAL EVENT COMPARE REGISTER

| R/W-0                             | R/W-0                                                           | R/W-0 | R/W-0                              | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|-----------------------------------|-----------------------------------------------------------------|-------|------------------------------------|-----------|-------|-------|-------|

|                                   |                                                                 |       | SSEVTO                             | CMP<15:8> |       |       |       |

| bit 15                            |                                                                 |       |                                    |           |       |       | bit 8 |

|                                   |                                                                 |       |                                    |           |       |       |       |

| R/W-0                             | R/W-0                                                           | R/W-0 | R/W-0                              | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|                                   |                                                                 |       | SSEVT                              | CMP<7:0>  |       |       |       |

| bit 7                             |                                                                 |       |                                    |           |       |       | bit 0 |

|                                   |                                                                 |       |                                    |           |       |       |       |

| Legend:                           |                                                                 |       |                                    |           |       |       |       |

| R = Readable bit W = Writable bit |                                                                 | t     | U = Unimplemented bit, read as '0' |           |       |       |       |

| -n = Value at P                   | alue at POR '1' = Bit is set '0' = Bit is cleared x = Bit is un |       | x = Bit is unkr                    | nown      |       |       |       |

|                                   |                                                                 |       |                                    |           |       |       |       |

bit 15-0 SSEVTCMP<15:0>: PWMx Secondary Special Event Compare Count Value bits

| R/W-0               | R/W-0                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                    | U-0                                                                            | U-0                     | U-0                    |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------|------------------------|--|

| TRGDIV3             | TRGDIV2                                                                                                                                                                                                                                                      | TRGDIV1                                                                                                                                                                                                                                                                                                                                                                                                                         | TRGDIV0                                                                                                                                                                                                                                                                                    |                                                                                                                                        | _                                                                              |                         | _                      |  |

| bit 15              |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                                |                         | bit                    |  |

| U-0                 | U-0                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                  | R/W-0                                                                          | R/W-0                   | R/W-0                  |  |

| _                   |                                                                                                                                                                                                                                                              | TRGSTRT5 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                         | TRGSTRT5 <sup>(1)</sup>                                                                                                                                                                                                                                                                    | TRGSTRT5 <sup>(1)</sup>                                                                                                                | TRGSTRT5 <sup>(1)</sup>                                                        | TRGSTRT5 <sup>(1)</sup> | TRGSTRT5 <sup>(1</sup> |  |

| bit 7               |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                                |                         | bit                    |  |

| Legend:             |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                                |                         |                        |  |

| R = Readabl         | e bit                                                                                                                                                                                                                                                        | W = Writable I                                                                                                                                                                                                                                                                                                                                                                                                                  | bit                                                                                                                                                                                                                                                                                        | U = Unimplem                                                                                                                           | ented bit, read                                                                | as '0'                  |                        |  |

| -n = Value at       | POR                                                                                                                                                                                                                                                          | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                            | (0) = Bit is cleared $x = Bit is unknown$                                                                                              |                                                                                |                         |                        |  |

|                     |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                                |                         |                        |  |

| bit 15-12           | 1111 = Trigg<br>1110 = Trigg<br>1101 = Trigg<br>1001 = Trigg<br>1010 = Trigg<br>1001 = Trigg<br>1000 = Trigg<br>0111 = Trigg<br>0110 = Trigg<br>0101 = Trigg<br>0101 = Trigg<br>0011 = Trigg<br>0010 = Trigg<br>0001 = Trigg<br>0001 = Trigg<br>0000 = Trigg | >: Trigger # Ou<br>er output for ev<br>er output for ev | ery 16th trigge<br>ery 15th trigge<br>ery 15th trigge<br>ery 13th trigge<br>ery 12th trigge<br>ery 12th trigge<br>ery 10th trigger<br>ery 9th trigger<br>ery 8th trigger<br>ery 6th trigger<br>ery 5th trigger<br>ery 5th trigger<br>ery 3rd trigger<br>ery 2nd trigger<br>ery trigger eve | r event<br>r event<br>r event<br>r event<br>r event<br>r event<br>event<br>event<br>event<br>event<br>event<br>event<br>event<br>event |                                                                                |                         |                        |  |

| bit 11-6<br>bit 5-0 | TRGSTRT<5<br>111111 = Wa                                                                                                                                                                                                                                     | ait 63 PWM cyc                                                                                                                                                                                                                                                                                                                                                                                                                  | stscaler Start E<br>les before gen<br>es before gene                                                                                                                                                                                                                                       | rating the first t                                                                                                                     | its <sup>(1)</sup><br>trigger event af<br>rigger event afte<br>gger event afte | er the module is        | s enabled              |  |

## REGISTER 16-18: TRGCONx: PWMx TRIGGER CONTROL REGISTER

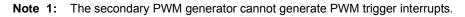

#### FIGURE 17-1: QEIX BLOCK DIAGRAM

JSPIC33EPXXXGM3XX/6XX/7XX

| R/W-0         | R/W-0                                                                   | R/W-0            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

|---------------|-------------------------------------------------------------------------|------------------|------------------|------------------|------------------|-----------------|-------|--|--|

| F7BP3         | F7BP2                                                                   | F7BP1            | F7BP0            | F6BP3            | F6BP2            | F6BP1           | F6BP0 |  |  |

| bit 15        |                                                                         |                  |                  |                  |                  |                 | bit 8 |  |  |

|               |                                                                         |                  |                  |                  |                  |                 |       |  |  |

| R/W-0         | R/W-0                                                                   | R/W-0            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

| F5BP3         | F5BP2                                                                   | F5BP1            | F5BP0            | F4BP3            | F4BP2            | F4BP1           | F4BP0 |  |  |

| bit 7         |                                                                         |                  |                  |                  |                  |                 | bit 0 |  |  |

| [             |                                                                         |                  |                  |                  |                  |                 |       |  |  |

| Legend:       |                                                                         |                  |                  |                  |                  |                 |       |  |  |

| R = Readable  | e bit                                                                   | W = Writable     | bit              | U = Unimpler     | mented bit, read | d as '0'        |       |  |  |

| -n = Value at | POR                                                                     | '1' = Bit is set |                  | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |  |  |

|               |                                                                         |                  |                  |                  |                  |                 |       |  |  |

| bit 15-12     |                                                                         | RX Buffer Masl   |                  |                  |                  |                 |       |  |  |

|               |                                                                         | hits received in |                  | -                |                  |                 |       |  |  |

|               | 1110 = Filter                                                           | hits received ir | NRX Buffer 14    | 4                |                  |                 |       |  |  |

|               | •                                                                       |                  |                  |                  |                  |                 |       |  |  |

|               | •                                                                       |                  |                  |                  |                  |                 |       |  |  |

|               | 0001 <b>= Filter</b>                                                    | hits received in | NRX Buffer 1     |                  |                  |                 |       |  |  |

|               | 0000 = Filter                                                           | hits received in | n RX Buffer 0    |                  |                  |                 |       |  |  |

| bit 11-8      | F6BP<3:0>:                                                              | RX Buffer Masl   | k for Filter 6 b | oits (same value | es as bits 15-12 | )               |       |  |  |

| bit 7-4       | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits 15-12) |                  |                  |                  |                  |                 |       |  |  |

|               |                                                                         |                  |                  |                  |                  |                 |       |  |  |

## REGISTER 21-13: CxBUFPNT2: CANx FILTERS 4-7 BUFFER POINTER REGISTER 2

#### REGISTER 21-14: CxBUFPNT3: CANx FILTERS 8-11 BUFFER POINTER REGISTER 3

F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits 15-12)

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| F11BP3 | F11BP2 | F11BP1 | F11BP0 | F10BP3 | F10BP2 | F10BP1 | F10BP0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-0  |

| F9BP3  | F9BP2  | F9BP1  | F9BP0  | F8BP3  | F8BP2  | F8BP1  | F8BP0  |

| bit 7  | ·      |        |        |        |        |        | bit 0  |

|        |        |        |        |        |        |        |        |

| Logond |        |        |        |        |        |        |        |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-12 | F11BP<3:0>: RX Buffer Mask for Filter 11 bits<br>1111 = Filter hits received in RX FIFO buffer<br>1110 = Filter hits received in RX Buffer 14<br>• |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 0001 = Filter hits received in RX Buffer 1<br>0000 = Filter hits received in RX Buffer 0                                                           |

| bit 11-8  | F10BP<3:0>: RX Buffer Mask for Filter 10 bits (same values as bits 15-12)                                                                          |

| bit 7-4   | F9BP<3:0>: RX Buffer Mask for Filter 9 bits (same values as bits 15-12)                                                                            |

| bit 3-0   | F8BP<3:0>: RX Buffer Mask for Filter 8 bits (same values as bits 15-12)                                                                            |

© 2013-2014 Microchip Technology Inc.

bit 3-0

## 24.2 DCI Control Registers

## REGISTER 24-1: DCICON1: DCI CONTROL REGISTER 1

| 1<br>bit 14 Re<br>bit 13 De<br>1<br>0<br>bit 12 Re<br>bit 11 DI                                                                                                                                                                                                                                                                                                     | e bit<br>POR<br>= DCI module<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will | e is disabled<br>ad as '0'                                                                                                       | t              | r-0<br>r<br>U = Unimplem<br>'0' = Bit is clea | r-0<br>r<br>ented bit, read a | CSCKE<br>R/W-0<br>COFSM1<br>as '0'<br>x = Bit is unkno | COFSD<br>bit 8<br>R/W-0<br>COFSM0<br>bit 0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------|-------------------------------|--------------------------------------------------------|--------------------------------------------|

| R/W-0         UNFM         bit 7         Legend:         R = Readable         -n = Value at         bit 15       D0         bit 14       Re         bit 13       D0         bit 13       D0         bit 13       D0         bit 13       D0         bit 14       Re         bit 13       D0         bit 14       Re         bit 13       D0         bit 14       D1 | CSDOM<br>e bit<br>POR<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will        | DJST<br>r = Reserved bi<br>W = Writable bi<br>'1' = Bit is set<br>odule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0' | r<br>t<br>t    | r<br>U = Unimplem                             | r<br>ented bit, read a        | COFSM1                                                 | R/W-0<br>COFSM0<br>bit (                   |

| UNFM<br>bit 7<br>Legend:<br>R = Readable<br>-n = Value at<br>bit 15 D0<br>1<br>0<br>bit 14 Re<br>bit 13 D0<br>1<br>0<br>bit 12 Re<br>bit 12 Re                                                                                                                                                                                                                      | CSDOM<br>e bit<br>POR<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will        | DJST<br>r = Reserved bi<br>W = Writable bi<br>'1' = Bit is set<br>odule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0' | r<br>t<br>t    | r<br>U = Unimplem                             | r<br>ented bit, read a        | COFSM1                                                 | COFSM0<br>bit (                            |

| UNFM<br>bit 7<br>Legend:<br>R = Readable<br>-n = Value at<br>bit 15 D0<br>1<br>0<br>bit 14 Re<br>bit 13 D0<br>1<br>0<br>bit 12 Re<br>bit 12 Re                                                                                                                                                                                                                      | CSDOM<br>e bit<br>POR<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will        | DJST<br>r = Reserved bi<br>W = Writable bi<br>'1' = Bit is set<br>odule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0' | r<br>t<br>t    | r<br>U = Unimplem                             | r<br>ented bit, read a        | COFSM1                                                 | COFSM0<br>bit (                            |

| bit 7<br>Legend:<br>R = Readable<br>-n = Value at<br>bit 15 De<br>1<br>0<br>bit 14 Re<br>bit 13 De<br>1<br>0<br>bit 12 Re<br>bit 12 Re                                                                                                                                                                                                                              | e bit<br>POR<br>= DCI module<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will | r = Reserved bi<br>W = Writable bi<br>'1' = Bit is set<br>odule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0'         | t<br>t         | U = Unimplem                                  | ented bit, read a             | as '0'                                                 | bit (                                      |

| R = Readable<br>-n = Value at<br>bit 15 De<br>bit 14 Re<br>bit 13 De<br>bit 13 De<br>bit 12 Re<br>bit 11 De                                                                                                                                                                                                                                                         | e bit<br>POR<br>= DCI module<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will | W = Writable bi<br>'1' = Bit is set<br>odule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0'                            | t              | -                                             |                               |                                                        | own                                        |

| R = Readable<br>-n = Value at<br>bit 15 D<br>bit 14 Re<br>bit 13 D<br>bit 13 D<br>bit 12 Re<br>bit 11 D                                                                                                                                                                                                                                                             | POR<br>= DCI module<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will          | '1' = Bit is set<br>odule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0'                                               |                | -                                             |                               |                                                        | own                                        |

| bit 15 D(<br>1<br>0<br>bit 14 R(<br>bit 13 D(<br>1<br>0<br>bit 12 R(<br>bit 11 D)                                                                                                                                                                                                                                                                                   | CIEN: DCI M<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                  | odule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0'                                                                   | t              | -                                             |                               |                                                        | own                                        |

| 1<br>0<br>bit 14<br>8<br>bit 13<br>1<br>0<br>bit 12<br>8<br>bit 12<br>1<br>0<br>bit 12<br>1<br>0                                                                                                                                                                                                                                                                    | = DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                                 | e is enabled<br>e is disabled<br>ad as '0'                                                                                       | t              |                                               |                               |                                                        |                                            |

| 1<br>0<br>bit 14<br>Re<br>bit 13<br>1<br>0<br>bit 12<br>Re<br>bit 11<br>D                                                                                                                                                                                                                                                                                           | = DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                                 | e is enabled<br>e is disabled<br>ad as '0'                                                                                       | t              |                                               |                               |                                                        |                                            |

| 0<br>bit 14 Re<br>bit 13 De<br>1<br>0<br>bit 12 Re<br>bit 11 De                                                                                                                                                                                                                                                                                                     | = DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                                                 | e is disabled<br>ad as '0'                                                                                                       |                |                                               |                               |                                                        |                                            |

| bit 14 Re<br>bit 13 D<br>1<br>0<br>bit 12 Re<br>bit 11 D                                                                                                                                                                                                                                                                                                            | eserved: Rea<br>CISIDL: DCI<br>= Module will                                                                 | ad as '0'                                                                                                                        |                |                                               |                               |                                                        |                                            |

| bit 13 D(<br>1<br>0<br>bit 12 Re<br>bit 11 DI                                                                                                                                                                                                                                                                                                                       | <b>CISIDL:</b> DCI<br>= Module will                                                                          |                                                                                                                                  |                |                                               |                               |                                                        |                                            |

| 1<br>0<br>bit 12 Re<br>bit 11 DI                                                                                                                                                                                                                                                                                                                                    | = Module will                                                                                                | Stop in Idle Con                                                                                                                 |                |                                               |                               |                                                        |                                            |

| 0<br>bit 12 Re<br>bit 11 Di                                                                                                                                                                                                                                                                                                                                         |                                                                                                              | •                                                                                                                                |                |                                               |                               |                                                        |                                            |

| bit 12 Re<br>bit 11 DI                                                                                                                                                                                                                                                                                                                                              |                                                                                                              | I halt in CPU Idle<br>I continue to ope                                                                                          |                | Idle mode                                     |                               |                                                        |                                            |

| bit 11 DI                                                                                                                                                                                                                                                                                                                                                           | eserved: Rea                                                                                                 | -                                                                                                                                |                |                                               |                               |                                                        |                                            |

|                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              | al Loopback Mod                                                                                                                  | le Control hit |                                               |                               |                                                        |                                            |

| 1                                                                                                                                                                                                                                                                                                                                                                   | •                                                                                                            | •                                                                                                                                |                | 0I and CSDO pin                               | s are internally o            | connected                                              |                                            |

|                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              | pback mode is d                                                                                                                  |                |                                               |                               |                                                        |                                            |

| bit 10 C                                                                                                                                                                                                                                                                                                                                                            | SCKD: Samp                                                                                                   | ole Clock Direction                                                                                                              | on Control bi  | t                                             |                               |                                                        |                                            |

|                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              | is an input when<br>is an output whe                                                                                             |                |                                               |                               |                                                        |                                            |

| bit 9 C                                                                                                                                                                                                                                                                                                                                                             | SCKE: Samp                                                                                                   | le Clock Edge C                                                                                                                  | Control bit    |                                               |                               |                                                        |                                            |

| 1                                                                                                                                                                                                                                                                                                                                                                   | = Data chang                                                                                                 | ges on serial clo                                                                                                                | ck falling edg | je, sampled on s                              | erial clock rising            | l edge                                                 |                                            |

| 0                                                                                                                                                                                                                                                                                                                                                                   | = Data chang                                                                                                 | ges on serial clo                                                                                                                | ck rising edg  | e, sampled on se                              | erial clock falling           | l edge                                                 |                                            |

|                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              | e Synchronizatio                                                                                                                 |                |                                               |                               |                                                        |                                            |

|                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              | s an input when                                                                                                                  |                |                                               |                               |                                                        |                                            |

|                                                                                                                                                                                                                                                                                                                                                                     | = COFS pin i<br>NFM: Underfi                                                                                 | is an output whe                                                                                                                 | en DCI modul   | le is enabled                                 |                               |                                                        |                                            |

| 1                                                                                                                                                                                                                                                                                                                                                                   | = Transmits I                                                                                                |                                                                                                                                  |                | smit registers on                             | a transmit unde               | rflow                                                  |                                            |

|                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              | I Data Output M                                                                                                                  |                |                                               |                               |                                                        |                                            |

|                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              | •                                                                                                                                |                | led transmit time                             | slots                         |                                                        |                                            |

|                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              |                                                                                                                                  |                | ansmit time slots                             |                               |                                                        |                                            |

| bit 5 D.                                                                                                                                                                                                                                                                                                                                                            | JST: DCI Dat                                                                                                 | a Justification C                                                                                                                | ontrol bit     |                                               |                               |                                                        |                                            |

|                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              |                                                                                                                                  |                | ring the same ser<br>one serial clock c       |                               |                                                        |                                            |

| bit 4-2 Re                                                                                                                                                                                                                                                                                                                                                          | eserved: Rea                                                                                                 | <b>ad as</b> '0'                                                                                                                 |                |                                               |                               |                                                        |                                            |

| bit 1-0 CO                                                                                                                                                                                                                                                                                                                                                          | OFSM<1:0>:                                                                                                   | Frame Sync Mo                                                                                                                    | ode bits       |                                               |                               |                                                        |                                            |

| 11                                                                                                                                                                                                                                                                                                                                                                  | L = 20-Bit AC                                                                                                | -Link mode                                                                                                                       |                |                                               |                               |                                                        |                                            |

|                                                                                                                                                                                                                                                                                                                                                                     | = 16-Bit AC                                                                                                  |                                                                                                                                  |                |                                               |                               |                                                        |                                            |

|                                                                                                                                                                                                                                                                                                                                                                     | L = I <sup>2</sup> S Frame<br>) = Multi-Cha                                                                  | e Sync mode<br>Innel Frame Syn                                                                                                   | ic mode        |                                               |                               |                                                        |                                            |

## REGISTER 24-5: RSCON: DCI RECEIVE SLOT CONTROL REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|--|

|                 |       |                  | RSE   | <15:8>                                  |       |       |       |  |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |  |

|                 |       |                  |       |                                         |       |       |       |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|                 |       |                  | RSE   | <7:0>                                   |       |       |       |  |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |  |

|                 |       |                  |       |                                         |       |       |       |  |

| Legend:         |       |                  |       |                                         |       |       |       |  |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |  |

bit 15-0 RSE<15:0>: DCI Receive Slot Enable bits

1 = CSDI data is received during Individual Time Slot n

0 = CSDI data is ignored during Individual Time Slot n

#### REGISTER 24-6: TSCON: DCI TRANSMIT SLOT CONTROL REGISTER

| R/W-0                                                                 | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|-----------------------------------------------------------------------|-------|-------|-----------------|------------------------------------|-------|-------|-------|--|

|                                                                       |       |       | TSE             | <15:8>                             |       |       |       |  |

| bit 15                                                                |       |       |                 |                                    |       |       | bit 8 |  |

|                                                                       |       |       |                 |                                    |       |       |       |  |

| R/W-0                                                                 | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|                                                                       |       |       | TSE             | <7:0>                              |       |       |       |  |

| bit 7                                                                 |       |       |                 |                                    |       |       | bit 0 |  |

|                                                                       |       |       |                 |                                    |       |       |       |  |

| Legend:                                                               |       |       |                 |                                    |       |       |       |  |

| R = Readable bit W = Writable bit                                     |       |       | bit             | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is un |       |       | x = Bit is unkr | nown                               |       |       |       |  |

|                                                                       |       |       |                 |                                    |       |       |       |  |

bit 15-0 TSE<15:0>: DCI Transmit Slot Enable Control bits

1 = Transmit buffer contents are sent during Individual Time Slot n

0 = CSDO pin is tri-stated or driven to logic '0' during the individual time slot, depending on the state of the CSDOM bit

#### REGISTER 26-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT **CONTROL REGISTER**

| U-0    | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | RW-0     |

|--------|-----|-----|-----|----------|----------|----------|----------|