Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 30x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm706-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXXGM3XX/6XX/7XX

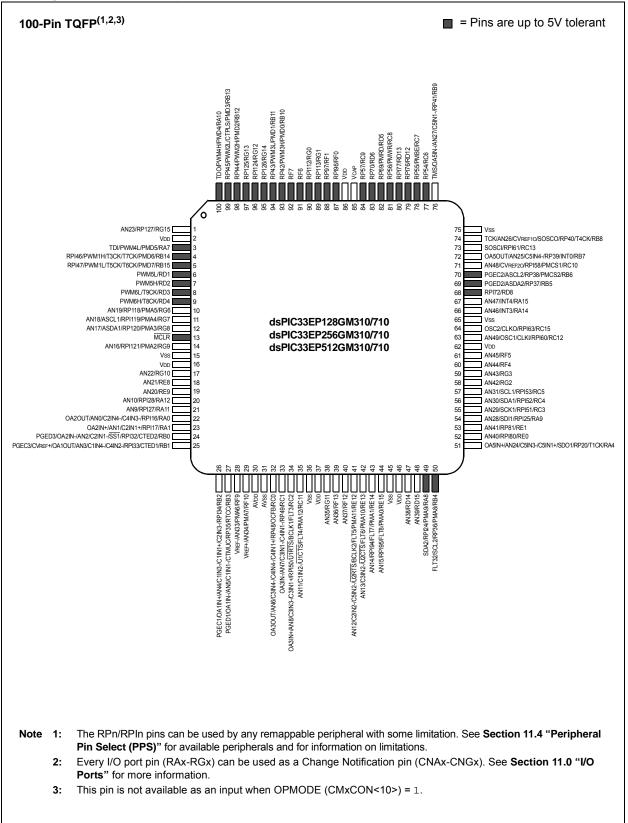

### **Pin Diagrams (Continued)**

## TABLE 1-1: PINOUT I/O DESCRIPTIONS

| Pin Name                                    | Pin<br>Type | Buffer<br>Type         | PPS              | Description                                                                                                                                                                        |

|---------------------------------------------|-------------|------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN49                                    | Ι           | Analog                 | No               | Analog Input Channels 0-49.                                                                                                                                                        |

| CLKI                                        | I           | ST/<br>CMOS            | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |

| CLKO                                        | 0           | _                      | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                                        | I           | ST/                    | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |

| OSC2                                        | I/O         | CMOS<br>—              | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |

| SOSCI                                       | I           | ST/<br>CMOS            | No               | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                     |

| SOSCO                                       | 0           | _                      | No               | 32.768 kHz low-power oscillator crystal output.                                                                                                                                    |

| IC1-IC8                                     | I           | ST                     | Yes              | Input Capture Inputs 1 through 8.                                                                                                                                                  |

| OCFA<br>OCFB<br>OC1-OC8                     | <br> <br>   | ST<br>ST               | Yes<br>No<br>Yes | Output Compare Fault A input (for compare channels).<br>Output Compare Fault B input (for compare channels).<br>Output Compare 1 through 8.                                        |

| INT0                                        |             | ST                     | No               | External Interrupt 0.                                                                                                                                                              |

| INT1                                        | l i         | ST                     | Yes              | External Interrupt 1.                                                                                                                                                              |

| INT2                                        | 1           | ST                     | Yes              | External Interrupt 2.                                                                                                                                                              |

| INT3                                        | I.          | ST                     | No               | External Interrupt 3.                                                                                                                                                              |

| INT4                                        | Ι           | ST                     | No               | External Interrupt 4.                                                                                                                                                              |

| RA0-RA4, RA7-RA12,<br>RA14-RA15             | I/O         | ST                     | Yes              | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                                    | I/O         | ST                     | Yes              | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                              | I/O         | ST                     | Yes              | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD1-RD6, RD8,<br>RD12-RD15                  | I/O         | ST                     | Yes              | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE0-RE1, RE8-RE9,<br>RE12-RE15              | I/O         | ST                     | Yes              | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0-RF1, RF4-RF7,<br>RF9-RF10,<br>RF12-RF13 | I/O         | ST                     | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG0-RG3,<br>RG6-RG15                        | I/O         | ST                     | Yes              | PORTG is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                                        | Ι           | ST                     | No               | Timer1 external clock input.                                                                                                                                                       |

| T2CK                                        |             | ST                     | Yes              | Timer2 external clock input.                                                                                                                                                       |

| T3CK                                        |             | ST                     | No               | Timer3 external clock input.                                                                                                                                                       |

| T4CK<br>T5CK                                |             | ST<br>ST               | No<br>No         | Timer4 external clock input.                                                                                                                                                       |

| T6CK                                        |             | ST                     | NO               | Timer5 external clock input.<br>Timer6 external clock input.                                                                                                                       |

| T7CK                                        |             | ST                     | No               | Timer7 external clock input.                                                                                                                                                       |

| T8CK                                        | l i         | ST                     | No               | Timer8 external clock input.                                                                                                                                                       |

| T9CK                                        | i           | ST                     | No               | Timer9 external clock input.                                                                                                                                                       |

| Legend: CMOS = CM<br>ST = Schmit            | tt Trigg    | mpatible<br>er input v | vith CN          | or output Analog = Analog input P = Power<br>IOS levels O = Output I = Input                                                                                                       |

| PPS = Perip                                 |             |                        |                  | TTL = TTL input buffer<br>es. For more information. see the " <b>Pin Diagrams</b> " section for pin                                                                                |

Note 1: This pin is not available on all devices. For more information, see the "Pin Diagrams" section for pin availability.

2: AVDD must be connected at all times.

|--|

| SFR<br>Name | Addr. | Bit 15 |                                        |          |         |         |         |     |           | All<br>Resets |             |        |          |          |          |          |          |      |

|-------------|-------|--------|----------------------------------------|----------|---------|---------|---------|-----|-----------|---------------|-------------|--------|----------|----------|----------|----------|----------|------|

| OC7CON1     | 093C  | _      | —                                      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _   | ENFLTB    | ENFLTA        | _           | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000 |

| OC7CON2     | 093E  | FLTMD  | FLTOUT                                 | FLTTRIEN | OCINV   |         | —       | _   | OC32      | OCTRIG        | TRIGSTAT    | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C |

| OC7RS       | 0940  |        | Output Compare 7 Secondary Register xx |          |         |         |         |     |           |               |             | xxxx   |          |          |          |          |          |      |

| OC7R        | 0942  |        | Output Compare 7 Register xx           |          |         |         |         |     |           | xxxx          |             |        |          |          |          |          |          |      |

| OC7TMR      | 0944  |        | Output Compare 7 Timer Value Register  |          |         |         |         |     | xxxx      |               |             |        |          |          |          |          |          |      |

| OC8CON1     | 0946  | _      | —                                      | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —   | ENFLTB    | ENFLTA        | _           | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000 |

| OC8CON2     | 0948  | FLTMD  | FLTOUT                                 | FLTTRIEN | OCINV   |         | —       | —   | OC32      | OCTRIG        | TRIGSTAT    | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C |

| OC8RS       | 094A  |        | Output Compare 8 Secondary Register x  |          |         |         |         |     | xxxx      |               |             |        |          |          |          |          |          |      |

| OC8R        | 094C  |        |                                        |          |         |         |         |     | Output    | Compare 8     | 8 Register  |        |          |          |          |          |          | xxxx |

| OC8TMR      | 094E  |        |                                        |          |         |         |         | Out | put Compa | are 8 Time    | Value Regis | ster   |          |          |          |          |          | xxxx |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-15: QEI1 REGISTER MAP

|             | 15.   |        | ILC IS                                                                                                 |          |          |          |          |                         |              |        |        |          |          |        |        |        |        |               |

|-------------|-------|--------|--------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|-------------------------|--------------|--------|--------|----------|----------|--------|--------|--------|--------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14                                                                                                 | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9                   | Bit 8        | Bit 7  | Bit 6  | Bit 5    | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| QEI1CON     | 01C0  | QEIEN  | REIEN - QEISIDL PIMOD2 PIMOD1 PIMOD0 IMV1 IMV0 - INTDIV2 INTDIV1 INTDIV0 CNTPOL GATEN CCM1 CCM0        |          |          |          |          |                         |              |        | 0000   |          |          |        |        |        |        |               |

| QEI1IOC     | 01C2  | QCAPEN | CAPEN FLTREN QFDIV2 QFDIV1 QFDIV0 OUTFNC1 OUTFNC0 SWPAB HOMPOL IDXPOL QEBPOL QEAPOL HOME INDEX QEB QEA |          |          |          |          |                         |              | 000x   |        |          |          |        |        |        |        |               |

| QEI1STAT    | 01C4  | —      | —                                                                                                      | PCHEQIRQ | PCHEQIEN | PCLEQIRQ | PCLEQIEN | POSOVIRQ                | POSOVIEN     | PCIIRQ | PCIIEN | VELOVIRQ | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS1CNTL    | 01C6  |        | POSCNT<15:0> 00                                                                                        |          |          |          |          |                         |              |        | 0000   |          |          |        |        |        |        |               |

| POS1CNTH    | 01C8  |        | POSCNT<31:16> 00                                                                                       |          |          |          |          |                         |              |        | 0000   |          |          |        |        |        |        |               |

| POS1HLD     | 01CA  |        | POSHLD<15:0> 000                                                                                       |          |          |          |          |                         |              |        | 0000   |          |          |        |        |        |        |               |

| VEL1CNT     | 01CC  |        | VELCNT<15:0> 000                                                                                       |          |          |          |          |                         |              |        | 0000   |          |          |        |        |        |        |               |

| INT1TMRL    | 01CE  |        | INTTMR<15:0> 0                                                                                         |          |          |          |          |                         |              | 0000   |        |          |          |        |        |        |        |               |

| INT1TMRH    | 01D0  |        | INTTMR<31:16>                                                                                          |          |          |          |          |                         |              | 0000   |        |          |          |        |        |        |        |               |

| INT1HLDL    | 01D2  |        |                                                                                                        |          |          |          |          |                         | INTHLD<15:0  | )>     |        |          |          |        |        |        |        | 0000          |

| INT1HLDH    | 01D4  |        |                                                                                                        |          |          |          |          | I                       | NTHLD<31:1   | 6>     |        |          |          |        |        |        |        | 0000          |

| INDX1CNTL   | 01D6  |        |                                                                                                        |          |          |          |          | I                       | NDXCNT<15:   | 0>     |        |          |          |        |        |        |        | 0000          |

| INDX1CNTH   | 01D8  |        |                                                                                                        |          |          |          |          | IN                      | NDXCNT<31:   | 16>    |        |          |          |        |        |        |        | 0000          |

| INDX1HLD    | 01DA  |        |                                                                                                        |          |          |          |          | I                       | NDXHLD<15:   | 0>     |        |          |          |        |        |        |        | 0000          |

| QEI1GECL    | 01DC  |        |                                                                                                        |          |          |          |          | (                       | QEIGEC<15:(  | )>     |        |          |          |        |        |        |        | 0000          |

| QEI1ICL     | 01DC  |        |                                                                                                        |          |          |          |          |                         | QEIIC<15:0>  | >      |        |          |          |        |        |        |        | 0000          |

| QEI1GECH    | 01DE  |        |                                                                                                        |          |          |          |          | (                       | QEIGEC<31:1  | 6>     |        |          |          |        |        |        |        | 0000          |

| QEI1ICH     | 01DE  |        |                                                                                                        |          |          |          |          |                         | QEIIC<31:16  | >      |        |          |          |        |        |        |        | 0000          |

| QEI1LECL    | 01E0  |        |                                                                                                        |          |          |          |          |                         | QEILEC<15:0  | )>     |        |          |          |        |        |        |        | 0000          |

| QEI1LECH    | 01E2  |        |                                                                                                        |          |          |          |          | (                       | QEILEC<31:1  | 6>     |        |          |          |        |        |        |        | 0000          |

| Lonondi     |       |        | an Deest                                                                                               |          |          |          | 4        | a la accuración da accu | a da alma al |        |        |          |          |        |        |        |        |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

bit 3

SLEEP: Wake-up from Sleep Flag bit

1 = Device was in Sleep mode

0 = Device was not in Sleep mode

bit 2

IDLE: Wake-up from Idle Flag bit

1 = Device was in Idle mode

0 = Device was not in Idle mode

0 = Device was not in Idle mode

bit 1

BOR: Brown-out Reset Flag bit

1 = A Brown-out Reset has occurred

0 = A Brown-out Reset has not occurred

## bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| R/W-0           | R/W-0                                                                                                                                                          | R/W-0                                                                                                                              | R/W-0                              | R/W-0             | R/W-0           | R/W-0          | R/W-0 |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------|-----------------|----------------|-------|--|--|--|--|

| NSTDIS          | OVAERR                                                                                                                                                         | OVBERR                                                                                                                             | COVAERR                            | COVBERR           | OVATE           | OVBTE          | COVTE |  |  |  |  |

| bit 15          | OWNERRY                                                                                                                                                        | OVBENIN                                                                                                                            | 00 WILLIN                          | OOVBENIN          | OWNE            | OVDIE          | bit 8 |  |  |  |  |

|                 |                                                                                                                                                                |                                                                                                                                    |                                    |                   |                 |                |       |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                                                          | R/W-0                                                                                                                              | R/W-0                              | R/W-0             | R/W-0           | R/W-0          | U-0   |  |  |  |  |

| SFTACERR        | DIV0ERR                                                                                                                                                        | DMACERR                                                                                                                            | MATHERR                            | ADDRERR           | STKERR          | OSCFAIL        |       |  |  |  |  |

| bit 7           |                                                                                                                                                                |                                                                                                                                    |                                    |                   |                 |                | bit ( |  |  |  |  |

| Legend:         |                                                                                                                                                                |                                                                                                                                    |                                    |                   |                 |                |       |  |  |  |  |

| R = Readable    | bit                                                                                                                                                            | W = Writable                                                                                                                       | bit                                | U = Unimplem      | ented bit, read | as '0'         |       |  |  |  |  |

| -n = Value at F | POR                                                                                                                                                            | '1' = Bit is set                                                                                                                   |                                    | '0' = Bit is clea | ired            | x = Bit is unk | nown  |  |  |  |  |

|                 |                                                                                                                                                                |                                                                                                                                    |                                    |                   |                 |                |       |  |  |  |  |

| bit 15          |                                                                                                                                                                | errupt Nesting                                                                                                                     |                                    |                   |                 |                |       |  |  |  |  |

|                 |                                                                                                                                                                | nesting is disa                                                                                                                    |                                    |                   |                 |                |       |  |  |  |  |

| L:1 4 4         | -                                                                                                                                                              | nesting is ena                                                                                                                     |                                    | -1                |                 |                |       |  |  |  |  |

| bit 14          |                                                                                                                                                                |                                                                                                                                    | Overflow Trap F<br>erflow of Accur | •                 |                 |                |       |  |  |  |  |

|                 | •                                                                                                                                                              | •                                                                                                                                  | y overflow of A                    |                   |                 |                |       |  |  |  |  |

| bit 13          | -                                                                                                                                                              |                                                                                                                                    | Overflow Trap F                    |                   |                 |                |       |  |  |  |  |

|                 | 1 = Trap was                                                                                                                                                   | s caused by ov                                                                                                                     | erflow of Accur                    | mulator B         |                 |                |       |  |  |  |  |

|                 | 0 = Trap was                                                                                                                                                   | s not caused by                                                                                                                    | y overflow of A                    | ccumulator B      |                 |                |       |  |  |  |  |

| bit 12          |                                                                                                                                                                | <b>COVAERR:</b> Accumulator A Catastrophic Overflow Trap Flag bit<br>1 = Trap was caused by catastrophic overflow of Accumulator A |                                    |                   |                 |                |       |  |  |  |  |

|                 |                                                                                                                                                                |                                                                                                                                    |                                    | flow of Accumu    |                 |                |       |  |  |  |  |

| bit 11          |                                                                                                                                                                |                                                                                                                                    | -                                  | Overflow Trap F   |                 |                |       |  |  |  |  |

|                 |                                                                                                                                                                |                                                                                                                                    |                                    | flow of Accumu    |                 |                |       |  |  |  |  |

|                 | •                                                                                                                                                              | •                                                                                                                                  | •                                  | overflow of Accu  |                 |                |       |  |  |  |  |

| bit 10          | OVATE: Accumulator A Overflow Trap Enable bit                                                                                                                  |                                                                                                                                    |                                    |                   |                 |                |       |  |  |  |  |

|                 | 1 = Trap ove<br>0 = Trap is d                                                                                                                                  | erflow of Accun<br>lisabled                                                                                                        | nulator A                          |                   |                 |                |       |  |  |  |  |

| bit 9           | OVBTE: Acc                                                                                                                                                     | cumulator B Ov                                                                                                                     | verflow Trap En                    | able bit          |                 |                |       |  |  |  |  |

|                 | 1 = Trap ove<br>0 = Trap is d                                                                                                                                  | erflow of Accun<br>lisabled                                                                                                        | ulator B                           |                   |                 |                |       |  |  |  |  |

| bit 8           | COVTE: Cat                                                                                                                                                     | tastrophic Ove                                                                                                                     | flow Trap Enal                     | ole bit           |                 |                |       |  |  |  |  |

|                 | 1 = Trap on<br>0 = Trap is d                                                                                                                                   |                                                                                                                                    | verflow of Accu                    | mulator A or B i  | s enabled       |                |       |  |  |  |  |

| bit 7           | SFTACERR: Shift Accumulator Error Status bit                                                                                                                   |                                                                                                                                    |                                    |                   |                 |                |       |  |  |  |  |

|                 | <ul> <li>1 = Math error trap was caused by an invalid accumulator shift</li> <li>0 = Math error trap was not caused by an invalid accumulator shift</li> </ul> |                                                                                                                                    |                                    |                   |                 |                |       |  |  |  |  |

| bit 6           | DIV0ERR: Divide-by-Zero Error Status bit                                                                                                                       |                                                                                                                                    |                                    |                   |                 |                |       |  |  |  |  |

|                 | <ul> <li>1 = Math error trap was caused by a divide-by-zero</li> <li>0 = Math error trap was not caused by a divide-by-zero</li> </ul>                         |                                                                                                                                    |                                    |                   |                 |                |       |  |  |  |  |

| bit 5           | DMACERR:                                                                                                                                                       | DMA Controlle                                                                                                                      | er Trap Flag bit                   |                   |                 |                |       |  |  |  |  |

|                 |                                                                                                                                                                | ntroller trap ha                                                                                                                   |                                    |                   |                 |                |       |  |  |  |  |

|                 |                                                                                                                                                                | ntroller trap ha                                                                                                                   |                                    |                   |                 |                |       |  |  |  |  |

| bit 4           |                                                                                                                                                                | Math Error Sta                                                                                                                     |                                    |                   |                 |                |       |  |  |  |  |

|                 |                                                                                                                                                                | or trap has occ<br>or trap has not                                                                                                 |                                    |                   |                 |                |       |  |  |  |  |

|                 |                                                                                                                                                                |                                                                                                                                    |                                    |                   |                 |                |       |  |  |  |  |

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| <b>REGISTER 11-9: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12</b> |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

| U-0                    | R/W-0                                                                                                                                 | R/W-0                                                | R/W-0         | R/W-0                      | R/W-0          | R/W-0              | R/W-0   |  |  |  |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------|----------------------------|----------------|--------------------|---------|--|--|--|--|--|--|

|                        | FX/VV-0                                                                                                                               | N/W-0                                                | F\/VV-U       | FLT2R<6:0>                 | N/W-U          | N/VV-0             | FV/VV-U |  |  |  |  |  |  |

| <br>bit 15             |                                                                                                                                       |                                                      |               | 1 2121(<0.02               |                |                    | bit 8   |  |  |  |  |  |  |

|                        |                                                                                                                                       |                                                      |               |                            |                |                    | DILO    |  |  |  |  |  |  |

| U-0                    | R/W-0                                                                                                                                 | R/W-0                                                | R/W-0         | R/W-0                      | R/W-0          | R/W-0              | R/W-0   |  |  |  |  |  |  |

|                        |                                                                                                                                       |                                                      |               | FLT1R<6:0>                 |                |                    |         |  |  |  |  |  |  |

| bit 7                  |                                                                                                                                       |                                                      |               |                            |                |                    | bit 0   |  |  |  |  |  |  |

|                        |                                                                                                                                       |                                                      |               |                            |                |                    |         |  |  |  |  |  |  |

| Legend:<br>R = Readabl | e hit                                                                                                                                 | W = Writable                                         | hit           | U = Unimplen               | nented hit rea | ad as 'N'          |         |  |  |  |  |  |  |

| -n = Value at POR      |                                                                                                                                       | '1' = Bit is set                                     |               | '0' = Bit is clea          |                | x = Bit is unknown |         |  |  |  |  |  |  |

|                        |                                                                                                                                       |                                                      |               |                            |                |                    |         |  |  |  |  |  |  |

| bit 15                 | Unimplemen                                                                                                                            | ted: Read as '                                       | 0'            |                            |                |                    |         |  |  |  |  |  |  |

| bit 14-8               | <b>FLT2R&lt;6:0&gt;:</b> Assign PWM Fault 2 (FLT2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |                                                      |               |                            |                |                    |         |  |  |  |  |  |  |

|                        | 1111100 <b>= I</b> r                                                                                                                  | 1111100 = Input tied to RPI124                       |               |                            |                |                    |         |  |  |  |  |  |  |

|                        | •                                                                                                                                     |                                                      |               |                            |                |                    |         |  |  |  |  |  |  |

|                        | •                                                                                                                                     |                                                      |               |                            |                |                    |         |  |  |  |  |  |  |

|                        | 0000001 = Input tied to CMP1                                                                                                          |                                                      |               |                            |                |                    |         |  |  |  |  |  |  |

|                        | 0000000 = Input tied to Vss                                                                                                           |                                                      |               |                            |                |                    |         |  |  |  |  |  |  |

| bit 7                  | Unimplemen                                                                                                                            | ted: Read as '                                       | 0'            |                            |                |                    |         |  |  |  |  |  |  |

| bit 6-0                | (see Table 11                                                                                                                         | Assign PWM I<br>-2 for input pin<br>nput tied to RPI | selection nun | ) to the Corresp<br>nbers) | onding RPn F   | Pin bits           |         |  |  |  |  |  |  |

|                        | •                                                                                                                                     |                                                      |               |                            |                |                    |         |  |  |  |  |  |  |

|                        |                                                                                                                                       | nput tied to CM<br>nput tied to Vss                  |               |                            |                |                    |         |  |  |  |  |  |  |

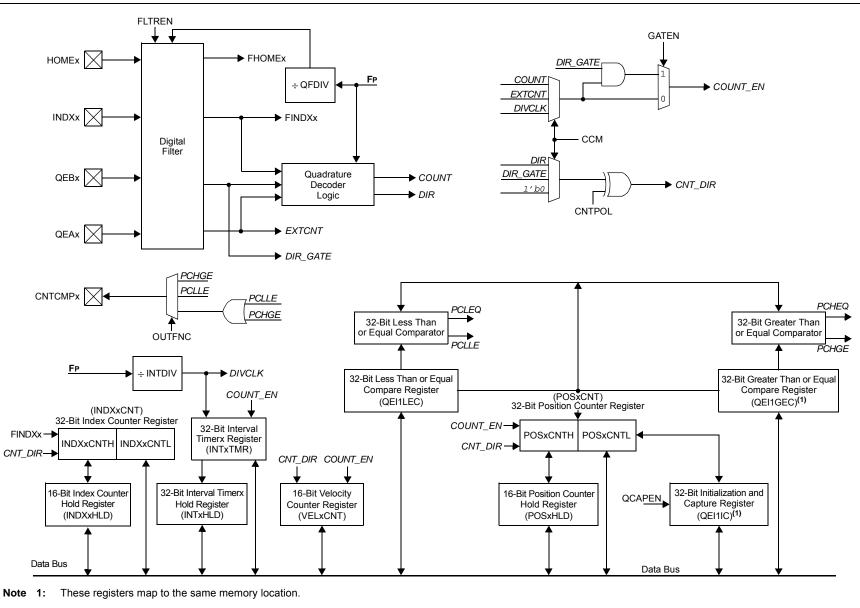

#### FIGURE 17-1: QEIX BLOCK DIAGRAM

JSPIC33EPXXXGM3XX/6XX/7XX

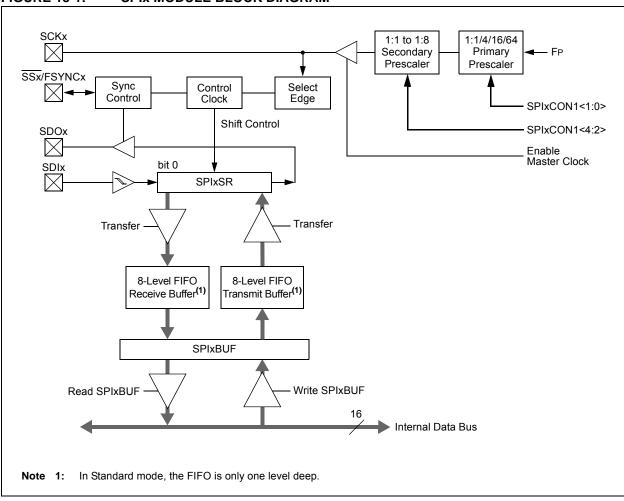

#### FIGURE 18-1: SPIX MODULE BLOCK DIAGRAM

| U-0                 | U-0                                                                                                                                                                                             | U-0                                                                                                                                                                  | R/W-0                | R/W-0                | R/W-0                | R/W-0                                  | R/W-0                            |  |  |  |  |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|----------------------------------------|----------------------------------|--|--|--|--|--|--|

| _                   |                                                                                                                                                                                                 | _                                                                                                                                                                    | DISSCK               | DISSDO               | MODE16               | SMP                                    | CKE <sup>(1)</sup>               |  |  |  |  |  |  |

| bit 15              |                                                                                                                                                                                                 | •                                                                                                                                                                    |                      |                      |                      |                                        | bit                              |  |  |  |  |  |  |

|                     |                                                                                                                                                                                                 |                                                                                                                                                                      |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

| R/W-0               | R/W-0                                                                                                                                                                                           | R/W-0                                                                                                                                                                | R/W-0                | R/W-0                | R/W-0                | R/W-0                                  | R/W-0                            |  |  |  |  |  |  |

| SSEN <sup>(2)</sup> | CKP                                                                                                                                                                                             | MSTEN                                                                                                                                                                | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup>                   | PPRE0 <sup>(3)</sup>             |  |  |  |  |  |  |

| bit 7               |                                                                                                                                                                                                 |                                                                                                                                                                      |                      |                      |                      |                                        | bit                              |  |  |  |  |  |  |

| Legend:             |                                                                                                                                                                                                 |                                                                                                                                                                      |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

| R = Readable bit    |                                                                                                                                                                                                 | W = Writable                                                                                                                                                         | bit                  | U = Unimplem         | nented bit, read     | l as '0'                               |                                  |  |  |  |  |  |  |

| -n = Value at POR   |                                                                                                                                                                                                 | '1' = Bit is set                                                                                                                                                     |                      | '0' = Bit is clea    | ared                 | x = Bit is unkr                        | iown                             |  |  |  |  |  |  |

|                     |                                                                                                                                                                                                 |                                                                                                                                                                      |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

| bit 15-13           | Unimplemer                                                                                                                                                                                      | nted: Read as '                                                                                                                                                      | 0'                   |                      |                      |                                        |                                  |  |  |  |  |  |  |

| bit 12              | DISSCK: Dis                                                                                                                                                                                     | able SCKx Pin                                                                                                                                                        | bit (SPI Maste       | er modes only)       |                      |                                        |                                  |  |  |  |  |  |  |

|                     |                                                                                                                                                                                                 | SPI clock is disa                                                                                                                                                    |                      | tions as I/O         |                      |                                        |                                  |  |  |  |  |  |  |

|                     |                                                                                                                                                                                                 | SPI clock is ena                                                                                                                                                     |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

| bit 11              |                                                                                                                                                                                                 | able SDOx Pir                                                                                                                                                        |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

|                     | <ul> <li>1 = SDOx pin is not used by the module; pin functions as I/O</li> <li>0 = SDOx pin is controlled by the module</li> </ul>                                                              |                                                                                                                                                                      |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

| bit 10              | •                                                                                                                                                                                               | ord/Byte Comm                                                                                                                                                        | -                    | ect bit              |                      |                                        |                                  |  |  |  |  |  |  |

|                     |                                                                                                                                                                                                 | <ul> <li>1 = Communication is word-wide (16 bits)</li> <li>0 = Communication is byte-wide (8 bits)</li> </ul>                                                        |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

|                     | 0 = Commun                                                                                                                                                                                      | ication is byte-                                                                                                                                                     | wide (8 bits)        |                      |                      |                                        |                                  |  |  |  |  |  |  |

| bit 9               | SMP: SPIx Data Input Sample Phase bit                                                                                                                                                           |                                                                                                                                                                      |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

|                     | Master mode                                                                                                                                                                                     |                                                                                                                                                                      |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

|                     | <ul> <li>1 = Input data is sampled at the end of data output time</li> <li>0 = Input data is sampled at the middle of data output time</li> </ul>                                               |                                                                                                                                                                      |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

|                     | <u>Slave mode:</u><br>SMP must be cleared when SPIx is used in Slave mode.                                                                                                                      |                                                                                                                                                                      |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

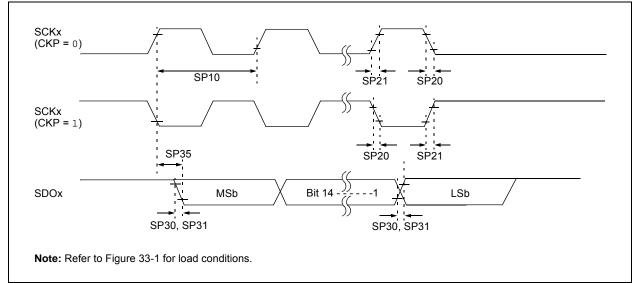

| bit 8               |                                                                                                                                                                                                 | CKE: SPIx Clock Edge Select bit <sup>(1)</sup>                                                                                                                       |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

|                     | 1 = Serial ou                                                                                                                                                                                   | tput data chang                                                                                                                                                      | jes on transitio     | on from active o     | lock state to Id     | le clock state (r<br>/e clock state (r | efer to bit 6)<br>efer to bit 6) |  |  |  |  |  |  |

| bit 7               | <ul> <li>0 = Serial output data changes on transition from Idle clock state to active clock state (refer to bit 6)</li> <li>SSEN: Slave Select Enable bit (Slave mode)<sup>(2)</sup></li> </ul> |                                                                                                                                                                      |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

|                     | $1 = \overline{SSx}$ pin is used for Slave mode                                                                                                                                                 |                                                                                                                                                                      |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

|                     | $0 = \overline{SSx}$ pin i                                                                                                                                                                      | $= \overline{SSx}$ pin is not used by the module; pin is controlled by port function                                                                                 |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

| bit 6               | CKP: Clock F                                                                                                                                                                                    | CKP: Clock Polarity Select bit                                                                                                                                       |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

|                     |                                                                                                                                                                                                 | <ul> <li>= Idle state for clock is a high level; active state is a low level</li> <li>= Idle state for clock is a low level; active state is a high level</li> </ul> |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

| bit 5               | MSTEN: Mas                                                                                                                                                                                      | MSTEN: Master Mode Enable bit                                                                                                                                        |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

|                     | 1 = Master m<br>0 = Slave mo                                                                                                                                                                    |                                                                                                                                                                      |                      |                      |                      |                                        |                                  |  |  |  |  |  |  |

|                     |                                                                                                                                                                                                 |                                                                                                                                                                      |                      | D                    |                      |                                        |                                  |  |  |  |  |  |  |

| Note 1: Th          | IE CKE DILIS NOL                                                                                                                                                                                | used in Frame                                                                                                                                                        | a SPI modes. I       | Program this bit     | to 10° for Frame     | ea SPI moaes (                         | FRMEN = 1                        |  |  |  |  |  |  |

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

**3:** Do not set both primary and secondary prescalers to the value of 1:1.

#### BUFFER 21-5: CANx MESSAGE BUFFER WORD 4

| R/W-x                             | R/W-x | R/W-x            | R/W-x        | R/W-x            | R/W-x     | R/W-x           | R/W-x |

|-----------------------------------|-------|------------------|--------------|------------------|-----------|-----------------|-------|

|                                   |       |                  | Byte         | 3<15:8>          |           |                 |       |

| bit 15                            |       |                  |              |                  |           |                 | bit 8 |

|                                   |       |                  |              |                  |           |                 |       |

| R/W-x                             | R/W-x | R/W-x            | R/W-x        | R/W-x            | R/W-x     | R/W-x           | R/W-x |

|                                   |       |                  | Byte         | 2<7:0>           |           |                 |       |

| bit 7                             |       |                  |              |                  |           |                 | bit 0 |

| Legend:                           |       |                  |              |                  |           |                 |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimpler | mented bit, rea  | id as '0' |                 |       |

| -n = Value at P                   | OR    | '1' = Bit is set |              | '0' = Bit is cle |           | x = Bit is unkı | nown  |

bit 15-8 Byte 3<15:8>: CANx Message Byte 3

bit 7-0 Byte 2<7:0>: CANx Message Byte 2

#### BUFFER 21-6: CANx MESSAGE BUFFER WORD 5

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |  |  |

|-----------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|--|--|--|

|                 |       |                  | Byte  | 5<15:8>                            |       |                    |       |  |  |  |

| bit 15          |       |                  |       |                                    |       |                    | bit 8 |  |  |  |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |  |  |

|                 |       |                  | Byte  | 4<7:0>                             |       |                    |       |  |  |  |

| bit 7           |       |                  |       |                                    |       |                    | bit 0 |  |  |  |

| Legend:         |       |                  |       |                                    |       |                    |       |  |  |  |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimplemented bit, read as '0' |       |                    |       |  |  |  |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unknown |       |  |  |  |

bit 7-0 Byte 4<7:0>: CANx Message Byte 4

## 32.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 32.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 32.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 32.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

| <b>TABLE 33-4</b> : | DC TEMPERATURE AND VOLTAGE SPECIFICATIONS |

|---------------------|-------------------------------------------|

|                     |                                           |

| DC CHARACTERISTICS |           |                                                                  | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |            |      |      |                                                         |  |

|--------------------|-----------|------------------------------------------------------------------|-------------------------------------------------------|------------|------|------|---------------------------------------------------------|--|

| Param<br>No.       | Symbol    | Characteristic                                                   | Min.                                                  | Conditions |      |      |                                                         |  |

| Operati            | ng Voltag | e                                                                |                                                       |            |      |      |                                                         |  |

| DC10               | Vdd       | Supply Voltage <sup>(3)</sup>                                    | 3.0                                                   | _          | 3.6  | V    |                                                         |  |

| DC12               | Vdr       | RAM Data Retention Voltage <sup>(2)</sup>                        | 1.95                                                  | —          |      | V    |                                                         |  |

| DC16               | VPOR      | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal | _                                                     | —          | Vss  | V    |                                                         |  |