Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT   |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | -                                                                                 |

| Data Converters            | A/D 30x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm706t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EPXXXGM3XX/ 6XX/7XX devices is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, the dsPIC33EPXXXGM3XX/ 6XX/7XX devices contain control registers for Modulo

Addressing and Bit-Reversed Addressing, and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Table 4-1.

| Register(s) Name                                  | Description                                               |

|---------------------------------------------------|-----------------------------------------------------------|

| W0 through W15                                    | Working Register Array                                    |

| ACCA, ACCB                                        | 40-Bit DSP Accumulators                                   |

| PC                                                | 23-Bit Program Counter                                    |

| SR                                                | ALU and DSP Engine Status register                        |

| SPLIM                                             | Stack Pointer Limit Value register                        |

| TBLPAG                                            | Table Memory Page Address register                        |

| DSRPAG                                            | Extended Data Space (EDS) Read Page register              |

| DSWPAG                                            | Extended Data Space (EDS) Write Page register             |

| RCOUNT                                            | REPEAT Loop Count register                                |

| DCOUNT                                            | DO Loop Count register                                    |

| DOSTARTH <sup>(1)</sup> , DOSTARTL <sup>(1)</sup> | DO Loop Start Address register (High and Low)             |

| DOENDH, DOENDL                                    | DO Loop End Address register (High and Low)               |

| CORCON                                            | Contains DSP Engine, DO Loop Control and Trap Status bits |

#### TABLE 3-1: PROGRAMMER'S MODEL REGISTER DESCRIPTIONS

**Note 1:** The DOSTARTH and DOSTARTL registers are read-only.

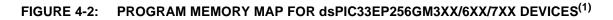

Note 1: Memory areas are not shown to scale.

2: On Reset, these bits are automatically copied into the device Configuration Shadow registers.

# 4.3 Special Function Register Maps

### TABLE 4-1: CPU CORE REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12      | Bit 11     | Bit 10 | Bit 9      | Bit 8       | Bit 7        | Bit 6  | Bit 5      | Bit 4      | Bit 3        | Bit 2       | Bit 1    | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|-------------|------------|--------|------------|-------------|--------------|--------|------------|------------|--------------|-------------|----------|-------|---------------|

| W0          | 0000  |        |        |        |             |            |        | 1          | W0 (WR      | EG)          |        |            |            |              |             | <b>I</b> |       | xxxx          |

| W1          | 0002  |        |        |        |             |            |        |            | W1          |              |        |            |            |              |             |          |       | xxxx          |

| W2          | 0004  |        |        |        |             |            |        |            | W2          |              |        |            |            |              |             |          |       | xxxx          |

| W3          | 0006  |        |        |        |             |            |        |            | W3          |              |        |            |            |              |             |          |       | xxxx          |

| W4          | 0008  |        |        |        |             |            |        |            | W4          |              |        |            |            |              |             |          |       | xxxx          |

| W5          | 000A  |        |        |        |             |            |        |            | W5          |              |        |            |            |              |             |          |       | xxxx          |

| W6          | 000C  |        |        |        |             |            |        |            | W6          |              |        |            |            |              |             |          |       | xxxx          |

| W7          | 000E  |        |        |        |             |            |        |            | W7          |              |        |            |            |              |             |          |       | xxxx          |

| W8          | 0010  |        |        |        |             |            |        |            | W8          |              |        |            |            |              |             |          |       | xxxx          |

| W9          | 0012  |        |        |        |             |            |        |            | W9          |              |        |            |            |              |             |          |       | xxxx          |

| W10         | 0014  |        |        |        |             |            |        |            | W10         |              |        |            |            |              |             |          |       | xxxx          |

| W11         | 0016  |        |        |        |             |            |        |            | W11         |              |        |            |            |              |             |          |       | xxxx          |

| W12         | 0018  |        |        |        |             |            |        |            | W12         |              |        |            |            |              |             |          |       | xxxx          |

| W13         | 001A  |        |        |        |             |            |        |            | W13         |              |        |            |            |              |             |          |       | xxxx          |

| W14         | 001C  |        |        |        |             |            |        |            | W14         |              |        |            |            |              |             |          |       | xxxx          |

| W15         | 001E  |        |        |        |             |            |        |            | W15         |              |        |            |            |              |             |          |       | xxxx          |

| SPLIM       | 0020  |        |        |        |             |            |        |            | SPLI        | N            |        |            |            |              |             |          |       | 0000          |

| ACCAL       | 0022  |        |        |        |             |            |        |            | ACCA        | L            |        |            |            |              |             |          |       | 0000          |

| ACCAH       | 0024  |        |        |        |             |            |        |            | ACCA        | .H           |        |            |            |              |             |          |       | 0000          |

| ACCAU       | 0026  |        |        | Się    | gn Extensio | n of ACCA< | 39>    |            |             |              |        |            | ACO        | CAU          |             |          |       | 0000          |

| ACCBL       | 0028  |        |        |        |             |            |        |            | ACCB        | L            |        |            |            |              |             |          |       | 0000          |

| ACCBH       | 002A  |        |        |        |             |            |        |            | ACCB        | Н            |        |            |            |              |             |          |       | 0000          |

| ACCBU       | 002C  |        |        | Się    | gn Extensio | n of ACCB< | 39>    |            |             |              |        |            | ACO        | CBU          |             |          |       | 0000          |

| PCL         | 002E  |        |        | -      |             |            | Pr     | ogram Cour | nter Low Wo | rd Register  |        |            |            |              |             |          | —     | 0000          |

| PCH         | 0030  | _      | —      | —      | _           | _          | _      | —          | —           | —            |        | Pr         | ogram Cou  | unter High V | Vord Regist | ter      |       | 0000          |

| DSRPAG      | 0032  | _      | —      | —      | —           | _          | —      |            |             |              | Data S | pace Read  | l Page Reg | gister       |             |          |       | 0001          |

| DSWPAG      | 0034  | _      | —      | —      | —           | —          | —      | —          |             |              | 0      | Data Space | Write Pag  | e Register   |             |          |       | 0001          |

| RCOUNT      | 0036  |        |        |        |             |            |        | REPE       | AT LOOP CO  | ount Registe | er     |            |            |              |             |          |       | 0000          |

| DCOUNT      | 0038  |        |        |        |             |            |        |            | DCOUNT<     | :15:0>       |        |            |            |              |             |          |       | 0000          |

| DOSTARTL    | 003A  |        |        |        |             |            |        | DOS        | TARTL<15:1  | >            |        |            |            |              |             |          | —     | 0000          |

| DOSTARTH    | 003C  | -      |        | —      | —           | —          | -      | _          | —           | _            | —      |            |            | DOSTAF       | RTH<5:0>    |          |       | 0000          |

| DOENDL      | 003E  |        |        |        |             |            |        | DO         | ENDL<15:1>  | >            |        |            |            |              |             |          | _     | 0000          |

| DOENDH      | 0040  | -      |        | —      | _           | _          | -      | —          | —           | _            | —      |            |            | DOEN         | DH<5:0>     |          |       | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000689D-page 46

| IABLE 4         | +-/.   | FIGK    | EGIST   |         |         |         |         |         |         |             |         |         |         |        |           |         |         |               |

|-----------------|--------|---------|---------|---------|---------|---------|---------|---------|---------|-------------|---------|---------|---------|--------|-----------|---------|---------|---------------|

| SFR<br>Name     | Addr.  | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7       | Bit 6   | Bit 5   | Bit 4   | Bit 3  | Bit 2     | Bit 1   | Bit 0   | All<br>Resets |

| PTGCST          | 0AC0   | PTGEN   | _       | PTGSIDL | PTGTOGL | _       | PTGSWT  | PTGSSEN | PTGIVIS | PTGSTRT     | PTGWDTO | _       | —       | —      | —         | PTGITM1 | PTGITM0 | 0000          |

| PTGCON          | 0AC2   | PTGCLK2 | PTGCLK1 | PTGCLK0 | PTGDIV4 | PTGDIV3 | PTGDIV2 | PTGDIV1 | PTGDIV0 | PTGPWD3     | PTGPWD2 | PTGPWD1 | PTGPWD0 | _      | PTGWDT2   | PTGWDT1 | PTGWDT0 | 0000          |

| PTGBTE          | 0AC4   | ADCTS4  | ADCTS3  | ADCTS2  | ADCTS1  | IC4TSS  | IC3TSS  | IC2TSS  | IC1TSS  | OC4CS       | OC3CS   | OC2CS   | OC1CS   | OC4TSS | OC3TSS    | OC2TSS  | OC1TSS  | 0000          |

| PTGHOLD         | 0AC6   |         |         |         | •       |         |         | •       | PTGł    | HOLD<15:0>  |         | •       |         | •      | •         |         |         | 0000          |

| PTGT0LIM        | 0AC8   |         |         |         |         |         |         |         | PTG     | OLIM<15:0>  |         |         |         |        |           |         |         | 0000          |

| PTGT1LIM        | 0ACA   |         |         |         |         |         |         |         | PTG     | TLIM<15:0>  |         |         |         |        |           |         |         | 0000          |

| PTGSDLIM        | 0ACC   |         |         |         |         |         |         |         | PTGS    | SDLIM<15:0> |         |         |         |        |           |         |         | 0000          |

| <b>PTGC0LIM</b> | 0ACE   |         |         |         |         |         |         |         | PTGC    | COLIM<15:0> |         |         |         |        |           |         |         | 0000          |

| PTGC1LIM        | 0AD0   |         |         |         |         |         |         |         | PTGC    | C1LIM<15:0> |         |         |         |        |           |         |         | 0000          |

| PTGADJ          | 0AD2   |         |         |         |         |         |         |         | PTG     | ADJ<15:0>   |         |         |         |        |           |         |         | 0000          |

| PTGL0           | 0AD4   |         |         |         |         |         |         |         | PT      | GL0<15:0>   |         |         |         |        |           |         |         | 0000          |

| PTGQPTR         | 0AD6   |         |         | _       | —       |         |         | _       | —       | —           | —       | —       |         | F      | PTGQPTR<4 | :0>     |         | 0000          |

| PTGQUE0         | 0AD8   |         |         |         | STEP1   | <7:0>   |         |         |         |             |         |         | STEP0   | <7:0>  |           |         |         | 0000          |

| PTGQUE1         | 0ADA   |         |         |         | STEP3   | <7:0>   |         |         |         |             |         |         | STEP2   | <7:0>  |           |         |         | 0000          |

| PTGQUE2         | 0ADC   |         |         |         | STEP5   | <7:0>   |         |         |         |             |         |         | STEP4   | <7:0>  |           |         |         | 0000          |

| PTGQUE3         | 0ADE   |         |         |         | STEP7   | <7:0>   |         |         |         |             |         |         | STEP6   | <7:0>  |           |         |         | 0000          |

| PTGQUE4         | 0AE0   |         |         |         | STEP9   | <7:0>   |         |         |         |             |         |         | STEP8   | <7:0>  |           |         |         | 0000          |

| PTGQUE5         | 0AE2   |         |         |         | STEP11  | <7:0>   |         |         |         |             |         |         | STEP10  | <7:0>  |           |         |         | 0000          |

| PTGQUE6         | 0AE4   |         |         |         | STEP13  | <7:0>   |         |         |         |             |         |         | STEP12  | 2<7:0> |           |         |         | 0000          |

| PTGQUE7         | 0AE6   |         |         |         | STEP15  | i<7:0>  |         |         |         |             |         |         | STEP14  | <7:0>  |           |         |         | 0000          |

| PTGQUE8         | 0x0AE8 |         |         |         | STEP17  | <7:0>   |         |         |         |             |         |         | STEP16  | 6<7:0> |           |         |         | 0000          |

| PTGQUE9         | 0x0AEA |         |         |         | STEP19  | <7:0>   |         |         |         |             |         |         | STEP18  | <7:0>  |           |         |         | 0000          |

| PTGQUE10        | 0x0AEC |         |         |         | STEP21  | <7:0>   |         |         |         |             |         |         | STEP20  | <7:0>  |           |         |         | 0000          |

| PTGQUE11        | 0x0AEE |         |         |         | STEP23  | <7:0>   |         |         |         |             |         |         | STEP22  | 2<7:0> |           |         |         | 0000          |

| PTGQUE12        | 0x0AF0 |         |         |         | STEP25  | <7:0>   |         |         |         |             |         |         | STEP24  | <7:0>  |           |         |         | 0000          |

| PTGQUE13        | 0x0AF2 |         |         |         | STEP27  | <7:0>   |         |         |         |             |         |         | STEP26  | 6<7:0> |           |         |         | 0000          |

| PTGQUE14        | 0x0AF4 |         |         |         | STEP29  | <7:0>   |         |         |         |             |         |         | STEP28  | <7:0>  |           |         |         | 0000          |

| PTGQUE15        | 0x0AF6 |         |         |         | STEP31  | <7:0>   |         |         |         |             |         |         | STEP30  | <7:0>  |           |         |         | 0000          |

#### TABLE 4-7: PTG REGISTER MAP

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-61: PORTG REGISTER MAP FOR dsPIC33EPXXXGM310/710 DEVICES

|          | • • • |        | • • • • • • • |        |        |         |        |       |                |       |       |       |       |       |        |        |       |               |

|----------|-------|--------|---------------|--------|--------|---------|--------|-------|----------------|-------|-------|-------|-------|-------|--------|--------|-------|---------------|

| SFR Name | Addr. | Bit 15 | Bit 14        | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9 | Bit 8          | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

| TRISG    | 0E60  |        |               |        |        | TRISG<1 | 5:6>   |       |                |       |       | -     | —     |       | TRISC  | 6<3:0> |       | 03C0          |

| PORTG    | 0E62  |        |               |        |        | RG<15:  | 6>     |       |                |       |       | _     | _     |       | RG<    | 3:0>   |       | xxxx          |

| LATG     | 0E64  |        |               |        |        | LATG<15 | 5:6>   |       |                |       |       | _     | _     |       | LATG   | <3:0>  |       | xxxx          |

| ODCG     | 0E66  |        |               |        |        | ODCG<1  | 5:6>   |       |                |       |       | —     | _     |       | ODCO   | G<3:0> |       | 0000          |

| CNENG    | 0E68  |        |               |        |        | CNIEG<1 | 5:6>   |       |                |       |       | —     | _     |       | CNIEC  | G<3:0> |       | 0000          |

| CNPUG    | 0E6A  |        |               |        |        | CNPUG<1 | 15:6>  |       |                |       |       | —     | _     |       | CNPU   | G<3:0> |       | 0000          |

| CNPDG    | 0E6C  |        |               |        |        | CNPDG<1 | 15:6>  |       |                |       |       | —     | _     |       | CNPD   | G<3:0> |       | 0000          |

| ANSELG   | 0E6E  | ANSG15 |               | _      | _      |         |        | ANSG< | 11:6>          |       |       | _     | _     | ANSG  | i<3:2> | _      |       | 0000          |

|          |       |        |               |        |        |         |        |       | and the second |       |       | •     | •     | •     |        | •      |       | •             |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-62: PORTG REGISTER MAP FOR dsPIC33EPXXXGM306/706 DEVICES

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISG    | 0E60  | _      | _      | _      | _      | _      |        |       | TRISC | 6<9:6> |       |       |       | —     | —     |       | —     | 03C0          |

| PORTG    | 0E62  | _      | _      | _      | _      | _      | _      |       | RG<   | 9:6>   |       | _     | _     | _     | _     | _     | _     | xxxx          |

| LATG     | 0E64  | —      | —      | _      | _      | —      | _      |       | LATG  | <9:6>  |       |       |       | —     | —     |       | —     | xxxx          |

| ODCG     | 0E66  | _      | _      | _      | _      | _      | _      |       | ODCO  | 6<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNENG    | 0E68  | _      | _      | _      | _      | _      | _      |       | CNIEC | G<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNPUG    | 0E6A  | —      | —      | _      | _      | —      | _      |       | CNPU  | G<9:6> |       |       |       | —     | —     |       | —     | 0000          |

| CNPDG    | 0E6C  | _      | _      | _      | _      | _      | _      |       | CNPD  | G<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| ANSELG   | 0E6E  | —      | _      | _      | _      | _      | _      |       | ANSO  | 6<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-63: PAD CONFIGURATION REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|----------|--------|---------------|

| PADCFG1   | 0EFE  | _      | _      |        | _      |        | _      | _     | _     | _     |       | _     | _     | _     | _     | RTSECSEL | PMPTTL | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0             | U-0                 | U-0                                | U-0   | U-0              | U-0              | U-0             | U-0   |

|-----------------|---------------------|------------------------------------|-------|------------------|------------------|-----------------|-------|

| —               | —                   | —                                  | —     | —                | —                | —               | —     |

| bit 15          |                     |                                    |       |                  |                  |                 | bit 8 |

|                 |                     |                                    |       |                  |                  |                 |       |

| U-0             | R/W-0               | R/W-0                              | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| —               |                     |                                    |       | INT2R<6:0>       |                  |                 |       |

| bit 7           |                     |                                    |       |                  |                  |                 | bit 0 |

|                 |                     |                                    |       |                  |                  |                 |       |

| Legend:         |                     |                                    |       |                  |                  |                 |       |

| R = Readable    | bit                 | W = Writable                       | bit   | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value at I | POR                 | '1' = Bit is set                   |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                 |                     |                                    |       |                  |                  |                 |       |

| bit 15-7        | Unimplemen          | ted: Read as '                     | כ'    |                  |                  |                 |       |

| bit 6-0         |                     | Assign Externa<br>-2 for input pin |       |                  | orresponding RI  | Pn Pin bits     |       |

|                 | 1111100 <b>= In</b> | put tied to RPI                    | 124   |                  |                  |                 |       |

|                 | •                   |                                    |       |                  |                  |                 |       |

|                 | •                   |                                    |       |                  |                  |                 |       |

|                 |                     | put tied to CMI<br>put tied to Vss |       |                  |                  |                 |       |

#### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

## REGISTER 11-29: RPINR41: PERIPHERAL PIN SELECT INPUT REGISTER 41

| U-0                 | U-0          | U-0                                  | U-0         | U-0              | U-0               | U-0             | U-0            |

|---------------------|--------------|--------------------------------------|-------------|------------------|-------------------|-----------------|----------------|

| _                   | —            | —                                    | _           | _                | —                 | —               | —              |

| bit 15              |              |                                      |             |                  |                   |                 | bit 8          |

|                     |              |                                      |             |                  |                   |                 |                |

| U-0                 | R/W-0        | R/W-0                                | R/W-0       | R/W-0            | R/W-0             | R/W-0           | R/W-0          |

| _                   |              |                                      |             | DTCMP6R<6:       | 0>                |                 |                |

| bit 7               |              |                                      |             |                  |                   |                 | bit 0          |

|                     |              |                                      |             |                  |                   |                 |                |

| Legend:             |              |                                      |             |                  |                   |                 |                |

| R = Readabl         | e bit        | W = Writable                         | bit         | U = Unimpler     | mented bit, read  | as '0'          |                |

| -n = Value at       | POR          | '1' = Bit is set                     |             | '0' = Bit is cle | ared              | x = Bit is unkr | nown           |

| bit 15-7<br>bit 6-0 | DTCMP6R<6    |                                      | M Dead-Time |                  | on Input 6 to the | Corresponding   | g RPn Pin bits |

|                     | -            | -2 for input pin<br>nput tied to RPI |             | ibers)           |                   |                 |                |

|                     | 0000001 = lr | put tied to CMI                      | P1          |                  |                   |                 |                |

0000000 = Input tied to Vss

NOTES:

| R/W-0               | R/W-0                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                    | U-0                                                                            | U-0                     | U-0                    |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------|------------------------|

| TRGDIV3             | TRGDIV2                                                                                                                                                                                                                                                      | TRGDIV1                                                                                                                                                                                                                                                                                                                                                                                                                         | TRGDIV0                                                                                                                                                                                                                                                                                    |                                                                                                                                        | _                                                                              |                         | _                      |

| bit 15              |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                                |                         | bit                    |

| U-0                 | U-0                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                  | R/W-0                                                                          | R/W-0                   | R/W-0                  |

| _                   |                                                                                                                                                                                                                                                              | TRGSTRT5 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                         | TRGSTRT5 <sup>(1)</sup>                                                                                                                                                                                                                                                                    | TRGSTRT5 <sup>(1)</sup>                                                                                                                | TRGSTRT5 <sup>(1)</sup>                                                        | TRGSTRT5 <sup>(1)</sup> | TRGSTRT5 <sup>(1</sup> |

| bit 7               |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                                |                         | bit                    |

| Legend:             |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                                |                         |                        |

| R = Readabl         | e bit                                                                                                                                                                                                                                                        | W = Writable I                                                                                                                                                                                                                                                                                                                                                                                                                  | bit                                                                                                                                                                                                                                                                                        | U = Unimplem                                                                                                                           | ented bit, read                                                                | as '0'                  |                        |

| -n = Value at       | POR                                                                                                                                                                                                                                                          | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                            | '0' = Bit is clea                                                                                                                      | ared                                                                           | x = Bit is unkno        | own                    |

|                     |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                                |                         |                        |

| bit 15-12           | 1111 = Trigg<br>1110 = Trigg<br>1101 = Trigg<br>1001 = Trigg<br>1010 = Trigg<br>1001 = Trigg<br>1000 = Trigg<br>0111 = Trigg<br>0110 = Trigg<br>0101 = Trigg<br>0101 = Trigg<br>0011 = Trigg<br>0010 = Trigg<br>0001 = Trigg<br>0001 = Trigg<br>0000 = Trigg | >: Trigger # Ou<br>er output for ev<br>er output for ev | ery 16th trigge<br>ery 15th trigge<br>ery 15th trigge<br>ery 13th trigge<br>ery 12th trigge<br>ery 12th trigge<br>ery 10th trigger<br>ery 9th trigger<br>ery 8th trigger<br>ery 6th trigger<br>ery 5th trigger<br>ery 5th trigger<br>ery 3rd trigger<br>ery 2nd trigger<br>ery trigger eve | r event<br>r event<br>r event<br>r event<br>r event<br>r event<br>event<br>event<br>event<br>event<br>event<br>event<br>event<br>event |                                                                                |                         |                        |

| bit 11-6<br>bit 5-0 | TRGSTRT<5<br>111111 = Wa                                                                                                                                                                                                                                     | ait 63 PWM cyc                                                                                                                                                                                                                                                                                                                                                                                                                  | stscaler Start E<br>les before gen<br>es before gene                                                                                                                                                                                                                                       | rating the first t                                                                                                                     | its <sup>(1)</sup><br>trigger event af<br>rigger event afte<br>gger event afte | er the module is        | s enabled              |

#### REGISTER 16-18: TRGCONx: PWMx TRIGGER CONTROL REGISTER

# REGISTER 17-1: QEIXCON: QEIX CONTROL REGISTER (CONTINUED)

| bit 6-4 | <b>INTDIV&lt;2:0&gt;:</b> Timer Input Clock Prescale Select bits (interval timer, main timer (position counter), velocity counter and index counter internal clock divider select) <sup>(3)</sup>                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 111 = 1:128 prescale value<br>110 = 1:64 prescale value                                                                                                                                                                                                                                                                      |

|         | 101 = 1:32 prescale value<br>100 = 1:16 prescale value<br>011 = 1:8 prescale value                                                                                                                                                                                                                                           |

|         | 010 = 1:4 prescale value<br>001 = 1:2 prescale value<br>000 = 1:1 prescale value                                                                                                                                                                                                                                             |

| bit 3   | CNTPOL: Position and Index Counter/Timer Direction Select bit                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = Counter direction is negative unless modified by external up/down signal</li> <li>0 = Counter direction is positive unless modified by external up/down signal</li> </ul>                                                                                                                                       |

| bit 2   | GATEN: External Count Gate Enable bit                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = External gate signal controls position counter operation</li> <li>0 = External gate signal does not affect position counter/timer operation</li> </ul>                                                                                                                                                          |

| bit 1-0 | CCM<1:0>: Counter Control Mode Selection bits                                                                                                                                                                                                                                                                                |

|         | <ul> <li>11 = Internal Timer mode with optional external count is selected</li> <li>10 = External clock count with optional external count is selected</li> <li>01 = External clock count with external up/down direction is selected</li> <li>00 = Quadrature Encoder Interface (x4 mode) Count mode is selected</li> </ul> |

| Note 1: | When CCM<1:0> = 10 or CCM<1:0> = 11, all of the QEI counters operate as timers and the PIMOD<2:0> bits are ignored.                                                                                                                                                                                                          |

- 2: When CCM<1:0> = 00, and QEAx and QEBx values match the Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

- 4: The match value applies to the A and B inputs after the swap and polarity bits have been applied.

# 21.3 CAN Control Registers

### REGISTER 21-1: CxCTRL1: CANx CONTROL REGISTER 1

| U-0             | U-0        | R/W-0            | R/W-0 | R/W-0            | R/W-1            | R/W-0           | R/W-0  |

|-----------------|------------|------------------|-------|------------------|------------------|-----------------|--------|

| —               | —          | CSIDL            | ABAT  | CANCKS           | REQOP2           | REQOP1          | REQOP0 |

| bit 15          |            |                  |       |                  |                  |                 | bit 8  |

|                 |            |                  |       |                  |                  |                 |        |

| R-1             | R-0        | R-0              | U-0   | R/W-0            | U-0              | U-0             | R/W-0  |

| OPMODE2         | OPMODE1    | OPMODE0          | _     | CANCAP           | —                |                 | WIN    |

| bit 7           | •          |                  |       | •                |                  |                 | bit 0  |

|                 |            |                  |       |                  |                  |                 |        |

| Legend:         |            |                  |       |                  |                  |                 |        |

| R = Readable I  | bit        | W = Writable b   | pit   | U = Unimpler     | nented bit, read | l as '0'        |        |

| -n = Value at P | OR         | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

|                 |            |                  |       |                  |                  |                 |        |

| bit 15-14       | Unimplemen | ted: Read as '0  | )'    |                  |                  |                 |        |

|          | 1                                                                 |

|----------|-------------------------------------------------------------------|

| bit 13   | CSIDL: CANx Stop in Idle Mode bit                                 |

|          | 1 = Discontinues module operation when device enters Idle mode    |

|          | 0 = Continues module operation in Idle mode                       |

| bit 12   | ABAT: Abort All Pending Transmissions bit                         |

|          | 1 = Signals all transmit buffers to abort transmission            |

|          | 0 = Module will clear this bit when all transmissions are aborted |

| bit 11   | CANCKS: CANx Module Clock (FCAN) Source Select bit                |

|          | 1 = FCAN is equal to 2 * FP                                       |

|          | 0 = FCAN is equal to FP                                           |

| bit 10-8 | REQOP<2:0>: Request Operation Mode bits                           |

|          | 111 = Set Listen All Messages mode                                |

|          | 110 = Reserved<br>101 = Reserved                                  |

|          | 100 = Set Configuration mode                                      |

|          | 011 = Set Listen Only mode                                        |

|          | 010 = Set Loopback mode                                           |

|          | 001 = Set Disable mode                                            |

|          | 000 = Set Normal Operation mode                                   |

| bit 7-5  | OPMODE<2:0>: Operation Mode bits                                  |

|          | 111 = Module is in Listen All Messages mode                       |

|          | 110 = Reserved<br>101 = Reserved                                  |

|          | 100 = Module is in Configuration mode                             |

|          | 011 = Module is in Listen Only mode                               |

|          | 010 = Module is in Loopback mode                                  |

|          | 001 = Module is in Disable mode                                   |

|          | 000 = Module is in Normal Operation mode                          |

| bit 4    | Unimplemented: Read as '0'                                        |

| bit 3    | CANCAP: CANx Message Receive Timer Capture Event Enable bit       |

|          | 1 = Enables input capture based on CAN message receive            |

|          | 0 = Disables CAN capture                                          |

| bit 2-1  | Unimplemented: Read as '0'                                        |

| bit 0    | WIN: SFR Map Window Select bit                                    |

|          | 1 = Uses filter window                                            |

|          | 0 = Uses buffer window                                            |

# REGISTER 21-11: CxFEN1: CANx ACCEPTANCE FILTER ENABLE REGISTER 1

| R/W-1           | R/W-1 | R/W-1            | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | FLTE  | N<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-1           | R/W-1 | R/W-1            | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|                 |       |                  | FLTE  | N<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | pit   | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n

0 = Disables Filter n

#### REGISTER 21-12: CxBUFPNT1: CANx FILTERS 0-3 BUFFER POINTER REGISTER 1

| R/W-0                             | R/W-0                                                                                              | R/W-0                                                                                                                              | R/W-0                                                                                                     | R/W-0                                              | R/W-0            | R/W-0                       | R/W-0 |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|-----------------------------|-------|--|--|

| F3BP3                             | F3BP2                                                                                              | F3BP1                                                                                                                              | F3BP0                                                                                                     | F2BP3                                              | F2BP2            | F2BP1                       | F2BP0 |  |  |

| bit 15                            | •                                                                                                  |                                                                                                                                    |                                                                                                           |                                                    |                  |                             | bit 8 |  |  |

| R/W-0                             | R/W-0                                                                                              | R/W-0                                                                                                                              | R/W-0                                                                                                     | R/W-0                                              | R/W-0            | R/W-0                       | R/W-0 |  |  |

| F1BP3                             | F1BP2                                                                                              | F1BP1                                                                                                                              | F1BP0                                                                                                     | F0BP3                                              | F0BP2            | F0BP1                       | F0BP0 |  |  |

| bit 7                             |                                                                                                    |                                                                                                                                    |                                                                                                           |                                                    |                  |                             | bit ( |  |  |

|                                   |                                                                                                    |                                                                                                                                    |                                                                                                           |                                                    |                  |                             |       |  |  |

| Legend:                           |                                                                                                    |                                                                                                                                    |                                                                                                           |                                                    |                  |                             |       |  |  |

| R = Readable bit W = Writable bit |                                                                                                    |                                                                                                                                    |                                                                                                           | U = Unimplemented bit, read as '0'                 |                  |                             |       |  |  |

| R = Readable                      | e bit                                                                                              | W = Writable                                                                                                                       | bit                                                                                                       | U = Unimpler                                       | mented bit, read | d as '0'                    |       |  |  |

| R = Readable<br>-n = Value at     |                                                                                                    | W = Writable<br>'1' = Bit is set                                                                                                   |                                                                                                           | 0' = Unimpler<br>0' = Bit is cle                   | ,                | t as '0'<br>x = Bit is unkr | nown  |  |  |

|                                   |                                                                                                    |                                                                                                                                    |                                                                                                           |                                                    | ,                |                             | iown  |  |  |

| -n = Value at                     | POR                                                                                                |                                                                                                                                    | t                                                                                                         | ʻ0' = Bit is cle                                   | ,                |                             | iown  |  |  |

| -n = Value at                     | POR<br><b>F3BP&lt;3:0&gt;</b> :                                                                    | '1' = Bit is set                                                                                                                   | t<br>k for Filter 3 b                                                                                     | ʻ0' = Bit is cle                                   | ,                |                             | nown  |  |  |

| -n = Value at                     | POR<br><b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter                                                    | '1' = Bit is set<br>RX Buffer Mas                                                                                                  | k for Filter 3 b                                                                                          | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | iown  |  |  |

| -n = Value at                     | POR<br><b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter                                                    | '1' = Bit is set<br>RX Buffer Mas<br>hits received in                                                                              | k for Filter 3 b                                                                                          | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | iown  |  |  |

|                                   | POR<br><b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter                                                    | '1' = Bit is set<br>RX Buffer Mas<br>hits received in                                                                              | k for Filter 3 b                                                                                          | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | nown  |  |  |

| -n = Value at                     | POR<br><b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter                                                    | '1' = Bit is set<br>RX Buffer Mas<br>hits received in                                                                              | k for Filter 3 b                                                                                          | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | nown  |  |  |

| -n = Value at                     | POR<br><b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter<br>1110 = Filter<br>0001 = Filter                  | '1' = Bit is set<br>RX Buffer Mas<br>hits received in                                                                              | k for Filter 3 b<br>n RX FIFO bu<br>n RX Buffer 14<br>n RX Buffer 1                                       | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | nown  |  |  |

| -n = Value at                     | POR<br><b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter<br>1110 = Filter<br>0001 = Filter<br>0000 = Filter | '1' = Bit is set<br>RX Buffer Mas<br>hits received in<br>hits received in<br>hits received in<br>hits received in                  | k for Filter 3 b<br>n RX FIFO bur<br>n RX Buffer 14<br>n RX Buffer 1<br>n RX Buffer 0                     | ʻ0' = Bit is cle<br>its<br>iffer                   | ,                | x = Bit is unkr             | iown  |  |  |

| -n = Value at<br>bit 15-12        | POR<br>F3BP<3:0>:<br>1111 = Filter<br>1110 = Filter                                                | '1' = Bit is set<br>RX Buffer Mas<br>hits received in<br>hits received in<br>hits received in<br>hits received in<br>RX Buffer Mas | k for Filter 3 b<br>n RX FIFO bur<br>n RX Buffer 14<br>n RX Buffer 1<br>n RX Buffer 0<br>k for Filter 2 b | ʻ0' = Bit is cle<br>its<br>ffer<br>its (same value | ared             | x = Bit is unkr             | iown  |  |  |

| R/W-x         | R/W-x                     | R/W-x                                      | R/W-x        | R/W-x            | R/W-x            | R/W-x           | R/W-x |  |

|---------------|---------------------------|--------------------------------------------|--------------|------------------|------------------|-----------------|-------|--|

| EID5          | EID4                      | EID3                                       | EID2         | EID1             | EID0             | RTR             | RB1   |  |

| bit 15        |                           |                                            |              |                  |                  |                 | bit 8 |  |

|               |                           |                                            |              |                  |                  |                 |       |  |

| U-x           | U-x                       | U-x                                        | R/W-x        | R/W-x            | R/W-x            | R/W-x           | R/W-x |  |

| —             | —                         | —                                          | RB0          | DLC3             | DLC2             | DLC1            | DLC0  |  |

| bit 7         |                           |                                            |              |                  |                  |                 | bit 0 |  |

|               |                           |                                            |              |                  |                  |                 |       |  |

| Legend:       |                           |                                            |              |                  |                  |                 |       |  |

| R = Readabl   |                           | W = Writable                               |              | •                | mented bit, read |                 |       |  |

| -n = Value at | t POR                     | '1' = Bit is set                           |              | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |

|               |                           |                                            |              |                  |                  |                 |       |  |

| bit 15-10     | EID<5:0>: E               | xtended Identifi                           | er bits      |                  |                  |                 |       |  |

| bit 9         | RTR: Remot                | e Transmission                             | Request bit  |                  |                  |                 |       |  |

|               | When IDE =                |                                            |              |                  |                  |                 |       |  |

|               |                           | = Message will request remote transmission |              |                  |                  |                 |       |  |

|               | 0 = Normal n              | -                                          |              |                  |                  |                 |       |  |

|               | When IDE =<br>The RTR bit |                                            |              |                  |                  |                 |       |  |

| bit 8         | RB1: Reserv               | -                                          |              |                  |                  |                 |       |  |

|               | User must se              | et this bit to '0' p                       | er CAN proto | ocol.            |                  |                 |       |  |

| bit 7-5       | Unimplemer                | nted: Read as '                            | 0'           |                  |                  |                 |       |  |

| bit 4         | RB0: Reserv               | ed Bit 0                                   |              |                  |                  |                 |       |  |

|               | User must se              | et this bit to '0' p                       | er CAN proto | ocol.            |                  |                 |       |  |

|               |                           | -                                          |              |                  |                  |                 |       |  |

#### BUFFER 21-3: CANx MESSAGE BUFFER WORD 2

| bit 3-0 | DLC<3:0>: Data Length Code bits |

|---------|---------------------------------|

|         | Dectore Data Longin Code Dite   |

#### BUFFER 21-4: CANx MESSAGE BUFFER WORD 3

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|

|                                   |       |                  | Byte  | 1<15:8>                            |       |                 |       |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |

|                                   |       |                  | Byte  | 0<7:0>                             |       |                 |       |

| bit 7                             |       |                  |       |                                    |       |                 | bit 0 |

| Logondi                           |       |                  |       |                                    |       |                 |       |

| Legend:                           |       |                  |       |                                    |       |                 |       |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at PC                  | )R    | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |

bit 15-8 Byte 1<15:8>: CANx Message Byte 1

bit 7-0 Byte 0<7:0>: CANx Message Byte 0

### REGISTER 25-1: PTGCST: PTG CONTROL/STATUS REGISTER (CONTINUED)

- bit 1-0 PTGITM<1:0>: PTG Input Trigger Command Operating Mode bits<sup>(1)</sup>

- 11 = Single level detect with step delay is not executed on exit of command (regardless of PTGCTRL command)

- 10 = Single level detect with step delay is executed on exit of command

- 01 = Continuous edge detect with step delay is not executed on exit of command (regardless of PTGCTRL command)

- 00 = Continuous edge detect with step delay is executed on exit of command

- Note 1: These bits apply to the PTGWHI and PTGWLO commands only.

- **2:** This bit is only used with the PTGCTRL Step command software trigger option.

# REGISTER 27-9: ALRMVAL (WHEN ALRMPTR<1:0> = 01): ALARM WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-----|-------|-------|-------|

| —      | _   | —   | —   | —   | WDAY2 | WDAY1 | WDAY0 |

| bit 15 |     |     |     |     |       |       | bit 8 |

|        |     |     |     |     |       |       |       |

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 10-8 **WDAY<2:0>:** Binary Coded Decimal Value of Weekday Digit bits Contains a value from 0 to 6.

bit 7-6 Unimplemented: Read as '0'

- bit 5-4 **HRTEN<1:0>:** Binary Coded Decimal Value of Hour's Tens Digit bits Contains a value from 0 to 2.

- bit 3-0 **HRONE<3:0>:** Binary Coded Decimal Value of Hour's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

# 28.1 PMP Control Registers

# REGISTER 28-1: PMCON: PARALLEL MASTER PORT CONTROL REGISTER<sup>(3)</sup>