Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm710-e-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IADL        | - <del>-</del> -J | . "    |         |         |         |        | LOISIL     |            | OK USFI    | CJJEFA  |                       |                       |                       | TINULD  | )       |         |         |               |

|-------------|-------------------|--------|---------|---------|---------|--------|------------|------------|------------|---------|-----------------------|-----------------------|-----------------------|---------|---------|---------|---------|---------------|

| SFR<br>Name | Addr.             | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10     | Bit 9      | Bit 8      | Bit 7   | Bit 6                 | Bit 5                 | Bit 4                 | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

| IPC11       | 0856              | _      | T6IP2   | T6IP1   | T6IP0   | —      | —          | _          | —          | _       | PMPIP2 <sup>(1)</sup> | PMPIP1 <sup>(1)</sup> | PMPIP0 <sup>(1)</sup> | —       | OC8IP2  | OC8IP1  | OC8IP0  | 4444          |

| IPC12       | 0858              | _      | T8IP2   | T8IP1   | T8IP0   | _      | MI2C2IP2   | MI2C2IP1   | MI2C2IP0   | _       | SI2C2IP2              | SI2C2IP1              | SI2C2IP0              | _       | T7IP2   | T7IP1   | T7IP0   | 4444          |

| IPC13       | 085A              | _      | _       | _       | _       | -      | INT4IP2    | INT4IP1    | INT4IP0    | -       | INT3IP2               | INT3IP1               | INT3IP0               | _       | T9IP2   | T9IP1   | T9IP0   | 4444          |

| IPC14       | 085C              | _      | DCIEIP2 | DCIEIP1 | DCIEIP0 | _      | QEI1IP2    | QEI1IP2    | QEI1IP0    | _       | PCEPIP2               | PCEPIP1               | PCEPIP0               | _       | _       | _       | _       | 4444          |

| IPC15       | 085E              | _      | FLT1IP2 | FLT1IP1 | FLT1IP0 |        | RTCCIP2(2) | RTCCIP1(2) | RTCCIP0(2) |         |                       | _                     | _                     | _       | DCIIP2  | DCIIP1  | DCIIP0  | 0404          |

| IPC16       | 0860              | _      | CRCIP2  | CRCIP1  | CRCIP0  |        | U2EIP2     | U2EIP1     | U2EIP0     |         | U1EIP2                | U1EIP1                | U1EIP0                | _       | FLT2IP2 | FLT2IP1 | FLT2IP0 | 4440          |

| IPC18       | 0864              | _      | C2TXIP2 | C2TXIP1 | C2TXIP0 |        | FLT3IP2    | FLT3IP1    | FLT3IP0    |         | PCESIP2               | PCESIP1               | PCESIP0               | _       | _       |         | _       | 4040          |

| IPC19       | 0866              | _      | _       |         | _       |        | _          | -          | _          |         | CTMUIP2               | CTMUIP1               | CTMUIP0               | _       | FLT4IP2 | FLT4IP1 | FLT4IP0 | 0004          |

| IPC20       | 0868              | _      | U3TXIP2 | U3TXIP1 | U3TXIP0 | _      | U3RXIP2    | U3RXIP1    | U3RXIP0    | _       | U3EIP2                | U3EIP1                | U3EIP0                | _       | _       | _       | _       | 0000          |

| IPC21       | 086A              | _      | U4EIP2  | U4EIP1  | U4EIP0  |        | _          | -          | _          |         |                       | _                     | _                     | _       | _       |         | _       | 0000          |

| IPC22       | 086C              | _      | SPI3IP2 | SPI3IP1 | SPI3IP0 |        | SPI3EIP2   | SPI3EIP1   | SPI3EIP0   |         | U4TXIP2               | U4TXIP1               | U4TXIP0               | _       | U4RXIP2 | U4RXIP1 | U4RXIP0 | 0000          |

| IPC23       | 086E              | _      | PGC2IP2 | PGC2IP1 | PGC2IP0 |        | PWM1IP2    | PWM1IP1    | PWM1IP0    |         |                       | _                     | _                     | _       | _       |         | _       | 4400          |

| IPC24       | 0870              | _      | PWM6IP2 | PWM6IP1 | PWM6IP0 |        | PWM5IP2    | PWM5IP1    | PWM5IP0    |         | PWM4IP2               | PWM4IP1               | PWM4IP0               | _       | PWM3IP2 | PWM3IP1 | PWM3IP0 | 4444          |

| IPC35       | 0886              | _      | JTAGIP2 | JTAGIP1 | JTAGIP0 |        | ICDIP2     | ICDIP1     | ICDIP0     |         |                       | _                     | _                     | _       | _       |         | _       | 4400          |

| IPC36       | 0888              | _      | PTG0IP2 | PTG0IP1 | PTG0IP0 | -      | PTGWDTIP2  | PTGWDTIP1  | PTGWDTIP0  |         | PTGSTEPIP2            | PTGSTEPIP1            | PTGSTEPIP0            | —       | _       |         | _       | 4440          |

| IPC37       | 088A              | _      | _       | -       | _       | -      | PTG3IP2    | PTG3IP1    | PTG3IP0    |         | PTG2IP2               | PTG2IP1               | PTG2IP0               | _       | PTG1IP2 | PTG1IP1 | PTG1IP0 | 0444          |

| INTTREG     | 08C8              | _      | _       |         | _       | ILR3   | ILR2       | ILR1       | ILR0       | VECNUM7 | VECNUM6               | VECNUM5               | VECNUM4               | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 | 0000          |

#### TABLE 4-3: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGM3XX DEVICES (CONTINUED)

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The PMPIF/PMPIE/PMPIPx flags are not available on 44-pin devices.

2: The RTCCIF/RTCCIE/RTCCIPx flags are not available on 44-pin devices.

# TABLE 4-27: CAN2 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 FOR dsPIC33EPXXXGM60X/7XX DEVICES<sup>(1)</sup>

| SFR<br>Name | Addr.         | Bit 15 | Bit 14                      | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8        | Bit 7       | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0   | All<br>Resets |

|-------------|---------------|--------|-----------------------------|---------|--------|--------|--------|---------|--------------|-------------|---------|---------|--------|--------|--------|---------|---------|---------------|

|             | 0500-<br>051E |        | See definition when WIN = x |         |        |        |        |         |              |             |         |         |        |        |        |         |         |               |

| C2RXFUL1    | 0520          |        |                             |         |        |        |        |         | RXFUL        | <15:0>      |         |         |        |        |        |         |         | 0000          |

| C2RXFUL2    | 0522          |        |                             |         |        |        |        |         | RXFUL<       | :31:16>     |         |         |        |        |        |         |         | 0000          |

| C2RXOVF1    | 0528          |        |                             |         |        |        |        |         | RXOVF        | <15:0>      |         |         |        |        |        |         |         | 0000          |

| C2RXOVF2    | 052A          |        |                             |         |        |        |        |         | <b>RXOVF</b> | <31:16>     |         |         |        |        |        |         |         | 0000          |

| C2TR01CON   | 0530          | TXEN1  | TXABT1                      | TXLARB1 | TXERR1 | TXREQ1 | RTREN1 | TX1PRI1 | TX1PRI0      | TXEN0       | TXABAT0 | TXLARB0 | TXERR0 | TXREQ0 | RTREN0 | TX0PRI1 | TX0PRI0 | 0000          |

| C2TR23CON   | 0532          | TXEN3  | TXABT3                      | TXLARB3 | TXERR3 | TXREQ3 | RTREN3 | TX3PRI1 | TX3PRI0      | TXEN2       | TXABAT2 | TXLARB2 | TXERR2 | TXREQ2 | RTREN2 | TX2PRI1 | TX2PRI0 | 0000          |

| C2TR45CON   | 0534          | TXEN5  | TXABT5                      | TXLARB5 | TXERR5 | TXREQ5 | RTREN5 | TX5PRI1 | TX5PRI0      | TXEN4       | TXABAT4 | TXLARB4 | TXERR4 | TXREQ4 | RTREN4 | TX4PRI1 | TX4PRI0 | 0000          |

| C2TR67CON   | 0536          | TXEN7  | TXABT7                      | TXLARB7 | TXERR7 | TXREQ7 | RTREN7 | TX7PRI1 | TX7PRI0      | TXEN6       | TXABAT6 | TXLARB6 | TXERR6 | TXREQ6 | RTREN6 | TX6PRI1 | TX6PRI0 | xxxx          |

| C2RXD       | 0540          |        |                             |         |        |        |        | CAN2    | Receive Da   | ta Word Re  | egister |         |        |        |        |         |         | xxxx          |

| C2TXD       | 0542          |        |                             |         |        |        |        | CAN2    | Transmit Da  | ata Word Re | egister |         |        |        |        |         |         | xxxx          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** These registers are not present on dsPIC33EPXXXGM3XX devices.

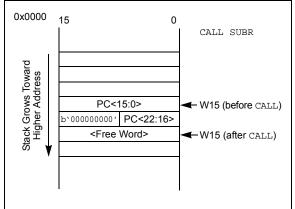

### 4.3.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack     |

|-------|-----------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the |

|       | hardware.                               |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGM3XX/6XX/7XX devices and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack, working from lower toward higher addresses. Figure 4-13 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-13. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain the Software Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore, restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a 'C' development environment

#### FIGURE 4-13: C.

#### CALL STACK FRAME

# 4.4 Instruction Addressing Modes

The addressing modes shown in Table 4-66 form the basis of the addressing modes optimized to support the specific features of the individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

### 4.4.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

### 4.4.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- · Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

Note: Not all instructions support all of the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

| U-0          |                                                                                                            |                                                                               |                            |                   |                 |                    |       |  |

|--------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------|-------------------|-----------------|--------------------|-------|--|

| 0-0          | R/W-0                                                                                                      | R/W-0                                                                         | R/W-0                      | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

| _            |                                                                                                            |                                                                               |                            | SCK2R<6:0>        |                 |                    |       |  |

| oit 15       |                                                                                                            |                                                                               |                            |                   |                 |                    | bit   |  |

| U-0          | R/W-0                                                                                                      | R/W-0                                                                         | R/W-0                      | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

| —            |                                                                                                            |                                                                               |                            | SDI2R<6:0>        |                 |                    |       |  |

| bit 7        |                                                                                                            |                                                                               |                            |                   |                 |                    | bit   |  |

| Legend:      |                                                                                                            |                                                                               |                            |                   |                 |                    |       |  |

| R = Readab   | ole bit                                                                                                    | W = Writable                                                                  | bit                        | U = Unimpler      | nented bit, rea | d as '0'           |       |  |

| -n = Value a | at POR                                                                                                     | '1' = Bit is set                                                              |                            | '0' = Bit is clea | ared            | x = Bit is unknown |       |  |

|              | (see Table 1 <sup>-</sup>                                                                                  |                                                                               |                            |                   | rresponding F   |                    |       |  |

|              | 1111100 =  <br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                             | 1-2 for input pin<br>nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss | selection nun<br>124<br>P1 |                   |                 |                    |       |  |

| bit 7        | 1111100 =  <br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | 1-2 for input pin<br>nput tied to RPI<br>nput tied to CMI                     | selection num<br>124<br>P1 |                   |                 |                    |       |  |

### REGISTER 11-16: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

# REGISTER 11-38: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8<sup>(1)</sup>

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP70  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

|        |     |       |       |       |        |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

| _      | —   |       |       | RP69  | R<5:0> |       |       |

bit 7

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP70R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP70 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP69R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP69 Output Pin bits (see Table 11-3 for peripheral function numbers) |

Note 1: This register is not available on dsPIC33EPXXXGM304/604 devices.

# REGISTER 11-39: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9<sup>(1)</sup>

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0                 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-----------------------|-------|-------|

|        | —   |       |       | RP97  | ′R<5:0>               |       |       |

| bit 15 |     |       |       |       |                       |       | bit 8 |

|        |     |       |       |       |                       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0                 | R/W-0 | R/W-0 |

|        |     |       |       | RP81F | R<5:0> <sup>(2)</sup> |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                              |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP97R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)                |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                              |

| bit 5-0   | <b>RP81R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP81 Output Pin bits <sup>(2)</sup> (see Table 11-3 for peripheral function numbers) |

| Note 1:   | This register is not available on dsPIC33EPXXXGM304/604 devices.                                                                                        |

2: These bits are not available on dsPIC33EPXXXGM306/706 devices.

bit 0

bit 0

#### REGISTER 16-6: STCON2: PWMx SECONDARY MASTER CLOCK DIVIDER SELECT REGISTER 2

| U-0            | U-0 | U-0          | U-0 | U-0          | U-0              | U-0           | U-0   |

|----------------|-----|--------------|-----|--------------|------------------|---------------|-------|

| —              | —   | —            | —   | —            | —                | —             | _     |

| bit 15         |     |              |     |              |                  |               | bit 8 |

|                |     |              |     |              |                  |               |       |

| U-0            | U-0 | U-0          | U-0 | U-0          | R/W-0            | R/W-0         | R/W-0 |

| —              | —   | —            | —   | —            | P                | CLKDIV<2:0>(1 | )     |

| bit 7          |     |              |     |              |                  |               | bit 0 |

|                |     |              |     |              |                  |               |       |

| Legend:        |     |              |     |              |                  |               |       |

| R = Readable I | bit | W = Writable | bit | U = Unimpler | mented bit, read | as '0'        |       |

| R – Reauable bit  |                  | 0 – Unimplemented bit, read |                    |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved

- 110 = Divide-by-64

- 101 = Divide-by-32

- 100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

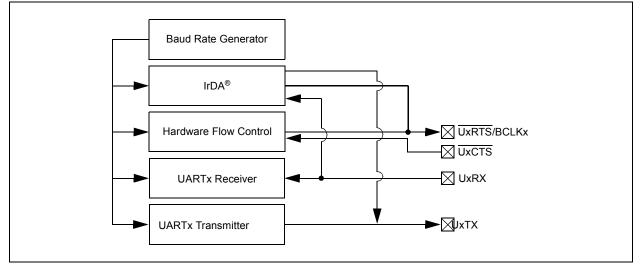

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX family of devices contains four UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGM3XX/6XX/7XX device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: Hardware flow control using UxRTS and UxCTS is not available on all pin count devices. See the "Pin Diagrams" section for availability.

The primary features of the UART module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop Bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for All UART Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA<sup>®</sup> Support

A simplified block diagram of the UART module is shown in Figure 20-1. The UART module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2013-2014 Microchip Technology Inc.

| R/W-0                             | R/W-0  | R/W-0            | R/W-0        | R/W-0                  | R/W-0  | R/W-0              | R/W-0  |

|-----------------------------------|--------|------------------|--------------|------------------------|--------|--------------------|--------|

| F15BP3                            | F15BP2 | F15BP1           | F15BP0       | F14BP3                 | F14BP2 | F14BP1             | F14BP0 |

| bit 15                            |        |                  |              | ·                      |        |                    | bit 8  |

|                                   |        |                  |              |                        |        |                    |        |

| R/W-0                             | R/W-0  | R/W-0            | R/W-0        | R/W-0                  | R/W-0  | R/W-0              | R/W-0  |

| F13BP3                            | F13BP2 | F13BP1           | F13BP0       | F12BP3                 | F12BP2 | F12BP1             | F12BP0 |

| bit 7                             |        |                  |              |                        |        |                    | bit 0  |

|                                   |        |                  |              |                        |        |                    |        |

| Legend:                           |        |                  |              |                        |        |                    |        |

| R = Readable bit W = Writable bit |        | bit              | U = Unimpler | nented bit, read       | as '0' |                    |        |

| -n = Value at POR '1'             |        | '1' = Bit is set |              | '0' = Bit is cleared x |        | x = Bit is unknown |        |

# REGISTER 21-15: CxBUFPNT4: CANx FILTERS 12-15 BUFFER POINTER REGISTER 4

| bit 15-12 | F15BP<3:0>: RX Buffer Mask for Filter 15 bits<br>1111 = Filter hits received in RX FIFO buffer<br>1110 = Filter hits received in RX Buffer 14 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|           | •                                                                                                                                             |

|           | •                                                                                                                                             |

|           | 0001 = Filter hits received in RX Buffer 1<br>0000 = Filter hits received in RX Buffer 0                                                      |

| bit 11-8  | F14BP<3:0>: RX Buffer Mask for Filter 14 bits (same values as bits 15-12)                                                                     |

| bit 7-4   | F13BP<3:0>: RX Buffer Mask for Filter 13 bits (same values as bits 15-12)                                                                     |

| bit 3-0   | F12BP<3:0>: RX Buffer Mask for Filter 12 bits (same values as bits 15-12)                                                                     |

| U-0           | U-0                          | U-0                                                                          | U-0                            | R/W-0                        | R/W-0                 | U-0             | U-0   |  |

|---------------|------------------------------|------------------------------------------------------------------------------|--------------------------------|------------------------------|-----------------------|-----------------|-------|--|

|               |                              | _                                                                            | _                              | CVRR1                        | VREFSEL               | _               |       |  |

| bit 15        |                              |                                                                              | ·                              |                              |                       |                 | bi    |  |

|               |                              |                                                                              |                                | 5444.6                       |                       | 5444.0          |       |  |

| R/W-0         | R/W-0                        | R/W-0                                                                        | R/W-0                          | R/W-0                        | R/W-0                 | R/W-0           | R/W-0 |  |

| CVREN         | CVROE                        | CVRR0                                                                        | CVRSS                          | CVR3                         | CVR2                  | CVR1            | CVR0  |  |

| bit 7         |                              |                                                                              |                                |                              |                       |                 | bit   |  |

| Legend:       |                              |                                                                              |                                |                              |                       |                 |       |  |

| R = Readabl   | le bit                       | W = Writable                                                                 | bit                            | U = Unimple                  | mented bit, read      | 1 as '0'        |       |  |

| -n = Value at | t POR                        | '1' = Bit is set                                                             |                                | '0' = Bit is cle             | eared                 | x = Bit is unkn | iown  |  |

| -             |                              |                                                                              |                                |                              |                       |                 |       |  |

| bit 15-12     | Unimplemen                   | ted: Read as '                                                               | 0'                             |                              |                       |                 |       |  |

| bit 11        | CVRR1: Com<br>See bit 5.     | nparator Voltage                                                             | e Reference I                  | Range Selectio               | on bit                |                 |       |  |

| bit 10        | VREFSEL: V                   | oltage Referen                                                               | ce Select bit                  |                              |                       |                 |       |  |

|               | 1 = CVREFIN                  | -                                                                            |                                |                              |                       |                 |       |  |

|               | 0 = CVREFIN                  | is generated by                                                              | the resistor                   | network                      |                       |                 |       |  |

| bit 9-8       | Unimplemen                   | Unimplemented: Read as '0'                                                   |                                |                              |                       |                 |       |  |

| bit 7         | CVREN: Con                   | nparator Voltag                                                              | e Reference                    | Enable bit                   |                       |                 |       |  |

|               | •                            | tor voltage refe<br>tor voltage refe                                         |                                | •                            | wn                    |                 |       |  |

| bit 6         | CVROE: Con                   | nparator Voltag                                                              | e Reference                    | Output Enable                | on CVREF10 Pi         | n bit           |       |  |

|               |                              | evel is output or<br>evel is disconne                                        |                                |                              |                       |                 |       |  |

| bit 11, 5     | CVRR<1:0>:                   | Comparator Vo                                                                | oltage Refere                  | nce Range Sel                | lection bits          |                 |       |  |

|               | 10 = 0.33 CV<br>01 = 0.00 CV | 'RSRC to 0.94, v<br>'RSRC to 0.96, v<br>'RSRC to 0.67, v<br>'RSRC to 0.75, v | vith CVRSRC/2<br>vith CVRSRC/2 | 24 step-size<br>24 step-size |                       |                 |       |  |

| bit 4         |                              | nparator Voltag                                                              |                                | -                            | on hit                |                 |       |  |

|               | 1 = Compara                  | tor voltage refe<br>tor voltage refe                                         | rence source                   | , CVRSRC = C\                | /ref+ – Avss          |                 |       |  |

| bit 3-0       |                              | •                                                                            |                                |                              | ion $0 \le CVR < 3$ : | )> < 15 bits    |       |  |

|               | When CVRR                    | -                                                                            | -                              |                              |                       |                 |       |  |

|               | When CVRR                    | , ,                                                                          |                                | $(CV_{RSRC})$                |                       |                 |       |  |

|               | When CVRR                    |                                                                              | 0.0.72                         |                              |                       |                 |       |  |

|               |                              | R<3:0>/24) • (0                                                              | CVRSRC)                        |                              |                       |                 |       |  |

|               | When CVRR                    | <1:0> = 00:                                                                  |                                |                              |                       |                 |       |  |

|               |                              | ) • (CVRSRC) +                                                               |                                |                              |                       |                 |       |  |

# REGISTER 26-7: CVR1CON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER 1

# **REGISTER 27-8:** ALRMVAL (WHEN ALRMPTR<1:0> = 10): ALARM MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| —      | —   | _   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

- bit 12 MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit bit Contains a value of 0 or 1.

- bit 11-8 MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits Contains a value from 0 to 9.

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 **DAYTEN<1:0>:** Binary Coded Decimal Value of Day's Tens Digit bits Contains a value from 0 to 3.

- bit 3-0 **DAYONE<3:0>:** Binary Coded Decimal Value of Day's Ones Digit bits Contains a value from 0 to 9.

- **Note 1:** A write to this register is only allowed when RTCWREN = 1.

# REGISTER 28-3: PMADDR: PARALLEL MASTER PORT ADDRESS REGISTER (MASTER MODES ONLY)<sup>(1,2)</sup>

| R/W-0            | R/W-0                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                   | R/W-0       | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------|------------------|----------|-------|

| CS2              | CS1                                                                                                                             | ADDR13                                                                                                                                                                                                                                                                                                                  | ADDR12      | ADDR11                                  | ADDR10           | ADDR9    | ADDR8 |

| bit 15           |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                         |             |                                         |                  |          | bit 8 |

|                  | DAMO                                                                                                                            |                                                                                                                                                                                                                                                                                                                         |             | DAMA                                    |                  | DAMO     | DAMO  |

| R/W-0            | R/W-0                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                   | R/W-0       | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |

| ADDR7            | ADDR6                                                                                                                           | ADDR5                                                                                                                                                                                                                                                                                                                   | ADDR4       | ADDR3                                   | ADDR2            | ADDR1    | ADDR0 |

| bit 7            |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                         |             |                                         |                  |          | bit 0 |

| Legend:          |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                         |             |                                         |                  |          |       |

| R = Readabl      | e bit                                                                                                                           | W = Writable                                                                                                                                                                                                                                                                                                            | bit         | U = Unimplen                            | nented bit, read | d as '0' |       |

| -n = Value at    | Reset                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                                                                                                        |             | '0' = Bit is cleared x = Bit is unknown |                  |          | nown  |

| bit 15<br>bit 14 | 1 = Chip Sele<br>0 = Chip Sele<br>If PMCON<7<br>Bit functions<br>CS1: Chip Sele<br>If PMCON<7<br>1 = Chip Sele<br>0 = Chip Sele | $\frac{1}{100} = 10 \text{ or } 01:$<br>$\frac{1}{100} = 10 \text{ or } 01:$<br>$\frac{1}{100} = 10 \text{ or } 00:$<br>$\frac{1}{100} = 10 \text{ or } 00:$<br>$\frac{1}{100} = 10:$<br>$\frac{1}{100} = 10:$<br>$\frac{1}{100} = 10:$<br>$\frac{1}{100} = 11 \text{ or } 0x:$<br>$\frac{1}{100} = 10 \text{ or } 0x:$ |             |                                         |                  |          |       |

| bit 13-0         | ADDR<13:0>                                                                                                                      | Destination A                                                                                                                                                                                                                                                                                                           | ddress bits |                                         |                  |          |       |

|                  |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                         |             |                                         |                  |          |       |

**Note 1:** In Enhanced Slave mode, PMADDR functions as PMDOUT1, one of the two Data Buffer registers.

2: This register is not available on 44-pin devices.

# 29.2 Programmable CRC Control Registers

### REGISTER 29-1: CRCCON1: CRC CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0 | R-0    | R-0    | R-0    | R-0    | R-0    |

|--------|-----|-------|--------|--------|--------|--------|--------|

| CRCEN  | —   | CSIDL | VWORD4 | VWORD3 | VWORD2 | VWORD1 | VWORD0 |

| bit 15 |     |       |        |        |        |        | bit 8  |

| R-0    | R-1    | R/W-0   | R/W-0 | R/W-0   | U-0 | U-0 | U-0   |

|--------|--------|---------|-------|---------|-----|-----|-------|

| CRCFUL | CRCMPT | CRCISEL | CRCGO | LENDIAN | —   | —   | —     |

| bit 7  |        |         |       |         |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15   | CRCEN: CRC Enable bit                                                                                                                                                             |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>1 = CRC module is enabled</li> <li>0 = CRC module is disabled; all state machines, pointers and CRCWDAT/CRCDAT are reset, other<br/>SFRs are not reset</li> </ul>        |

| bit 14   | Unimplemented: Read as '0'                                                                                                                                                        |

| bit 13   | CSIDL: CRC Stop in Idle Mode bit                                                                                                                                                  |

|          | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                           |

| bit 12-8 | VWORD<4:0>: Valid Word Pointer Value bits                                                                                                                                         |

|          | Indicates the number of valid words in the FIFO; has a maximum value of 8 when PLEN<4:0> > 7 or 16 when PLEN<4:0> $\leq$ 7                                                        |

| bit 7    | CRCFUL: CRC FIFO Full bit                                                                                                                                                         |

|          | 1 = FIFO is full<br>0 = FIFO is not full                                                                                                                                          |

| bit 6    | CRCMPT: CRC FIFO Empty Bit                                                                                                                                                        |

|          | <ul><li>1 = FIFO is empty</li><li>0 = FIFO is not empty</li></ul>                                                                                                                 |

| bit 5    | CRCISEL: CRC Interrupt Selection bit                                                                                                                                              |

|          | <ul> <li>1 = Interrupt on FIFO empty; final word of data is still shifting through CRC</li> <li>0 = Interrupt on shift complete and CRCWDAT results are ready</li> </ul>          |

| bit 4    | CRCGO: CRC Start bit                                                                                                                                                              |

|          | <ul> <li>1 = Start CRC serial shifter</li> <li>0 = CRC serial shifter is turned off</li> </ul>                                                                                    |

| bit 3    | LENDIAN: Data Word Little-Endian Configuration bit                                                                                                                                |

|          | <ul> <li>1 = Data word is shifted into the CRC starting with the LSb (little endian)</li> <li>0 = Data word is shifted into the CRC starting with the MSb (big endian)</li> </ul> |

| bit 2-0  | Unimplemented: Read as '0'                                                                                                                                                        |

|          |                                                                                                                                                                                   |

# **30.0 SPECIAL FEATURES**

Note: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

dsPIC33EPXXXGM3XX/6XX/7XX devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

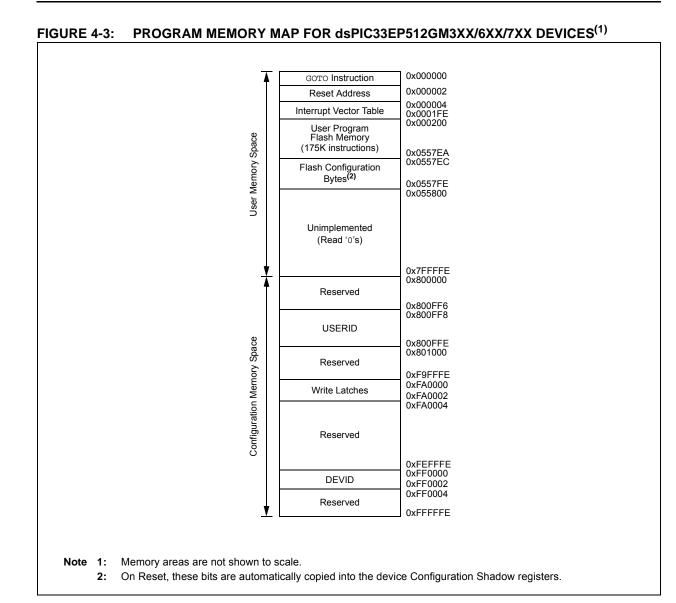

# 30.1 Configuration Bits

In dsPIC33EPXXXGM3XX/6XX/7XX devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored at the top of the on-chip program memory space, known as the Flash Configuration bytes. Their specific locations are shown in Table 30-1. The configuration data is automatically loaded from the Flash Configuration bytes to the proper Configuration Shadow registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration bytes for configuration data in their code for the compiler. This is to make certain that program code is not stored in this address when the code is compiled.

The upper 2 bytes of all Flash Configuration Words in program memory should always be '1111 1111 1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration bytes, enabling code protection as a result. Therefore, users should avoid performing page erase operations on the last page of program memory.

The Configuration Flash bytes map is shown in Table 30-1.

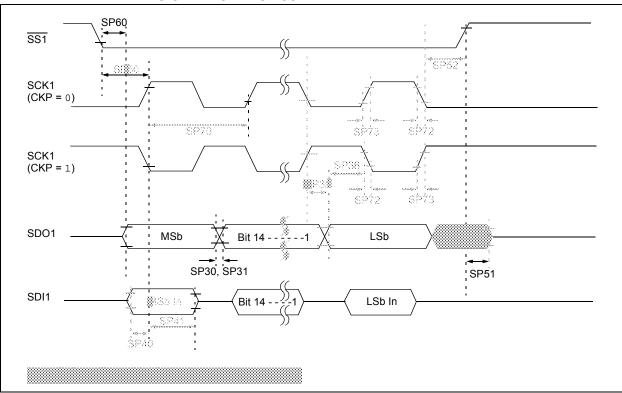

### FIGURE 33-28: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

# TABLE 33-45:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| АС СНА | RACTERIS              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |              |                     |      |       |                                       |

|--------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|------|-------|---------------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                           | Min.         | Typ. <sup>(2)</sup> | Max. | Units | Conditions                            |

| SP70   | FscP                  | Maximum SCK1 Input Frequency                                                                                                                                                                                                                                                            | _            | —                   | 25   | MHz   | (Note 3)                              |

| SP72   | TscF                  | SCK1 Input Fall Time                                                                                                                                                                                                                                                                    | —            | _                   | _    | ns    | See Parameter<br>DO32 (Note 4)        |

| SP73   | TscR                  | SCK1 Input Rise Time                                                                                                                                                                                                                                                                    | —            | —                   |      | ns    | See Parameter<br>DO31 (Note 4)        |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                                                                                                                                                                                                                                                              | —            | -                   | _    | ns    | See Parameter<br>DO32 (Note 4)        |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                                                                                                                                                                                                                                                              | —            | -                   | _    | ns    | See Parameter<br>DO31 <b>(Note 4)</b> |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge                                                                                                                                                                                                                                               | —            | 6                   | 20   | ns    |                                       |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge                                                                                                                                                                                                                                            | 20           | _                   | _    | ns    |                                       |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge                                                                                                                                                                                                                                              | 20           | _                   |      | ns    |                                       |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge                                                                                                                                                                                                                                               | 15           | _                   |      | ns    |                                       |

| SP50   | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input                                                                                                                                                                                                                                                      | 120          | —                   | _    | ns    |                                       |

| SP51   | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance                                                                                                                                                                                                                                                  | 10           | —                   | 50   | ns    | (Note 4)                              |

| SP52   | TscH2ssH,<br>TscL2ssH | SS1 ↑ after SCK1 Edge                                                                                                                                                                                                                                                                   | 1.5 Tcy + 40 | —                   | _    | ns    | (Note 4)                              |

| SP60   | TssL2doV              | SDO1 Data Output Valid after<br>SS1 Edge                                                                                                                                                                                                                                                | —            | _                   | 50   | ns    |                                       |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 91 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

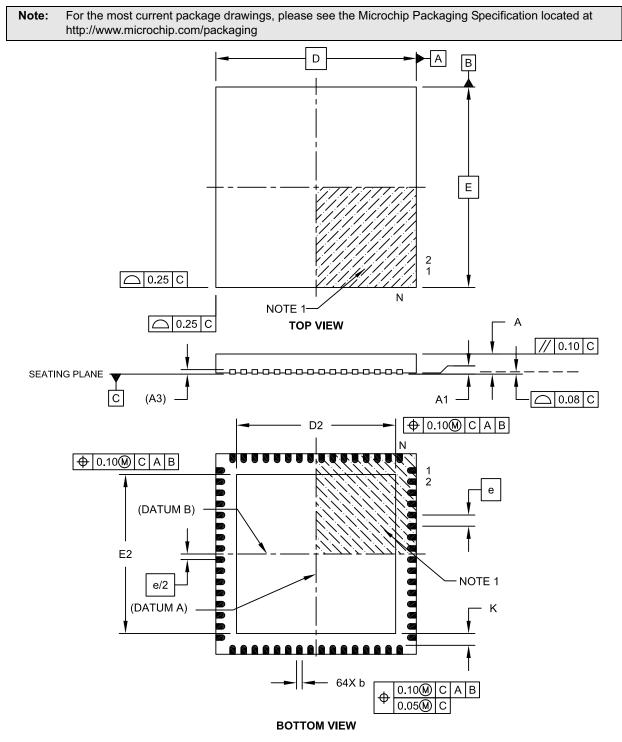

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad

Microchip Technology Drawing C04-149C Sheet 1 of 2

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |          |      |      |  |  |

|------------------------|-------------|----------|------|------|--|--|

| Dimensio               | MIN         | NOM      | MAX  |      |  |  |

| Number of Pins         | N           | 64       |      |      |  |  |

| Pitch                  | е           | 0.50 BSC |      |      |  |  |

| Overall Height         | A           | 0.80     | 0.90 | 1.00 |  |  |

| Standoff               | A1          | 0.00     | 0.02 | 0.05 |  |  |

| Contact Thickness      | A3          | 0.20 REF |      |      |  |  |

| Overall Width          | E           | 9.00 BSC |      |      |  |  |

| Exposed Pad Width      | E2          | 7.05     | 7.15 | 7.50 |  |  |

| Overall Length         | D           | 9.00 BSC |      |      |  |  |

| Exposed Pad Length     | D2          | 7.05     | 7.15 | 7.50 |  |  |

| Contact Width          | b           | 0.18     | 0.25 | 0.30 |  |  |

| Contact Length         | L           | 0.30     | 0.40 | 0.50 |  |  |

| Contact-to-Exposed Pad | K           | 0.20     | -    | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-149C Sheet 2 of 2

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470 China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205 **China - Shanghai**

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

**France - Paris** Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Pforzheim Tel: 49-7231-424750

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

03/25/14