Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | -                                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | -                                                                                |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm710-h-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IABLE 4-    | <b>ZZ</b> . | ADO                 |                     |           | REGIST   |          |          | NOLD)    |          |              |       |           |          |          |          |          |          |               |

|-------------|-------------|---------------------|---------------------|-----------|----------|----------|----------|----------|----------|--------------|-------|-----------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr.       | Bit 15              | Bit 14              | Bit 13    | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7        | Bit 6 | Bit 5     | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| ADC2BUF9    | 0352        |                     |                     |           |          |          |          |          | ADC2 Da  | ata Buffer   | 9     |           |          |          |          |          |          | xxxx          |

| ADC2BUFA    | 0354        |                     |                     |           |          |          |          |          | ADC2 Da  | ta Buffer 1  | 10    |           |          |          |          |          |          | xxxx          |

| ADC2BUFB    | 0356        |                     |                     |           |          |          |          |          | ADC2 Da  | ta Buffer ´  | 11    |           |          |          |          |          |          | xxxx          |

| ADC2BUFC    | 0358        |                     | ADC2 Data Buffer 12 |           |          |          |          |          |          | xxxx         |       |           |          |          |          |          |          |               |

| ADC2BUFD    | 035A        | ADC2 Data Buffer 13 |                     |           |          |          |          | xxxx     |          |              |       |           |          |          |          |          |          |               |

| ADC2BUFE    | 035C        |                     |                     |           |          |          |          |          | ADC2 Da  | ta Buffer 1  | 14    |           |          |          |          |          |          | xxxx          |

| ADC2BUFF    | 035E        |                     |                     |           |          |          |          |          | ADC2 Da  | ta Buffer 1  | 15    |           |          |          |          |          |          | xxxx          |

| AD2CON1     | 0360        | ADON                | _                   | ADSIDL    | ADDMABM  |          | AD12B    | FORM1    | FORM0    | SSRC2        | SSRC1 | SSRC0     | SSRCG    | SIMSAM   | ASAM     | SAMP     | DONE     | 0000          |

| AD2CON2     | 0362        | VCFG2               | VCFG1               | VCFG0     | OFFCAL   |          | CSCNA    | CHPS1    | CHPS0    | BUFS         | SMPI4 | SMPI3     | SMPI2    | SMPI1    | SMPI0    | BUFM     | ALTS     | 0000          |

| AD2CON3     | 0364        | ADRC                | -                   | _         | SAMC4    | SAMC3    | SAMC2    | SAMC1    | SAMC0    | ADCS7        | ADCS6 | ADCS5     | ADCS4    | ADCS3    | ADCS2    | ADCS1    | ADCS0    | 0000          |

| AD2CHS123   | 0366        | —                   | -                   | _         | CH123SB2 | CH123SB1 | CH123NB1 | CH123NB0 | CH123SB0 | _            | _     | _         | CH123SA2 | CH123SA1 | CH123NA1 | CH123NA0 | CH123SA0 | 0000          |

| AD2CHS0     | 0368        | <b>CH0NB</b>        | -                   | CH0SB5(1) | CH0SB4   | CH0SB3   | CH0SB2   | CH0SB1   | CH0SB0   | <b>CH0NA</b> | _     | CH0SA5(1) | CH0SA4   | CH0SA3   | CH0SA2   | CH0SA1   | CH0SA0   | 0000          |

| AD2CSSH     | 036E        |                     |                     |           |          |          |          |          | CSS<     | :31:16>      |       |           |          |          |          |          |          | 0000          |

| AD2CSSL     | 0370        |                     |                     |           |          |          |          |          | CSS      | <15:0>       |       |           |          |          |          |          |          | 0000          |

| AD2CON4     | 0372        | —                   | _                   | —         | —        | —        | —        | —        | ADDMAEN  | _            |       | _         | _        | _        | DMABL2   | DMABL1   | DMABL0   | 0000          |

#### TABLE 4-22: ADC1 AND ADC2 REGISTER MAP (CONTINUED)

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Bits 13 and bit 5 are reserved in the AD2CHS0 register, unlike the AD1CHS0 register.

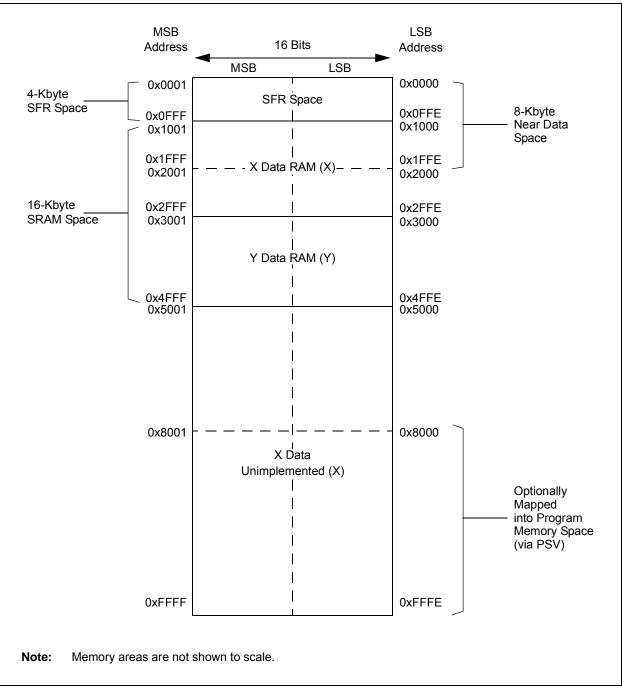

## 4.3.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGM3XX/6XX/7XX architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre- and post-modified Effective Addresses (EA). The upper half of the Base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Data Space Read Page register (DSRPAG) or the 9-bit Data Space Write Page register (DSWPAG), to form an Extended Data Space (EDS) address, or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

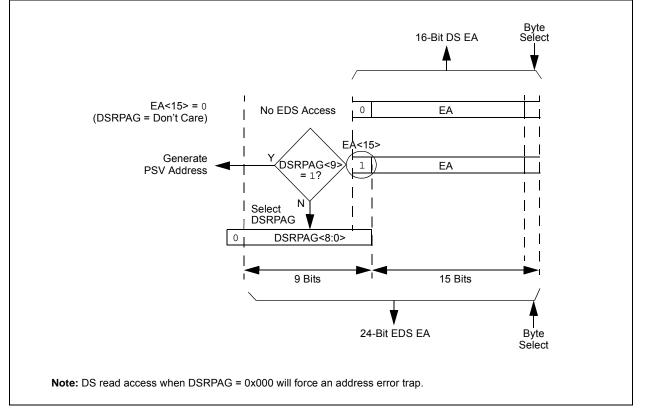

Construction of the EDS address is shown in Figure 4-8. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when the base address bit, EA<15> =1, the DSWPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS write address.

## FIGURE 4-8: EXTENDED DATA SPACE (EDS) READ ADDRESS GENERATION

| R/W-0        | R/W-0                                   | R/W-1                                                       | R/W-1                | R/W-0                                 | R/W-0              | R/W-0           | R/W-0     |  |  |  |  |  |

|--------------|-----------------------------------------|-------------------------------------------------------------|----------------------|---------------------------------------|--------------------|-----------------|-----------|--|--|--|--|--|

| ROI          | DOZE2 <sup>(3)</sup>                    | DOZE1 <sup>(3)</sup>                                        | DOZE0 <sup>(3)</sup> | DOZEN <sup>(1,4)</sup>                | FRCDIV2            | FRCDIV1         | FRCDIV0   |  |  |  |  |  |

| bit 15       |                                         |                                                             |                      |                                       |                    |                 | bit 8     |  |  |  |  |  |

|              |                                         |                                                             |                      |                                       |                    |                 |           |  |  |  |  |  |

| R/W-0        | R/W-1                                   | U-0                                                         | R/W-0                | R/W-0                                 | R/W-0              | R/W-0           | R/W-0     |  |  |  |  |  |

| PLLPOST      | 1 PLLPOST0                              |                                                             | PLLPRE4              | PLLPRE3                               | PLLPRE2            | PLLPRE1         | PLLPRE0   |  |  |  |  |  |

| bit 7        |                                         |                                                             |                      |                                       |                    |                 |           |  |  |  |  |  |

| <del></del>  |                                         |                                                             |                      |                                       |                    |                 |           |  |  |  |  |  |

| Legend:      | la hit                                  |                                                             | L:4                  | II — Ilucius da un                    | antad bit was      | L == (0'        |           |  |  |  |  |  |

| R = Readab   |                                         | W = Writable                                                |                      | •                                     | nented bit, read   |                 |           |  |  |  |  |  |

| -n = Value a | IL POR                                  | '1' = Bit is set                                            |                      | '0' = Bit is clea                     | ared               | x = Bit is unkr | IOWI      |  |  |  |  |  |

| bit 15       | ROI: Recover                            | on Interrupt b                                              | it                   |                                       |                    |                 |           |  |  |  |  |  |

|              |                                         | will clear the D                                            |                      |                                       |                    |                 |           |  |  |  |  |  |

|              |                                         | will have no ef                                             |                      | OZEN bit                              |                    |                 |           |  |  |  |  |  |

| bit 14-12    | DOZE<2:0>:                              | Processor Clo                                               | ck Reduction         | Select bits <sup>(3)</sup>            |                    |                 |           |  |  |  |  |  |

|              | 111 = Fcy div                           |                                                             |                      |                                       |                    |                 |           |  |  |  |  |  |

|              | 110 = Fcy div                           | •                                                           |                      |                                       |                    |                 |           |  |  |  |  |  |

|              | 101 = FCY div                           |                                                             |                      |                                       |                    |                 |           |  |  |  |  |  |

|              |                                         | 100 = Fcy divided by 16<br>011 = Fcy divided by 8 (default) |                      |                                       |                    |                 |           |  |  |  |  |  |

|              | 010 = FCY div                           |                                                             |                      |                                       |                    |                 |           |  |  |  |  |  |

|              | 001 = Fcy div                           |                                                             |                      |                                       |                    |                 |           |  |  |  |  |  |

|              | 000 = FCY div                           | •                                                           |                      |                                       |                    |                 |           |  |  |  |  |  |

| bit 11       |                                         | e Mode Enable                                               |                      |                                       |                    |                 |           |  |  |  |  |  |

|              |                                         |                                                             |                      | etween the perip                      |                    | nd the processo | or clocks |  |  |  |  |  |

| hit 10 0     |                                         | •                                                           | •                    | ratio are forced<br>r Postscaler bits |                    |                 |           |  |  |  |  |  |

| bit 10-8     |                                         |                                                             | RC Oscillator        | Posiscaler bits                       | 5                  |                 |           |  |  |  |  |  |

|              |                                         | 111 = FRC divided by 256<br>110 = FRC divided by 64         |                      |                                       |                    |                 |           |  |  |  |  |  |

|              |                                         | 100 = FRC divided by 84<br>101 = FRC divided by 32          |                      |                                       |                    |                 |           |  |  |  |  |  |

|              | 100 <b>= FRC di</b>                     |                                                             |                      |                                       |                    |                 |           |  |  |  |  |  |

|              | 011 = FRC di                            |                                                             |                      |                                       |                    |                 |           |  |  |  |  |  |

|              | 010 = FRC di<br>001 = FRC di            | •                                                           |                      |                                       |                    |                 |           |  |  |  |  |  |

|              |                                         | ivided by 1 (de                                             | fault)               |                                       |                    |                 |           |  |  |  |  |  |

| bit 7-6      |                                         | •                                                           |                      | r Select bits (als                    | so denoted as      | N2', PLL posts  | caler)    |  |  |  |  |  |

|              | 11 = Output o                           | livided by 8                                                | -                    |                                       |                    | -               | ·         |  |  |  |  |  |

|              | 10 = Reserve                            |                                                             |                      |                                       |                    |                 |           |  |  |  |  |  |

|              | 01 = Output c<br>00 = Output c          | livided by 4 (de                                            | efault)              |                                       |                    |                 |           |  |  |  |  |  |

| bit 5        | -                                       | ted: Read as '                                              | 0'                   |                                       |                    |                 |           |  |  |  |  |  |

|              | -                                       |                                                             |                      | n interment a                         |                    |                 |           |  |  |  |  |  |

|              | This bit is cleared                     |                                                             |                      |                                       | uis.               |                 |           |  |  |  |  |  |

|              | This register resets<br>The DOZE<2:0> b | -                                                           |                      |                                       | hit is clear. If D |                 | writes to |  |  |  |  |  |

|              | OZE<2:0> b<br>OZE<2:0> are ig           | -                                                           |                      |                                       | on is oreal. If D  | ∪∠∟iv – ⊥, ally |           |  |  |  |  |  |

|              |                                         |                                                             |                      |                                       |                    |                 |           |  |  |  |  |  |

## REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup>

4: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| REGISTER 11-7: | RPINR10: PERIPHERAL PIN SELECT INPUT REGISTER 10 |

|----------------|--------------------------------------------------|

|                |                                                  |

| U-0          | R/W-0         | R/W-0                                                                                                                                                     | R/W-0 | R/W-0              | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |  |

|--------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|-----------------|-----------------|-------|--|--|--|--|--|--|

| _            |               |                                                                                                                                                           |       | IC8R<6:0>          |                 |                 |       |  |  |  |  |  |  |

| bit 15       |               |                                                                                                                                                           |       |                    |                 |                 | bit 8 |  |  |  |  |  |  |

| U-0          | DAMO          |                                                                                                                                                           | DAMO  | DANO               |                 | DAMO            | DAMO  |  |  |  |  |  |  |

| 0-0          | R/W-0         | R/W-0                                                                                                                                                     | R/W-0 | R/W-0<br>IC7R<6:0> | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |  |

| bit 7        |               |                                                                                                                                                           |       | IC/R<0.02          |                 |                 | bit 0 |  |  |  |  |  |  |

|              |               |                                                                                                                                                           |       |                    |                 |                 |       |  |  |  |  |  |  |

| Legend:      |               |                                                                                                                                                           |       |                    |                 |                 |       |  |  |  |  |  |  |

| R = Readab   | le bit        | W = Writable                                                                                                                                              | bit   | U = Unimplen       | nented bit, rea | ad as '0'       |       |  |  |  |  |  |  |

| -n = Value a | t POR         | '1' = Bit is set                                                                                                                                          |       | '0' = Bit is clea  | ared            | x = Bit is unkr | nown  |  |  |  |  |  |  |

|              |               |                                                                                                                                                           |       |                    |                 |                 |       |  |  |  |  |  |  |

| bit 15       | Unimplemen    | ted: Read as '                                                                                                                                            | 0'    |                    |                 |                 |       |  |  |  |  |  |  |

| bit 14-8     |               | IC8R<6:0>: Assign Input Capture 8 (IC8) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers)                                |       |                    |                 |                 |       |  |  |  |  |  |  |

|              | 1111100 = lr  | nput tied to RPI                                                                                                                                          | 124   |                    |                 |                 |       |  |  |  |  |  |  |

|              | •             |                                                                                                                                                           |       |                    |                 |                 |       |  |  |  |  |  |  |

|              | •             |                                                                                                                                                           |       |                    |                 |                 |       |  |  |  |  |  |  |

|              | 0000001 = lr  | nput tied to CM                                                                                                                                           | P1    |                    |                 |                 |       |  |  |  |  |  |  |

|              | 0000000 = Ir  | nput tied to Vss                                                                                                                                          |       |                    |                 |                 |       |  |  |  |  |  |  |

| bit 7        | Unimplemen    | ted: Read as '                                                                                                                                            | 0'    |                    |                 |                 |       |  |  |  |  |  |  |

| bit 6-0      | (see Table 11 | IC7R<6:0>: Assign Input Capture 7 (IC7) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111100 = Input tied to RPI124 |       |                    |                 |                 |       |  |  |  |  |  |  |

|              | •             |                                                                                                                                                           |       |                    |                 |                 |       |  |  |  |  |  |  |

|              | •             |                                                                                                                                                           |       |                    |                 |                 |       |  |  |  |  |  |  |

|              |               | nput tied to CM                                                                                                                                           |       |                    |                 |                 |       |  |  |  |  |  |  |

| U-0             | U-0                 | U-0                               | U-0   | U-0              | U-0              | U-0                | U-0   |  |

|-----------------|---------------------|-----------------------------------|-------|------------------|------------------|--------------------|-------|--|

| —               | —                   |                                   | _     | —                |                  | —                  | —     |  |

| bit 15          |                     |                                   |       |                  |                  |                    | bit 8 |  |

|                 |                     |                                   |       |                  |                  |                    |       |  |

| U-0             | R/W-0               | R/W-0                             | R/W-0 | R/W-0            | R/W-0            | R/W-0              | R/W-0 |  |

| —               |                     |                                   |       | OCFAR<6:0>       | >                |                    |       |  |

| bit 7           |                     |                                   |       |                  |                  |                    | bit 0 |  |

|                 |                     |                                   |       |                  |                  |                    |       |  |

| Legend:         |                     |                                   |       |                  |                  |                    |       |  |

| R = Readable    | bit                 | W = Writable                      | bit   | U = Unimpler     | nented bit, read | as '0'             |       |  |

| -n = Value at F | POR                 | '1' = Bit is set                  |       | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |

|                 |                     |                                   |       |                  |                  |                    |       |  |

| bit 15-7        | Unimplemen          | ted: Read as '                    | כ'    |                  |                  |                    |       |  |

| bit 6-0         |                     | : Assign Outpu<br>2 for input pin |       |                  | to the Correspon | nding RPn Pin      | bits  |  |

|                 | 1111100 <b>= In</b> | put tied to RPI                   | 124   |                  |                  |                    |       |  |

|                 | •                   |                                   |       |                  |                  |                    |       |  |

|                 | •                   |                                   |       |                  |                  |                    |       |  |

|                 |                     |                                   |       |                  |                  |                    |       |  |

#### REGISTER 11-8: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

# 12.1 Timer1 Control Register

# REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0              | U-0                               | R/W-0                                                  | U-0                       | U-0              | U-0                       | U-0                | U-0         |  |  |  |  |

|--------------------|-----------------------------------|--------------------------------------------------------|---------------------------|------------------|---------------------------|--------------------|-------------|--|--|--|--|

| TON <sup>(1)</sup> | —                                 | TSIDL                                                  | _                         | —                | —                         | —                  | —           |  |  |  |  |

| bit 15             |                                   |                                                        |                           |                  |                           |                    | bit 8       |  |  |  |  |

|                    |                                   |                                                        |                           |                  |                           |                    |             |  |  |  |  |

| U-0                | R/W-0                             | R/W-0                                                  | R/W-0                     | U-0              | R/W-0                     | R/W-0              | U-0         |  |  |  |  |

| _                  | TGATE                             | TCKPS1                                                 | TCKPS1                    |                  | TSYNC <sup>(1)</sup>      | TCS <sup>(1)</sup> | —           |  |  |  |  |

| bit 7              |                                   |                                                        |                           |                  |                           |                    | bit 0       |  |  |  |  |

| r                  |                                   |                                                        |                           |                  |                           |                    |             |  |  |  |  |

| Legend:            |                                   |                                                        |                           |                  |                           |                    |             |  |  |  |  |

| R = Readable       |                                   | W = Writable                                           |                           | -                | mented bit, read          |                    |             |  |  |  |  |

| -n = Value at F    | POR                               | '1' = Bit is set                                       |                           | '0' = Bit is cle | ared                      | x = Bit is unkr    | IOWN        |  |  |  |  |

|                    | TON: Timer1                       | o                                                      |                           |                  |                           |                    |             |  |  |  |  |

| bit 15             | 1 = Starts 16-                    |                                                        |                           |                  |                           |                    |             |  |  |  |  |

|                    | 1 = Starts 16-<br>0 = Stops 16-   |                                                        |                           |                  |                           |                    |             |  |  |  |  |

| bit 14             | •                                 | ted: Read as '                                         | )'                        |                  |                           |                    |             |  |  |  |  |

| bit 13             | -                                 | 1 Stop in Idle N                                       |                           |                  |                           |                    |             |  |  |  |  |

|                    | 1 = Discontine                    | ues module op                                          | eration when              | device enters I  | dle mode                  |                    |             |  |  |  |  |

|                    |                                   | s module opera                                         |                           | ode              |                           |                    |             |  |  |  |  |

| bit 12-7           | -                                 | ted: Read as '                                         |                           |                  |                           |                    |             |  |  |  |  |

| bit 6              |                                   | <b>GATE:</b> Timer1 Gated Time Accumulation Enable bit |                           |                  |                           |                    |             |  |  |  |  |

|                    | When TCS =<br>This bit is igno    |                                                        |                           |                  |                           |                    |             |  |  |  |  |

|                    | When TCS =                        |                                                        |                           |                  |                           |                    |             |  |  |  |  |

|                    |                                   | e accumulatior                                         | n is enabled              |                  |                           |                    |             |  |  |  |  |

|                    | 0 = Gated tim                     | e accumulatior                                         | n is disabled             |                  |                           |                    |             |  |  |  |  |

| bit 5-4            |                                   | : Timer1 Input                                         | Clock Prescal             | e Select bits    |                           |                    |             |  |  |  |  |

|                    | 11 = 1:256<br>10 = 1:64           |                                                        |                           |                  |                           |                    |             |  |  |  |  |

|                    | 01 = 1:8                          |                                                        |                           |                  |                           |                    |             |  |  |  |  |

|                    | 00 = 1:1                          |                                                        |                           |                  |                           |                    |             |  |  |  |  |

| bit 3              | Unimplemen                        | ted: Read as '                                         | )'                        |                  |                           |                    |             |  |  |  |  |

| bit 2              |                                   | er1 External Clo                                       | ock Input Synd            | chronization Se  | elect bit <sup>(1)</sup>  |                    |             |  |  |  |  |

|                    | When TCS = $\frac{1}{1}$          |                                                        | a al ciana ut             |                  |                           |                    |             |  |  |  |  |

|                    |                                   | izes external cl<br>synchronize ex                     |                           | nout             |                           |                    |             |  |  |  |  |

|                    | When TCS =                        | •                                                      |                           | iput             |                           |                    |             |  |  |  |  |

|                    | This bit is igno                  |                                                        |                           |                  |                           |                    |             |  |  |  |  |

| bit 1              | TCS: Timer1                       | Clock Source S                                         | Select bit <sup>(1)</sup> |                  |                           |                    |             |  |  |  |  |

|                    |                                   | clock is from pir                                      | n, T1CK (on th            | ne rising edge)  |                           |                    |             |  |  |  |  |

| hit 0              | 0 = Internal cl                   |                                                        | ۰ <b>۲</b>                |                  |                           |                    |             |  |  |  |  |

| bit 0              | ommplemen                         | ted: Read as '                                         | J                         |                  |                           |                    |             |  |  |  |  |

|                    | en Timer1 is en<br>mpts by user s |                                                        |                           |                  | ode (TCS = 1, T<br>nored. | SYNC = 1, TO       | N = 1), any |  |  |  |  |

# 16.0 HIGH-SPEED PWM MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "High-Speed PWM" (DS70645), which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX devices support a dedicated Pulse-Width Modulation (PWM) module with up to 12 outputs.

The high-speed PWMx module consists of the following major features:

- · Six PWM generators

- Two PWM outputs per PWM generator

- Individual period and duty cycle for each PWM pair

- Duty cycle, dead time, phase shift and a frequency resolution of 7.14 ns

- Independent Fault and current-limit inputs for six PWM outputs

- · Redundant output

- Center-Aligned PWM mode

- Output override control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Prescaler for input clock

- PWMxL and PWMxH output pin swapping

- Independent PWM frequency, duty cycle and phase-shift changes for each PWM generator

- Dead-time compensation

- Enhanced Leading-Edge Blanking (LEB) functionality

- Frequency resolution enhancement

- PWM capture functionality

**Note:** In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 7.14 ns.

The high-speed PWMx module contains up to six PWM generators. Each PWMx generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADCx module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADCx module, based on either of the two master time bases.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 and SYNCI2 input pins that utilize PPS, can synchronize the high-speed PWMx module with an external signal. The SYNCO1 and SYNCO2 pins are output pins that provides a synchronous signal to an external device.

Figure 16-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

## 16.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs, which include FLT1 and FLT2. The inputs are remappable using the PPS feature. FLT3 is available on 44-pin, 64-pin and 100-pin packages; FLT4 through FLT8 are available on specific pins on 64-pin and 100-pin packages, and FLT32, which has been implemented with Class B safety features, and is available on a fixed pin on all devices.

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

#### 16.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the highspeed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled high externally or the internal pull-up resistor in the CNPUx register can be enabled.

Note: The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCONx<1:0>), regardless of the state of FLT32.

#### REGISTER 16-21: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER (CONTINUED)

| bit 7-3 | FLTSRC<4:0>: Fault Control Signal Source Select for PWMx Generator # bits<br>11111 = Fault 32 (default)<br>11110 = Reserved<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 00011 = Fault 4<br>00010 = Fault 3<br>00001 = Fault 2<br>00000 = Fault 1                                                                                                                                                                                                                         |

| bit 2   | <b>FLTPOL:</b> Fault Polarity for PWMx Generator # bit <sup>(1)</sup><br>1 = The selected Fault source is active-low<br>0 = The selected Fault source is active-high                                                                                                                             |

| bit 1-0 | FLTMOD<1:0>: Fault Mode for PWMx Generator # bits<br>11 = Fault input is disabled<br>10 = Reserved<br>01 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (cycle)<br>00 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (latched condition) |

**Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| U-0                   | U-0                            | HS, R/C-0                              | R/W-0           | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

|-----------------------|--------------------------------|----------------------------------------|-----------------|------------------|------------------|-----------------------|----------|

| _                     |                                | PCHEQIRQ                               | PCHEQIEN        | PCLEQIRQ         | PCLEQIEN         | POSOVIRQ              | POSOVIEN |

| bit 15                |                                |                                        |                 |                  |                  |                       | bit 8    |

|                       |                                |                                        |                 |                  |                  |                       |          |

| HS, R/C-0             | R/W-0                          | HS, R/C-0                              | R/W-0           | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

| PCIIRQ <sup>(1)</sup> | PCIIEN                         | VELOVIRQ                               | VELOVIEN        | HOMIRQ           | HOMIEN           | IDXIRQ                | IDXIEN   |

| bit 7                 |                                |                                        |                 |                  |                  |                       | bit 0    |

|                       |                                |                                        |                 |                  |                  |                       |          |

| Legend:               |                                | HS = Hardware                          |                 | C = Clearable    |                  |                       |          |

| R = Readable          |                                | W = Writable b                         | bit             |                  | nented bit, read |                       |          |

| -n = Value at         | POR                            | '1' = Bit is set                       |                 | '0' = Bit is cle | ared             | x = Bit is unki       | nown     |

| bit 15-14             | Unimplome                      | ntad. Dood oo '                        | <b>,</b>        |                  |                  |                       |          |

| bit 13                | -                              | nted: Read as '(                       |                 |                  | nnara Statua hi  |                       |          |

| DIL IO                |                                | Position Counter<br>IT ≥ QEIxGEC       | er Greater i Na |                  | npare Status DI  | ι                     |          |

|                       |                                | IT < QEIXGEC                           |                 |                  |                  |                       |          |

| bit 12                | PCHEQIEN:                      | Position Counter                       | er Greater Tha  | n or Equal Con   | npare Interrupt  | Enable bit            |          |

|                       | 1 = Interrupt                  |                                        |                 |                  |                  |                       |          |

|                       | 0 = Interrupt                  |                                        |                 |                  | o                |                       |          |

| bit 11                |                                | Position Counter<br>$T \leq QEIxLEC$   | er Less Than o  | r Equal Compa    | are Status bit   |                       |          |

|                       |                                | $T \ge QEIXLEC$                        |                 |                  |                  |                       |          |

| bit 10                | PCLEQIEN:                      | Position Counte                        | er Less Than o  | r Equal Compa    | re Interrupt En  | able bit              |          |

|                       | 1 = Interrupt                  |                                        |                 |                  |                  |                       |          |

|                       | 0 = Interrupt                  |                                        |                 |                  |                  |                       |          |

| bit 9                 |                                | Position Counter                       | er Overflow Sta | atus bit         |                  |                       |          |

|                       |                                | has occurred                           | d               |                  |                  |                       |          |

| bit 8                 |                                | Position Counte                        |                 | errupt Enable b  | bit              |                       |          |

|                       | 1 = Interrupt                  |                                        |                 | I                |                  |                       |          |

|                       | 0 = Interrupt                  |                                        |                 |                  |                  | <i></i>               |          |

| bit 7                 |                                | sition Counter (H                      | ÷.              | ation Process    | Complete Statu   | us bit <sup>(1)</sup> |          |

|                       |                                | IT was reinitializ                     |                 |                  |                  |                       |          |

| bit 6                 |                                | IT was not reinit<br>sition Counter (H |                 | ation Process    | Complete inter   | runt Enable bit       |          |

| DILO                  | 1 = Interrupt                  | -                                      | oming) mitianz  | auoniniocess     |                  |                       |          |

|                       | 0 = Interrupt                  |                                        |                 |                  |                  |                       |          |

| bit 5                 | VELOVIRQ:                      | Velocity Counter                       | r Overflow Sta  | tus bit          |                  |                       |          |

|                       |                                | has occurred                           |                 |                  |                  |                       |          |

|                       |                                | low has occurre                        |                 |                  | .,               |                       |          |

| bit 4                 |                                | Velocity Counte                        | r Overflow Inte | errupt Enable b  | It               |                       |          |

|                       | 1 = Interrupt<br>0 = Interrupt |                                        |                 |                  |                  |                       |          |

| bit 3                 | -                              | atus Flag for Ho                       | me Event Stat   | us bit           |                  |                       |          |

|                       |                                | ent has occurre                        |                 |                  |                  |                       |          |

|                       | 0 = No home                    | e event has occu                       | irred           |                  |                  |                       |          |

|                       |                                |                                        |                 |                  |                  |                       |          |

#### REGISTER 17-3: QEIxSTAT: QEIx STATUS REGISTER

**Note 1:** This status bit is only applicable to PIMOD<2:0> = 011 and 100 modes.

## **REGISTER 17-6: POSxHLD: POSITION COUNTER x HOLD REGISTER**

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | POSH  | LD<15:8>          |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | POSH  | ILD<7:0>          |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-0 **POSHLD<15:0>:** Holding Register for Reading and Writing POSxCNT bits

## REGISTER 17-7: VELxCNT: VELOCITY COUNTER x REGISTER

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |  |

|------------------------------------|-------|----------------|-------|-----------------------------------------|------------------|----------|-------|--|

|                                    |       |                | VELC  | NT<15:8>                                |                  |          |       |  |

| bit 15                             |       |                |       |                                         |                  |          | bit 8 |  |

|                                    |       |                |       |                                         |                  |          |       |  |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |  |

|                                    |       |                | VELC  | NT<7:0>                                 |                  |          |       |  |

| bit 7                              |       |                |       |                                         |                  |          | bit 0 |  |

|                                    |       |                |       |                                         |                  |          |       |  |

| Legend:                            |       |                |       |                                         |                  |          |       |  |

| R = Readable                       | bit   | W = Writable b | oit   | U = Unimpler                            | nented bit, read | d as '0' |       |  |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |

| L                                  |       |                |       |                                         |                  |          |       |  |

bit 15-0 VELCNT<15:0>: Velocity Counter x bits

NOTES:

# 22.1 CTMU Control Registers

## REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

| R/W-0                        | U-0          | R/W-0                                  | R/W-0          | R/W-0                | R/W-0                    | R/W-0                  | R/W-0  |

|------------------------------|--------------|----------------------------------------|----------------|----------------------|--------------------------|------------------------|--------|

| CTMUEN                       | _            | CTMUSIDL                               | TGEN           | EDGEN                | EDGSEQEN                 | IDISSEN <sup>(1)</sup> | CTTRIG |

| pit 15                       |              |                                        |                |                      |                          | L                      | bit 8  |

|                              |              |                                        |                |                      |                          |                        |        |

| U-0                          | U-0          | U-0                                    | U-0            | U-0                  | U-0                      | U-0                    | U-0    |

| —                            | —            | —                                      | —              | —                    | —                        | —                      | —      |

| pit 7                        |              |                                        |                |                      |                          |                        | bit (  |

| o er o ro d i                |              |                                        |                |                      |                          |                        |        |

| -egend:                      | , hit        | W - Writchlo h                         |                |                      | aantad hit raad          | aa '0'                 |        |

| R = Readable<br>n = Value at |              | W = Writable b<br>'1' = Bit is set     | It             | 0 = Onimplen         | nented bit, read         | x = Bit is unkn        |        |

| n = value at                 | PUR          | I = DILIS SEL                          |                |                      | areu                     |                        | JWII   |

| oit 15                       |              | TMU Enable bit                         |                |                      |                          |                        |        |

|                              | 1 = Module   |                                        |                |                      |                          |                        |        |

|                              | 0 = Module   |                                        |                |                      |                          |                        |        |

| oit 14                       | Unimpleme    | nted: Read as '0'                      |                |                      |                          |                        |        |

| oit 13                       | CTMUSIDL:    | CTMU Stop in Id                        | le Mode bit    |                      |                          |                        |        |

|                              |              | nues module ope                        |                | device enters lo     | lle mode                 |                        |        |

|                              | 0 = Continue | es module operat                       | ion in Idle mo | ode                  |                          |                        |        |

| pit 12                       | TGEN: Time   | Generation Enab                        | ole bit        |                      |                          |                        |        |

|                              |              | edge delay gene<br>s edge delay gene   |                |                      |                          |                        |        |

| pit 11                       |              | ge Enable bit                          |                |                      |                          |                        |        |

|                              | 1 = Hardwai  | re modules are us                      | sed to trigger | edges (TMRx,         | CTEDx, etc.)             |                        |        |

|                              | 0 = Software | e is used to trigge                    | r edges (mar   | nual set of EDG      | SXSTAT)                  |                        |        |

| pit 10                       | EDGSEQEN     | : Edge Sequence                        | e Enable bit   |                      |                          |                        |        |

|                              |              | event must occur                       |                | 2 event can oc       | cur                      |                        |        |

|                              | -            | e sequence is nee                      |                | (1)                  |                          |                        |        |

| bit 9                        |              | nalog Current Sou                      |                |                      |                          |                        |        |

|                              | •            | current source ou<br>current source ou |                |                      |                          |                        |        |

| oit 8                        | -            | Cx Trigger Contr                       |                | Janaca               |                          |                        |        |

|                              |              | riggers ADCx sta                       |                | n                    |                          |                        |        |

|                              |              | loes not trigger A                     |                |                      |                          |                        |        |

| oit 7-0                      |              | nted: Read as '0'                      |                |                      |                          |                        |        |

|                              |              |                                        |                | n n nito n i n n n t | the meetic all the state |                        |        |

|                              |              | ile Sample-and-H<br>on cycles. Any sc  |                |                      |                          |                        |        |

sample/conversion cycles. Any software using the ADCx as part of a capacitance measurement must discharge the ADCx capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADCx must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

#### CM4CON: OP AMP/COMPARATOR 4 CONTROL REGISTER (CONTINUED) REGISTER 26-3: EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits<sup>(2)</sup> bit 7-6 11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0) 10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0) If CPOL = 1 (inverted polarity): Low-to-high transition of the comparator output. If CPOL = 0 (non-inverted polarity): High-to-low transition of the comparator output. 01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity selected comparator output (while CEVT = 0) If CPOL = 1 (inverted polarity): High-to-low transition of the comparator output. If CPOL = 0 (non-inverted polarity): Low-to-high transition of the comparator output. 00 = Trigger/event/interrupt generation is disabled Unimplemented: Read as '0' bit 5 CREF: Comparator Reference Select bit (VIN+ input)<sup>(1)</sup> bit 4 1 = VIN+ input connects to internal CVREFIN voltage 0 = VIN+ input connects to C4IN1+ pin bit 3-2 Unimplemented: Read as '0' CCH<1:0>: Comparator Channel Select bits<sup>(1)</sup> bit 1-0 11 = VIN- input of comparator connects to OA3/AN6 10 = VIN- input of comparator connects to OA2/AN0 01 = VIN- input of comparator connects to OA1/AN3 00 = VIN- input of comparator connects to C4IN1-Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

2: After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator Event bit, CEVT (CMxCON<9>), and the Comparator Combined Interrupt Flag, CMPIF (IFS1<2>), **must be cleared** before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>). NOTES:

# 27.3 RTCC Registers

# **REGISTER 27-1:** RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup>

| R/W-0                | U-0                                                                                                                                    | R/W-0                             | R-0             | R-0                    | R/W-0            | R/W-0           | R/W-0   |  |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|------------------------|------------------|-----------------|---------|--|--|--|

| RTCEN <sup>(2)</sup> |                                                                                                                                        | RTCWREN                           | RTCSYNC         | HALFSEC <sup>(3)</sup> | RTCOE            | RTCPTR1         | RTCPTR0 |  |  |  |

| bit 15               |                                                                                                                                        |                                   |                 |                        |                  |                 | bit 8   |  |  |  |

|                      |                                                                                                                                        |                                   |                 |                        |                  |                 |         |  |  |  |

| R/W-0                | R/W-0                                                                                                                                  | R/W-0                             | R/W-0           | R/W-0                  | R/W-0            | R/W-0           | R/W-0   |  |  |  |

| CAL7                 | CAL6                                                                                                                                   | CAL5                              | CAL4            | CAL3                   | CAL2             | CAL1            | CAL0    |  |  |  |

| bit 7                |                                                                                                                                        |                                   |                 |                        |                  |                 | bit (   |  |  |  |

|                      |                                                                                                                                        |                                   |                 |                        |                  |                 |         |  |  |  |

| Legend:              |                                                                                                                                        |                                   |                 |                        |                  |                 |         |  |  |  |

| R = Readable         |                                                                                                                                        | W = Writable                      | bit             | •                      | nented bit, read | l as '0'        |         |  |  |  |

| -n = Value at F      | POR                                                                                                                                    | '1' = Bit is set                  |                 | '0' = Bit is clea      | ared             | x = Bit is unkr | nown    |  |  |  |

| h:+ 45               |                                                                                                                                        | C Enable bit <sup>(2)</sup>       |                 |                        |                  |                 |         |  |  |  |

| bit 15               |                                                                                                                                        | odule is enable                   |                 |                        |                  |                 |         |  |  |  |

|                      |                                                                                                                                        | odule is disable                  |                 |                        |                  |                 |         |  |  |  |

| bit 14               | Unimplemen                                                                                                                             | ted: Read as '                    | )'              |                        |                  |                 |         |  |  |  |

| bit 13               | RTCWREN:                                                                                                                               | RTCC Value Re                     | egister Write E | Enable bit             |                  |                 |         |  |  |  |

|                      | 1 = RTCVAL register can be written to by the user application                                                                          |                                   |                 |                        |                  |                 |         |  |  |  |

|                      | 0 = RTCVAL register is locked out from being written to by the user application                                                        |                                   |                 |                        |                  |                 |         |  |  |  |

| bit 12               | RTCSYNC: RTCC Value Register Read Synchronization bit                                                                                  |                                   |                 |                        |                  |                 |         |  |  |  |

|                      | <ul> <li>1 = A rollover is about to occur in 32 clock edges (approximately 1 ms)</li> <li>0 = A rollover will not occur</li> </ul>     |                                   |                 |                        |                  |                 |         |  |  |  |

| bit 11               | HALFSEC: Half-Second Status bit <sup>(3)</sup>                                                                                         |                                   |                 |                        |                  |                 |         |  |  |  |

| DIT II               | 1 = Second half period of a second                                                                                                     |                                   |                 |                        |                  |                 |         |  |  |  |

|                      | 0 = First half period of a second                                                                                                      |                                   |                 |                        |                  |                 |         |  |  |  |

| bit 10               | RTCOE: RTCC Output Enable bit                                                                                                          |                                   |                 |                        |                  |                 |         |  |  |  |

|                      | 1 = RTCC output is enabled                                                                                                             |                                   |                 |                        |                  |                 |         |  |  |  |

|                      | 0 = RTCC output is disabled                                                                                                            |                                   |                 |                        |                  |                 |         |  |  |  |

| bit 9-8              | RTCPTR<1:0>: RTCC Value Register Pointer bits<br>Points to the corresponding RTCC Value register when reading the RTCVAL register; the |                                   |                 |                        |                  |                 |         |  |  |  |

|                      |                                                                                                                                        | e correspondii<br>)> value decren |                 |                        |                  |                 |         |  |  |  |

| bit 7-0              | CAL<7:0>: RTCC Drift Calibration bits                                                                                                  |                                   |                 |                        |                  |                 |         |  |  |  |

|                      | 01111111 = Maximum positive adjustment; adds 508 RTCC clock pulses every one minute                                                    |                                   |                 |                        |                  |                 |         |  |  |  |

|                      | •                                                                                                                                      |                                   |                 |                        |                  |                 |         |  |  |  |

|                      | •                                                                                                                                      |                                   |                 |                        |                  |                 |         |  |  |  |

|                      | 00000001 = Minimum positive adjustment; adds 4 RTCC clock pulses every one minute                                                      |                                   |                 |                        |                  |                 |         |  |  |  |

|                      | 00000000 = No adjustment<br>1111111 = Minimum negative adjustment; subtracts 4 RTCC clock pulses every one minute                      |                                   |                 |                        |                  |                 |         |  |  |  |

|                      | •                                                                                                                                      | immuni nega                       | ave aujusuille  | ni, sudi acis 4 i      |                  | ises every offe | minute  |  |  |  |

|                      | •                                                                                                                                      |                                   |                 |                        |                  |                 |         |  |  |  |

|                      | •                                                                                                                                      |                                   |                 |                        |                  |                 |         |  |  |  |