Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm710-i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

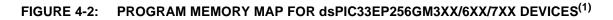

Note 1: Memory areas are not shown to scale.

2: On Reset, these bits are automatically copied into the device Configuration Shadow registers.

# 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory, program a row and to program two instruction words at a time. See Table 1 in the "dsPIC33EPXXXGM3XX/6XX/7XX Product Family" section for the page sizes of each device.

The Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of program memory, which consists of eight rows (512 instructions) at a time, and to program one row or two adjacent words at a time. The 8-row erase pages and single row write rows are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

For more information on erasing and programming Flash memory, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Flash Programming"** (DS70609).

# 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time), in Table 33-13.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change. Programmers can also program a row of data (64 instruction words/ 192 bytes) at a time using the row programming feature present in these devices. For row programming, the source data is fetched directly from the data memory (RAM) on these devices. Two new registers have been provided to point to the RAM location where the source data resides. The page that has the row to be programmed must first be erased before the programming operation.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Flash Programming"** (DS70609) for details and code examples on programming using RTSP.

# 5.4 Control Registers

Six SFRs are used to read and write the program Flash memory: NVMCON, NVMKEY, NVMADR, NVMADRU, NVMSRCADRL and NVMSRCADRH.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRU and NVMADR. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations, or the selected page for erase operations.

The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA.

The NVMSRCADRH and NVMSRCADRL registers are used to hold the source address of the data in the data memory that needs to be written to Flash memory.

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Secondary (Timer1) Oscillator (SOSC)                       | Secondary         | xx          | 100        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 00          | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

# REGISTER 16-19: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup> (CONTINUED)

- bit 1 SWAP: SWAP PWMxH and PWMxL Pins bit

- 1 = PWMxH output signal is connected to the PWMxL pins; PWMxL output signal is connected to the PWMxH pins

- 0 = PWMxH and PWMxL pins are mapped to their respective pins

- bit 0 OSYNC: Output Override Synchronization bit

- 1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWM time base

- 0 = Output overrides via the OVDDAT<1:0> bits occur on the next CPU clock boundary

- **Note 1:** These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

#### REGISTER 16-20: TRIGX: PWMX PRIMARY TRIGGER COMPARE VALUE REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | TRGCI | MP<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | TRGC  | MP<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in the local time base, this register contains the compare values that can trigger the ADCx module.

| U-0                   | U-0                            | HS, R/C-0                              | R/W-0           | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

|-----------------------|--------------------------------|----------------------------------------|-----------------|------------------|------------------|-----------------------|----------|

| _                     |                                | PCHEQIRQ                               | PCHEQIEN        | PCLEQIRQ         | PCLEQIEN         | POSOVIRQ              | POSOVIEN |

| bit 15                |                                |                                        |                 |                  |                  |                       | bit 8    |

|                       |                                |                                        |                 |                  |                  |                       |          |

| HS, R/C-0             | R/W-0                          | HS, R/C-0                              | R/W-0           | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

| PCIIRQ <sup>(1)</sup> | PCIIEN                         | VELOVIRQ                               | VELOVIEN        | HOMIRQ           | HOMIEN           | IDXIRQ                | IDXIEN   |

| bit 7                 |                                |                                        |                 |                  |                  |                       | bit 0    |

|                       |                                |                                        |                 |                  |                  |                       |          |

| Legend:               |                                | HS = Hardware                          |                 | C = Clearable    |                  |                       |          |

| R = Readable          |                                | W = Writable b                         | bit             |                  | nented bit, read |                       |          |

| -n = Value at         | POR                            | '1' = Bit is set                       |                 | '0' = Bit is cle | ared             | x = Bit is unki       | nown     |

| bit 15-14             | Unimplome                      | ntad. Dood oo '                        | <b>,</b>        |                  |                  |                       |          |

| bit 13                | -                              | nted: Read as '(                       |                 | n or Fauld Con   | nnara Statua hi  |                       |          |

| DIL IO                |                                | Position Counter<br>IT ≥ QEIxGEC       | er Greater i Na |                  | npare Status DI  | ι                     |          |

|                       |                                | IT < QEIXGEC                           |                 |                  |                  |                       |          |

| bit 12                | PCHEQIEN:                      | Position Counter                       | er Greater Tha  | n or Equal Con   | npare Interrupt  | Enable bit            |          |

|                       | 1 = Interrupt                  |                                        |                 |                  |                  |                       |          |

|                       | 0 = Interrupt                  |                                        |                 |                  | o                |                       |          |

| bit 11                |                                | Position Counter<br>$T \leq QEIxLEC$   | er Less Than o  | r Equal Compa    | are Status bit   |                       |          |

|                       |                                | $T \ge QEIXLEC$                        |                 |                  |                  |                       |          |

| bit 10                | PCLEQIEN:                      | Position Counte                        | er Less Than o  | r Equal Compa    | re Interrupt En  | able bit              |          |

|                       | 1 = Interrupt                  |                                        |                 |                  |                  |                       |          |

|                       | 0 = Interrupt                  |                                        |                 |                  |                  |                       |          |

| bit 9                 |                                | Position Counter                       | er Overflow Sta | atus bit         |                  |                       |          |

|                       |                                | has occurred                           | d               |                  |                  |                       |          |

| bit 8                 |                                | Position Counte                        |                 | errupt Enable b  | bit              |                       |          |

|                       | 1 = Interrupt                  |                                        |                 | I                |                  |                       |          |

|                       | 0 = Interrupt                  |                                        |                 |                  |                  | <i></i>               |          |

| bit 7                 |                                | sition Counter (H                      | ÷.              | ation Process    | Complete Statu   | us bit <sup>(1)</sup> |          |

|                       |                                | IT was reinitializ                     |                 |                  |                  |                       |          |

| bit 6                 |                                | IT was not reinit<br>sition Counter (H |                 | ation Process    | Complete inter   | runt Enable bit       |          |

| DILO                  | 1 = Interrupt                  | -                                      | oming) mitianz  | auoniniocess     |                  |                       |          |

|                       | 0 = Interrupt                  |                                        |                 |                  |                  |                       |          |

| bit 5                 | VELOVIRQ:                      | Velocity Counter                       | r Overflow Sta  | tus bit          |                  |                       |          |

|                       |                                | has occurred                           |                 |                  |                  |                       |          |

|                       |                                | low has occurre                        |                 |                  | .,               |                       |          |

| bit 4                 |                                | Velocity Counte                        | r Overflow Inte | errupt Enable b  | It               |                       |          |

|                       | 1 = Interrupt<br>0 = Interrupt |                                        |                 |                  |                  |                       |          |

| bit 3                 | -                              | atus Flag for Ho                       | me Event Stat   | us bit           |                  |                       |          |

|                       |                                | ent has occurre                        |                 |                  |                  |                       |          |

|                       | 0 = No home                    | e event has occu                       | irred           |                  |                  |                       |          |

|                       |                                |                                        |                 |                  |                  |                       |          |

#### REGISTER 17-3: QEIxSTAT: QEIx STATUS REGISTER

**Note 1:** This status bit is only applicable to PIMOD<2:0> = 011 and 100 modes.

# REGISTER 17-17: INTxTMRH: INTERVAL TIMERx HIGH WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | INTTM | R<31:24>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INTTM | R<23:16>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|                 |       |                  |       |                  |                 |                 |       |

bit 15-0 INTTMR<31:16>: High Word Used to Form 32-Bit Interval Timerx Register (INTxTMR) bits

### REGISTER 17-18: INTxTMRL: INTERVAL TIMERx LOW WORD REGISTER

| R/W-0 | R/W-0            | R/W-0       | R/W-0                                                       | R/W-0                                                                                              | R/W-0                                                                          | R/W-0                                                                                                                                                          |

|-------|------------------|-------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                  | INTTM       | IR<15:8>                                                    |                                                                                                    |                                                                                |                                                                                                                                                                |

|       |                  |             |                                                             |                                                                                                    |                                                                                | bit 8                                                                                                                                                          |

|       |                  |             |                                                             |                                                                                                    |                                                                                |                                                                                                                                                                |

| R/W-0 | R/W-0            | R/W-0       | R/W-0                                                       | R/W-0                                                                                              | R/W-0                                                                          | R/W-0                                                                                                                                                          |

|       |                  | INTT        | /IR<7:0>                                                    |                                                                                                    |                                                                                |                                                                                                                                                                |

|       |                  |             |                                                             |                                                                                                    |                                                                                | bit 0                                                                                                                                                          |

|       |                  |             |                                                             |                                                                                                    |                                                                                |                                                                                                                                                                |

|       |                  |             |                                                             |                                                                                                    |                                                                                |                                                                                                                                                                |

| bit   | W = Writable I   | bit         | U = Unimpler                                                | nented bit, rea                                                                                    | d as '0'                                                                       |                                                                                                                                                                |

| OR    | '1' = Bit is set |             | '0' = Bit is cle                                            | ared                                                                                               | x = Bit is unkr                                                                | nown                                                                                                                                                           |

|       | R/W-0            | R/W-0 R/W-0 | INTTM<br>R/W-0 R/W-0 R/W-0<br>INTTM<br>Dit W = Writable bit | INTTMR<15:8>           R/W-0         R/W-0         R/W-0           INTTMR<7:0>         INTTMR<7:0> | INTTMR<15:8>           R/W-0         R/W-0         R/W-0           INTTMR<7:0> | INTTMR<15:8>         R/W-0       R/W-0       R/W-0       R/W-0         INTTMR<7:0>         Dit       W = Writable bit       U = Unimplemented bit, read as '0' |

bit 15-0 INTTMR<15:0>: Low Word Used to Form 32-Bit Interval Timerx Register (INTxTMR) bits

# 21.0 CONTROLLER AREA NETWORK (CAN) MODULE (dsPIC33EPXXXGM6XX/7XX DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Enhanced Controller Area Network (ECAN™)" (DS70353), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

### 21.1 Overview

The Controller Area Network (CAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/ protocol was designed to allow communications within noisy environments. The dsPIC33EPXXXGM6XX/7XX devices contain two CAN modules.

The CAN module is a communication controller, implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details. The CAN module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and Extended Data Frames

- 0-8 Bytes of Data Length

- Programmable Bit Rate, up to 1 Mbit/sec

- Automatic Response to Remote Transmission Requests

- Up to 8 Transmit Buffers with Application Specified Prioritization and Abort Capability (each buffer can contain up to 8 bytes of data)

- Up to 32 Receive Buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 Full (Standard/Extended Identifier) Acceptance Filters

- Three Full Acceptance Filter Masks

- DeviceNet<sup>™</sup> Addressing Support

- Programmable Wake-up Functionality with Integrated Low-Pass Filter

- Programmable Loopback mode supports Self-Test Operation

- Signaling via Interrupt Capabilities for all CAN Receiver and Transmitter Error States

- · Programmable Clock Source

- Programmable Link to Input Capture 2 (IC2) module for Timestamping and Network Synchronization

- · Low-Power Sleep and Idle modes

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

| U-0                     | U-0             | R-0                                  | R-0            | R-0                            | R-0                | R-0              | R-0   |

|-------------------------|-----------------|--------------------------------------|----------------|--------------------------------|--------------------|------------------|-------|

| _                       |                 | ТХВО                                 | TXBP           | RXBP                           | TXWAR              | RXWAR            | EWARN |

| bit 15                  |                 |                                      |                |                                |                    |                  | bit 8 |

|                         |                 |                                      |                |                                |                    |                  |       |

| R/C-0                   | R/C-0           | R/C-0                                | U-0            | R/C-0                          | R/C-0              | R/C-0            | R/C-0 |

| IVRIF                   | WAKIF           | ERRIF                                | —              | FIFOIF                         | RBOVIF             | RBIF             | TBIF  |

| bit 7                   |                 |                                      |                |                                |                    |                  | bit 0 |

|                         |                 | 0                                    |                | 1                              |                    |                  |       |

| Legend:<br>R = Readable | <b>b</b> :4     |                                      | -              |                                | n to clear the bit |                  |       |

| -n = Value at F         |                 | W = Writable<br>'1' = Bit is set     |                | 0 = Unimple<br>0' = Bit is cle | mented bit, read   | x = Bit is unki  |       |

|                         | -OK             | I – DILIS SEL                        |                |                                | areu               | x – Dit is uliki | IOWIT |

| bit 15-14               | Unimplemen      | ted: Read as '                       | י)             |                                |                    |                  |       |

| bit 13                  | -               | mitter in Error S                    |                | bit                            |                    |                  |       |

|                         |                 | er is in Bus Off                     |                |                                |                    |                  |       |

|                         | 0 = Transmitte  | er is not in Bus                     | Off state      |                                |                    |                  |       |

| bit 12                  | TXBP: Transr    | mitter in Error S                    | State Bus Pas  | sive bit                       |                    |                  |       |

|                         |                 | er is in Bus Pa                      |                |                                |                    |                  |       |

| L:1 44                  |                 | er is not in Bus                     |                |                                |                    |                  |       |

| bit 11                  |                 | ver in Error Sta<br>is in Bus Passi  |                | /e dit                         |                    |                  |       |

|                         |                 | is not in Bus Passi                  |                |                                |                    |                  |       |

| bit 10                  |                 | nsmitter in Erro                     |                | na bit                         |                    |                  |       |

|                         |                 | er is in Error W                     |                | 5                              |                    |                  |       |

|                         | 0 = Transmitte  | er is not in Erro                    | or Warning sta | ite                            |                    |                  |       |

| bit 9                   | RXWAR: Rec      | eiver in Error S                     | State Warning  | bit                            |                    |                  |       |

|                         |                 | is in Error War                      |                |                                |                    |                  |       |

| <b>h</b> # 0            |                 | is not in Error \                    | •              | Ctata Manaina                  | <b>b</b> :4        |                  |       |

| bit 8                   |                 | nsmitter or Rec<br>er or receiver is |                | •                              | DIT                |                  |       |

|                         |                 | er or receiver is                    |                |                                |                    |                  |       |

| bit 7                   |                 | Message Inter                        |                | 5                              |                    |                  |       |

|                         |                 | request has occ                      |                |                                |                    |                  |       |

|                         | •               | request has not                      |                |                                |                    |                  |       |

| bit 6                   |                 | Wake-up Activi                       | , ,            | ag bit                         |                    |                  |       |

|                         |                 | request has occ                      |                |                                |                    |                  |       |

| hit E                   | -               | request has not                      |                | ouroop in CvIN                 | TE<12.95 ragio     | tor)             |       |

| bit 5                   |                 | request has occ                      |                | Jurces in Cxin                 | TF<13:8> regis     | ler)             |       |

|                         |                 | request has not                      |                |                                |                    |                  |       |

| bit 4                   | •               | ted: Read as '                       |                |                                |                    |                  |       |

| bit 3                   | -               | Almost Full In                       |                | it                             |                    |                  |       |

|                         | 1 = Interrupt r | equest has occ                       | curred         |                                |                    |                  |       |

|                         |                 | request has not                      |                |                                |                    |                  |       |

| bit 2                   |                 | Buffer Overflow                      | •              | ig bit                         |                    |                  |       |

|                         |                 | request has occ                      |                |                                |                    |                  |       |

|                         | 0 = interrupt r | request has not                      | occurred       |                                |                    |                  |       |

# REGISTER 21-6: CXINTF: CANX INTERRUPT FLAG REGISTER

# 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Charge Time Measurement Unit (CTMU)" (DS70661), which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- · Four edge input trigger sources

- · Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · Precise time measurement resolution of 1 ns

- Accurate current source suitable for capacitive measurement

- On-chip temperature measurement using a built-in diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUCON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

| r-0            | r-0                                                                                                          | r-0                                                                     | r-0                                                           | R-0                          | R-0              | R-0             | R-0   |

|----------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------|------------------|-----------------|-------|

| r              | r                                                                                                            | r                                                                       | r                                                             | SLOT3                        | SLOT2            | SLOT1           | SLOT0 |

| bit 15         |                                                                                                              |                                                                         |                                                               |                              |                  |                 | bit   |

| r-0            | r-0                                                                                                          | r-0                                                                     | r-0                                                           | R-0                          | R-0              | R-0             | R-0   |

| r              | r                                                                                                            | r                                                                       | r                                                             | ROV                          | RFUL             | TUNF            | TMPTY |

| bit 7          |                                                                                                              |                                                                         |                                                               |                              |                  |                 | bit   |

| Legend:        |                                                                                                              | r = Reserved                                                            | bit                                                           |                              |                  |                 |       |

| R = Readab     | le bit                                                                                                       | W = Writable                                                            | bit                                                           | U = Unimpler                 | mented bit, rea  | d as '0'        |       |

| -n = Value a   | t POR                                                                                                        | '1' = Bit is set                                                        | :                                                             | '0' = Bit is cle             |                  | x = Bit is unkr | nown  |

|                | 1111 = Slot 1<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | is currently ac<br>is currently ac<br>is currently ac                   | ctive<br>ctive                                                |                              |                  |                 |       |

| bit 7-4        | Reserved: Re                                                                                                 |                                                                         |                                                               |                              |                  |                 |       |

| bit 3<br>bit 2 | 0 = A receive<br><b>RFUL:</b> Receiv<br>1 = New data                                                         | overflow has o<br>overflow has r<br>ve Buffer Full S<br>is available in | occurred for a<br>not occurred<br>Status bit<br>the Receive i | t least one Rec<br>registers | eive register    |                 |       |

| bit 1          | 0 = The Rece<br>TUNF: Transr<br>1 = A transmit<br>0 = A transmit                                             | nit Buffer Under<br>t underflow ha                                      | erflow Status<br>s occurred for                               | r at least one Tr            | ransmit register | r               |       |

| bit 0          | <b>TMPTY:</b> Trans<br>1 = The Trans<br>0 = The Trans                                                        | smit Buffer Err<br>smit registers a                                     | ipty Status bit<br>are empty                                  | -                            |                  |                 |       |

# REGISTER 24-4: DCISTAT: DCI STATUS REGISTER

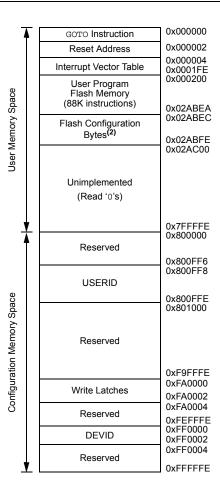

| PTG Output<br>Number | PTG Output Description                   |

|----------------------|------------------------------------------|

| PTGO0                | Trigger/Synchronization Source for OC1   |

| PTGO1                | Trigger/Synchronization Source for OC2   |

| PTGO2                | Trigger/Synchronization Source for OC3   |

| PTGO3                | Trigger/Synchronization Source for OC4   |

| PTGO4                | Clock Source for OC1                     |

| PTGO5                | Clock Source for OC2                     |

| PTGO6                | Clock Source for OC3                     |

| PTGO7                | Clock Source for OC4                     |

| PTGO8                | Trigger/Synchronization Source for IC1   |

| PTGO9                | Trigger/Synchronization Source for IC2   |

| PTGO10               | Trigger/Synchronization Source for IC3   |

| PTGO11               | Trigger/Synchronization Source for IC4   |

| PTGO12               | Sample Trigger for ADC                   |

| PTGO13               | Sample Trigger for ADC                   |

| PTGO14               | Sample Trigger for ADC                   |

| PTGO15               | Sample Trigger for ADC                   |

| PTGO16               | PWM Time Base Synchronous Source for PWM |

| PTGO17               | PWM Time Base Synchronous Source for PWM |

| PTGO18               | Mask Input Select for Op Amp/Comparator  |

| PTGO19               | Mask Input Select for Op Amp/Comparator  |

| PTGO20               | Reserved                                 |

| PTGO21               | Reserved                                 |

| PTGO22               | Reserved                                 |

| PTGO23               | Reserved                                 |

| PTGO24               | Reserved                                 |

| PTGO25               | Reserved                                 |

| PTGO26               | Reserved                                 |

| PTGO27               | Reserved                                 |

| PTGO28               | Reserved                                 |

| PTGO29               | Reserved                                 |

| PTGO30               | PTG Output to PPS Input Selection        |

| PTGO31               | PTG Output to PPS Input Selection        |

## TABLE 25-2: PTG OUTPUT DESCRIPTIONS

### 26.1 Op Amp Application Considerations

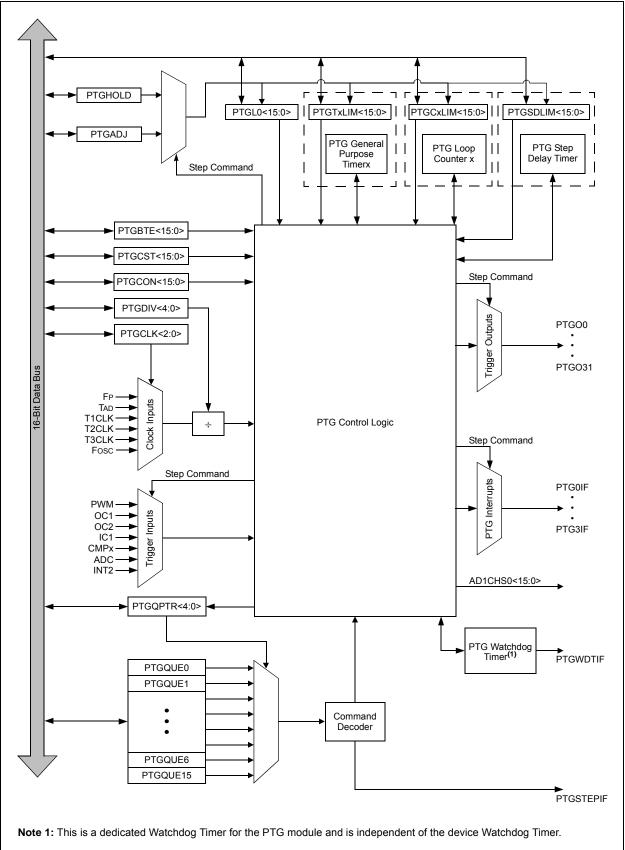

There are two configurations to take into consideration when designing with the op amp modules that are available in the dsPIC33EPXXXGM3XX/6XX/7XX devices. Configuration A (see Figure 26-5) takes advantage of the internal connection to the ADCx module to route the output of the op amp directly to the ADCx for measurement. Configuration B (see Figure 26-6) requires that the designer externally route the output of the op amp (OAxOUT) to a separate analog input pin (ANy) on the device. Table 33-53 in **Section 33.0 "Electrical Characteristics**" describes the performance characteristics for the op amps, distinguishing between the two configuration types where applicable.

### 26.1.1 OP AMP CONFIGURATION A

Figure 26-5 shows a typical inverting amplifier circuit taking advantage of the internal connections from the op amp output to the input of the ADCx. The advantage of this configuration is that the user does not need to consume another analog input (ANy) on the device, and allows the user to simultaneously sample all three op amps with the ADCx module, if needed. However, the presence of the internal resistance, RINT1, adds an error in the feedback path. Since RINT1 is an internal resistance, in relation to the op amp output (VOAXOUT) and ADCx internal connection (VADC), RINT1 must be included in the numerator term of the transfer function. See Table 33-52 in Section 33.0 "Electrical Characteristics" for the typical value of RINT1. Table 33-57 and Table 33-58 in Section 33.0 "Electrical Characteristics" describe the minimum sample time (TSAMP) requirements for the ADCx module in this configuration. Figure 26-5 also defines the equations that should be used when calculating the expected voltages at points, VADC and VOAXOUT.

### FIGURE 26-5: OP AMP CONFIGURATION A

Note 1: See Table 33-56 for the Typical value.

- 2: See Table 33-52 for the Minimum value for the feedback resistor.

- 3: See Table 33-59 and Table 33-60 for the Minimum Sample Time (TSAMP).

- 4: CVREF10 or CVREF20 are two options that are available for supplying bias voltage to the op amps.

| DC CHARACT    | ERISTICS                   |      |       | •          | ns: 3.0V to 3.6V<br>≤ Ta ≤ +85°C for Ind<br>≤ Ta ≤ +125°C for E: |           |  |  |

|---------------|----------------------------|------|-------|------------|------------------------------------------------------------------|-----------|--|--|

| Param.        | Typ. <sup>(2)</sup>        | Max. | Units | Conditions |                                                                  |           |  |  |

| Operating Cur | rrent (IDD) <sup>(1)</sup> |      |       | •          |                                                                  |           |  |  |

| DC20d         | 6.0                        | 18.0 | mA    | -40°C      |                                                                  |           |  |  |

| DC20a         | 6.0                        | 18.0 | mA    | +25°C      | 2.21/                                                            |           |  |  |

| DC20b         | 6.0                        | 18.0 | mA    | +85°C      | - 3.3V                                                           | 10 MIPS   |  |  |

| DC20c         | 6.0                        | 18.0 | mA    | +125°C     |                                                                  |           |  |  |

| DC21d         | 11.0                       | 20.0 | mA    | -40°C      |                                                                  |           |  |  |

| DC21a         | 11.0                       | 20.0 | mA    | +25°C      | - 3.3V                                                           | 20 MIPS   |  |  |

| DC21b         | 11.0                       | 20.0 | mA    | +85°C      |                                                                  | 20 101173 |  |  |

| DC21c         | 11.0                       | 20.0 | mA    | +125°C     |                                                                  |           |  |  |

| DC22d         | 17.0                       | 30.0 | mA    | -40°C      |                                                                  |           |  |  |

| DC22a         | 17.0                       | 30.0 | mA    | +25°C      | 2.21/                                                            |           |  |  |

| DC22b         | 17.0                       | 30.0 | mA    | +85°C      | - 3.3V                                                           | 40 MIPS   |  |  |

| DC22c         | 17.0                       | 30.0 | mA    | +125°C     |                                                                  |           |  |  |

| DC23d         | 25.0                       | 50.0 | mA    | -40°C      |                                                                  |           |  |  |

| DC23a         | 25.0                       | 50.0 | mA    | +25°C      | 2.21/                                                            |           |  |  |

| DC23b         | 25.0                       | 50.0 | mA    | +85°C      | - 3.3V                                                           | 60 MIPS   |  |  |

| DC23c         | 25.0                       | 50.0 | mA    | +125°C     |                                                                  |           |  |  |

| DC24d         | 30.0                       | 60.0 | mA    | -40°C      |                                                                  |           |  |  |

| DC24a         | 30.0                       | 60.0 | mA    | +25°C      | 3.3V                                                             | 70 MIPS   |  |  |

| DC24b         | 30.0                       | 60.0 | mA    | +85°C      |                                                                  |           |  |  |

### TABLE 33-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as outputs and driving low

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- · CPU executing

- while(1)

- { NOP();

- }

- · JTAG is disabled

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

| DC CHARACTERISTICS |        |                                         | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |   |    |    |                                                                                                                                               |  |  |

|--------------------|--------|-----------------------------------------|-------------------------------------------------------|---|----|----|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic                          | Min. Typ. Max. Units Conditions                       |   |    |    |                                                                                                                                               |  |  |

|                    | liL    | Input Leakage Current <sup>(1,2)</sup>  |                                                       |   |    |    |                                                                                                                                               |  |  |

| DI50               |        | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1                                                    | — | +1 | μA | $Vss \le VPIN \le 5V$ ,<br>Pin at high-impedance                                                                                              |  |  |

| DI51               |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _ | +1 | μA | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ Pin \text{ at high-impedance}, \\ -40^\circC \leq TA \leq +85^\circC \end{array}$ |  |  |

| DI51a              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _ | +1 | μA | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +85^{\circ}C$                                                 |  |  |

| DI51b              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _ | +1 | μA | Vss $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance,<br>-40°C $\leq$ TA $\leq$ +125°C                                                        |  |  |

| DI51c              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _ | +1 | μA | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +125^{\circ}C$                                                |  |  |

| DI55               |        | MCLR                                    | -5                                                    | — | +5 | μA | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                      |  |  |

| DI56               |        | OSC1                                    | -5                                                    | — | +5 | μA | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$                                     |  |  |

#### TABLE 33-10: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- **5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

| AC CHA       | AC CHARACTERISTICS |                                                                                    |                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                  |                   |                               |  |  |

|--------------|--------------------|------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|-------------------------------|--|--|

| Param<br>No. | Symb               | Characteristic                                                                     | Min.              | Тур. <sup>(1)</sup>                                                                                                                                                                                                                                                                   | Max.             | Units             | Conditions                    |  |  |

| OS10         | FIN                | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                | —                                                                                                                                                                                                                                                                                     | 60               | MHz               | EC                            |  |  |

|              |                    | Oscillator Crystal Frequency                                                       | 3.5<br>10<br>32.4 | <br>32.768                                                                                                                                                                                                                                                                            | 10<br>25<br>33.1 | MHz<br>MHz<br>kHz | XT<br>HS<br>SOSC              |  |  |

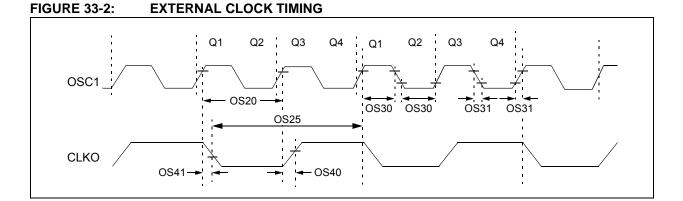

| OS20         | Tosc               | Tosc = 1/Fosc                                                                      | 8.33              | _                                                                                                                                                                                                                                                                                     | DC               | ns                | TA = +125°C                   |  |  |

|              |                    | Tosc = 1/Fosc                                                                      | 7.14              | _                                                                                                                                                                                                                                                                                     | DC               | ns                | TA = +85°C                    |  |  |

| OS25         | Тсү                | Instruction Cycle Time <sup>(2)</sup>                                              | 16.67             |                                                                                                                                                                                                                                                                                       | DC               | ns                | TA = +125°C                   |  |  |

|              |                    |                                                                                    | 14.28             |                                                                                                                                                                                                                                                                                       | DC               | ns                | TA = +85°C                    |  |  |

| OS30         | TosL,<br>TosH      | External Clock in (OSC1)<br>High or Low Time                                       | 0.375 x Tosc      | —                                                                                                                                                                                                                                                                                     | 0.625 x Tosc     | ns                | EC                            |  |  |

| OS31         | TosR,<br>TosF      | External Clock in (OSC1)<br>Rise or Fall Time                                      | —                 | —                                                                                                                                                                                                                                                                                     | 20               | ns                | EC                            |  |  |

| OS40         | TckR               | CLKO Rise Time <sup>(3)</sup>                                                      | —                 | 5.2                                                                                                                                                                                                                                                                                   | _                | ns                |                               |  |  |

| OS41         | TckF               | CLKO Fall Time <sup>(3)</sup>                                                      | —                 | 5.2                                                                                                                                                                                                                                                                                   | _                | ns                |                               |  |  |

| OS42         | Gм                 | External Oscillator<br>Transconductance <sup>(4)</sup>                             | —                 | 12                                                                                                                                                                                                                                                                                    | —                | mA/V              | HS, VDD = 3.3V,<br>TA = +25°C |  |  |

|              |                    |                                                                                    | —                 | 6                                                                                                                                                                                                                                                                                     | —                | mA/V              | XT, VDD = 3.3V,<br>TA = +25°C |  |  |

### TABLE 33-16: EXTERNAL CLOCK TIMING REQUIREMENTS

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- 2: Instruction cycle period (TCY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Minimum" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Maximum" cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: This parameter is characterized, but not tested in manufacturing.

NOTES:

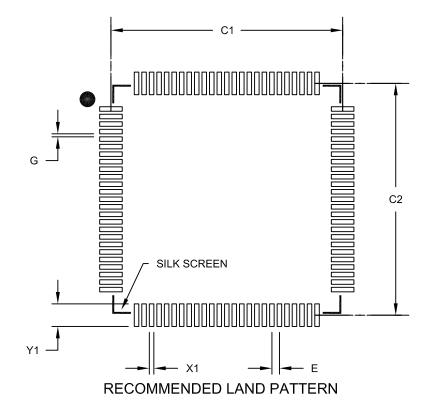

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                     |    | MILLIMETERS |          |      |  |

|---------------------------|----|-------------|----------|------|--|

| Dimension Limits          |    | MIN         | NOM      | MAX  |  |

| Contact Pitch             | E  |             | 0.50 BSC |      |  |

| Contact Pad Spacing       | C1 |             | 15.40    |      |  |

| Contact Pad Spacing       | C2 |             | 15.40    |      |  |

| Contact Pad Width (X100)  | X1 |             |          | 0.30 |  |

| Contact Pad Length (X100) | Y1 |             |          | 1.50 |  |

| Distance Between Pads     | G  | 0.20        |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B

# APPENDIX A: REVISION HISTORY

### **Revision A (February 2013)**

This is the initial released version of this document.

### Revision B (June 2013)

Changes to Section 5.0 "Flash Program Memory", Register 5-1. Changes to Section 6.0 "Resets", Figure 6-1. Changes to Section 26.0 "Op Amp/Comparator Module", Register 26-2. Updates to most of the tables in Section 33.0 "Electrical Characteristics". Minor text edits throughout the document.

### **Revision C (September 2013)**

Changes to Figure 23-1. Changes to Figure 26-2. Changes to Table 30-2. Changes to Section 33.0 "Electrical Characteristics". Added Section 34.0 "High-Temperature Electrical Characteristics" to the data sheet. Minor typographical edits throughout the document.

### **Revision D (August 2014)**

This revision incorporates the following updates:

- Sections:

- Updated Section 2.0 "Guidelines for Getting Started with 16-Bit Digital Signal Controllers", Section 8.0 "Direct Memory Access (DMA)", Section 10.3 "Doze Mode", Section 21.0 "Controller Area Network (CAN) Module (dsPIC33EPXXXGM6XX/7XX Devices Only)", Section 23.0 "10-Bit/12-Bit Analog-to-Digital Converter (ADC)", Section 23.1.2 "12-Bit ADCx Configuration", Section 21.4 "CAN Message Buffers", Section 35.0 "Packaging Information"

- · Figures:

- Updated **"Pin Diagrams"**, Figure 1-1, Figure 9-1

- · Registers:

- Updated Register 5-1, Register 8-2, Register 21-1, Register 23-2

- · Tables:

- Updated Table 1-1, Table 7-1, Table 8-1, Table 34-9, Table 1, Table 4-2, Table 4-3, Table 4-25, Table 4-33, Table 4-34, Table 4-39, Table 4-30, Table 4-46, Table 4-47, Table 33-16, Table 34-8