Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT   |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | -                                                                                 |

| Data Converters            | A/D 49x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 121-TFBGA                                                                         |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep256gm710t-i-bg |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Ref-erence Manual"*, which are available from the Microchip web site (www.microchip.com). These documents should be considered as the general reference for the operation of a particular module or device feature.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70000600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70000598)

- "Timers" (DS70362)

- "Input Capture" (DS70000352)

- "Output Compare" (DS70005157)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582)

- "Serial Peripheral Interface (SPI)" (DS70005185)

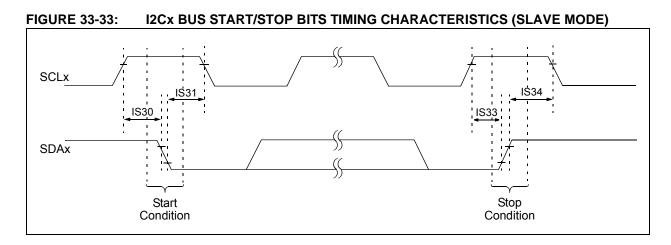

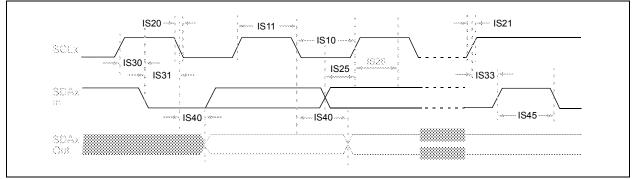

- "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70000195)

- "Data Converter Interface (DCI) Module" (DS70356)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70000357)

- "32-Bit Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Parallel Master Port (PMP)" (DS70576)

- "Device Configuration" (DS70000618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

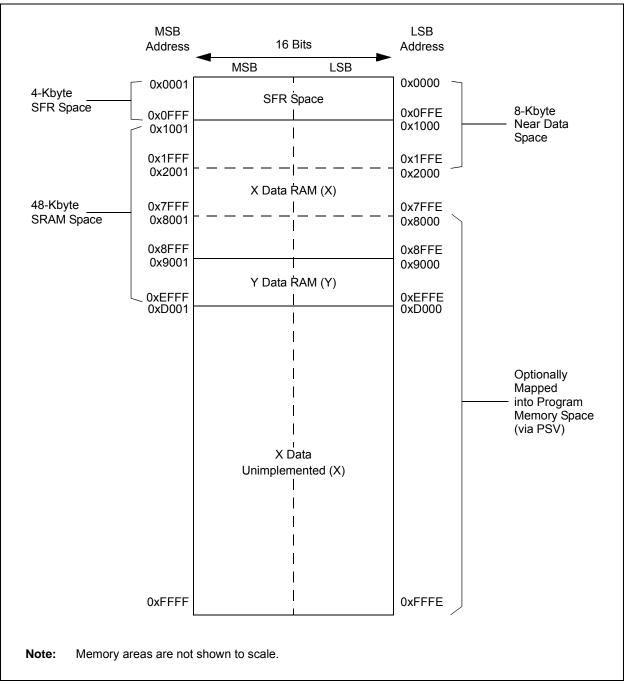

#### FIGURE 4-7: DATA MEMORY MAP FOR 512-KBYTE DEVICES

| IABLE 4     | 4-0:  | 00     | IPUIC                               |          |         | SIER W  | AP      |       |            |             |               |        |          |          |          |          |          |               |

|-------------|-------|--------|-------------------------------------|----------|---------|---------|---------|-------|------------|-------------|---------------|--------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14                              | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8      | Bit 7       | Bit 6         | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| OC1CON1     | 0900  | _      | —                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | ENFLTB     | ENFLTA      | —             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2     | 0902  | FLTMD  | FLTOUT                              | FLTTRIEN | OCINV   | —       | _       | _     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS       | 0904  |        |                                     |          |         |         |         | Ou    | Itput Comp | are 1 Seco  | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC1R        | 0906  |        |                                     |          |         |         |         |       | Output     | Compare 7   | 1 Register    |        |          |          |          |          |          | xxxx          |

| OC1TMR      | 0908  |        |                                     |          |         |         |         | Out   | tput Comp  | are 1 Time  | r Value Regis | ster   |          |          |          |          |          | xxxx          |

| OC2CON1     | 090A  | _      | —                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | ENFLTB     | ENFLTA      | -             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC2CON2     | 090C  | FLTMD  | FLTOUT                              | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS       | 090E  |        |                                     |          |         |         |         | Ou    | Itput Comp | oare 2 Seco | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC2R        | 0910  |        |                                     |          |         |         |         |       | Output     | Compare 2   | 2 Register    |        |          |          |          |          |          | xxxx          |

| OC2TMR      | 0912  |        |                                     |          |         |         | -       | Ou    | tput Comp  | are 2 Time  | r Value Regis | ster   |          | -        |          |          |          | xxxx          |

| OC3CON1     | 0914  | —      | _                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2     | 0916  | FLTMD  | FLTOUT                              | FLTTRIEN | OCINV   | _       | —       | _     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS       | 0918  |        | Output Compare 3 Secondary Register |          |         |         |         |       |            |             |               |        |          | xxxx     |          |          |          |               |

| OC3R        | 091A  |        |                                     |          |         |         |         |       |            |             |               |        |          |          | xxxx     |          |          |               |

| OC3TMR      | 091C  |        |                                     |          |         |         | -       | Ou    | tput Comp  | are 3 Time  | r Value Regis | ster   |          | -        |          |          |          | xxxx          |

| OC4CON1     | 091E  | —      | _                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC4CON2     | 0920  | FLTMD  | FLTOUT                              | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC4RS       | 0922  |        |                                     |          |         |         |         | Ou    | tput Comp  | oare 4 Seco | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC4R        | 0924  |        |                                     |          |         |         |         |       | Output     | Compare 4   | 4 Register    |        |          |          |          |          |          | xxxx          |

| OC4TMR      | 0926  |        |                                     |          |         |         |         | Ou    | tput Comp  | are 4 Time  | r Value Regis | ster   |          |          |          |          |          | xxxx          |

| OC5CON1     | 0928  |        | _                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC5CON2     | 092A  | FLTMD  | FLTOUT                              | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC5RS       | 092C  |        |                                     |          |         |         |         | Ou    | tput Comp  | are 5 Seco  | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC5R        | 092E  |        |                                     |          |         |         |         |       | Output     | Compare &   | 5 Register    |        |          |          |          |          |          | xxxx          |

| OC5TMR      | 0930  |        |                                     |          |         |         |         | Ou    | tput Comp  | are 5 Time  | r Value Regis | ster   |          |          |          |          |          | xxxx          |

| OC6CON1     | 0932  | —      | —                                   | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC6CON2     | 0934  | FLTMD  | FLTOUT                              | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC6RS       | 0936  |        |                                     |          |         |         |         | Ou    | <u> </u>   |             | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC6R        | 0938  |        |                                     |          |         |         |         |       | Output     | Compare 6   | 6 Register    |        |          |          |          |          |          | xxxx          |

| OC6TMR      | 093A  |        |                                     |          |         |         |         | Out   | tput Comp  | are 6 Time  | r Value Regis | ster   |          |          |          |          |          | xxxx          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4-28: CAN2 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FOR dsPIC33EPXXXGM60X/7XX DEVICES <sup>(1)</sup> (CONTINUED | <b>TABLE 4-28</b> : | CAN2 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FO | )R dsPIC33EPXXXGM60X/7XX DEVICES <sup>(1)</sup> (CONTINUED) |

|--------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------|-------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------|-------------------------------------------------------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|----------|-------|-------|-------|-------|-------|-------|-------|---------------|

| C2RXF11SID  | 056C  | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | _     | EXIDE | —     | EID17 | EID16 | xxxx          |

| C2RXF11EID  | 056E  |        |        |        |        |        |        |       | E     | ID<15:0> |       |       |       |       |       |       |       | xxxx          |

| C2RXF12SID  | 0570  | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | _     | MIDE  | _     | EID17 | EID16 | xxxx          |

| C2RXF12EID  | 0572  |        |        |        |        |        |        |       | E     | ID<15:0> |       |       |       |       |       |       |       | xxxx          |

| C2RXF13SID  | 0574  | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | —     | MIDE  | —     | EID17 | EID16 | xxxx          |

| C2RXF13EID  | 0576  |        |        |        |        |        |        |       | E     | ID<15:0> |       |       |       |       |       |       |       | xxxx          |

| C2RXF14SID  | 0578  | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | —     | MIDE  | —     | EID17 | EID16 | xxxx          |

| C2RXF14EID  | 057A  |        |        |        |        |        |        |       | E     | ID<15:0> |       |       |       |       |       |       |       | xxxx          |

| C2RXF15SID  | 057C  | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | —     | MIDE  | _     | EID17 | EID16 | xxxx          |

| C2RXF15EID  | 057E  |        |        |        |        |        |        |       | E     | ID<15:0> |       |       |       |       |       |       |       | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers are not present on dsPIC33EPXXXGM3XX devices.

## TABLE 4-29: PROGRAMMABLE CRC REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14                       | Bit 14     Bit 13     Bit 12     Bit 11     Bit 10     Bit 90     Bit 8     Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2     Bit 1     Bit 0     Res       -     CSIDL     VWORD4     VWORD3     VWORD2     VWORD1     VWORD0     CRCFUL     CRCMPT     CRCISEL     CRCG0     LENDIAN     -     -     -     000       -     -     DWIDTH4     DWIDTH3     DWIDTH2     DWIDTH1     DWIDTH0     -     -     -     PLEN4     PLEN2     PLEN1     PLEN0     000       -     -     DWIDTH4     DWIDTH3     DWIDTH1     DWIDTH0     -     -     -     -     -     000       -     -     -     Statistics     -     -     -     -     -     -     000       -     -     -     -     -     -     -     -     -     -     000       -     -     -     -     -     -     -     -     -     000       -     -     -     -     -     -     -     -     -     -     000 |         |         |         |         |               |            |         |         |       |         | All<br>Resets |       |       |      |

|-------------|-------|--------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------------|------------|---------|---------|-------|---------|---------------|-------|-------|------|

| CRCCON1     | 0640  | CRCEN  | —                            | CSIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VWORD4  | VWORD3  | VWORD2  | VWORD1  | VWORD0        | CRCFUL     | CRCMPT  | CRCISEL | CRCGO | LENDIAN | —             | —     | —     | 0000 |

| CRCCON2     | 0642  | _      | _                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DWIDTH4 | DWIDTH3 | DWIDTH2 | DWIDTH1 | DWIDTH0       | _          | _       | _       | PLEN4 | PLEN3   | PLEN2         | PLEN1 | PLEN0 | 0000 |

| CRCXORL     | 0644  |        |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |         |         |         |               |            |         |         |       | 0000    |               |       |       |      |

| CRCXORH     | 0646  |        |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |         |         |         |               |            |         |         |       |         | 0000          |       |       |      |

| CRCDATL     | 0648  |        |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |         |         | CRC E   | Data Input Lo | w Word Re  | egister |         |       |         |               |       |       | 0000 |

| CRCDATH     | 064A  |        |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |         |         | CRC D   | ata Input Hi  | gh Word Re | egister |         |       |         |               |       |       | 0000 |

| CRCWDATL    | 064C  |        |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |         |         | CRC     | Result Low    | Word Regi  | ster    |         |       |         |               |       |       | 0000 |

| CRCWDATH    | 064E  |        | CRC Result Low Word Register |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |         |         |         |               |            |         |         |       | 0000    |               |       |       |      |

**Legend:** — = unimplemented, read as '0'. Shaded bits are not used in the operation of the programmable CRC module.

| IABLE 4     | 4-33: | PERI   | PHERA  | L PIN 3 | ELECI  | INPUT      | <b>KEGISI</b> |       | , FOK q | SPIC33         |       |       |       | ICE3       |          |       |       |               |

|-------------|-------|--------|--------|---------|--------|------------|---------------|-------|---------|----------------|-------|-------|-------|------------|----------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11     | Bit 10        | Bit 9 | Bit 8   | Bit 7          | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| RPINR0      | 06A0  | _      |        |         |        | INT1R<6:0> | >             |       |         | —              | —     | _     | _     | _          | _        | _     | _     | 0000          |

| RPINR1      | 06A2  | —      | —      | —       | _      | —          | —             | _     | _       | —              |       |       |       | INT2R<6:0> | •        |       |       | 0000          |

| RPINR3      | 06A6  | _      | _      | _       | _      | _          | _             | _     | _       | _              |       |       | -     | T2CKR<6:0  | >        |       |       | 0000          |

| RPINR7      | 06AE  | —      |        |         |        | IC2R<6:0>  |               |       |         | —              |       |       |       | IC1R<6:0>  |          |       |       | 0000          |

| RPINR8      | 06B0  | _      |        |         |        | IC4R<6:0>  |               |       |         | —              |       |       |       | IC3R<6:0>  |          |       |       | 0000          |

| RPINR9      | 06B2  | _      |        |         |        | IC6R<6:0>  |               |       |         | _              |       |       |       | IC5R<6:0>  |          |       |       | 0000          |

| RPINR10     | 06B4  | _      |        |         |        | IC8R<6:0>  |               |       |         | _              |       |       |       | IC7R<6:0>  |          |       |       | 0000          |

| RPINR11     | 06B6  | —      | —      | -       | —      | —          | _             |       | _       | —              |       |       | (     | OCFAR<6:0  | >        |       |       | 0000          |

| RPINR12     | 06B8  | _      |        |         |        | FLT2R<6:0  | >             |       |         | _              |       |       |       | FLT1R<6:0> | >        |       |       | 0000          |

| RPINR14     | 06BC  | —      |        |         |        | QEB1R<6:0  | >             |       |         | —              |       |       | (     | QEA1R<6:0  | >        |       |       | 0000          |

| RPINR15     | 06BE  | —      |        |         | Н      | OME1R<6:   | 0>            |       |         | —              |       |       | I     | NDX1R<6:0  | >        |       |       | 0000          |

| RPINR16     | 06C0  | —      |        |         |        | QEB2R<6:0  | >             |       |         | —              |       |       | (     | QEA2R<6:0  | >        |       |       | 0000          |

| RPINR17     | 06C2  | —      |        |         | н      | OME2R<6:   | 0>            |       | ÷       | —              |       |       | 1     | NDX2R<6:0  | >        |       |       | 0000          |

| RPINR18     | 06C4  | —      | —      | _       | —      | —          | _             | —     | —       | —              |       |       | I     | J1RXR<6:0  | >        |       |       | 0000          |

| RPINR19     | 06C6  | —      | —      | _       | —      | —          | _             | —     | —       | —              |       |       | I     | J2RXR<6:0  | >        |       |       | 0000          |

| RPINR22     | 06CC  | —      |        |         | :      | SCK2R<6:0  | >             |       |         | —              |       |       |       | SDI2R<6:0> | >        |       |       | 0000          |

| RPINR23     | 06CE  | —      | —      | _       | —      | —          | —             | —     | —       | —              |       |       |       | SS2R<6:0>  |          |       |       | 0000          |

| RPINR24     | 06D0  | —      |        |         | (      | CSCKR<6:0  | >             |       |         | —              |       |       |       | CSDIR<6:0> | >        |       |       | 0000          |

| RPINR25     | 06D2  | —      | —      | _       | —      | —          | —             | —     | —       | —              |       |       | (     | COFSR<6:0  | >        |       |       | 0000          |

| RPINR26     | 06D4  | —      |        |         |        | C2RXR<6:0  | >             |       |         | —              |       |       | (     | C1RXR<6:0  | >        |       |       | 0000          |

| RPINR27     | 06D6  | —      |        |         | ι      | J3CTSR<6:( | )>            |       |         | —              |       |       | l     | J3RXR<6:0  | >        |       |       | 0000          |

| RPINR28     | 06D8  | —      |        |         | ι      | J4CTSR<6:( | )>            |       |         | —              |       |       | l     | J4RXR<6:0  | >        |       |       | 0000          |

| RPINR29     | 06DA  | —      |        |         |        | SCK3R<6:0  | >             |       |         | —              |       |       |       | SDI3R<6:0> | <b>`</b> |       |       | 0000          |

| RPINR30     | 06DC  | —      | —      | —       | —      | —          | —             |       | —       | —              |       |       |       | SS3R<6:0>  |          |       | •     | 0000          |

| RPINR37     | 06EA  | —      |        |         | S      | YNCI1R<6:  | 0>            |       |         | —              |       | —     | _     | —          | _        | _     |       | 0000          |

| RPINR38     | 06EC  | _      |        |         |        | TCMP1R<6   |               |       |         | —              | _     | —     |       | —          | —        | _     | —     | 0000          |

| RPINR39     | 06EE  | _      |        |         |        | TCMP3R<6   | -             |       |         | —              |       |       | D     | TCMP2R<6:  | 0>       |       |       | 0000          |

| RPINR40     | 06F0  | —      |        |         | D      | TCMP5R<6   | :0>           |       |         | - DTCMP4R<6:0> |       |       |       |            |          | 0000  |       |               |

| RPINR41     | 06F2  | —      | —      | —       | —      | —          | —             | —     | —       | —              |       |       | D     | TCMP6R<6:  | 0>       |       |       | 0000          |

# TABLE 4-33: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXGM60X/7XX DEVICES

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXGM3XX DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8  | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-----------------------|--------|--------|-------|--------|--------|--------|--------|--------|--------|---------------|

| PMD1        | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD                 | DCIMD  | I2C1MD | U2MD  | U1MD   | SPI2MD | SPI1MD | —      | —      | AD1MD  | 0000          |

| PMD2        | 0762  | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD                 | IC1MD  | OC8MD  | OC7MD | OC6MD  | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3        | 0764  | T9MD   | T8MD   | T7MD   | T6MD   | _      | CMPMD  | RTCCMD <sup>(1)</sup> | PMPMD  | CRCMD  | _     | QEI2MD | _      | U3MD   | _      | I2C2MD | ADC2MD | 0000          |

| PMD4        | 0766  | _      | _      | _      | _      | _      | _      | _                     | _      | _      | _     | U4MD   | _      | REFOMD | CTMUMD | _      | _      | 0000          |

| PMD6        | 076A  | _      | _      | PWM6MD | PWM5MD | PWM4MD | PWM3MD | PWM2MD                | PWM1MD | _      | _     | _      | _      | _      | _      | _      | SPI3MD | 0000          |

|             |       |        |        |        |        |        |        |                       |        |        |       |        | DMA0MD |        |        |        |        |               |

| PMD7        | 076C  |        |        |        |        |        |        |                       |        |        |       |        | DMA1MD | PTGMD  |        |        |        |               |

| PMD7        | 0760  | _      | _      | _      | _      | _      | _      | _                     | _      | _      | _     | _      | DMA2MD | PIGMD  | _      | _      | _      | 0000          |

|             |       |        |        |        |        |        |        |                       |        |        |       |        | DMA3MD |        |        |        |        |               |

Legend:

— = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1:

The RTCCMD bit is not available on 44-pin devices.

# 7.3 Interrupt Control and Status Registers

dsPIC33EPXXXGM3XX/6XX/7XX devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- IFSx

- IECx

- IPCx

- INTTREG

# 7.3.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS) as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the Software Generated Hard Trap (SGHT) status bit.

#### 7.3.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

# 7.3.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

# 7.3.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

# 7.3.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into Vector Number (VECNUM<7:0>) and Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

# 7.3.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"CPU"** (DS70359).

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit, which together with IPL<2:0>, also indicates the current CPU Interrupt Priority Level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Secondary (Timer1) Oscillator (SOSC)                       | Secondary         | xx          | 100        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 00          | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

# TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

# 11.5 High-Voltage Detect

The dsPIC33EPXXXGM3XX/6XX/7XX devices contain High-Voltage Detection (HVD) which monitors the VCAP voltage. The HVD is used to monitor the VCAP supply voltage to ensure that an external connection does not raise the value above a safe level (~2.4V). If high core voltage is detected, all I/Os are disabled and put in a tri-state condition. The device remains in this I/O tristate condition as long as the high-voltage condition is present.

# 11.6 I/O Helpful Tips

- In some cases, certain pins, as defined in Table 33-10 under "Injection Current", have internal protection diodes to VDD and VSs. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD – 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specifications. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in **Section 33.0 "Electrical Characteristics"** for additional information.

# REGISTER 11-36: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| U-0           | U-0        | R/W-0                                | R/W-0          | R/W-0                   | R/W-0            | R/W-0           | R/W-0 |

|---------------|------------|--------------------------------------|----------------|-------------------------|------------------|-----------------|-------|

| _             | —          |                                      |                | RP55                    | R<5:0>           |                 |       |

| bit 15        |            |                                      |                |                         |                  |                 | bit 8 |

| U-0           | U-0        | R/W-0                                |                | D/M/ 0                  | D/M/ 0           |                 | DAM 0 |

| 0-0           | 0-0        | R/W-U                                | R/W-0          | R/W-0                   | R/W-0            | R/W-0           | R/W-0 |

|               |            |                                      |                | RP54                    | R<5:0>           |                 |       |

| bit 7         |            |                                      |                |                         |                  |                 | bit 0 |

|               |            |                                      |                |                         |                  |                 |       |

| Legend:       |            |                                      |                |                         |                  |                 |       |

| R = Readabl   | le bit     | W = Writable                         | bit            | U = Unimplen            | nented bit, read | d as '0'        |       |

| -n = Value at | t POR      | '1' = Bit is set                     |                | '0' = Bit is clea       | ared             | x = Bit is unkr | nown  |

| bit 15-14     | Unimpleme  | nted: Read as '                      | 0'             |                         |                  |                 |       |

| bit 13-8      |            | Peripheral Out<br>1-3 for peripheral | •              | n is Assigned to mbers) | RP55 Output I    | Pin bits        |       |

| bit 7-6       | Unimpleme  | nted: Read as '                      | 0'             |                         |                  |                 |       |

| bit 5-0       | RP54R<5:0> | Peripheral Out                       | Itput Functior | n is Assigned to        | RP54 Output I    | Pin bits        |       |

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-37: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0          | U-0        | R/W-0            | R/W-0          | R/W-0               | R/W-0         | R/W-0           | R/W-0 |

|--------------|------------|------------------|----------------|---------------------|---------------|-----------------|-------|

| _            | —          |                  |                | RP57R<              | <5:0>         |                 |       |

| bit 15       |            |                  |                |                     |               |                 | bit 8 |

|              |            |                  |                |                     |               |                 |       |

| U-0          | U-0        | R/W-0            | R/W-0          | R/W-0               | R/W-0         | R/W-0           | R/W-0 |

| —            | —          |                  |                | RP56R<              | <5:0>         |                 |       |

| bit 7        |            |                  |                |                     |               |                 | bit 0 |

|              |            |                  |                |                     |               |                 |       |

| Legend:      |            |                  |                |                     |               |                 |       |

| R = Readab   | le bit     | W = Writable     | bit            | U = Unimpleme       | nted bit, rea | d as '0'        |       |

| -n = Value a | t POR      | '1' = Bit is set |                | '0' = Bit is cleare | ed            | x = Bit is unkr | nown  |

|              |            |                  |                |                     |               |                 |       |

| bit 15-14    | Unimplemen | ted: Read as '   | 0'             |                     |               |                 |       |

| bit 13-8     | RP57R<5:0> | • Peripheral Ou  | Itout Function | n is Assigned to RI | 257 Output    | Pin bits        |       |

bit 13-8 **RP57R<5:0>:** Peripheral Output Function is Assigned to RP57 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP56R<5:0>:** Peripheral Output Function is Assigned to RP56 Output Pin bits (see Table 11-3 for peripheral function numbers)

## REGISTER 16-21: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER (CONTINUED)

| bit 7-3 | FLTSRC<4:0>: Fault Control Signal Source Select for PWMx Generator # bits<br>11111 = Fault 32 (default)<br>11110 = Reserved<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 00011 = Fault 4<br>00010 = Fault 3<br>00001 = Fault 2<br>00000 = Fault 1                                                                                                                                                                                                                         |

| bit 2   | <b>FLTPOL:</b> Fault Polarity for PWMx Generator # bit <sup>(1)</sup><br>1 = The selected Fault source is active-low<br>0 = The selected Fault source is active-high                                                                                                                             |

| bit 1-0 | FLTMOD<1:0>: Fault Mode for PWMx Generator # bits<br>11 = Fault input is disabled<br>10 = Reserved<br>01 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (cycle)<br>00 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDATx values (latched condition) |

**Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# **REGISTER 17-4: POSxCNTH: POSITION COUNTER x HIGH WORD REGISTER**

| R/W-0 | R/W-0            | R/W-0       | R/W-0                                                                            | R/W-0                                                                                                              | R/W-0                                                                                                                                                        | R/W-0                                                                                                                                                             |

|-------|------------------|-------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                  | POSC        | NT<31:24>                                                                        |                                                                                                                    |                                                                                                                                                              |                                                                                                                                                                   |

|       |                  |             |                                                                                  |                                                                                                                    |                                                                                                                                                              | bit 8                                                                                                                                                             |

|       |                  |             |                                                                                  |                                                                                                                    |                                                                                                                                                              |                                                                                                                                                                   |

| R/W-0 | R/W-0            | R/W-0       | R/W-0                                                                            | R/W-0                                                                                                              | R/W-0                                                                                                                                                        | R/W-0                                                                                                                                                             |

|       |                  | POSC        | NT<23:16>                                                                        |                                                                                                                    |                                                                                                                                                              |                                                                                                                                                                   |

|       |                  |             |                                                                                  |                                                                                                                    |                                                                                                                                                              | bit 0                                                                                                                                                             |

|       |                  |             |                                                                                  |                                                                                                                    |                                                                                                                                                              |                                                                                                                                                                   |

|       |                  |             |                                                                                  |                                                                                                                    |                                                                                                                                                              |                                                                                                                                                                   |

| bit   | W = Writable I   | bit         | U = Unimplen                                                                     | nented bit, rea                                                                                                    | d as '0'                                                                                                                                                     |                                                                                                                                                                   |

| OR    | '1' = Bit is set |             | '0' = Bit is cle                                                                 | ared                                                                                                               | x = Bit is unkr                                                                                                                                              | nown                                                                                                                                                              |

|       | R/W-0            | R/W-0 R/W-0 | R/W-0     R/W-0       R/W-0     R/W-0       POSCN       Dit     W = Writable bit | POSCNT<31:24>           R/W-0         R/W-0         R/W-0           POSCNT<23:16>         Dit         U = Unimpler | POSCNT<31:24>           R/W-0         R/W-0         R/W-0           POSCNT<23:16>           Dit         W = Writable bit         U = Unimplemented bit, real | POSCNT<31:24>         R/W-0       R/W-0       R/W-0       R/W-0         POSCNT<23:16>         Dit       W = Writable bit       U = Unimplemented bit, read as '0' |

bit 15-0 POSCNT<31:16>: High Word Used to Form 32-Bit Position Counter x Register (POSxCNT) bits

# REGISTER 17-5: POSxCNTL: POSITION COUNTER x LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | POSC  | NT<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | POSC  | NT<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | it    | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 **POSCNT<15:0>:** Low Word Used to Form 32-Bit Position Counter x Register (POSxCNT) bits

# REGISTER 17-10: INDXxHLD: INDEX COUNTER x HOLD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | INDXH | LD<15:8>          |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | INDXH | ILD<7:0>          |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-0 INDXHLD<15:0>: Holding Register for Reading and Writing INDXxCNT bits

# REGISTER 17-11: QEIXICH: QEIX INITIALIZATION/CAPTURE HIGH WORD REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0        | R/W-0            | R/W-0     | R/W-0           | R/W-0 |

|-----------------------------------|-------|------------------|--------------|------------------|-----------|-----------------|-------|

|                                   |       |                  | QEIIC        | <31:24>          |           |                 |       |

| bit 15                            |       |                  |              |                  |           |                 | bit 8 |

|                                   |       |                  |              |                  |           |                 |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0        | R/W-0            | R/W-0     | R/W-0           | R/W-0 |

|                                   |       |                  | QEIIC        | <23:16>          |           |                 |       |

| bit 7                             |       |                  |              |                  |           |                 | bit C |

|                                   |       |                  |              |                  |           |                 |       |

| Legend:                           |       |                  |              |                  |           |                 |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplen | nented bit, rea  | ad as '0' |                 |       |

| -n = Value at P                   | OR    | '1' = Bit is set |              | '0' = Bit is cle | ared      | x = Bit is unki | nown  |

bit 15-0 QEIIC<31:16>: High Word Used to Form 32-Bit Initialization/Capture Register (QEIxIC) bits

#### REGISTER 17-12: QEIxICL: QEIx INITIALIZATION/CAPTURE LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | QEIIC | C<15:8>           |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | QEII  | C<7:0>            |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

| L               |       |                  |       |                   |                  |                 |       |

bit 15-0 QEIIC<15:0>: Low Word Used to Form 32-Bit Initialization/Capture Register (QEIxIC) bits

# REGISTER 25-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER<sup>(1,2)</sup> (CONTINUED)

| bit 4   | OC1CS: Clock Source for OC1 bit                                                                                                                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Generates clock pulse when the broadcast command is executed                                                                                                                               |

|         | 0 = Does not generate clock pulse when the broadcast command is executed                                                                                                                       |

| bit 3   | OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| bit 2   | OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| bit 1   | OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| bit 0   | OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| Note 1: | This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and                                                                                                       |

- PTGSTRT = 1).

- 2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

#### REGISTER 26-5: **CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)**

- bit 3 ABEN: AND Gate B Input Enable bit

- 1 = MBI is connected to the AND gate

- 0 = MBI is not connected to the AND gate

- bit 2 ABNEN: AND Gate B Input Inverted Enable bit 1 = Inverted MBI is connected to the AND gate

- 0 = Inverted MBI is not connected to the AND gate bit 1 AAEN: AND Gate A Input Enable bit 1 = MAI is connected to the AND gate 0 = MAI is not connected to the AND gate bit 0

- AANEN: AND Gate A Input Inverted Enable bit

- 1 = Inverted MAI is connected to the AND gate

- 0 = Inverted MAI is not connected to the AND gate

# 31.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EP instruction set is almost identical to that of the dsPIC30F and dsPIC33F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- Control operations

Table 31-1 lists the general symbols used in describing the instructions.

The dsPIC33E instruction set summary in Table 31-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- · The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- · The accumulator write back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |                       | Description                                     | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-----------------|-----------------------|-------------------------------------------------|---------------|----------------|--------------------------|

| 8                  | BSW                  | BSW.C           | Ws,Wb                 | Write C bit to Ws <wb></wb>                     | 1             | 1              | None                     |

|                    |                      | BSW.Z           | Ws,Wb                 | Write Z bit to Ws <wb></wb>                     | 1             | 1              | None                     |

| 9                  | BTG                  | BTG             | f,#bit4               | Bit Toggle f                                    | 1             | 1              | None                     |

|                    |                      | BTG             | Ws,#bit4              | Bit Toggle Ws                                   | 1             | 1              | None                     |

| 10                 | BTSC                 | BTSC            | f,#bit4               | Bit Test f, Skip if Clear                       | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSC            | Ws,#bit4              | Bit Test Ws, Skip if Clear                      | 1             | 1<br>(2 or 3)  | None                     |

| 11                 | BTSS                 | BTSS            | f,#bit4               | Bit Test f, Skip if Set                         | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSS            | Ws,#bit4              | Bit Test Ws, Skip if Set                        | 1             | 1<br>(2 or 3)  | None                     |

| 12                 | BTST                 | BTST            | f,#bit4               | Bit Test f                                      | 1             | 1              | Z                        |

|                    |                      | BTST.C          | Ws,#bit4              | Bit Test Ws to C                                | 1             | 1              | С                        |

|                    |                      | BTST.Z          | Ws,#bit4              | Bit Test Ws to Z                                | 1             | 1              | Z                        |

|                    |                      | BTST.C          | Ws,Wb                 | Bit Test Ws <wb> to C</wb>                      | 1             | 1              | С                        |

|                    |                      | BTST.Z          | Ws,Wb                 | Bit Test Ws <wb> to Z</wb>                      | 1             | 1              | Z                        |

| 13                 | BTSTS                | BTSTS           | f,#bit4               | Bit Test then Set f                             | 1             | 1              | Z                        |

|                    |                      | BTSTS.C         | Ws,#bit4              | Bit Test Ws to C, then Set                      | 1             | 1              | С                        |

|                    |                      | BTSTS.Z         | Ws,#bit4              | Bit Test Ws to Z, then Set                      | 1             | 1              | Z                        |

| 14                 | CALL                 | CALL            | lit23                 | Call subroutine                                 | 2             | 4              | SFA                      |

|                    |                      | CALL            | Wn                    | Call indirect subroutine                        | 1             | 4              | SFA                      |

|                    |                      | CALL.L          | Wn                    | Call indirect subroutine (long address)         | 1             | 4              | SFA                      |

| 15                 | CLR                  | CLR             | f                     | f = 0x0000                                      | 1             | 1              | None                     |

|                    |                      | CLR             | WREG                  | WREG = 0x0000                                   | 1             | 1              | None                     |