Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | -                                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 48K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | -                                                                                |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gm304-h-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXXGM3XX/6XX/7XX

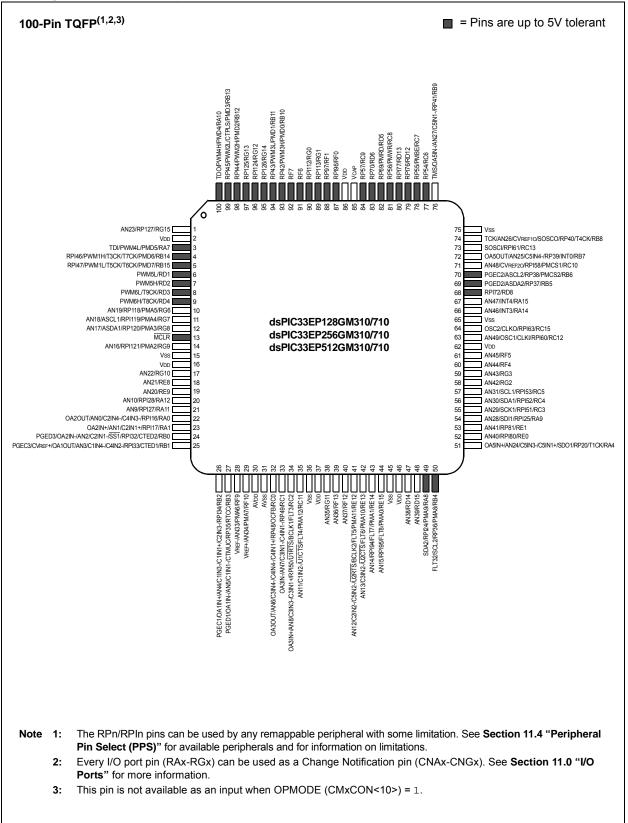

# **Pin Diagrams (Continued)**

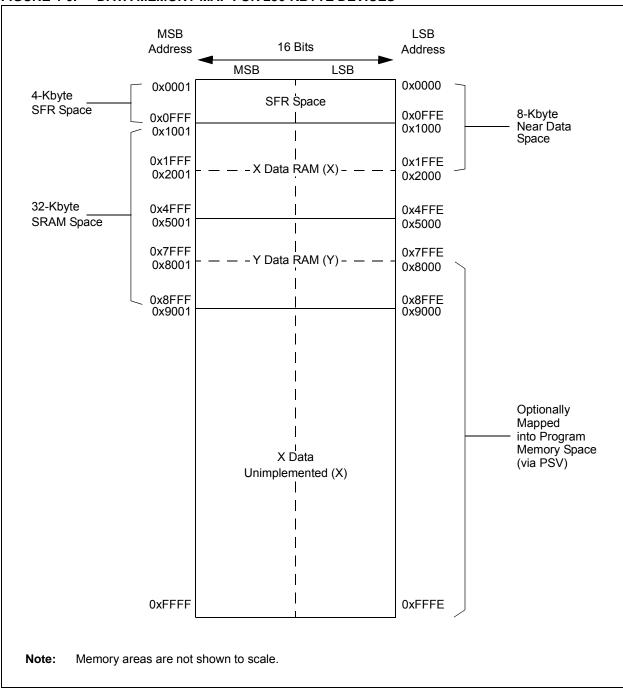

FIGURE 4-6: DATA MEMORY MAP FOR 256-KBYTE DEVICES

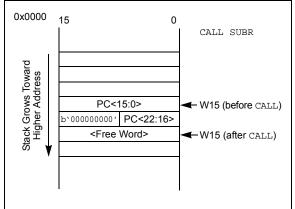

#### 4.3.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack     |

|-------|-----------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the |

|       | hardware.                               |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGM3XX/6XX/7XX devices and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack, working from lower toward higher addresses. Figure 4-13 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-13. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain the Software Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore, restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a 'C' development environment

#### FIGURE 4-13: C.

#### CALL STACK FRAME

# 4.4 Instruction Addressing Modes

The addressing modes shown in Table 4-66 form the basis of the addressing modes optimized to support the specific features of the individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

#### 4.4.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.4.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- · Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

Note: Not all instructions support all of the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

| REGISTER 7-1: SI | R: CPU STATUS REGISTER <sup>(1)</sup> |

|------------------|---------------------------------------|

|------------------|---------------------------------------|

| R/W-0                | R/W-0                | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|----------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                   | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                      |                      |       |       |       |       | bit 8 |

|                      |                      |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA    | N     | OV    | Z     | С     |

| bit 7                |                      |                      |       |       |       |       | bit 0 |

| Legend:           | C = Clearable bit |                      |                                    |  |  |

|-------------------|-------------------|----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bi | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared | x = Bit is unknown                 |  |  |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>                                                                                                                                                                                                                                                    |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled</li> <li>110 = CPU Interrupt Priority Level is 6 (14)</li> <li>101 = CPU Interrupt Priority Level is 5 (13)</li> <li>100 = CPU Interrupt Priority Level is 4 (12)</li> <li>011 = CPU Interrupt Priority Level is 3 (11)</li> </ul> |

|         | 010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8)                                                                                                                                                                             |

**Note 1:** For complete register details, see Register 3-1.

2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

|                 |                           |                          | (1)                        |

|-----------------|---------------------------|--------------------------|----------------------------|

| REGISTER 11-42: | <b>RPOR12: PERIPHERAL</b> | <b>PIN SELECT OUTPUT</b> | REGISTER 12 <sup>(1)</sup> |

| U-0          | U-0      | R/W-0                                                                                                                                      | R/W-0 | R/W-0                         | R/W-0         | R/W-0           | R/W-0 |  |

|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------|---------------|-----------------|-------|--|

| -            | -        |                                                                                                                                            |       | RP127R                        | -             |                 |       |  |

| bit 15       |          |                                                                                                                                            |       |                               |               |                 | bit 8 |  |

|              |          |                                                                                                                                            |       |                               |               |                 |       |  |

| U-0          | U-0      | R/W-0                                                                                                                                      | R/W-0 | R/W-0                         | R/W-0         | R/W-0           | R/W-0 |  |

| —            | —        |                                                                                                                                            |       | RP126R                        | <5:0>         |                 |       |  |

| bit 7        |          |                                                                                                                                            |       |                               |               |                 | bit 0 |  |

|              |          |                                                                                                                                            |       |                               |               |                 |       |  |

| Legend:      |          |                                                                                                                                            |       |                               |               |                 |       |  |

| R = Readab   | le bit   | W = Writable                                                                                                                               | bit   | U = Unimpleme                 | nted bit, rea | d as '0'        |       |  |

| -n = Value a | t POR    | '1' = Bit is set                                                                                                                           |       | '0' = Bit is cleare           | ed            | x = Bit is unkr | nown  |  |

|              |          |                                                                                                                                            |       |                               |               |                 |       |  |

| bit 15-14    | Unimplem | ented: Read as '                                                                                                                           | 0'    |                               |               |                 |       |  |

| bit 13-8     |          | :0>: Peripheral C<br>11-3 for periphera                                                                                                    | •     | on is Assigned to F<br>mbers) | RP127 Outp    | ut Pin bits     |       |  |

| bit 7-6      | Unimplem | ented: Read as '                                                                                                                           | 0'    |                               |               |                 |       |  |

| bit 5-0      |          | <b>RP126R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP126 Output Pin bits (see Table 11-3 for peripheral function numbers) |       |                               |               |                 |       |  |

Note 1: This register is not available on dsPIC33EPXXXGM30X/604/706 devices.

| R/W-0               | R/W-0                                                                                                                                                                                                                              | R/W-0                                                                                                        | R/W-0                         | R/W-0            | R/W-0                 | R/W-0                | R/W-0   |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------|------------------|-----------------------|----------------------|---------|--|--|--|

| IFLTMOD             | CLSRC4                                                                                                                                                                                                                             | CLSRC3                                                                                                       | CLSRC2                        | CLSRC1           | CLSRC0                | CLPOL <sup>(1)</sup> | CLMOD   |  |  |  |

| bit 15              |                                                                                                                                                                                                                                    |                                                                                                              |                               |                  |                       |                      | bit 8   |  |  |  |

|                     |                                                                                                                                                                                                                                    |                                                                                                              |                               |                  |                       |                      |         |  |  |  |

| R/W-1               | R/W-1                                                                                                                                                                                                                              | R/W-1                                                                                                        | R/W-1                         | R/W-1            | R/W-0                 | R/W-0                | R/W-0   |  |  |  |

| FLTSRC4             | FLTSRC3                                                                                                                                                                                                                            | FLTSRC2                                                                                                      | FLTSRC1                       | FLTSRC0          | FLTPOL <sup>(1)</sup> | FLTMOD1              | FLTMOD0 |  |  |  |

| bit 7               |                                                                                                                                                                                                                                    |                                                                                                              |                               |                  |                       |                      | bit     |  |  |  |

| Legend:             |                                                                                                                                                                                                                                    |                                                                                                              |                               |                  |                       |                      |         |  |  |  |

| R = Readable        | bit                                                                                                                                                                                                                                | W = Writable                                                                                                 | bit                           | U = Unimplen     | nented bit, read      | 1 as '0'             |         |  |  |  |

| -n = Value at I     | POR                                                                                                                                                                                                                                | '1' = Bit is set                                                                                             |                               | '0' = Bit is cle | ared                  | x = Bit is unkr      | nown    |  |  |  |

| bit 15<br>bit 14-10 | 1 = Independ<br>0 = Independ                                                                                                                                                                                                       | dependent Fau<br>lent Fault mode<br>lent Fault mode<br>: Current-Limit                                       | e is enabled<br>e is disabled |                  | t for the PWM         | < Generator # b      | its     |  |  |  |

|                     | CLSRC<4:0>: Current-Limit Control Signal Source Select for the PWMx Generator # bits<br>11111 = Fault 32<br>11110 = Reserved                                                                                                       |                                                                                                              |                               |                  |                       |                      |         |  |  |  |

|                     | •                                                                                                                                                                                                                                  |                                                                                                              |                               |                  |                       |                      |         |  |  |  |

|                     | 01011 = Com<br>01010 = Op A<br>01001 = Op A<br>01000 = Op A<br>00111 = Faul<br>00101 = Faul<br>00101 = Faul<br>00011 = Faul<br>00010 = Faul<br>00001 = Faul<br>00000 = Faul                                                        | Amp/Comparat<br>Amp/Comparat<br>Amp/Comparat<br>It 8<br>It 7<br>It 6<br>It 5<br>It 4<br>It 3<br>It 2<br>It 1 | or 3<br>or 2<br>or 1          |                  | (1)                   |                      |         |  |  |  |

| bit 9               | 1 = The selec                                                                                                                                                                                                                      | ent-Limit Polari<br>ted current-lim<br>ted current-lim                                                       | it source is ac               | tive-low         | (1)                   |                      |         |  |  |  |

| bit 8               | <ul> <li>0 = The selected current-limit source is active-high</li> <li>CLMOD: Current-Limit Mode Enable for PWMx Generator # bit</li> <li>1 = Current-Limit mode is enabled</li> <li>0 = Current-Limit mode is disabled</li> </ul> |                                                                                                              |                               |                  |                       |                      |         |  |  |  |

# REGISTER 16-21: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER

**Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| U-0             | U-0                                                                                       | U-0              | U-0             | U-0                                     | U-0              | U-0    | U-0 |  |

|-----------------|-------------------------------------------------------------------------------------------|------------------|-----------------|-----------------------------------------|------------------|--------|-----|--|

| —               | _                                                                                         | _                | _               | _                                       | _                |        | _   |  |

| bit 15          |                                                                                           | b                |                 |                                         |                  |        |     |  |

|                 |                                                                                           |                  |                 |                                         |                  |        |     |  |

| U-0             | U-0                                                                                       | U-0              | R-0             | R-0                                     | R-0              | R-0    | R-0 |  |

| —               | —                                                                                         | —                |                 |                                         | DNCNT<4:0>       |        |     |  |

| bit 7           |                                                                                           | bit 0            |                 |                                         |                  |        |     |  |

|                 |                                                                                           |                  |                 |                                         |                  |        |     |  |

| Legend:         |                                                                                           |                  |                 |                                         |                  |        |     |  |

| R = Readable    | bit                                                                                       | W = Writable     | bit             | U = Unimpler                            | mented bit, read | as '0' |     |  |

| -n = Value at P | OR                                                                                        | '1' = Bit is set |                 | '0' = Bit is cleared x = Bit is unknown |                  |        |     |  |

|                 |                                                                                           |                  |                 |                                         |                  |        |     |  |

| bit 15-5        | Unimplemen                                                                                | ted: Read as 'o  | כ'              |                                         |                  |        |     |  |

| bit 4-0         | DNCNT<4:0>                                                                                | : DeviceNet™     | Filter Bit Num  | iber bits                               |                  |        |     |  |

|                 | 10010-11111                                                                               | L = Invalid sele | ction           |                                         |                  |        |     |  |

|                 | 10001 <b>= Com</b>                                                                        | npare up to Dat  | a Byte 3, bit 6 | 6 with EID<17>                          | •                |        |     |  |

|                 | •                                                                                         |                  |                 |                                         |                  |        |     |  |

|                 | •                                                                                         |                  |                 |                                         |                  |        |     |  |

|                 | •                                                                                         |                  |                 |                                         |                  |        |     |  |

|                 | 00001 = Compare up to Data Byte 1, bit 7 with EID<0><br>00000 = Do not compare data bytes |                  |                 |                                         |                  |        |     |  |

# REGISTER 21-2: CxCTRL2: CANx CONTROL REGISTER 2

#### BUFFER 21-7: CANx MESSAGE BUFFER WORD 6

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |       |                  | Byte  | 7<15:8>                                 |       |       |       |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |

|                 |       |                  | Byte  | 6<7:0>                                  |       |       |       |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |

| Legend:         |       |                  |       |                                         |       |       |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-8 Byte 7<15:8>: CANx Message Byte 7

bit 7-0 Byte 6<7:0>: CANx Message Byte 6

#### BUFFER 21-8: CANx MESSAGE BUFFER WORD 7

| U-0    | U-0 | U-0 | R/W-x | R/W-x | R/W-x         | R/W-x | R/W-x |

|--------|-----|-----|-------|-------|---------------|-------|-------|

| _      | —   | —   |       |       | FILHIT<4:0>(1 | )     |       |

| bit 15 |     |     |       |       |               |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | _   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                     |

|-----------|----------------------------------------------------------------|

| bit 12-8  | FILHIT<4:0>: Filter Hit Code bits <sup>(1)</sup>               |

|           | Encodes number of filter that resulted in writing this buffer. |

bit 7-0 Unimplemented: Read as '0'

Note 1: Only written by module for receive buffers, unused for transmit buffers.

| R/W-0                | R/W-0               | R/W-0                                 | R/W-0               | U-0                                     | R/W-0             | R/W-0     | R/W-0 |  |

|----------------------|---------------------|---------------------------------------|---------------------|-----------------------------------------|-------------------|-----------|-------|--|

| VCFG2 <sup>(1)</sup> | VCFG1 <sup>(1</sup> | ) VCFG0 <sup>(1)</sup>                | OFFCAL              | _                                       | CSCNA             | CHPS1     | CHPS0 |  |

| bit 15               |                     |                                       |                     |                                         |                   |           | bit 8 |  |

|                      |                     |                                       |                     |                                         |                   |           |       |  |

| R-0                  | R/W-0               | R/W-0                                 | R/W-0               | R/W-0                                   | R/W-0             | R/W-0     | R/W-0 |  |

| BUFS                 | SMPI4               | SMPI3                                 | SMPI2               | SMPI1                                   | SMPI0             | BUFM      | ALTS  |  |

| bit 7                |                     |                                       |                     |                                         |                   |           | bit ( |  |

|                      |                     |                                       |                     |                                         |                   |           |       |  |

| Legend:              |                     |                                       |                     |                                         |                   |           |       |  |

| R = Readable         | bit                 | W = Writable bit                      | :                   | U = Unimp                               | lemented bit, rea | ad as '0' |       |  |

| -n = Value at I      | POR                 | '1' = Bit is set                      |                     | '0' = Bit is cleared x = Bit is unknown |                   |           |       |  |

|                      |                     |                                       |                     |                                         | (1)               |           |       |  |

| bit 15-13            | VCFG<2:0            | >: Converter Voltag                   | e Reference         | Configuratio                            | on bits()         |           |       |  |

|                      | Value               | VREFH                                 | VREFL               |                                         |                   |           |       |  |

|                      | 000                 | Avdd                                  | Avss                |                                         |                   |           |       |  |

|                      |                     |                                       |                     |                                         |                   |           |       |  |

|                      | 001                 | External VREF+(2)                     | Avss                |                                         |                   |           |       |  |

|                      | 001 010             | External VREF+ <sup>(2)</sup><br>AVDD | Avss<br>External VR | <sub>EF-</sub> (2)                      |                   |           |       |  |

|                      |                     |                                       |                     |                                         |                   |           |       |  |

#### REGISTER 23-2: ADxCON2: ADCx CONTROL REGISTER 2

1 = + and – inputs of channel Sample-and-Hold are connected to AVss

0 = + and – inputs of channel Sample-and-Hold are normal

- bit 11 Unimplemented: Read as '0'

- bit 10 CSCNA: Input Scan Select bit

- 1 = Scans inputs for CH0+ during Sample MUXA

0 = Does not scan inputs

## bit 9-8 CHPS<1:0>: Channel Select bits

In 12-Bit Mode (AD12B = 1), CHPS<1:0> Bits are Unimplemented and are Read as '00':

- lx = Converts CH0, CH1, CH2 and CH3

- 01 = Converts CH0 and CH1

- 00 = Converts CH0

- bit 7 **BUFS:** Buffer Fill Status bit (only valid when BUFM = 1)

- 1 = ADCx is currently filling the second half of the buffer; the user application should access data in the first half of the buffer

- 0 = ADCx is currently filling the first half of the buffer; the user application should access data in the second half of the buffer

- **Note 1:** The '001', '010' and '011' bit combinations for VCFG<2:0> are not applicable on ADC2.

- 2: ADC2 does not support external VREF± inputs.

# **REGISTER 23-7:** ADxCSSH: ADCx INPUT SCAN SELECT REGISTER HIGH<sup>(2)</sup> (CONTINUED)

| bit 4 | <b>CSS20:</b> ADCx Input Scan Selection bit<br>1 = Selects ANx for input scan<br>0 = Skips ANx for input scan |

|-------|---------------------------------------------------------------------------------------------------------------|

| bit 3 | <b>CSS19:</b> ADCx Input Scan Selection bit<br>1 = Selects ANx for input scan<br>0 = Skips ANx for input scan |

| bit 2 | <b>CSS18:</b> ADCx Input Scan Selection bit<br>1 = Selects ANx for input scan<br>0 = Skips ANx for input scan |

| bit 1 | <b>CSS17:</b> ADCx Input Scan Selection bit<br>1 = Selects ANx for input scan<br>0 = Skips ANx for input scan |

| bit 0 | <b>CSS16:</b> ADCx Input Scan Selection bit<br>1 = Selects ANx for input scan<br>0 = Skips ANx for input scan |

- **Note 1:** If the op amp is selected (OPMODE bit (CMxCON<10>) = 1), the OAx input is used; otherwise, the ANx input is used.

- 2: All bits in this register can be selected by the user application. However, inputs selected for scan without a corresponding input on the device convert VREFL.

NOTES:

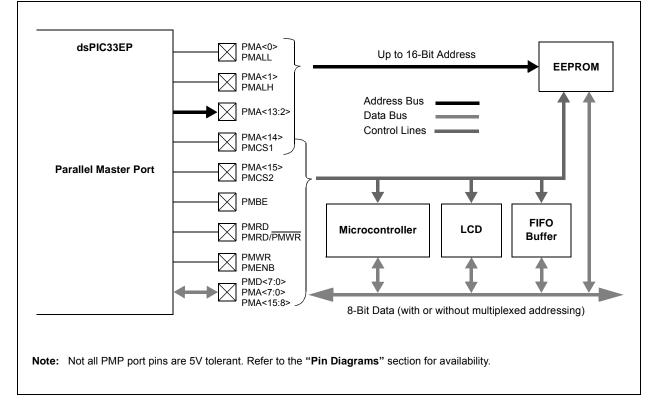

# 28.0 PARALLEL MASTER PORT (PMP)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Parallel Master Port (PMP)" (DS70576), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Parallel Master Port (PMP) module is a parallel 8-bit I/O module, specifically designed to communicate with a wide variety of parallel devices, such as communication peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP is highly configurable.

Key features of the PMP module include:

- Eight Data Lines

- Up to 16 Programmable Address Lines

- · Up to 2 Chip Select Lines

- Programmable Strobe Options:

- Individual read and write strobes, or

- Read/Write strobe with enable strobe

- Address Auto-Increment/Auto-Decrement

- Programmable Address/Data Multiplexing

- Programmable Polarity on Control Signals

- · Legacy Parallel Slave Port (PSP) Support

- Enhanced Parallel Slave Support:

- Address support

- 4-byte deep auto-incrementing buffer

- Programmable Wait States

#### FIGURE 28-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

| REGISTER 28-6: PADCFG1: PAD CONFIGURATION CONTROL REGISTER | REGISTER 28-6: | PADCFG1: PAD CONFIGURATION CONTROL REGISTER |

|------------------------------------------------------------|----------------|---------------------------------------------|

|------------------------------------------------------------|----------------|---------------------------------------------|

| U-0             | U-0 | U-0              | U-0 | U-0                                     | U-0 | U-0      | U-0    |  |

|-----------------|-----|------------------|-----|-----------------------------------------|-----|----------|--------|--|

| —               | —   | —                | _   | —                                       | —   | —        | —      |  |

| bit 15          |     | •                |     |                                         |     | •<br>•   | bit 8  |  |

|                 |     |                  |     |                                         |     |          |        |  |

| U-0             | U-0 | U-0              | U-0 | U-0                                     | U-0 | R/W-0    | R/W-0  |  |

| _               |     | —                | —   | —                                       | —   | RTSECSEL | PMPTTL |  |

| bit 7           |     | •                |     |                                         |     |          | bit 0  |  |

|                 |     |                  |     |                                         |     |          |        |  |

| Legend:         |     |                  |     |                                         |     |          |        |  |

| R = Readable    | bit | W = Writable     | bit | U = Unimplemented bit, read as '0'      |     |          |        |  |

| -n = Value at P | POR | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |          |        |  |

bit 15-2 Unimplemented: Read as '0'

bit 1 Not used by the PMP module.

bit 0 PMPTTL: PMP Module TTL Input Buffer Select bit

1 = PMP module uses TTL input buffers

0 = PMP module uses Schmitt Trigger input buffers

| Bit Field         | Description                                |

|-------------------|--------------------------------------------|

| WDTPRE            | Watchdog Timer Prescaler bit               |

|                   | 1 = 1:128                                  |

|                   | 0 = 1:32                                   |

| WDTPOST<3:0>      | Watchdog Timer Postscaler bits             |

|                   | 1111 = 1:32,768                            |

|                   | 1110 = 1:16,384                            |

|                   | •                                          |

|                   |                                            |

|                   | 0001 = 1:2                                 |

|                   | 0001 = 1.2<br>0000 = 1.1                   |

| WDTWIN<1:0>       | Watchdog Timer Window Select bits          |

| -                 | 11 = WDT Window is 25% of WDT Period       |

|                   | 10 = WDT Window is 37.5% of WDT Period     |

|                   | 01 = WDT Window is 50% of WDT Period       |

|                   | 00 = WDT Window is 75% of WDT Period       |

| ALTI2C1           | Alternate I2C1 Pins bit                    |

|                   | 1 = I2C1 is mapped to the SDA1/SCL1 pins   |

|                   | 0 = I2C1 is mapped to the ASDA1/ASCL1 pins |

| ALTI2C2           | Alternate I2C2 Pins bit                    |

|                   | 1 = I2C2 is mapped to the SDA2/SCL2 pins   |

|                   | 0 = I2C2 is mapped to the ASDA2/ASCL2 pins |

| BOREN             | Brown-out Reset (BOR) Detection Enable bit |

|                   | 1 = BOR is enabled                         |

|                   | 0 = BOR is disabled                        |

| JTAGEN            | JTAG Enable bit                            |

|                   | 1 = JTAG is enabled                        |

|                   | 0 = JTAG is disabled                       |

| ICS<1:0>          | ICD Communication Channel Select bits      |

|                   | 11 = Communicates on PGEC1 and PGED1       |

|                   | 10 = Communicates on PGEC2 and PGED2       |

|                   | 01 = Communicates on PGEC3 and PGED3       |

| Note 4. The Two C | 00 = Reserved, do not use                  |

# TABLE 30-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

Note 1: The Two-Speed Start-up is not enabled when EC mode is used since the EC clocks will be ready immediately.

#### TABLE 33-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACT                              | ERISTICS            |      | (unless oth | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |       |                                              |  |  |  |  |

|-----------------------------------------|---------------------|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------|--|--|--|--|

| Parameter<br>No.                        | Тур. <sup>(2)</sup> | Max. | Units       | Conditions                                                                                                                                                                                                                                                                              |       |                                              |  |  |  |  |

| Power-Down Current (IPD) <sup>(1)</sup> |                     |      |             |                                                                                                                                                                                                                                                                                         |       |                                              |  |  |  |  |

| DC60d                                   | 35                  | 100  | μA          | -40°C                                                                                                                                                                                                                                                                                   |       |                                              |  |  |  |  |

| DC60c                                   | 40                  | 200  | μA          | +25°C                                                                                                                                                                                                                                                                                   | 3.3V  | Read Device Device Current                   |  |  |  |  |

| DC60b                                   | 250                 | 500  | μA          | +85°C                                                                                                                                                                                                                                                                                   | 3.3V  | Base Power-Down Current                      |  |  |  |  |

| DC60c                                   | 1000                | 2500 | μA          | +125°C                                                                                                                                                                                                                                                                                  |       |                                              |  |  |  |  |

| DC61d                                   | 8                   | 10   | μA          | -40°C                                                                                                                                                                                                                                                                                   |       |                                              |  |  |  |  |

| DC61c                                   | 10                  | 15   | μA          | +25°C                                                                                                                                                                                                                                                                                   | 0.01/ | Watchdog Timer Current: ΔIwDT <sup>(3)</sup> |  |  |  |  |

| DC61b                                   | 12                  | 20   | μA          | +85°C                                                                                                                                                                                                                                                                                   | 3.3V  |                                              |  |  |  |  |

| DC61c                                   | 13                  | 25   | μA          | +125°C                                                                                                                                                                                                                                                                                  |       |                                              |  |  |  |  |

Note 1: IPD (Sleep) current is measured as follows:

CPU core is off, oscillator is configured in EC mode and external clock is active, OSC1 is driven with

external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as outputs and driving low

- $\overline{\text{MCLR}}$  = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all ones)

- The VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to standby while the device is in Sleep mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

ITAC is disabled

- JTAG is disabled

- 2: Data in the "Typical" column is at 3.3V, +25°C unless otherwise specified.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

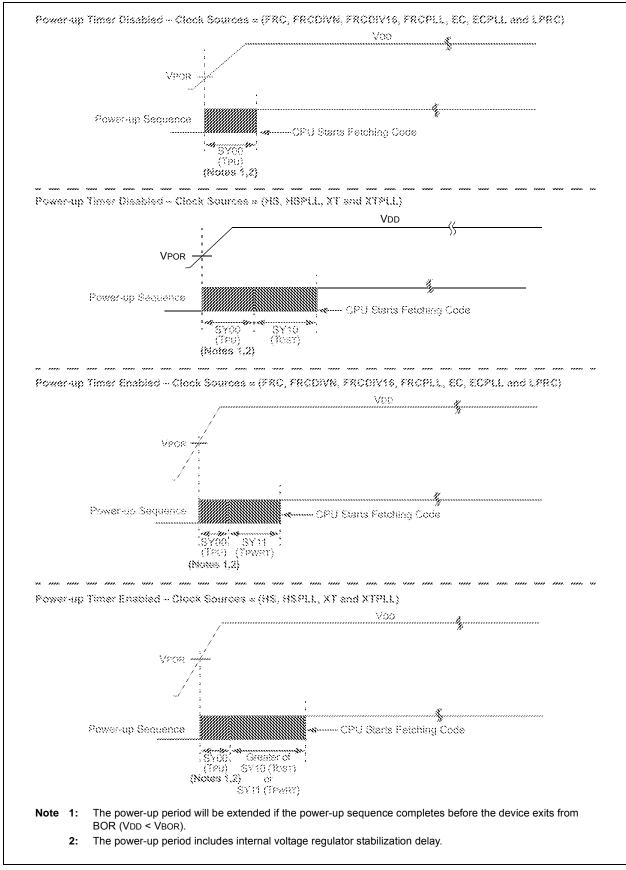

#### FIGURE 33-5: POWER-ON RESET TIMING CHARACTERISTICS

| AC CHARACTERISTICS |        |                                                      | Standard Operating Conditions (see Note 1): 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |         |                                   |                   |                                                                                                 |  |  |  |

|--------------------|--------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------|-------------------|-------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.       | Symbol | Characteristic                                       | Min.                                                                                                                                                                                                              | Тур.    | -40 C                             | ≤ IA ≤ +<br>Units | Conditions                                                                                      |  |  |  |

| Device Supply      |        |                                                      |                                                                                                                                                                                                                   |         |                                   |                   |                                                                                                 |  |  |  |

| AD01               | AVDD   | Module VDD Supply                                    | Greater of:<br>VDD – 0.3<br>or 3.0                                                                                                                                                                                | _       | Lesser of:<br>VDD + 0.3<br>or 3.6 | V                 |                                                                                                 |  |  |  |

| AD02               | AVss   | Module Vss Supply                                    | Vss – 0.3                                                                                                                                                                                                         |         | Vss + 0.3                         | V                 |                                                                                                 |  |  |  |

|                    |        | ·                                                    | Reference                                                                                                                                                                                                         | ce Inpu | ts                                |                   | ·                                                                                               |  |  |  |

| AD05               | Vrefh  | Reference Voltage High                               | AVss + 2.7                                                                                                                                                                                                        |         | AVDD                              | V                 | <b>(Note 1)</b><br>VREFH = VREF+,<br>VREFL = VREF-                                              |  |  |  |

| AD05a              |        |                                                      | 3.0                                                                                                                                                                                                               | _       | 3.6                               | V                 | VREFH = AVDD,<br>VREFL = AVSS = 0                                                               |  |  |  |

| AD06               | VREFL  | Reference Voltage Low                                | AVss                                                                                                                                                                                                              |         | AVDD - 2.7                        | V                 | (Note 1)                                                                                        |  |  |  |

| AD06a              |        |                                                      | 0                                                                                                                                                                                                                 |         | 0                                 | V                 | VREFH = AVDD,<br>VREFL = AVSS = 0                                                               |  |  |  |

| AD07               | VREF   | Absolute Reference<br>Voltage                        | 2.7                                                                                                                                                                                                               | _       | 3.6                               | V                 | VREF = VREFH – VREFL                                                                            |  |  |  |

| AD08               | IREF   | Current Drain                                        | _                                                                                                                                                                                                                 |         | 10<br>600                         | μΑ<br>μΑ          | ADC off<br>ADC on                                                                               |  |  |  |

| AD09               | Iad    | Operating Current                                    | —                                                                                                                                                                                                                 | 5       | —                                 | mA                | ADC operating in 10-bit mode (Note 1)                                                           |  |  |  |

|                    |        |                                                      | —                                                                                                                                                                                                                 | 2       |                                   | mA                | ADC operating in 12-bit mode (Note 1)                                                           |  |  |  |

|                    |        |                                                      | Analog                                                                                                                                                                                                            | g Input |                                   |                   |                                                                                                 |  |  |  |

| AD12               | Vinh   | Input Voltage Range,<br>Vinn                         | VINL                                                                                                                                                                                                              | _       | Vrefh                             | V                 | This voltage reflects<br>Sample-and-Hold<br>Channels 0, 1, 2 and 3<br>(CH0-CH3), positive input |  |  |  |

| AD13               | VINL   | Input Voltage Range,<br>ViNL                         | VREFL                                                                                                                                                                                                             | _       | AVss + 1V                         | V                 | This voltage reflects<br>Sample-and-Hold<br>Channels 0, 1, 2 and 3<br>(CH0-CH3), negative input |  |  |  |

| AD17               | RIN    | Recommended<br>Impedance of Analog<br>Voltage Source | _                                                                                                                                                                                                                 |         | 200                               | Ω                 | Impedance to achieve<br>maximum performance of<br>ADC                                           |  |  |  |

## TABLE 33-56: ADCx MODULE SPECIFICATIONS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 33-12 for the minimum and maximum BOR values.

| AC CHARACTERISTICS                        |        |                           | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |          |          |                   |                                                  |  |  |  |

|-------------------------------------------|--------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------------------|--------------------------------------------------|--|--|--|

| Param<br>No.                              | Symbol | Characteristic            | Min                                                                                                                               | Тур      | Max      | Units             | Conditions                                       |  |  |  |

| ADC Accuracy (12-Bit Mode) <sup>(1)</sup> |        |                           |                                                                                                                                   |          |          |                   |                                                  |  |  |  |

| HAD20a                                    | Nr     | Resolution <sup>(3)</sup> | 1:                                                                                                                                | 2 Data B | its      | bits              |                                                  |  |  |  |

| HAD21a                                    | INL    | Integral Nonlinearity     | -6                                                                                                                                | _        | 6        | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD22a                                    | DNL    | Differential Nonlinearity | -1                                                                                                                                | —        | 1        | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD23a                                    | Gerr   | Gain Error                | -10                                                                                                                               | _        | 10       | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD24a                                    | EOFF   | Offset Error              | -5                                                                                                                                | —        | 5        | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

|                                           |        | Dynamic I                 | Performa                                                                                                                          | nce (12- | Bit Mode | e) <sup>(2)</sup> | -                                                |  |  |  |

| HAD33a                                    | Fnyq   | Input Signal Bandwidth    | _                                                                                                                                 | —        | 200      | kHz               |                                                  |  |  |  |

#### TABLE 34-14: ADCx MODULE SPECIFICATIONS (12-BIT MODE)

**Note 1:** These parameters are characterized, but are tested at 20 ksps only.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

#### TABLE 34-15: ADCx MODULE SPECIFICATIONS (10-BIT MODE)

| AC CHARACTERISTICS                        |        |                           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |          |          |                   |                                                  |  |  |  |

|-------------------------------------------|--------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------------------|--------------------------------------------------|--|--|--|

| Param<br>No.                              | Symbol | Characteristic            | Min Typ Max                                                                                                                         |          | Units    | Conditions        |                                                  |  |  |  |

| ADC Accuracy (10-Bit Mode) <sup>(1)</sup> |        |                           |                                                                                                                                     |          |          |                   |                                                  |  |  |  |

| HAD20b                                    | Nr     | Resolution <sup>(3)</sup> | 10                                                                                                                                  | ) Data B | its      | bits              |                                                  |  |  |  |

| HAD21b                                    | INL    | Integral Nonlinearity     | -1.5                                                                                                                                | —        | 1.5      | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD22b                                    | DNL    | Differential Nonlinearity | -0.25                                                                                                                               |          | 0.25     | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD23b                                    | Gerr   | Gain Error                | -2.5                                                                                                                                |          | 2.5      | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD24b                                    | EOFF   | Offset Error              | -1.25                                                                                                                               |          | 1.25     | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

|                                           |        | Dynamic F                 | Performa                                                                                                                            | nce (10- | Bit Mode | e) <sup>(2)</sup> |                                                  |  |  |  |

| HAD33b                                    | Fnyq   | Input Signal Bandwidth    |                                                                                                                                     | _        | 400      | kHz               |                                                  |  |  |  |

Note 1: These parameters are characterized, but are tested at 20 ksps only.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

#### 35.1 Package Marking Information (Continued)

64-Lead TQFP (10x10x1 mm)

Example

100-Lead TQFP (12x12x1 mm)

100-Lead TQFP (14x14x1 mm)

121-Lead TFBGA (10x10x1.1 mm)

Example

Example

NOTES: