Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 48K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

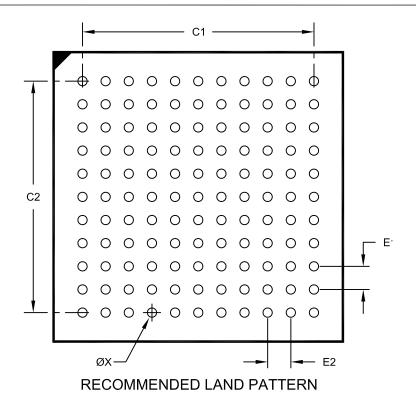

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gm304-i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin # | Full Pin Name                                   |     | Pin # | Full Pin Name                                                 |

|-------|-------------------------------------------------|-----|-------|---------------------------------------------------------------|

| E1    | PWM6H/T8CK/RD4                                  |     | J8    | No Connect                                                    |

| E2    | PWM6L/T9CK/RD3                                  |     | J9    | No Connect                                                    |

| E3    | AN19/RP118/PMA5/RG6                             |     | J10   | AN41/RP81/RE1                                                 |

| E4    | PWM5H/RD2                                       |     | J11   | AN30/SDA1/RPI52/RC4                                           |

| E5    | No Connect                                      |     | K1    | PGED3/OA2IN-/AN2/C2IN1-/SS1/RPI32/CTED2/RB0                   |

| E6    | RP113/RG1                                       |     | K2    | PGEC3/CVREF+/OA1OUT/AN3/C1IN4-/C4IN2-/RPI33/<br>CTED1/RB1     |

| E7    | No Connect                                      |     | K3    | VREF+/AN34/PMA7/RF10                                          |

| K4    | OA3OUT/AN6/C3IN4-/C4IN4-/C4IN1+/RP48/OCFB/RC0   |     | L3    | AVss                                                          |

| K5    | No Connect                                      |     | L4    | OA3IN-/AN7/C3IN1-/C4IN1-/RP49/RC1                             |

| K6    | AN37/RF12                                       |     | L5    | OA3IN+/AN8/C3IN3-/C3IN1+/RPI50/U1RTS/BCLK1/FLT3/<br>PMA13/RC2 |

| K7    | AN14/RPI94/FLT7/PMA1/RE14                       |     | L6    | AN36/RF13                                                     |

| K8    | VDD                                             |     | L7    | AN13/C3IN2-/U2CTS/FLT6/PMA10/RE13                             |

| K9    | AN39/RD15                                       |     | L8    | AN15/RPI95/FLT8/PMA0/RE15                                     |

| K10   | OA5IN+/AN24/C5IN3-/C5IN1+/SDO1/RP20/T1CK/RA4    |     | L9    | AN38/RD14                                                     |

| K11   | AN40/RPI80/RE0                                  |     | L10   | SDA2/RPI24/PMA9/RA8                                           |

| L1    | PGEC1/OA1IN+/AN4/C1IN3-/C1IN1+/C2IN3-/RPI34/RB2 |     | L11   | FLT32/SCL2/RP36/PMA8/RB4                                      |

| L2    | VREF-/AN33/PMA6/RF9                             | 1 - |       |                                                               |

# TABLE 2:PIN NAMES: dsPIC33EP128/256/512GM310/710 DEVICES<sup>(1,2,3)</sup> (CONTINUED)

Note 1: The RPn/RPIn pins can be used by any remappable peripheral with some limitation. See Section 11.4 "Peripheral Pin Select (PPS)" for available peripherals and for information on limitations.

2: Every I/O port pin (RAx-RGx) can be used as a Change Notification pin (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: The availability of I<sup>2</sup>C™ interfaces varies by device. Selection (SDAx/SCLx or ASDAx/ASCLx) is made using the device Configuration bits, ALTI2C1 and ALTI2C2 (FPOR<5:4>). See Section 30.0 "Special Features" for more information.

| Name<br>Name<br>NameAddr.Bit 10Bit 10Bit 10Bit 10Bit 10Bit 10Bit 10Bit 20Bit 10Bit 20Bit                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                                                            |       |       |       |        |            |              |             |            |            |         |        | MAP    | ISTER N | SREG   | TIMER  | 4-4:  | TABLE 4 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------------------------|-------|-------|-------|--------|------------|--------------|-------------|------------|------------|---------|--------|--------|---------|--------|--------|-------|---------|

| PR1       0102       Period Register 1         TICON       0104       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       —       TSYNC       TCS       —         TIM2       0106       -       Time?       Period Register       FORATE       TCKPS1       TCKPS1       TCKPS1       TCKPS0       —       TSYNC       TCS       —         TIM3       0106       -       Time?       Register for 32-bit timer operations only)       -       TTSYNC       TCS       —         TRR3H_D       0106       -       -       Time?       Period Register 3       -       TCS       -       -       -       TGATE       TCKPS0       T32       -       TCS       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -       -       -       TGATE       TCKPS1       TCKPS0       TS12       -       TCS       -       -       TGATE       TCKPS1       TCKPS0       TS10       -       TCS       -       TTS15       -                                                                                                                                                                         | All<br>Resets | Bit 0                                                      | Bit 1 | Bit 2 | Bit 3 | Bit 4  | Bit 5      | Bit 6        | Bit 7       | Bit 8      | Bit 9      | Bit 10  | Bit 11 | Bit 12 | Bit 13  | Bit 14 | Bit 15 | Addr. | -       |

| TICON       014//       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       TSYNC       TCS       -         TMR2       0106       -       Timer2       Register       -       TGATE       TCKPS1       TCKPS0       -       TSYNC       TCS       -         TMR3       0106       -       Timer3       Register       -       TS2-bit filter operations only)       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       TCKPS0       T32       -       TCS       -       -       -       -       TCS       -       -       TCS       -       -       TCS       -       TCS       -       TCS       -       TCS       -       TCS       -       TCS       1       1       1                                                                                                                                                                                                                                     | 0000          |                                                            |       |       |       |        |            | r            | er1 Registe | Tim        |            |         |        |        |         |        |        | 0100  | TMR1    |

| TMR2       0.106       Timer2 Register         TMR3HLD       0108       Timer3 Holding Register (For 32-bit timer operations only)         TMR3       0100       Period Register 2         PR2       0100       Period Register 2         PR3       0110       TON       -       TSIDL       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         T3CON       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4HD       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5HD       0116       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         PR5 </td <td>FFFF</td> <td>-</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>1</td> <td>od Register</td> <td>Peri</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>0102</td> <td>PR1</td> | FFFF          | -                                                          |       |       |       |        |            | 1            | od Register | Peri       |            |         |        |        |         |        |        | 0102  | PR1     |

| TMR3HLD       0108       Timer3 Holding Register (For 32-bit timer operations only)         TMR3       010A       Timer3 Register         PR2       010C       Period Register 2         PR3       0100       Period Register 2         PR3       0100       Timer3 Register 2         PR3       0100       Timer3 Register 2         PR3       0110       TON -       TISDL -       -       Period Register 1         TMR4       0110       ToN -       Timer3 Register         TMR4       0114       Timer5 Holding Register (For 32-bit timer operations only)         TMR5       OTIR       TIMEr5 Register         TMR5       OTIR       ToKPS1       TCKPS1                                                                                                                                                                                                                                                                                                                                                           | 0000          | _                                                          | TCS   | TSYNC | _     | TCKPS0 | TCKPS1     | TGATE        |             | _          | _          | _       | —      | _      | TSIDL   | _      | TON    | 0104  | T1CON   |

| TMR3       010A       Timer3 Register 7         PR2       010C       Period Register 3         TZCON       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         T3CON       0112       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5       0114       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         TMR5       0118       -       -       -       -       -       TGATE       TCKPS1       TCKPS0       T32       -       TCS       -         T4CON       0112       TON       <                                                                                                                                                                                                                                                | 0000          | -                                                          |       |       |       |        |            | r            | er2 Registe | Tim        |            |         |        |        |         |        |        | 0106  | TMR2    |

| PR2       010C       Period Register 2         PR3       010E       Period Register 3         T2CON       0110       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T3CON       0112       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR4       0114       -       -       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR5HLD       0118       -       -       -       -       -       Period Register 4       Period Register 4         PR5       0110       -       -       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T4CON       0112       TON       -       TSIDL       -       -       -       -       TGA                                                                                                                                                                                                                                                    | xxxx          |                                                            |       |       |       |        | ions only) | timer operat | (For 32-bit | g Register | er3 Holdin | Time    |        |        |         |        |        | 0108  | TMR3HLD |

| PR3         010E         Period Register 3           T2CON         0110         TON         -         TSIDL         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T3CON         0112         TON         -         TSIDL         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T3CON         0112         TON         -         TSIDL         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           TMR4         0114         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           TMR5         0116         -         -         Timer5 Holding Register (For 32-bit timer operations only)         -         TCS         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           PR4         0114         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T4CON         0112         TON                                                                                                                               | 0000          |                                                            |       |       |       |        |            | r            | er3 Registe | Tim        |            |         |        |        |         |        |        | 010A  | TMR3    |

| T2CON         0110         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS1         TCKPS0         T32         -         TCS         -           T3CON         0112         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS1         TCKPS0         T32         -         TCS         -           TMR4         0114         -         -         -         -         TGATE         TCKPS1         TCKPS0         -         -         TCS         -           TMR4         0114         -         -         -         -         TGS0         -         -         TCS         10116         -         -         TGATE         TCKPS1         TCKPS0         T32         -         TCS         -         -         TCS         -                                                                                                                                   | FFFF          | Period Register 2                                          |       |       |       |        |            |              |             |            |            |         | 010C   | PR2    |         |        |        |       |         |

| T3CON     0112     TON     —     TSIDL     —     —     —     —     TGATE     TCKPS0     —     —     —     TCS     —       TMR4     0114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FFFF          | Period Register 3                                          |       |       |       |        |            |              |             |            |            | 010E    | PR3    |        |         |        |        |       |         |

| TMR4     0114     Immediate     Timer4 Register       TMR4LD     0116     Timer5 Holding Register (For 32-bit timer operations only)       TMR5     0118       PR4     011A       PR5     011C       TMR6     012       TMR6     012       TMR7     012       TMR7     012       PR6     012       TMR7     0126       TMR7     0126       PR7     0128       PR7     0128       PR7     0120       TON     —       TMR7     0126       PR7     0128       PR7     0120       TON     —       TMR7     0126       PR7     0120       TON     —       TMR7     0126       PR7     0128       PR7     0120       TON     —       TMR7     0126       PR7     0120       TON     —       TMR7     0126       PR7     0120       TON     —       TMR8     0130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0000          | —                                                          | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | _           | _          | _          | —       | —      |        | TSIDL   |        | TON    | 0110  | T2CON   |

| TMRSHLD       0116       TimerS Holding Register (For 32-bit timer operations only)         TMRS       0118       TimerS Register         PR4       011A       Period Register 4         PR5       011C       Period Register 5         T4CON       011E       TON       -       TSIDL       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T5CON       0120       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR6       0120       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR6       0122       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR7       0126       Timer7 Holding Register (For 32-bit timer operations only)       TImer7 Register       Period Register 6         PR6       0132       TON       -       TSIDL       -       -       -       TGATE       TCKPS0                                                                                                                                                                                                 | 0000          | —                                                          | TCS   | —     | —     | TCKPS0 | TCKPS1     | TGATE        | _           | _          | _          | —       | —      |        | TSIDL   |        | TON    | 0112  | T3CON   |

| TMR5       0118       Timer5 Register         PR4       011A       Period Register 4         PR5       011C       Period Register 5         T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T4CON       011E       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0122       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       —       —       —       —       —       —       —       —       —       —       TCS       —       —       —       —       —       —       TCS       P       P       P       P       P       P       P       P       P       P <t< td=""><td>0000</td><td></td><td></td><td></td><td></td><td></td><td></td><td>r</td><td>er4 Registe</td><td>Tim</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>0114</td><td>TMR4</td></t<>                                        | 0000          |                                                            |       |       |       |        |            | r            | er4 Registe | Tim        |            |         |        |        |         |        |        | 0114  | TMR4    |

| PR4       011A       Period Register 4         PR5       011C       Period Register 5         T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0122       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR7       0126       Timer7 Holding Register (For 32-bit timer operations only)       TImer7 Register       Period Register 6       Period Register       Period Register       Period Register       TCKPS0       T32       —       TCS       —         T6CON       012C       TON       —       TSIDL       —       —                                                                                                                                                                                       | xxxx          | Timer5 Holding Register (For 32-bit timer operations only) |       |       |       |        |            |              |             |            | 0116       | TMR5HLD |        |        |         |        |        |       |         |

| PR5       011C       Period Register 5         T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         TMR6       0122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0000          | Timer5 Register                                            |       |       |       |        |            |              |             |            |            | 0118    | TMR5   |        |         |        |        |       |         |

| T4CON       011E       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       T32       —       TCS       —         TMR6       0122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | FFFF          | Period Register 4                                          |       |       |       |        |            |              |             |            | 011A       | PR4     |        |        |         |        |        |       |         |

| T5CON       0120       TON       —       TSIDL       —       —       —       —       TGATE       TCKPS1       TCKPS0       —       —       TCS       —         TMR6       0122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FFFF          |                                                            |       |       |       |        |            | 5            | od Register | Peri       |            |         |        |        |         |        |        | 011C  | PR5     |

| TMR6       0122       Timer6 Register         TMR7HLD       0124       Timer7 Holding Register (For 32-bit timer operations only)         TMR7       0126       Timer7 Register         PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       012C       TON       -       TSIDL       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR8       0130       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                            | 0000          | —                                                          | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | —           |            |            | —       | —      |        | TSIDL   | -      | TON    | 011E  | T4CON   |

| TMR7 HLD       0124       Timer7 Holding Register (For 32-bit timer operations only)         TMR7       0126       Timer7 Register         PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       0122       TON       -       TSIDL       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR8       0130       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       -       TImer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0000          | —                                                          | TCS   | —     | —     | TCKPS0 | TCKPS1     | TGATE        | —           |            |            | —       | —      |        | TSIDL   |        | TON    | 0120  | T5CON   |

| TMR7       0126       Timer7 Register         PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       012C       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         T7CON       012E       TON       -       TSIDL       -       -       -       -       TGATE       TCKPS0       T32       -       TCS       -         TMR8       0130       -       TSIDL       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       TGATE       TCKPS1       TCKPS0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <td>0000</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>r</td> <td>er6 Registe</td> <td>Tim</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>0122</td> <td>TMR6</td>                                   | 0000          |                                                            |       |       |       |        |            | r            | er6 Registe | Tim        |            |         |        |        |         |        |        | 0122  | TMR6    |

| PR6       0128       Period Register 6         PR7       012A       Period Register 7         T6CON       012C       TON       —       TSIDL       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T7CON       012E       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         T7CON       012E       TON       —       TSIDL       —       —       —       —       —       TGATE       TCKPS0       T32       —       TCS       —         TMR8       0130       —       TSIDL       —       —       —       —       TImer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | xxxx          |                                                            |       |       |       |        | ions only) | timer operat | For 32-bit  | g Register | er7 Holdin | Time    |        |        |         |        |        | 0124  | TMR7HLD |

| PR7         012A         Period Register 7           T6CON         012C         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T7CON         012E         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           T7CON         012E         TON         -         TSIDL         -         -         -         -         TGATE         TCKPS0         T32         -         TCS         -           TMR8         0130         -         TSIDL         -         -         -         TImer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0000          |                                                            |       |       |       |        |            | r            | er7 Registe | Tim        |            |         |        |        |         |        |        | 0126  | TMR7    |

| T6CON     012C     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     T32     —     TCS     —       T7CON     012E     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     T32     —     TCS     —       T7CON     012E     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     —     —     TCS     —       TMR8     0130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FFFF          |                                                            |       |       |       |        |            | 6            | od Register | Peri       |            |         |        |        |         |        |        | 0128  | PR6     |

| T7CON     012E     TON     —     TSIDL     —     —     —     —     —     TGATE     TCKPS1     TCKPS0     —     —     TCS     —       TMR8     0130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | FFFF          |                                                            |       |       |       |        |            | 7            | od Register | Peri       |            |         |        |        |         |        |        | 012A  | PR7     |

| TMR8 0130 Timer8 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0000          | —                                                          | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | —           | —          | _          | —       | —      | —      | TSIDL   | _      | TON    | 012C  | T6CON   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0000          | —                                                          | TCS   | —     | _     | TCKPS0 | TCKPS1     | TGATE        | _           | —          | _          | —       | —      | —      | TSIDL   | _      | TON    | 012E  | T7CON   |

| TMR9HLD 0132 Timer9 Holding Register (For 32-bit timer operations only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0000          |                                                            |       |       |       |        |            | r            | er8 Registe | Tim        |            |         |        |        |         |        |        | 0130  | TMR8    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | xxxx          |                                                            |       |       |       |        | ions only) | timer operat | For 32-bit  | g Register | er9 Holdin | Time    |        |        |         |        |        | 0132  | TMR9HLD |

| TMR9     0134     Timer9 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0000          |                                                            |       |       |       |        |            | r            | er9 Registe | Tim        |            |         |        |        |         |        |        | 0134  | TMR9    |

| PR8 0136 Period Register 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FFFF          |                                                            |       |       |       |        |            | 8            | od Register | Peri       |            |         |        |        |         |        |        | 0136  | PR8     |

| PR9 0138 Period Register 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FFFF          |                                                            |       |       |       |        |            | 9            | od Register | Peri       |            |         |        |        |         |        |        | 0138  | PR9     |

| T8CON         013A         TON         —         TSIDL         —         —         —         —         TGATE         TCKPS1         TCKPS0         T32         —         TCS         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0000          | -                                                          | TCS   | —     | T32   | TCKPS0 | TCKPS1     | TGATE        | _           | _          | _          | _       | —      | _      | TSIDL   | _      | TON    | 013A  | T8CON   |

| T9CON     013C     TON     —     TSIDL     —     —     —     —     TGATE     TCKPS1     TCKPS0     —     —     TCS     —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0000          | -                                                          | TCS   | -     | _     | TCKPS0 | TCKPS1     | TGATE        | _           | _          | _          | _       | —      | —      | TSIDL   | _      | TON    | 013C  | T9CON   |

dsPIC33EPXXXGM3XX/6XX/7XX

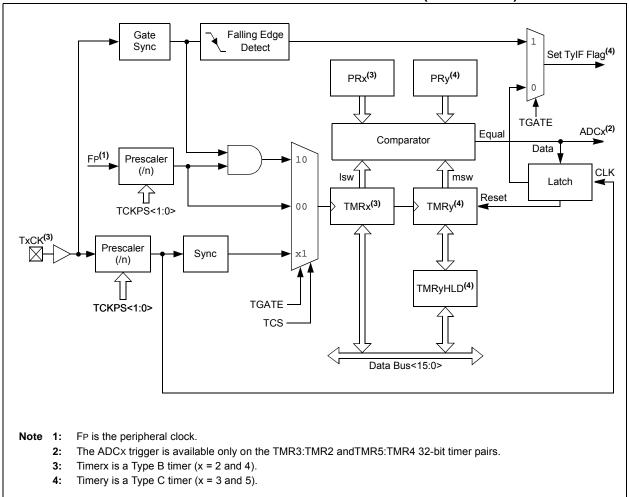

#### TABLE 4-4: TIMERS REGISTER MAP

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory, program a row and to program two instruction words at a time. See Table 1 in the "dsPIC33EPXXXGM3XX/6XX/7XX Product Family" section for the page sizes of each device.

The Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of program memory, which consists of eight rows (512 instructions) at a time, and to program one row or two adjacent words at a time. The 8-row erase pages and single row write rows are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

For more information on erasing and programming Flash memory, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Flash Programming"** (DS70609).

## 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time), in Table 33-13.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change. Programmers can also program a row of data (64 instruction words/ 192 bytes) at a time using the row programming feature present in these devices. For row programming, the source data is fetched directly from the data memory (RAM) on these devices. Two new registers have been provided to point to the RAM location where the source data resides. The page that has the row to be programmed must first be erased before the programming operation.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Flash Programming"** (DS70609) for details and code examples on programming using RTSP.

## 5.4 Control Registers

Six SFRs are used to read and write the program Flash memory: NVMCON, NVMKEY, NVMADR, NVMADRU, NVMSRCADRL and NVMSRCADRH.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRU and NVMADR. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations, or the selected page for erase operations.

The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA.

The NVMSRCADRH and NVMSRCADRL registers are used to hold the source address of the data in the data memory that needs to be written to Flash memory.

| R/W-0        | R/W-0                                     | U-0                                         | U-0            | R/W-0                 | U-0              | R/W-0            | R/W-0        |

|--------------|-------------------------------------------|---------------------------------------------|----------------|-----------------------|------------------|------------------|--------------|

| TRAPR        | IOPUWR                                    | _                                           |                | VREGSF                | _                | CM               | VREGS        |

| bit 15       |                                           |                                             |                |                       |                  |                  | bit 8        |

|              |                                           |                                             |                |                       |                  |                  |              |

| R/W-0        | R/W-0                                     | R/W-0                                       | R/W-0          | R/W-0                 | R/W-0            | R/W-1            | R/W-1        |

| EXTR         | SWR                                       | SWDTEN <sup>(2)</sup>                       | WDTO           | SLEEP                 | IDLE             | BOR              | POR          |

| bit 7        |                                           |                                             |                |                       |                  |                  | bit          |

| Legend:      |                                           |                                             |                |                       |                  |                  |              |

| R = Readal   | ole bit                                   | W = Writable b                              | oit            | U = Unimplem          | nented bit, read | l as '0'         |              |

| -n = Value a | at POR                                    | '1' = Bit is set                            |                | '0' = Bit is clea     | ared             | x = Bit is unk   | nown         |

| hit 1E       |                                           | Depart Flag hit                             |                |                       |                  |                  |              |

| bit 15       | -                                         | Reset Flag bit<br>onflict Reset has         | occurred       |                       |                  |                  |              |

|              |                                           | onflict Reset has                           |                | d                     |                  |                  |              |

| bit 14       | IOPUWR: Ille                              | gal Opcode or l                             | Jninitialized  | W Access Rese         | et Flag bit      |                  |              |

|              | 1 = An illega                             | al opcode detec                             | tion, an illeg | gal address mo        | de or Uninitial  | ized W registe   | er used as a |

|              |                                           | Pointer caused                              |                | Dogistor Dogot k      | an not anourra   | d                |              |

| bit 13-12    | -                                         | l opcode or Unir                            |                | Register Reset r      | las not occurre  | u                |              |

| bit 11       | •                                         | i <b>ted:</b> Read as '0<br>ash Voltage Reg |                | by During Sloop       | , bit            |                  |              |

|              |                                           | Itage regulator i                           |                |                       | זומ מ            |                  |              |

|              |                                           | Itage regulator                             |                |                       | ing Sleep        |                  |              |

| bit 10       | Unimplemen                                | ted: Read as '0                             | ,              | -                     |                  |                  |              |

| bit 9        | CM: Configur                              | ation Mismatch                              | Flag bit       |                       |                  |                  |              |

|              | •                                         | uration Mismatcl                            |                |                       |                  |                  |              |

|              | •                                         | uration Mismatcl                            |                |                       |                  |                  |              |

| bit 8        |                                           | age Regulator S                             |                |                       |                  |                  |              |

|              |                                           | egulator is activ                           |                |                       |                  |                  |              |

| bit 7        | -                                         | nal Reset (MCLF                             | -              | node during Sie       | eb.              |                  |              |

|              |                                           | Clear (pin) Res                             | ,              | red                   |                  |                  |              |

|              |                                           | Clear (pin) Res                             |                |                       |                  |                  |              |

| bit 6        | SWR: Softwa                               | IRE RESET (Instru                           | uction) Flag   | bit                   |                  |                  |              |

|              |                                           | instruction has l                           |                |                       |                  |                  |              |

|              |                                           | instruction has i                           |                |                       |                  |                  |              |

| bit 5        |                                           | oftware Enable/[                            | Disable of W   | DT bit <sup>(2)</sup> |                  |                  |              |

|              | 1 = WDT is e<br>0 = WDT is d              |                                             |                |                       |                  |                  |              |

| bit 4        |                                           | hdog Timer Tim                              | e-out Elag bi  | it                    |                  |                  |              |

| with i       |                                           | e-out has occurr                            | -              |                       |                  |                  |              |

|              |                                           | e-out has not oc                            |                |                       |                  |                  |              |

|              | All of the Reset sta<br>cause a device Re |                                             | set or cleare  | d in software. S      | etting one of th | ese bits in soft | ware does no |

| <b>2:</b>    | f the FWDTEN Co                           | onfiguration bit is                         | s '1' (unprog  | rammed), the W        | /DT is always e  | nabled, regard   | lless of the |

#### RCON: RESET CONTROL REGISTER<sup>(1)</sup> **REGISTER 6-1:**

e сy SWDTEN bit setting.

NOTES:

# 9.1 CPU Clocking System

The dsPIC33EPXXXGM3XX/6XX/7XX family of devices provides seven system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase-Locked Loop (PLL)

- FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

- · Secondary (LP) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = FOSC/2

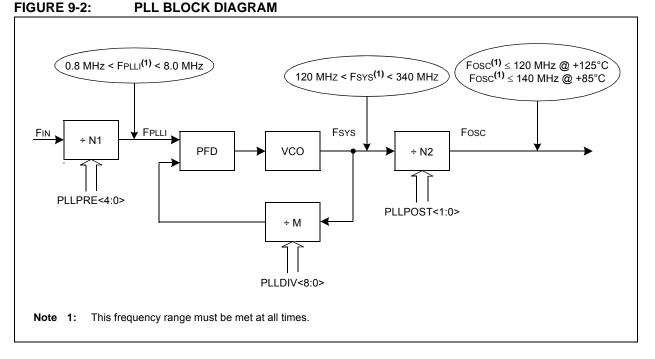

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FOSC).

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FSYS).

#### EQUATION 9-2: Fosc CALCULATION

$$FOSC = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV < 8:0 > + 2)}{(PLLPRE < 4:0 > + 2) \times 2(PLLPOST < 1:0 > + 1)}\right)$$

Where:

N1 = PLLPRE<4:0> + 2 N2 = 2 x (PLLPOST<1:0> + 1) M = PLLDIV<8:0> + 2

#### EQUATION 9-3: Fvco CALCULATION

$FSYS = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV < 8:0 > + 2)}{(PLLPRE < 4:0 > + 2)}\right)$

| U-0          | U-0                                          | U-0              | U-0        | U-0                                     | U-0              | U-0    | U-0    |  |  |  |  |  |

|--------------|----------------------------------------------|------------------|------------|-----------------------------------------|------------------|--------|--------|--|--|--|--|--|

| _            | —                                            | _                | _          | —                                       | _                | _      | _      |  |  |  |  |  |

| oit 15       |                                              |                  |            |                                         |                  |        | bit 8  |  |  |  |  |  |

| U-0          | U-0                                          | R/W-0            | R/W-0      | R/W-0                                   | R/W-0            | R/W-0  | R/W-0  |  |  |  |  |  |

| _            |                                              |                  | 1000 0     | _                                       | <5:0>            | 1011 0 | 1010 0 |  |  |  |  |  |

| pit 7        |                                              |                  |            |                                         |                  |        | bit (  |  |  |  |  |  |

|              |                                              |                  |            |                                         |                  |        |        |  |  |  |  |  |

| _egend:      |                                              |                  |            |                                         |                  |        |        |  |  |  |  |  |

| R = Readab   | le bit                                       | W = Writable     | bit        | U = Unimplen                            | nented bit, read | as '0' |        |  |  |  |  |  |

| -n = Value a | t POR                                        | '1' = Bit is set |            | '0' = Bit is cleared x = Bit is unknown |                  |        |        |  |  |  |  |  |

|              |                                              |                  |            |                                         |                  |        |        |  |  |  |  |  |

| oit 15-6     | Unimplement                                  | ted: Read as '   | 0'         |                                         |                  |        |        |  |  |  |  |  |

| oit 5-0      | TUN<5:0>: FI                                 | RC Oscillator T  | uning bits |                                         |                  |        |        |  |  |  |  |  |

|              | 111111 <b>= Ce</b>                           | nter frequency   | - 0.047%   |                                         |                  |        |        |  |  |  |  |  |

|              | •                                            |                  |            |                                         |                  |        |        |  |  |  |  |  |

|              | •                                            |                  |            |                                         |                  |        |        |  |  |  |  |  |

|              | 100001 = Center frequency – 1.453%           |                  |            |                                         |                  |        |        |  |  |  |  |  |

|              | 100000 = Center frequency – 1.5% (7.355 MHz) |                  |            |                                         |                  |        |        |  |  |  |  |  |

|              | 011111 = Center frequency + 1.5% (7.385 MHz) |                  |            |                                         |                  |        |        |  |  |  |  |  |

|              | 011110 = Center frequency + 1.453%           |                  |            |                                         |                  |        |        |  |  |  |  |  |

|              | •                                            |                  |            |                                         |                  |        |        |  |  |  |  |  |

|              | •                                            |                  |            |                                         |                  |        |        |  |  |  |  |  |

|              |                                              | nter frequency   |            |                                         |                  |        |        |  |  |  |  |  |

|              |                                              | nter frequency   |            |                                         |                  |        |        |  |  |  |  |  |

# **REGISTER 9-4:** OSCTUN: FRC OSCILLATOR TUNING REGISTER<sup>(1)</sup>

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

- bit 6-4

SYNCSRC<2:0>: Synchronous Source Selection bits<sup>(1)</sup>

111 = Reserved

...

...

...

100 = Reserved

011 = PTGO17<sup>(2)</sup>

010 = PTGO16<sup>(2)</sup>

001 = Reserved

000 = SYNCI1

bit 3-0

SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits<sup>(1)</sup>

1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event

...

0001 = 1:2 Postscaler generates Special Event Trigger on every second compare match event

...

0001 = 1:1 Postscaler generates Special Event Trigger on every second compare match event

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

#### **REGISTER 16-23: LEBDLYx: LEADING-EDGE BLANKING DELAY REGISTER x**

| U-0             | U-0   | U-0              | U-0   | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

|-----------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|--|--|

| —               | _     | —                | —     |                                    | LEB   | <11:8>             |       |  |  |

| bit 15          |       |                  |       |                                    |       |                    | bit 8 |  |  |

|                 |       |                  |       |                                    |       |                    |       |  |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

|                 |       |                  | LEE   | <7:0>                              |       |                    |       |  |  |

| bit 7           |       |                  |       |                                    |       |                    | bit C |  |  |

|                 |       |                  |       |                                    |       |                    |       |  |  |

| Legend:         |       |                  |       |                                    |       |                    |       |  |  |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplemented bit, read as '0' |       |                    |       |  |  |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unknown |       |  |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

#### REGISTER 21-16: CxRXFnSID: CANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| R/W-x                                                                | R/W-x                                                                                                                                                                                                                                     | R/W-x                                                     | R/W-x         | R/W-x             | R/W-x           | R/W-x | R/W-x |  |  |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------|-------------------|-----------------|-------|-------|--|--|

| SID10                                                                | SID9                                                                                                                                                                                                                                      | SID8                                                      | SID7          | SID6              | SID5            | SID4  | SID3  |  |  |