Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Betunio                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 48K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gm304-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXXGM3XX/6XX/7XX

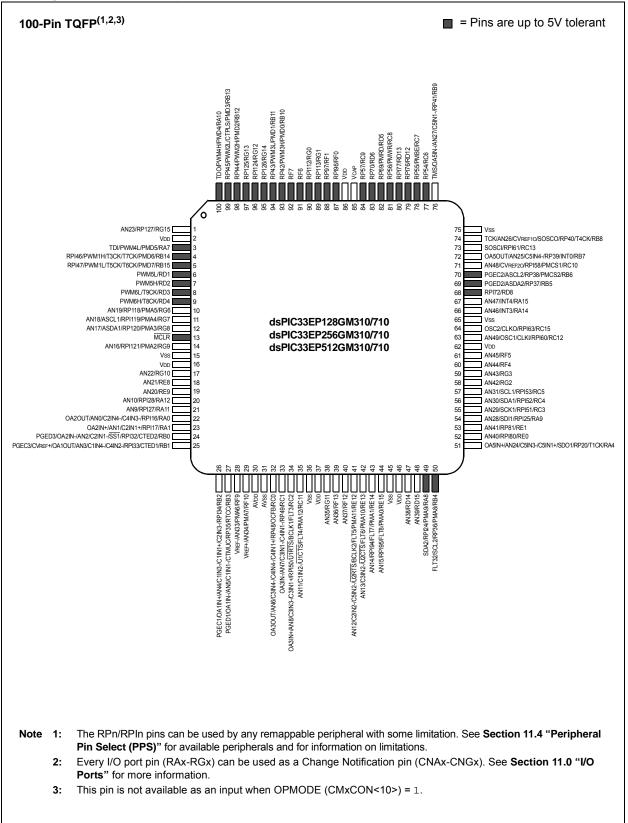

# **Pin Diagrams (Continued)**

# TABLE 4-23: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 OR 1 FOR dsPIC33EPXXXGM60X/7XX DEVICES<sup>(1)</sup>

|             |       |          |          |          |          |          |          | - , , -  |          |          |          |          |          |          |            |          |          |               |

|-------------|-------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|------------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2      | Bit 1    | Bit 0    | All<br>Resets |

| C1CTRL1     | 0400  | _        | _        | CSIDL    | ABAT     | CANCKS   | REQOP2   | REQOP1   | REQOP0   | OPMODE2  | OPMODE1  | OPMODE0  | —        | CANCAP   | -          | —        | WIN      | 0480          |

| C1CTRL2     | 0402  | _        |          | _        | _        | _        | _        | _        | _        | _        | _        | _        |          |          | DNCNT<4:0> |          | -        | 0000          |

| C1VEC       | 0404  | _        |          | _        | FILHIT4  | FILHIT3  | FILHIT2  | FILHIT1  | FILHIT0  | _        | ICODE6   | ICODE5   | ICODE4   | ICODE3   | ICODE2     | ICODE1   | ICODE0   | 0040          |

| C1FCTRL     | 0406  | DMABS2   | DMABS1   | DMABS0   | —        |          |          | —        | —        | —        | —        | _        | FSA4     | FSA3     | FSA2       | FSA1     | FSA0     | 0000          |

| C1FIFO      | 0408  | _        |          | FBP5     | FBP4     | FBP3     | FBP2     | FBP1     | FBP0     | —        | —        | FNRB5    | FNRB4    | FNRB3    | FNRB2      | FNRB1    | FNRB0    | 0000          |

| C1INTF      | 040A  | _        |          | TXBO     | TXBP     | RXBP     | TXWAR    | RXWAR    | EWARN    | IVRIF    | WAKIF    | ERRIF    | _        | FIFOIF   | RBOVIF     | RBIF     | TBIF     | 0000          |

| C1INTE      | 040C  | _        |          | —        | —        |          |          | —        | —        | IVRIE    | WAKIE    | ERRIE    | _        | FIFOIE   | RBOVIE     | RBIE     | TBIE     | 0000          |

| C1EC        | 040E  | TERRCNT7 | TERRCNT6 | TERRCNT5 | TERRCNT4 | TERRCNT3 | TERRCNT2 | TERRCNT1 | TERRCNT0 | RERRCNT7 | RERRCNT6 | RERRCNT5 | RERRCNT4 | RERRCNT3 | RERRCNT2   | RERRCNT1 | RERRCNT0 | 0000          |

| C1CFG1      | 0410  | _        |          | —        | —        |          |          | —        | —        | SJW1     | SJW0     | BRP5     | BRP4     | BRP3     | BRP2       | BRP1     | BRP0     | 0000          |

| C1CFG2      | 0412  | _        | WAKFIL   | —        | —        |          | SEG2PH2  | SEG2PH1  | SEG2PH0  | SEG2PHTS | SAM      | SEG1PH2  | SEG1PH1  | SEG1PH0  | PRSEG2     | PRSEG1   | PRSEG0   | 0000          |

| C1FEN1      | 0414  |          |          |          |          |          |          |          | FLTE     | N<15:0>  |          |          |          |          |            |          |          | FFFF          |

| C1FMSKSEL1  | 0418  | F7MSK1   | F7MSK0   | F6MSK1   | F6MSK0   | F5MSK1   | F5MSK0   | F4MSK1   | F4MSK0   | F3MSK1   | F3MSK0   | F2MSK1   | F2MSK0   | F1MSK1   | F1MSK0     | F0MSK1   | F0MSK0   | 0000          |

| C1FMSKSEL2  | 041A  | F15MSK1  | F15MSK0  | F14MSK1  | F14MSK0  | F13MSK1  | F13MSK0  | F12MSK1  | F12MSK0  | F11MSK1  | F11MSK0  | F10MSK1  | F10MSK0  | F9MSK1   | F9MSK0     | F8MSK1   | F8MSK0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers are not present on dsPIC33EPXXXGM3XX devices.

# TABLE 4-24: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 FOR dsPIC33EPXXXGM60X/7XX DEVICES<sup>(1)</sup>

| SFR<br>Name | Addr.         | Bit 15 | Bit 14                      | Bit 13            | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8        | Bit 7       | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0   | All<br>Resets |

|-------------|---------------|--------|-----------------------------|-------------------|--------|--------|--------|---------|--------------|-------------|---------|---------|--------|--------|--------|---------|---------|---------------|

|             | 0400-<br>041E |        |                             |                   |        |        |        | Se      | e definition | when WIN :  | ×       |         |        |        |        |         |         |               |

| C1RXFUL1    | 0420          |        |                             |                   |        |        |        |         | RXFUL        | <15:0>      |         |         |        |        |        |         |         | 0000          |

| C1RXFUL2    | 0422          |        |                             | RXFUL<31:16> 0000 |        |        |        |         |              |             |         |         |        |        |        |         |         |               |

| C1RXOVF1    | 0428          |        |                             | RXOVF<15:0> 0000  |        |        |        |         |              |             |         |         |        |        |        |         |         |               |

| C1RXOVF2    | 042A          |        |                             |                   |        |        |        |         | RXOVF        | <31:16>     |         |         |        |        |        |         |         | 0000          |

| C1TR01CON   | 0430          | TXEN1  | TXABT1                      | TXLARB1           | TXERR1 | TXREQ1 | RTREN1 | TX1PRI1 | TX1PRI0      | TXEN0       | TXABAT0 | TXLARB0 | TXERR0 | TXREQ0 | RTREN0 | TX0PRI1 | TX0PRI0 | 0000          |

| C1TR23CON   | 0432          | TXEN3  | TXABT3                      | TXLARB3           | TXERR3 | TXREQ3 | RTREN3 | TX3PRI1 | TX3PRI0      | TXEN2       | TXABAT2 | TXLARB2 | TXERR2 | TXREQ2 | RTREN2 | TX2PRI1 | TX2PRI0 | 0000          |

| C1TR45CON   | 0434          | TXEN5  | TXABT5                      | TXLARB5           | TXERR5 | TXREQ5 | RTREN5 | TX5PRI1 | TX5PRI0      | TXEN4       | TXABAT4 | TXLARB4 | TXERR4 | TXREQ4 | RTREN4 | TX4PRI1 | TX4PRI0 | 0000          |

| C1TR67CON   | 0436          | TXEN7  | TXABT7                      | TXLARB7           | TXERR7 | TXREQ7 | RTREN7 | TX7PRI1 | TX7PRI0      | TXEN6       | TXABAT6 | TXLARB6 | TXERR6 | TXREQ6 | RTREN6 | TX6PRI1 | TX6PRI0 | xxxx          |

| C1RXD       | 0440          |        | CAN1 Receive Data Word xxxx |                   |        |        |        |         |              |             |         |         |        | xxxx   |        |         |         |               |

| C1TXD       | 0442          |        |                             |                   |        |        |        | C       | AN1 Transn   | nit Data Wo | rd      |         |        |        |        |         |         | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** These registers are not present on dsPIC33EPXXXGM3XX devices.

#### TABLE 4-35: NVM REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7   | Bit 6 | Bit 5 | Bit 4   | Bit 3     | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|--------|--------|--------|---------|--------|--------|-------|---------|---------|-------|-------|---------|-----------|--------|--------|--------|---------------|

| NVMCON      | 0728  | WR     | WREN   | WRERR  | NVMSIDL |        | —      | RPDF  | URERR   | -       | -     |       | _       | NVMOP3    | NVMOP2 | NVMOP1 | NVMOP0 | 0000          |

| NVMADR      | 072A  |        |        |        |         |        |        |       | NVMAD   | R<15:0> |       |       |         |           |        |        |        | 0000          |

| NVMADRU     | 072C  | _      | _      | _      | _       | _      | _      | _     | _       |         |       |       | NVMAD   | RU<23:16> |        |        |        | 0000          |

| NVMKEY      | 072E  | _      | _      | _      | _       | _      | _      | _     | _       |         |       |       | NVM     | (EY<7:0>  |        |        |        | 0000          |

| NVMSRCADRL  | 0730  |        |        |        |         |        |        | NVMS  | SRCADR< | 15:1>   |       |       |         |           |        |        | 0      | 0000          |

| NVMSRCADRH  | 0732  |        |        |        |         |        |        |       |         |         |       |       | NVMSRCA | ADRH<23:1 | 6>     |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-36: SYSTEM CONTROL REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7    | Bit 6    | Bit 5  | Bit 4     | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|---------|---------|---------|----------|----------|--------|-----------|---------|---------|---------|---------|---------------|

| RCON        | 0740  | TRAPR  | IOPUWR |        | —      | VREGSF |         | СМ      | VREGS   | EXTR     | SWR      | SWDTEN | WDTO      | SLEEP   | IDLE    | BOR     | POR     | Note 1        |

| OSCCON      | 0742  | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2   | NOSC1   | NOSC0   | CLKLOCK  | IOLOCK   | LOCK   | _         | CF      | _       | LPOSCEN | OSWEN   | Note 2        |

| CLKDIV      | 0744  | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | FRCDIV2 | FRCDIV1 | FRCDIV0 | PLLPOST1 | PLLPOST0 | _      | PLLPRE4   | PLLPRE3 | PLLPRE2 | PLLPRE1 | PLLPRE0 | 0030          |

| PLLFBD      | 0746  | _      | _      | _      | —      |        |         | —       |         |          |          | PL     | LDIV<8:0> |         |         |         |         | 0030          |

| OSCTUN      | 0748  | _      | _      |        | _      |        |         | _       |         |          |          |        |           | TUN     | <5:0>   |         |         | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the configuration fuses.

# TABLE 4-37: REFERENCE CLOCK REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON     | 074E  | ROON   |        | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _     |       |       |       |       |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER (CONTINUED)

- bit 3-0 NVMOP<3:0>: NVM Operation Select bits<sup>(1,3,4)</sup>

- 1111 = Reserved

- 1110 = Reserved

- 1101 = Bulk erase primary program Flash memory

- 1100 = Reserved

- 1011 = Reserved

- 1010 = Reserved

- 0011 = Memory page erase operation

- 0010 = Memory row program operation with source data from RAM

- 0001 = Memory double-word program operation<sup>(5)</sup>

- 0000 = Reserved

- Note 1: These bits can only be reset on POR.

- 2: If this bit is set, there will be minimal power savings (IIDLE), and upon exiting Idle mode, there is a delay (TVREG) before Flash memory becomes operational.

- **3:** All other combinations of NVMOP<3:0> are unimplemented.

- 4: Execution of the PWRSAV instruction is ignored while any of the NVM operations are in progress.

- 5: Two adjacent words on a 4-word boundary are programmed during execution of this operation.

- 6: When URERR is set, the bus mastered row programming operation will terminate with the WRERR bit still set.

|                                  |                                      | •                                                       | •                                                      |

|----------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| Peripheral to DMA<br>Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

| CAN1 – RX Data Ready             | 00100010                             | 0x0440 (C1RXD)                                          | —                                                      |

| CAN1 – TX Data Request           | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| CAN2 – RX Data Ready             | 00110111                             | 0X0540(C2RXD)                                           | —                                                      |

| CAN2 – TX Data Request           | 01000111                             | —                                                       | 0X0542(C2TXD)                                          |

| DCI – Codec Transfer Done        | 00111100                             | 0X0290(RXBUF0)                                          | 0X0298(TXBUF0)                                         |

| ADC1 – ADC1 Convert Done         | 00001101                             | 0x0300 (ADC1BUF0)                                       | _                                                      |

| ADC2 – ADC2 Convert Done         | 00010101                             | 0X0340(ADC2BUF0)                                        | —                                                      |

| PMP – PMP Data Move              | 00101101                             | 0X0608(PMPDAT1)                                         | 0X0608(PMPDAT1)                                        |

### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS (CONTINUED)

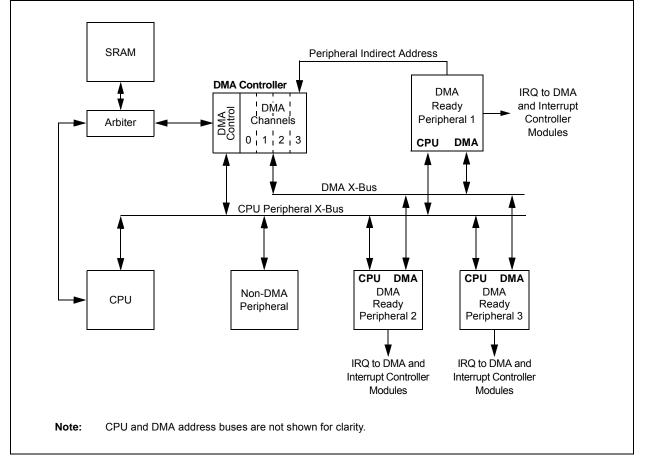

# FIGURE 8-2: DMA CONTROLLER BLOCK DIAGRAM

| <b>REGISTER 11-9: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12</b> |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

| U-0                    | R/W-0                | R/W-0                                                | R/W-0         | R/W-0                      | R/W-0          | R/W-0           | R/W-0   |

|------------------------|----------------------|------------------------------------------------------|---------------|----------------------------|----------------|-----------------|---------|

|                        | FX/VV-0              | N/W-0                                                | F\/VV-U       | FLT2R<6:0>                 | N/W-U          | N/W-0           | FV/VV-U |

| <br>bit 15             |                      |                                                      |               | 1 2121(<0.02               |                |                 | bit 8   |

|                        |                      |                                                      |               |                            |                |                 | DILO    |

| U-0                    | R/W-0                | R/W-0                                                | R/W-0         | R/W-0                      | R/W-0          | R/W-0           | R/W-0   |

|                        |                      |                                                      |               | FLT1R<6:0>                 |                |                 |         |

| bit 7                  |                      |                                                      |               |                            |                |                 | bit 0   |

|                        |                      |                                                      |               |                            |                |                 |         |

| Legend:<br>R = Readabl | e hit                | W = Writable                                         | hit           | U = Unimplen               | nented hit rea | ad as 'N'       |         |

| -n = Value at          |                      | '1' = Bit is set                                     |               | '0' = Bit is clea          |                | x = Bit is unkr | NOWD    |

|                        |                      |                                                      |               |                            |                |                 |         |

| bit 15                 | Unimplemen           | ted: Read as '                                       | 0'            |                            |                |                 |         |

| bit 14-8               |                      | Assign PWM I<br>-2 for input pin                     |               | ) to the Corresp<br>nbers) | onding RPn F   | Pin bits        |         |

|                        | 1111100 <b>= I</b> r | nput tied to RPI                                     | 124           |                            |                |                 |         |

|                        | •                    |                                                      |               |                            |                |                 |         |

|                        | •                    |                                                      |               |                            |                |                 |         |

|                        | 0000001 = lr         | nput tied to CM                                      | P1            |                            |                |                 |         |

|                        |                      | nput tied to Vss                                     |               |                            |                |                 |         |

| bit 7                  | Unimplemen           | ted: Read as '                                       | 0'            |                            |                |                 |         |

| bit 6-0                | (see Table 11        | Assign PWM I<br>-2 for input pin<br>nput tied to RPI | selection nun | ) to the Corresp<br>nbers) | onding RPn F   | Pin bits        |         |

|                        | •                    |                                                      |               |                            |                |                 |         |

|                        |                      | nput tied to CM<br>nput tied to Vss                  |               |                            |                |                 |         |

# 13.0 TIMER2/3, TIMER4/5, TIMER6/7 AND TIMER8/9

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Timers" (DS70362), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3, Timer4/5, Timer6/7 and Timer8/9 modules are 32-bit timers, which can also be configured as eight independent 16-bit timers with selectable operating modes.

As a 32-bit timer, Timer2/3, Timer4/5, Timer6/7 and Timer8/9 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with All 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

- They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare modules

- ADC1 Event Trigger (Timer2/3 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON, T5CON, T6CON, T7CON, T8CON and T9CON registers. T2CON, T4CON, T6CON and T8CON are shown in generic form in Register 13-1. T3CON, T5CON, T7CON and T9CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2, Timer4, Timer6 and Timer8 are the least significant word (Isw); Timer3, Timer5, Timer7 and Timer9 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON, T5CON, T7CON and T9CON register control bits are ignored. Only T2CON, T4CON, T6CON and T8CON register control bits are used for setup and control. Timer2, Timer4, Timer6 and Timer8 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3, Timer5, Timer7 and Timer9 interrupt flags.

A block diagram for an example of a 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

Note: Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

# 13.1 Timer Control Registers

# REGISTER 13-1: TxCON (T2CON, T4CON, T6CON AND T8CON) CONTROL REGISTER

| R/W-0            | U-0                            | R/W-0                               | U-0            | U-0              | U-0             | U-0                | U-0   |

|------------------|--------------------------------|-------------------------------------|----------------|------------------|-----------------|--------------------|-------|

| TON              |                                | TSIDL                               | —              | —                | _               | —                  |       |

| bit 15           |                                |                                     |                |                  |                 |                    | bit 8 |

|                  |                                |                                     |                |                  |                 |                    |       |

| U-0              | R/W-0                          | R/W-0                               | R/W-0          | R/W-0            | U-0             | R/W-0              | U-0   |

|                  | TGATE                          | TCKPS1                              | TCKPS0         | T32              | _               | TCS <sup>(1)</sup> | _     |

| bit 7            |                                |                                     |                |                  |                 |                    | bit 0 |

|                  |                                |                                     |                |                  |                 |                    |       |

| Legend:          |                                |                                     |                |                  |                 |                    |       |

| R = Readable b   |                                | W = Writable                        |                | •                | nented bit, rea |                    |       |

| -n = Value at P0 | DR                             | '1' = Bit is set                    |                | '0' = Bit is cle | ared            | x = Bit is unkn    | iown  |

|                  |                                | 0.1.1                               |                |                  |                 |                    |       |

|                  | TON: Timerx                    |                                     |                |                  |                 |                    |       |

|                  | When T32 = 1<br>1 = Starts 32- |                                     |                |                  |                 |                    |       |

|                  | 0 = Stops 32-                  |                                     |                |                  |                 |                    |       |

|                  | When T32 =                     |                                     |                |                  |                 |                    |       |

|                  | 1 = Starts 16-                 |                                     |                |                  |                 |                    |       |

| bit 14           | 0 = Stops 16-                  | ted: Read as '                      | o'             |                  |                 |                    |       |

|                  | -                              | x Stop in Idle M                    |                |                  |                 |                    |       |

| bit 15           |                                | ues module op                       |                | device enters l  | dle mode        |                    |       |

|                  |                                | s module opera                      |                |                  |                 |                    |       |

| bit 12-7         | Unimplemen                     | ted: Read as '                      | 0'             |                  |                 |                    |       |

| bit 6            | TGATE: Time                    | erx Gated Time                      | Accumulation   | Enable bit       |                 |                    |       |

|                  | When TCS =                     |                                     |                |                  |                 |                    |       |

|                  | This bit is igno               |                                     |                |                  |                 |                    |       |

|                  | When TCS =<br>1 = Gated tim    | <u><i>u.</i></u><br>le accumulatior | n is enabled   |                  |                 |                    |       |

|                  |                                | e accumulation                      |                |                  |                 |                    |       |

| bit 5-4          | TCKPS<1:0>                     | : Timerx Input                      | Clock Prescal  | e Select bits    |                 |                    |       |

|                  | 11 = 1:256                     |                                     |                |                  |                 |                    |       |

|                  | 10 = 1:64<br>01 = 1:8          |                                     |                |                  |                 |                    |       |

|                  | 00 = 1:1                       |                                     |                |                  |                 |                    |       |

| bit 3            | T32: 32-Bit Ti                 | mer Mode Sele                       | ect bit        |                  |                 |                    |       |

|                  | 1 = Timerx an                  | nd Timery form                      | a single 32-bi | t timer          |                 |                    |       |

|                  |                                | nd Timery act a                     |                | ners             |                 |                    |       |

|                  |                                | ted: Read as '                      |                |                  |                 |                    |       |

|                  |                                | Clock Source S                      |                |                  |                 |                    |       |

|                  |                                | clock is from pir                   | n, TxCK (on th | e rising edge)   |                 |                    |       |

|                  | 0 = Internal cl                |                                     |                |                  |                 |                    |       |

| bit 0            |                                | ted: Read as '                      | n'             |                  |                 |                    |       |

#### U-0 U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 \_\_\_\_ \_\_\_\_ **BLANKSEL3 BLANKSEL2** BLANKSEL1 **BLANKSEL0** \_\_\_\_ \_\_\_\_ bit 15 bit 8 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 CHOPSEL2 CHOPSEL1 CHOPHEN CHOPSEL3 CHOPSEL0 CHOPLEN \_ bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown bit 15-12 Unimplemented: Read as '0' bit 11-8 BLANKSEL<3:0>: PWMx State Blank Source Select bits The selected state blank signal will block the current-limit and/or Fault input signals (if enabled via the BCH and BCL bits in the LEBCONx register). 1001 = Reserved 0110 = PWM6H is selected as state blank source 0101 = PWM5H is selected as state blank source 0100 = PWM4H is selected as state blank source 0011 = PWM3H is selected as state blank source 0010 = PWM2H is selected as state blank source 0001 = PWM1H is selected as state blank source 0000 = No state blanking bit 7-6 Unimplemented: Read as '0' bit 5-2 CHOPSEL<3:0>: PWMx Chop Clock Source Select bits The selected signal will enable and disable (CHOP) the selected PWMx outputs. 1001 = Reserved 0110 = PWM6H is selected as state blank source 0101 = PWM5H is selected as state blank source 0100 = PWM4H is selected as state blank source 0011 = PWM3H is selected as CHOP clock source 0010 = PWM2H is selected as CHOP clock source 0001 = PWM1H is selected as CHOP clock source 0000 = Chop clock generator is selected as CHOP clock source bit 1 CHOPHEN: PWMxH Output Chopping Enable bit 1 = PWMxH chopping function is enabled 0 = PWMxH chopping function is disabled bit 0 CHOPLEN: PWMxL Output Chopping Enable bit 1 = PWMxL chopping function is enabled 0 = PWMxL chopping function is disabled

### REGISTER 16-24: AUXCONx: PWMx AUXILIARY CONTROL REGISTER

# 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Quadrature Encoder Interface (QEI)" (DS70601) which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

This chapter describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI module include:

- · 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 16-Bit Velocity Counter

- 32-Bit Position Initialization/Capture/Compare High Register

- 32-Bit Position Compare Low Register

- x4 Quadrature Count mode

- External Up/Down Count mode

- External Gated Count mode

- · External Gated Timer mode

- Internal Timer mode

Figure 17-1 illustrates the QEIx block diagram.

# 19.0 INTER-INTEGRATED CIRCUIT<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70000195), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX family of devices contains two Inter-Integrated Circuit ( $I^2C$ ) modules: I2C1 and I2C2.

The  $I^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface. The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx pin is clock.

- The SDAx pin is data.

The  $I^2C$  module offers the following key features:

- I<sup>2</sup>C Interface Supporting both Master and Slave modes of Operation.

- I<sup>2</sup>C Slave mode Supports 7 and 10-Bit Addressing.

- I<sup>2</sup>C Master mode Supports 7 and 10-Bit Addressing.

- I<sup>2</sup>C Port Allows Bidirectional Transfers Between Master and Slaves.

- Serial Clock Synchronization for I<sup>2</sup>C Port can be used as a Handshake Mechanism to Suspend and Resume Serial Transfer (SCLREL control).

- I<sup>2</sup>C Supports Multi-Master Operation, Detects Bus Collision and Arbitrates Accordingly.

- Intelligent Platform Management Interface (IPMI)

Support

- System Management Bus (SMBus) Support

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX family of devices contains four UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGM3XX/6XX/7XX device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: Hardware flow control using UxRTS and UxCTS is not available on all pin count devices. See the "Pin Diagrams" section for availability.

The primary features of the UART module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop Bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for All UART Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA<sup>®</sup> Support

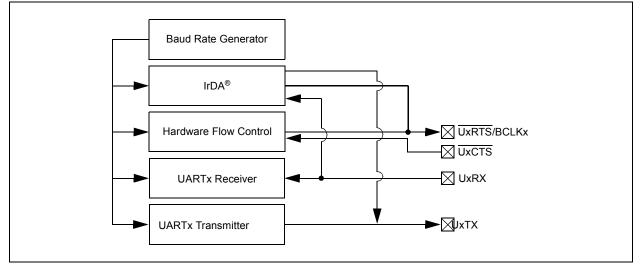

A simplified block diagram of the UART module is shown in Figure 20-1. The UART module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2013-2014 Microchip Technology Inc.

NOTES:

# REGISTER 23-2: ADxCON2: ADCx CONTROL REGISTER 2 (CONTINUED)

| bit 6-2 | SMPI<4:0>: Increment Rate bits                                                                                                                                                           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | When ADDMAEN = 0:                                                                                                                                                                        |

|         | x1111 = Generates interrupt after completion of every 16th sample/conversion operation                                                                                                   |

|         | x1110 = Generates interrupt after completion of every 15th sample/conversion operation                                                                                                   |

|         | •                                                                                                                                                                                        |

|         | •                                                                                                                                                                                        |

|         |                                                                                                                                                                                          |

|         | x0001 = Generates interrupt after completion of every 2nd sample/conversion operation<br>x0000 = Generates interrupt after completion of every sample/conversion operation               |

|         | When ADDMAEN = 1:                                                                                                                                                                        |

|         | 11111 = Increments the DMA address after completion of every 32nd sample/conversion operation                                                                                            |

|         | 11110 = Increments the DMA address after completion of every 31st sample/conversion operation                                                                                            |

|         | •                                                                                                                                                                                        |

|         | •                                                                                                                                                                                        |

|         | •                                                                                                                                                                                        |

|         | 00001 = Increments the DMA address after completion of every 2nd sample/conversion operation<br>00000 = Increments the DMA address after completion of every sample/conversion operation |

| bit 1   | BUFM: Buffer Fill Mode Select bit                                                                                                                                                        |

|         | 1 = Starts buffer filling the first half of the buffer on the first interrupt and the second half of the buffer<br>on the next interrupt                                                 |

|         | 0 = Always starts filling the buffer from the Start address                                                                                                                              |

| bit 0   | ALTS: Alternate Input Sample Mode Select bit                                                                                                                                             |

|         | 1 = Uses channel input selects for Sample MUXA on the first sample and Sample MUXB on the next sample 0 = Always uses channel input selects for Sample MUXA                              |

| Note 1: | The '001', '010' and '011' bit combinations for VCFG<2:0> are not applicable on ADC2.                                                                                                    |

2: ADC2 does not support external VREF± inputs.

| R/W-0                 | U-0                                                                                                       | U-0                                                                                               | R/W-0                                              | R/W-0                           | R/W-0                | R/W-0                | R/W-0                |

|-----------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------|----------------------|----------------------|----------------------|

| ADRC                  | _                                                                                                         |                                                                                                   | SAMC4 <sup>(1)</sup>                               | SAMC3 <sup>(1)</sup>            | SAMC2 <sup>(1)</sup> | SAMC1 <sup>(1)</sup> | SAMC0 <sup>(1)</sup> |

| bit 15                |                                                                                                           | ·                                                                                                 | •                                                  |                                 |                      |                      | bit 8                |

| R/W-0                 | R/W-0                                                                                                     | R/W-0                                                                                             | R/W-0                                              | R/W-0                           | R/W-0                | R/W-0                | R/W-0                |

| ADCS7(2)              | ADCS6 <sup>(2)</sup>                                                                                      | ADCS5 <sup>(2)</sup>                                                                              | ADCS4 <sup>(2)</sup>                               | ADCS3 <sup>(2)</sup>            | ADCS2 <sup>(2)</sup> | ADCS1 <sup>(2)</sup> | ADCS0 <sup>(2)</sup> |

| bit 7                 |                                                                                                           |                                                                                                   |                                                    |                                 |                      |                      | bit (                |

| Legend:               |                                                                                                           |                                                                                                   |                                                    |                                 |                      |                      |                      |

| R = Readable          | e bit                                                                                                     | W = Writable I                                                                                    | bit                                                | U = Unimplen                    | nented bit, read     | d as '0'             |                      |

| -n = Value at         | POR                                                                                                       | '1' = Bit is set                                                                                  |                                                    | '0' = Bit is cle                | ared                 | x = Bit is unkr      | nown                 |

| bit 14-13<br>bit 12-8 | Unimplemen                                                                                                | ived from syste<br>ted: Read as '(<br>Auto-Sample T<br>AD                                         | )'                                                 |                                 |                      |                      |                      |

|                       | •<br>•<br>00001 = 1 TA<br>00000 = 0 TA                                                                    | D                                                                                                 |                                                    |                                 |                      |                      |                      |

| bit 7-0               | 11111111 =<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ADCx Convers<br>TP • (ADCS<7:<br>TP • (ADCS<7:<br>TP • (ADCS<7:<br>TP • (ADCS<7:<br>TP • (ADCS<7: | 0> + 1) = TP •<br>0> + 1) = TP •<br>0> + 1) = TP • | 256 = Tad<br>3 = Tad<br>2 = Tad |                      |                      |                      |

|                       | nis bit is only use<br>nis bit is not usec                                                                |                                                                                                   | •                                                  | ,                               | nd SSRCG (AD         | 1CON1<4>) =          | 0.                   |

| REGISTER 23-3: ADXCONS: ADCX CONTROL REGISTER 3 | REGISTER 23-3: | ADxCON3: ADCx CONTROL REGISTER 3 |

|-------------------------------------------------|----------------|----------------------------------|

|-------------------------------------------------|----------------|----------------------------------|

# REGISTER 27-9: ALRMVAL (WHEN ALRMPTR<1:0> = 01): ALARM WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-----|-----|-------|-------|-------|

| —      | _   | —   | —   | —   | WDAY2 | WDAY1 | WDAY0 |

| bit 15 |     |     |     |     |       |       | bit 8 |

|        |     |     |     |     |       |       |       |

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 10-8 **WDAY<2:0>:** Binary Coded Decimal Value of Weekday Digit bits Contains a value from 0 to 6.

bit 7-6 Unimplemented: Read as '0'

- bit 5-4 **HRTEN<1:0>:** Binary Coded Decimal Value of Hour's Tens Digit bits Contains a value from 0 to 2.

- bit 3-0 **HRONE<3:0>:** Binary Coded Decimal Value of Hour's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### REGISTER 29-3: CRCXORH: CRC XOR POLYNOMIAL HIGH REGISTER

| R/W-0                              | R/W-0          | R/W-0       | R/W-0                                           | R/W-0                                                                                                     | R/W-0                                                                                          | R/W-0                                                                                                                                     |

|------------------------------------|----------------|-------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|                                    |                | X<3         | 31:24>                                          |                                                                                                           |                                                                                                |                                                                                                                                           |

|                                    |                |             |                                                 |                                                                                                           |                                                                                                | bit 8                                                                                                                                     |

|                                    |                |             |                                                 |                                                                                                           |                                                                                                |                                                                                                                                           |

| R/W-0                              | R/W-0          | R/W-0       | R/W-0                                           | R/W-0                                                                                                     | R/W-0                                                                                          | R/W-0                                                                                                                                     |

|                                    |                | X<2         | 23:16>                                          |                                                                                                           |                                                                                                |                                                                                                                                           |

|                                    |                |             |                                                 |                                                                                                           |                                                                                                | bit 0                                                                                                                                     |

|                                    |                |             |                                                 |                                                                                                           |                                                                                                |                                                                                                                                           |

|                                    |                |             |                                                 |                                                                                                           |                                                                                                |                                                                                                                                           |

| oit                                | W = Writable b | oit         | U = Unimplemented bit, read as '0'              |                                                                                                           |                                                                                                |                                                                                                                                           |

| -n = Value at POR '1' = Bit is set |                |             | '0' = Bit is cleared x = Bit is unknown         |                                                                                                           |                                                                                                |                                                                                                                                           |

|                                    | R/W-0          | R/W-0 R/W-0 | R/W-0         R/W-0         R/W-0           X<2 | X<31:24>         R/W-0       R/W-0         X<23:16>         Dit       W = Writable bit       U = Unimpler | X<31:24> $R/W-0 R/W-0 R/W-0 R/W-0$ $X<23:16>$ bit W = Writable bit U = Unimplemented bit, real | X<31:24>         R/W-0       R/W-0       R/W-0       R/W-0 $X<23:16>$ bit       W = Writable bit       U = Unimplemented bit, read as '0' |

bit 15-0 X<31:16>: XOR of Polynomial Term X<sup>n</sup> Enable bits

#### REGISTER 29-4: CRCXORL: CRC XOR POLYNOMIAL LOW REGISTER

| R/W-0                             | R/W-0   | R/W-0            | R/W-0  | R/W-0                              | R/W-0   | R/W-0              | R/W-0 |

|-----------------------------------|---------|------------------|--------|------------------------------------|---------|--------------------|-------|

|                                   |         |                  | Х<     | 15:8>                              |         |                    |       |

| bit 15                            |         |                  |        |                                    |         |                    | bit 8 |

| R/W-0                             | R/W-0   | R/W-0            | R/W-0  | R/W-0                              | R/W-0   | R/W-0              | U-0   |

| 10.00-0                           | 10,00-0 | 10.00-0          | X<7:1> | 10.00-0                            | 10.00-0 | 10.00-0            | _     |

| bit 7                             |         |                  |        |                                    |         |                    | bit 0 |

| Legend:                           |         |                  |        |                                    |         |                    |       |

| R = Readable bit W = Writable bit |         |                  | bit    | U = Unimplemented bit, read as '0' |         |                    |       |

| -n = Value at POR                 |         | '1' = Bit is set |        | '0' = Bit is cleared               |         | x = Bit is unknown |       |

bit 15-1X<15:1>: XOR of Polynomial Term X<sup>n</sup> Enable bitsbit 0Unimplemented: Read as '0'

# 33.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33EPXXXGM3XX/6XX/7XX electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXXGM3XX/6XX/7XX family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# **Absolute Maximum Ratings**

#### (See Note 1)

| Ambient temperature under bias                                                | 40°C to +125°C       |

|-------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                           | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                            | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 3.0V^{(3)}$  | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD < 3.0V^{(3)}$    | -0.3V to +3.6V       |

| Voltage on VCAP with respect to Vss                                           | 1.62V to 1.98V       |

| Maximum current out of Vss pin                                                | 350 mA               |

| Maximum current into Vod pin <sup>(2)</sup>                                   | 350 mA               |

| Maximum current sunk by any I/O pin                                           | 20 mA                |

| Maximum current sourced by I/O pin                                            |                      |

| Maximum current sourced/sunk by all ports <sup>(2,4)</sup>                    | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 33-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

- 4: Exceptions are: RA3, RA4, RA7, RA9, RA10, RB7-RB15, RC3, RC15, RD1-RD4, which are able to sink 30 mA and source 20 mA.

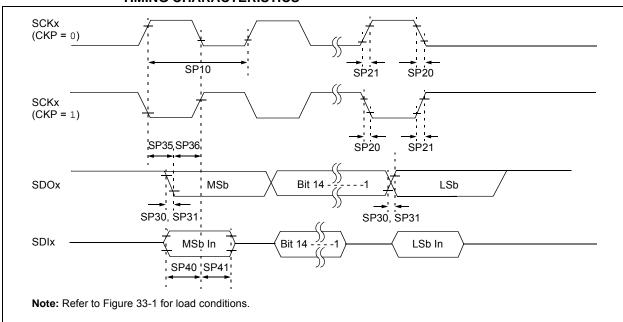

### FIGURE 33-18: SPI2 AND SPI3 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 33-35:SPI2 AND SPI3 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1)TIMING REQUIREMENTS

| АС СНА | RACTERIST             | ICS                                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |            |     |                             |

|--------|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|-----|-----------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Conditions |     |                             |

| SP10   | FscP                  | Maximum SCKx Frequency                        |                                                                                                                                                                                                                                                                                         | —                   | 9          | MHz | -40°C to +125°C<br>(Note 3) |

| SP20   | TscF                  | SCKx Output Fall Time                         | _                                                                                                                                                                                                                                                                                       | —                   | _          | ns  | See Parameter DO32 (Note 4) |

| SP21   | TscR                  | SCKx Output Rise Time                         | _                                                                                                                                                                                                                                                                                       | —                   | _          | ns  | See Parameter DO31 (Note 4) |

| SP30   | TdoF                  | SDOx Data Output Fall Time                    | _                                                                                                                                                                                                                                                                                       | —                   |            | ns  | See Parameter DO32 (Note 4) |

| SP31   | TdoR                  | SDOx Data Output Rise Time                    | _                                                                                                                                                                                                                                                                                       | —                   | _          | ns  | See Parameter DO31 (Note 4) |

| SP35   | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge     | _                                                                                                                                                                                                                                                                                       | 6                   | 20         | ns  |                             |

| SP36   | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge  | 30                                                                                                                                                                                                                                                                                      | —                   | _          | ns  |                             |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30                                                                                                                                                                                                                                                                                      | —                   | —          | ns  |                             |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge     | 30                                                                                                                                                                                                                                                                                      | _                   |            | ns  |                             |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPIx pins.

# dsPIC33EPXXXGM3XX/6XX/7XX

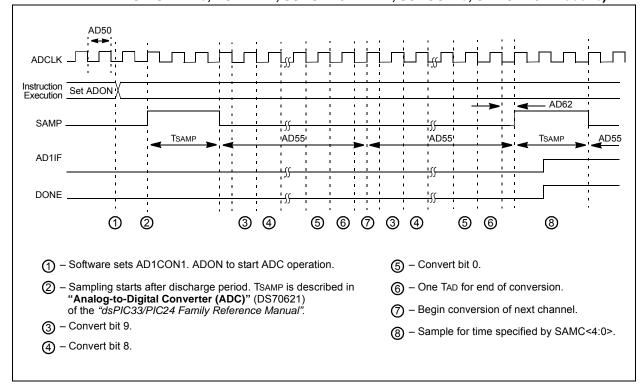

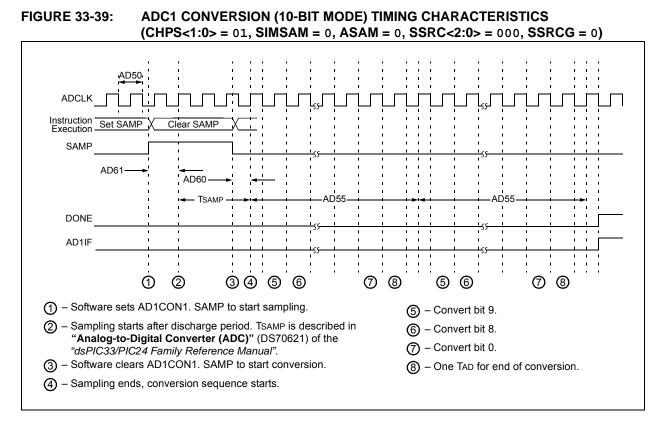

### FIGURE 33-40: ADC1 CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SSRCG = 0, SAMC<4:0> = 00010)