Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT   |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 48K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | -                                                                                 |

| Data Converters            | A/D 18x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

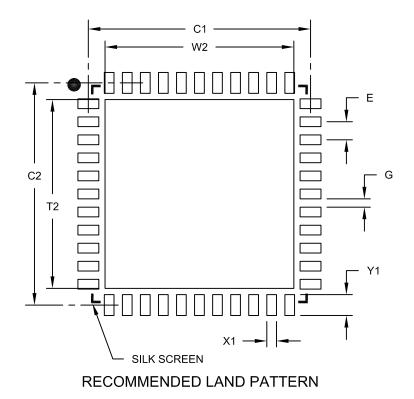

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-TQFP                                                                           |

| Supplier Device Package    | 44-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gm304t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

dsPIC33EPXXXGM3XX/6XX/7XX

### 4.5.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed, but the contents of the register remain unchanged.

# 4.6 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms; it is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.6.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all of these conditions are met:

- BWM bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume       |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|

|       | word-sized data (LSb of every EA is always    |  |  |  |  |  |  |  |

|       | clear). The XB value is scaled accordingly to |  |  |  |  |  |  |  |

|       | generate compatible (byte) addresses.         |  |  |  |  |  |  |  |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo    | Addressing                                  | and     | Bit-Rev  | ersed |  |  |  |  |  |

|-------|-----------|---------------------------------------------|---------|----------|-------|--|--|--|--|--|

|       | Addressi  | Addressing can be enabled simultaneously    |         |          |       |  |  |  |  |  |

|       | using the | using the same W register, but Bit-Reversed |         |          |       |  |  |  |  |  |

|       | Addressi  | Addressing operation will always take       |         |          |       |  |  |  |  |  |

|       | preceder  | nce for data w                              | rites w | hen enab | led.  |  |  |  |  |  |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

## REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0            | U-0                                                                | U-0 | U-0   | U-0     | U-0 | U-0 | U-0   |  |  |

|----------------|--------------------------------------------------------------------|-----|-------|---------|-----|-----|-------|--|--|

| —              |                                                                    | —   | —     | —       | —   | —   | —     |  |  |

| bit 15         |                                                                    |     |       |         |     |     | bit 8 |  |  |

|                |                                                                    |     |       |         |     |     |       |  |  |

| W-0            | W-0                                                                | W-0 | W-0   | W-0     | W-0 | W-0 | W-0   |  |  |

|                |                                                                    |     | NVMKI | EY<7:0> |     |     |       |  |  |

| bit 7          |                                                                    |     |       |         |     |     | bit 0 |  |  |

|                |                                                                    |     |       |         |     |     |       |  |  |

| Legend:        |                                                                    |     |       |         |     |     |       |  |  |

| R = Readable I | = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |       |         |     |     |       |  |  |

|                |                                                                    |     |       |         |     |     |       |  |  |

'0' = Bit is cleared

bit 15-8 Unimplemented: Read as '0'

-n = Value at POR

bit 7-0 NVMKEY<7:0>: NVM Key Register (write-only) bits

'1' = Bit is set

# REGISTER 5-5: NVMSRCADRH: NONVOLATILE DATA MEMORY UPPER ADDRESS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-x             | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|-------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| NVMSRCADRH<23:16> |       |       |       |       |       |       |       |  |  |

| bit 7             |       |       |       |       |       |       | bit 0 |  |  |

|                   |       |       |       |       |       |       |       |  |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMSRCADRH<23:16>: Nonvolatile Data Memory Upper Address bits

x = Bit is unknown

| U-0          | U-0                    | U-0                             | U-0            | U-0              | U-0                        | U-0                | R/W-0     |  |  |  |

|--------------|------------------------|---------------------------------|----------------|------------------|----------------------------|--------------------|-----------|--|--|--|

| _            | —                      | —                               | —              | —                | —                          | _                  | PLLDIV<8> |  |  |  |

| bit 15       |                        |                                 |                |                  |                            |                    | bit 8     |  |  |  |

|              |                        |                                 |                |                  |                            |                    |           |  |  |  |

| R/W-0        | R/W-0                  | R/W-1                           | R/W-1          | R/W-0            | R/W-0                      | R/W-0              | R/W-0     |  |  |  |

|              |                        |                                 | PLLD           | IV<7:0>          |                            |                    |           |  |  |  |

| bit 7        |                        |                                 |                |                  |                            |                    | bit 0     |  |  |  |

|              |                        |                                 |                |                  |                            |                    |           |  |  |  |

| Legend:      |                        |                                 |                |                  |                            |                    |           |  |  |  |

| R = Readab   | ole bit                | W = Writable                    | bit            | U = Unimpler     | plemented bit, read as '0' |                    |           |  |  |  |

| -n = Value a | at POR                 | '1' = Bit is set                |                | '0' = Bit is cle | ared                       | x = Bit is unknown |           |  |  |  |

|              |                        |                                 |                |                  |                            |                    |           |  |  |  |

| bit 15-9     | Unimplemer             | nted: Read as '                 | o'             |                  |                            |                    |           |  |  |  |

| bit 8-0      | PLLDIV<8:0             | >: PLL Feedbac                  | k Divisor bits | s (also denoted  | as 'M', PLL mu             | ltiplier)          |           |  |  |  |

|              | 111111111              | = 513                           |                |                  |                            |                    |           |  |  |  |

|              | •                      |                                 |                |                  |                            |                    |           |  |  |  |

|              | •                      |                                 |                |                  |                            |                    |           |  |  |  |

|              | •                      | 000110000 <b>= 50 (default)</b> |                |                  |                            |                    |           |  |  |  |

|              | •                      |                                 |                |                  |                            |                    |           |  |  |  |

|              | •                      |                                 |                |                  |                            |                    |           |  |  |  |

|              | •                      |                                 |                |                  |                            |                    |           |  |  |  |

|              | 00000010               |                                 |                |                  |                            |                    |           |  |  |  |

|              | 000000001<br>000000000 |                                 |                |                  |                            |                    |           |  |  |  |

|              | 000000000              | - <b>L</b>                      |                |                  |                            |                    |           |  |  |  |

# REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

# 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation. For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

# **10.4** Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled, using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

Note: If a PMD bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

| R/W-0          | R/W-0       | R/W-0                                | R/W-0                    | U-0              | R/W-0           | R/W-0                 | R/W-0  |

|----------------|-------------|--------------------------------------|--------------------------|------------------|-----------------|-----------------------|--------|

| T9MD           | T8MD        | T7MD                                 | T6MD                     | —                | CMPMD           | RTCCMD <sup>(1)</sup> | PMPMD  |

| bit 15         |             |                                      |                          |                  |                 |                       | bit    |

| DAALO          | DAMA        | DAALO                                | DAMA                     | <b>D</b> /// 0   | <b>D</b> 444.0  | DAALO                 | DANA   |

| R/W-0          | R/W-0       | R/W-0                                | R/W-0                    | R/W-0            | R/W-0           | R/W-0                 | R/W-0  |

| CRCMD<br>bit 7 | DACMD       | QEI2MD                               | PWM2MD                   | U3MD             | I2C3MD          | I2C2MD                | ADC2MD |

|                |             |                                      |                          |                  |                 |                       |        |

| Legend:        |             |                                      |                          |                  |                 |                       |        |

| R = Readable   | e bit       | W = Writable                         | bit                      | U = Unimpler     | nented bit, rea | d as '0'              |        |

| -n = Value at  | POR         | '1' = Bit is set                     |                          | '0' = Bit is cle | ared            | x = Bit is unkn       | own    |

| bit 15         | T9MD: Timer | 9 Module Disab                       | le bit                   |                  |                 |                       |        |

|                |             | odule is disable<br>odule is enable  |                          |                  |                 |                       |        |

| bit 13         | T8MD: Timer | 8 Module Disab                       | le bit                   |                  |                 |                       |        |

|                |             | odule is disable<br>odule is enable  |                          |                  |                 |                       |        |

| bit 14         | T7MD: Timer | 7 Module Disab                       | le bit                   |                  |                 |                       |        |

|                | -           | odule is disable<br>odule is enable  |                          |                  |                 |                       |        |

| bit 12         | T6MD: Timer | 6 Module Disab                       | le bit                   |                  |                 |                       |        |

|                |             | odule is disable<br>odule is enable  |                          |                  |                 |                       |        |

| bit 11         | Unimplemen  | ted: Read as 'd                      | )'                       |                  |                 |                       |        |

| bit 10         | CMPMD: Cor  | nparator Modul                       | e Disable bit            |                  |                 |                       |        |

|                |             | tor module is di<br>tor module is er |                          |                  |                 |                       |        |

| bit 9          | RTCCMD: RT  | FCC Module Dis                       | sable bit <sup>(1)</sup> |                  |                 |                       |        |

|                |             | odule is disable<br>odule is enable  |                          |                  |                 |                       |        |

| bit 8          | PMPMD: PMI  | P Module Disat                       | ole bit                  |                  |                 |                       |        |

|                |             | lule is disabled<br>lule is enabled  |                          |                  |                 |                       |        |

| bit 7          | CRCMD: CR   | C Module Disat                       | ole bit                  |                  |                 |                       |        |

|                |             | lule is disabled<br>lule is enabled  |                          |                  |                 |                       |        |

| bit 6          | DACMD: DAG  | C Module Disat                       | ole bit                  |                  |                 |                       |        |

|                |             | lule is disabled<br>lule is enabled  |                          |                  |                 |                       |        |

| bit 5          | QEI2MD: QE  | I2 Module Disa                       | ble bit                  |                  |                 |                       |        |

|                |             | dule is disabled<br>dule is enabled  |                          |                  |                 |                       |        |

| bit 4          | PWM2MD: P   | WM2 Module D                         | isable bit               |                  |                 |                       |        |

|                |             | odule is disable<br>odule is enable  |                          |                  |                 |                       |        |

### REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

**Note 1:** The RTCCMD bit is not available on 44-pin devices.

| Selec | eral Pin<br>et Input<br>er Value | Input/<br>Output | Pin Assignment | Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment |

|-------|----------------------------------|------------------|----------------|--------------------------------------------------|------------------|----------------|

| 010   | 1001                             | I/O              | RP41           | 101 0101                                         | —                |                |

| 010   | 1010                             | I/O              | RP42           | 101 0110                                         | —                | —              |

| 010   | 1011                             | I/O              | RP43           | 101 0111                                         | —                | —              |

| 101   | 1000                             | —                | —              | 110 1100                                         |                  | —              |

| 101   | 1001                             | —                | —              | 110 1101                                         | —                | —              |

| 101   | 1010                             | —                | —              | 110 1110                                         | —                | —              |

| 101   | 1011                             | —                | —              | 110 1111                                         |                  | —              |

| 101   | 1100                             | —                | —              | 111 0000                                         | I                | RPI112         |

| 101   | 1101                             | —                | —              | 111 0001                                         | I/O              | RP113          |

| 101   | 1110                             | I                | RPI94          | 111 0010                                         | —                |                |

| 101   | 1111                             | I                | RPI95          | 111 0011                                         | —                | —              |

| 110   | 0000                             | I                | RPI96          | 111 0100                                         | —                | _              |

| 110   | 0001                             | I/O              | RP97           | 111 0101                                         | —                |                |

| 110   | 0010                             | —                | —              | 111 0110                                         | I/O              | RP118          |

| 110   | 0011                             | —                | —              | 111 0111                                         | I                | RPI119         |

| 110   | 0100                             | —                | _              | 111 1000                                         | I/O              | RP120          |

| 110   | 0101                             | —                | —              | 111 1001                                         | I                | RPI121         |

| 110   | 0110                             | —                | _              | 111 1010                                         | —                | _              |

| 110   | 0111                             | —                | —              | 111 1011                                         | —                |                |

| 110   | 1000                             | —                | —              | 111 1100                                         | I                | RPI124         |

| 110   | 1001                             | —                | —              | 111 1101                                         | I/O              | RP125          |

| 110   | 1010                             | —                |                | 111 1110                                         | I/O              | RP126          |

| 110   | 1011                             | —                |                | 111 1111                                         | I/O              | RP127          |

# TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES (CONTINUED)

**Legend:** Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

| U-0          | U-0                | U-0              | U-0   | U-0                                | U-0            | U-0                | U-0   |  |

|--------------|--------------------|------------------|-------|------------------------------------|----------------|--------------------|-------|--|

| _            | —                  | —                | —     | —                                  | —              | _                  | _     |  |

| bit 15       |                    | ·                |       |                                    |                |                    | bit 8 |  |

|              |                    |                  |       |                                    |                |                    |       |  |

| U-0          | R/W-0              | R/W-0            | R/W-0 | R/W-0                              | R/W-0          | R/W-0              | R/W-0 |  |

| _            |                    |                  |       | T2CKR<6:0>                         | >              |                    |       |  |

| bit 7        |                    |                  |       |                                    |                |                    | bit 0 |  |

|              |                    |                  |       |                                    |                |                    |       |  |

| Legend:      |                    |                  |       |                                    |                |                    |       |  |

| R = Readat   | ole bit            | W = Writable     | bit   | U = Unimplemented bit, read as '0' |                |                    |       |  |

| -n = Value a | at POR             | '1' = Bit is set |       | '0' = Bit is cleared               |                | x = Bit is unknown |       |  |

|              |                    |                  |       |                                    |                |                    |       |  |

| bit 15-7     | Unimplemer         | ted: Read as '   | 0'    |                                    |                |                    |       |  |

| bit 6-0      |                    | -: Assign Timer  |       | . ,                                | he Correspondi | ng RPn pin bits    | 3     |  |

|              | 1111100 <b>=  </b> | nput tied to RP  | 124   |                                    |                |                    |       |  |

|              | •                  |                  |       |                                    |                |                    |       |  |

|              | •                  |                  |       |                                    |                |                    |       |  |

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

© 2013-2014 Microchip Technology Inc.

| U-0                                                                                                                                                      | U-0                            | U-0              | U-0   | U-0              | U-0              | U-0                | U-0   |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------|-------|------------------|------------------|--------------------|-------|--|--|--|

| —                                                                                                                                                        | —                              |                  | _     | —                |                  | —                  | —     |  |  |  |

| bit 15                                                                                                                                                   |                                |                  |       |                  |                  |                    | bit 8 |  |  |  |

|                                                                                                                                                          |                                |                  |       |                  |                  |                    |       |  |  |  |

| U-0                                                                                                                                                      | R/W-0                          | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0              | R/W-0 |  |  |  |

| —                                                                                                                                                        | OCFAR<6:0>                     |                  |       |                  |                  |                    |       |  |  |  |

| bit 7                                                                                                                                                    |                                |                  |       |                  |                  |                    | bit 0 |  |  |  |

|                                                                                                                                                          |                                |                  |       |                  |                  |                    |       |  |  |  |

| Legend:                                                                                                                                                  |                                |                  |       |                  |                  |                    |       |  |  |  |

| R = Readable                                                                                                                                             | bit                            | W = Writable     | bit   | U = Unimpler     | nented bit, read | as '0'             |       |  |  |  |

| -n = Value at F                                                                                                                                          | POR                            | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |  |  |

|                                                                                                                                                          |                                |                  |       |                  |                  |                    |       |  |  |  |

| bit 15-7                                                                                                                                                 | Unimplemen                     | ted: Read as '   | כ'    |                  |                  |                    |       |  |  |  |

| bit 6-0 <b>OCFAR&lt;6:0&gt;:</b> Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |                                |                  |       |                  |                  |                    |       |  |  |  |

|                                                                                                                                                          | 1111100 = Input tied to RPI124 |                  |       |                  |                  |                    |       |  |  |  |

|                                                                                                                                                          | •                              |                  |       |                  |                  |                    |       |  |  |  |

|                                                                                                                                                          | •                              |                  |       |                  |                  |                    |       |  |  |  |

|                                                                                                                                                          |                                |                  |       |                  |                  |                    |       |  |  |  |

## REGISTER 11-8: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

| <b>REGISTER 11-9: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12</b> |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

| U-0                    | R/W-0                          | R/W-0                                                                                                                                                      | R/W-0   | R/W-0                                              | R/W-0          | R/W-0              | R/W-0   |  |  |  |  |

|------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------|----------------|--------------------|---------|--|--|--|--|

|                        | FX/VV-0                        | N/W-0                                                                                                                                                      | FX/VV-U | FLT2R<6:0>                                         | N/W-U          | N/W-0              | FV/VV-U |  |  |  |  |

| <br>bit 15             |                                |                                                                                                                                                            |         | 1 2121(<0.02                                       |                |                    | bit 8   |  |  |  |  |

|                        |                                |                                                                                                                                                            |         |                                                    |                |                    | DILO    |  |  |  |  |

| U-0                    | R/W-0                          | R/W-0                                                                                                                                                      | R/W-0   | R/W-0                                              | R/W-0          | R/W-0              | R/W-0   |  |  |  |  |

|                        |                                |                                                                                                                                                            |         | FLT1R<6:0>                                         |                |                    |         |  |  |  |  |

| bit 7                  |                                |                                                                                                                                                            |         |                                                    |                |                    | bit 0   |  |  |  |  |

|                        |                                |                                                                                                                                                            |         |                                                    |                |                    |         |  |  |  |  |

| Legend:<br>R = Readabl | e hit                          | W = Writable                                                                                                                                               | hit     | II = I Inimplen                                    | nented hit rea | ad as 'N'          |         |  |  |  |  |

| -n = Value at          |                                | '1' = Bit is set                                                                                                                                           |         | U = Unimplemented bit, rea<br>'0' = Bit is cleared |                | x = Bit is unknown |         |  |  |  |  |

|                        |                                |                                                                                                                                                            |         |                                                    |                |                    |         |  |  |  |  |

| bit 15                 | Unimplemen                     | ted: Read as '                                                                                                                                             | 0'      |                                                    |                |                    |         |  |  |  |  |

| bit 14-8               |                                | Assign PWM I<br>-2 for input pin                                                                                                                           |         | ) to the Corresp<br>nbers)                         | onding RPn F   | Pin bits           |         |  |  |  |  |

|                        | 1111100 = Input tied to RPI124 |                                                                                                                                                            |         |                                                    |                |                    |         |  |  |  |  |

|                        | •                              |                                                                                                                                                            |         |                                                    |                |                    |         |  |  |  |  |

|                        | •                              |                                                                                                                                                            |         |                                                    |                |                    |         |  |  |  |  |

|                        | 0000001 = Input tied to CMP1   |                                                                                                                                                            |         |                                                    |                |                    |         |  |  |  |  |

|                        |                                | nput tied to Vss                                                                                                                                           |         |                                                    |                |                    |         |  |  |  |  |

| bit 7                  | Unimplemen                     | ted: Read as '                                                                                                                                             | 0'      |                                                    |                |                    |         |  |  |  |  |

| bit 6-0                | (see Table 11                  | FLT1R<6:0>: Assign PWM Fault 1 (FLT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers)<br>1111100 = Input tied to RPI124 |         |                                                    |                |                    |         |  |  |  |  |

|                        | •                              |                                                                                                                                                            |         |                                                    |                |                    |         |  |  |  |  |

|                        |                                | nput tied to CM<br>nput tied to Vss                                                                                                                        |         |                                                    |                |                    |         |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                                                           | R/W-0              | R/W-0              | R/W-0                              | R/W-0                                    | U-0               | U-0           |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------------------------------------|------------------------------------------|-------------------|---------------|--|--|--|--|

| PHR             | PHF                                                                                                                                                             | PLR                | PLF                | FLTLEBEN                           | CLLEBEN                                  |                   |               |  |  |  |  |

| bit 15          |                                                                                                                                                                 |                    |                    |                                    |                                          |                   | bit           |  |  |  |  |

| U-0             | U-0                                                                                                                                                             | R/W-0              | R/W-0              | R/W-0                              | R/W-0                                    | R/W-0             | R/W-0         |  |  |  |  |

| _               | _                                                                                                                                                               | BCH <sup>(1)</sup> | BCL <sup>(1)</sup> | BPHH                               | BPHL                                     | BPLH              | BPLL          |  |  |  |  |

| bit 7           |                                                                                                                                                                 | 20                 |                    |                                    |                                          |                   | bit           |  |  |  |  |

| Legend:         |                                                                                                                                                                 |                    |                    |                                    |                                          |                   |               |  |  |  |  |

| R = Readable    | bit                                                                                                                                                             | W = Writable       | bit                | U = Unimpler                       | nented bit, read                         | l as '0'          |               |  |  |  |  |

| -n = Value at F | POR                                                                                                                                                             | '1' = Bit is set   |                    | '0' = Bit is cle                   | ared                                     | x = Bit is unkr   | nown          |  |  |  |  |

| bit 15          |                                                                                                                                                                 | H Rising Edge      | Triggor Enabl      | o hit                              |                                          |                   |               |  |  |  |  |

| JIL 15          |                                                                                                                                                                 | • •                |                    |                                    | Blanking count                           | ter               |               |  |  |  |  |

|                 | <ul> <li>1 = Rising edge of PWMxH will trigger the Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores the rising edge of PWMxH</li> </ul> |                    |                    |                                    |                                          |                   |               |  |  |  |  |

| bit 14          | PHF: PWMxH                                                                                                                                                      | H Falling Edge     | Trigger Enab       | le bit                             |                                          |                   |               |  |  |  |  |

|                 |                                                                                                                                                                 |                    |                    |                                    | e Blanking coun                          | ter               |               |  |  |  |  |

|                 | 0 = Leading-Edge Blanking ignores the falling edge of PWMxH                                                                                                     |                    |                    |                                    |                                          |                   |               |  |  |  |  |

| bit 13          |                                                                                                                                                                 | Rising Edge        |                    |                                    | DI L'A                                   |                   |               |  |  |  |  |

|                 |                                                                                                                                                                 |                    |                    | sing edge of PV                    | Blanking count                           | er                |               |  |  |  |  |

| bit 12          |                                                                                                                                                                 | _uge blanking      |                    |                                    | VIVIAE                                   |                   |               |  |  |  |  |

|                 |                                                                                                                                                                 |                    |                    |                                    | Blanking count                           | ter               |               |  |  |  |  |

|                 | Ų                                                                                                                                                               | 0                  | 00                 | alling edge of P                   | Ų                                        |                   |               |  |  |  |  |

| bit 11          |                                                                                                                                                                 | •                  | • •                | anking Enable I                    |                                          |                   |               |  |  |  |  |

|                 |                                                                                                                                                                 |                    |                    | he selected Fail to the selected   |                                          |                   |               |  |  |  |  |

| bit 10          | CLLEBEN: C                                                                                                                                                      | Current-Limit Le   | ading-Edge E       | Blanking Enable                    | e bit                                    |                   |               |  |  |  |  |

|                 |                                                                                                                                                                 |                    |                    | he selected cur<br>to the selected | rrent-limit input<br>I current-limit inj | put               |               |  |  |  |  |

| bit 9-6         | Unimplemen                                                                                                                                                      | ted: Read as '     | 0'                 |                                    |                                          |                   |               |  |  |  |  |

| bit 5           | BCH: Blankin                                                                                                                                                    | ng in Selected I   | Blanking Sign      | al High Enable                     | bit <sup>(1)</sup>                       |                   |               |  |  |  |  |

|                 |                                                                                                                                                                 | nking (of currer   |                    |                                    | nals) when seled                         | cted blanking s   | ignal is high |  |  |  |  |

| bit 4           | BCL: Blankin                                                                                                                                                    | g in Selected E    | Blanking Signa     | al Low Enable b                    | <sub>Dit</sub> (1)                       |                   |               |  |  |  |  |

|                 |                                                                                                                                                                 | nking (of currer   |                    |                                    | nals) when seled                         | cted blanking s   | ignal is low  |  |  |  |  |

| bit 3           | BPHH: Blanking in PWMxH High Enable bit                                                                                                                         |                    |                    |                                    |                                          |                   |               |  |  |  |  |

|                 |                                                                                                                                                                 | nking (of currer   |                    |                                    | nals) when PWN                           | /IxH output is h  | igh           |  |  |  |  |

| bit 2           | BPHL: Blanking in PWMxH Low Enable bit                                                                                                                          |                    |                    |                                    |                                          |                   |               |  |  |  |  |

|                 |                                                                                                                                                                 | nking (of currer   |                    |                                    | nals) when PWN                           | /IxH output is lo | W             |  |  |  |  |

| bit 1           | BPLH: Blanki                                                                                                                                                    | ing in PWMxL       | High Enable I      | oit                                |                                          |                   |               |  |  |  |  |

|                 |                                                                                                                                                                 | nking (of currer   |                    |                                    | als) when PWN                            | /lxL output is hi | gh            |  |  |  |  |

|                 | 0 = No blanki                                                                                                                                                   | ing when PWM       | xL output is h     | igh                                |                                          |                   |               |  |  |  |  |

| bit 0           |                                                                                                                                                                 |                    | -                  | -                                  |                                          |                   |               |  |  |  |  |

# REGISTER 16-22: LEBCONX: LEADING-EDGE BLANKING CONTROL REGISTER x

Note 1: The blanking signal is selected via the BLANKSELx bits in the AUXCONx register.

# 20.2 UART Control Registers

# REGISTER 20-1: UxMODE: UARTx MODE REGISTER

| R/W-0                 | U-0                                | R/W-0                                  | R/W-0               | R/W-0              | U-0             | R/W-0            | R/W-0           |  |

|-----------------------|------------------------------------|----------------------------------------|---------------------|--------------------|-----------------|------------------|-----------------|--|

| UARTEN <sup>(1)</sup> | 0-0                                | USIDL                                  | IREN <sup>(2)</sup> | RTSMD              | 0-0             | UEN1             | UEN0            |  |

| bit 15                | _                                  | USIDE                                  | INEN <sup>®</sup>   | KT SIVID           | _               | UENT             | bit             |  |

|                       |                                    |                                        |                     |                    |                 |                  | Dit             |  |

| R/W-0, HC             | R/W-0                              | R/W-0, HC                              | R/W-0               | R/W-0              | R/W-0           | R/W-0            | R/W-0           |  |

| WAKE                  | LPBACK                             | ABAUD                                  | URXINV              | BRGH               | PDSEL1          | PDSEL0           | STSEL           |  |

| bit 7                 |                                    |                                        |                     |                    |                 |                  | bit             |  |

|                       |                                    |                                        |                     |                    |                 |                  |                 |  |

| Legend:               |                                    | HC = Hardwar                           | e Clearable bit     | t                  |                 |                  |                 |  |

| R = Readable          | bit                                | W = Writable b                         | bit                 | U = Unimple        | mented bit, rea | ad as '0'        |                 |  |

| -n = Value at F       | POR                                | '1' = Bit is set                       |                     | '0' = Bit is cle   | eared           | x = Bit is unki  | nown            |  |

|                       |                                    |                                        | (4)                 |                    |                 |                  |                 |  |

| bit 15                |                                    | ARTx Enable bit                        |                     |                    |                 |                  | <u> </u>        |  |

|                       |                                    | s enabled; all U,<br>s disabled; all L |                     |                    |                 |                  |                 |  |

|                       | is minima                          |                                        |                     | controlled by      | I OIT lateries  |                  |                 |  |

| bit 14                | Unimplemen                         | ted: Read as '0                        | )'                  |                    |                 |                  |                 |  |

| bit 13                | USIDL: UARTx Stop in Idle Mode bit |                                        |                     |                    |                 |                  |                 |  |

|                       |                                    | nues module op                         |                     | levice enters Id   | le mode         |                  |                 |  |

|                       |                                    | es module opera                        |                     |                    |                 |                  |                 |  |

| bit 12                | IREN: IrDA®                        | Encoder and De                         | ecoder Enable       | bit <sup>(2)</sup> |                 |                  |                 |  |

|                       | 1 = IrDA enc                       | oder and decod                         | ler are enabled     | 1                  |                 |                  |                 |  |

|                       | 0 = IrDA enc                       | oder and decod                         | ler are disabled    | b                  |                 |                  |                 |  |

| bit 11                | RTSMD: Mod                         | le Selection for                       | UxRTS Pin bit       |                    |                 |                  |                 |  |

|                       |                                    | in is in Simplex                       |                     |                    |                 |                  |                 |  |

| L:1 10                | •                                  | oin is in Flow Co                      |                     |                    |                 |                  |                 |  |

| bit 10                | -                                  | ted: Read as '0                        |                     |                    |                 |                  |                 |  |

| bit 9-8               |                                    | JARTx Pin Enab                         |                     |                    |                 |                  |                 |  |

|                       |                                    | JxRX and BCLK<br>JxRX, UxCTS a         |                     |                    |                 | controlled by PC | JRT latches     |  |

|                       |                                    | JxRX and UxRT                          |                     |                    |                 | controlled by PO | ORT latches     |  |

|                       |                                    | nd UxRX pins a                         |                     |                    |                 |                  |                 |  |

|                       | PORT la                            | atches                                 |                     |                    |                 |                  |                 |  |

| bit 7                 | WAKE: Wake                         | e-up on Start bit                      | Detect During       | Sleep Mode E       | nable bit       |                  |                 |  |

|                       |                                    | ontinues to sam                        |                     |                    | generated on    | the falling edge | ; bit is cleare |  |

|                       |                                    | are on the follow<br>-up is enabled    | ving rising eag     | e                  |                 |                  |                 |  |

| bit 6                 |                                    | ARTx Loopback                          | Mode Select h       | it.                |                 |                  |                 |  |

|                       | 1 = Enables                        | nı,                                    |                     |                    |                 |                  |                 |  |

|                       |                                    | k mode is disab                        |                     |                    |                 |                  |                 |  |

| Note 1: Ret           | fer to the "de DU                  | C33/PIC24 Fam                          | ily Reference M     | lanual" "Univa     | real Asynchry   | nous Possiva     | r Transmitte    |  |

|                       |                                    | 0582) for inform                       |                     |                    |                 |                  |                 |  |

| •                     |                                    | y available for th                     |                     | •                  |                 |                  |                 |  |

|                       |                                    | y available on 4                       |                     |                    | - /-            |                  |                 |  |

|                       |                                    | y available on f                       |                     |                    |                 |                  |                 |  |

4: This feature is only available on 64-pin devices.

# REGISTER 25-1: PTGCST: PTG CONTROL/STATUS REGISTER (CONTINUED)

- bit 1-0 PTGITM<1:0>: PTG Input Trigger Command Operating Mode bits<sup>(1)</sup>

- 11 = Single level detect with step delay is not executed on exit of command (regardless of PTGCTRL command)

- 10 = Single level detect with step delay is executed on exit of command

- 01 = Continuous edge detect with step delay is not executed on exit of command (regardless of PTGCTRL command)

- 00 = Continuous edge detect with step delay is executed on exit of command

- Note 1: These bits apply to the PTGWHI and PTGWLO commands only.

- **2:** This bit is only used with the PTGCTRL Step command software trigger option.

# 27.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Real-Time Clock and Calendar (RTCC)" (DS70584), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter discusses the Real-Time Clock and Calendar (RTCC) module and its operation.

Some of the key features of this module are:

- · Time: Hours, Minutes and Seconds

- 24-Hour Format (military time)

- · Calendar: Weekday, Date, Month and Year

- Alarm Configurable

- Year Range: 2000 to 2099

- Leap Year Correction

- BCD Format for Compact Firmware

- · Optimized for Low-Power Operation

- User Calibration with Auto-Adjust

- Calibration Range: ±2.64 Seconds Error per Month

- Requirements: External 32.768 kHz Clock Crystal

- Alarm Pulse or Seconds Clock Output on RTCC Pin

The RTCC module is intended for applications where accurate time must be maintained for extended periods with minimum to no intervention from the CPU. The RTCC module is optimized for low-power usage to provide extended battery lifetime while keeping track of time.

The RTCC module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099.

The hours are available in 24-hour (military time) format. The clock provides a granularity of one second with half-second visibility to the user.

# **REGISTER 27-8:** ALRMVAL (WHEN ALRMPTR<1:0> = 10): ALARM MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| —      | —   | _   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

- bit 12 MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit bit Contains a value of 0 or 1.

- bit 11-8 **MTHONE<3:0>:** Binary Coded Decimal Value of Month's Ones Digit bits Contains a value from 0 to 9.

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 **DAYTEN<1:0>:** Binary Coded Decimal Value of Day's Tens Digit bits Contains a value from 0 to 3.

- bit 3-0 **DAYONE<3:0>:** Binary Coded Decimal Value of Day's Ones Digit bits Contains a value from 0 to 9.

- **Note 1:** A write to this register is only allowed when RTCWREN = 1.

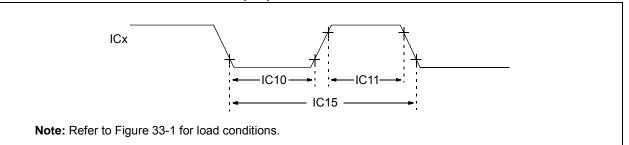

# FIGURE 33-7: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

# TABLE 33-25: INPUT CAPTURE x (ICx) TIMING REQUIREMENTS

| AC CHA        | RACTERI | STICS                          | (unless otherwis                                | Standard Operating Conditions: 3.0V to 3.6V<br>unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |       |                                  |                                  |  |  |

|---------------|---------|--------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------|----------------------------------|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup> | Min.                                            | Max.                                                                                                                                                                                                           | Units | Conditions                       |                                  |  |  |

| IC10          | TccL    | ICx Input Low Time             | Greater of:<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25 | —                                                                                                                                                                                                              | ns    | Must also meet<br>Parameter IC15 |                                  |  |  |

| IC11          | ТссН    | ICx Input High Time            | Greater of:<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25 | —                                                                                                                                                                                                              | ns    | Must also meet<br>Parameter IC15 | N = Prescale value<br>(1, 4, 16) |  |  |

| IC15          | TccP    | ICx Input Period               | Greater of:<br>25 + 50 or<br>(1 Tcy/N) + 50     |                                                                                                                                                                                                                | ns    |                                  |                                  |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

# dsPIC33EPXXXGM3XX/6XX/7XX

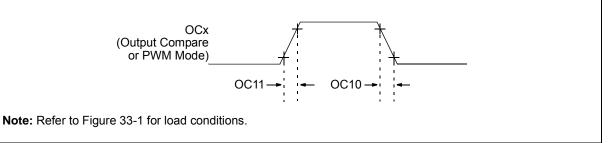

# FIGURE 33-8: OUTPUT COMPARE x (OCx) TIMING CHARACTERISTICS

## TABLE 33-26: OUTPUT COMPARE x (OCx) TIMING REQUIREMENTS

| АС СНА       | RACTER | ISTICS                        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                    |  |  |

|--------------|--------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------|--|--|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                    | Тур. | Max. | Units | Conditions         |  |  |

| OC10         | TccF   | OCx Output Fall Time          |                                                                                                                                                                                                                                                                                         |      |      | ns    | See Parameter DO32 |  |  |

| OC11         | TccR   | OCx Output Rise Time          | —                                                                                                                                                                                                                                                                                       | —    | —    | ns    | See Parameter DO31 |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

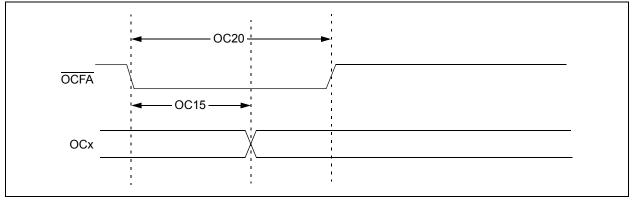

## FIGURE 33-9: OCx/PWMx MODULE TIMING CHARACTERISTICS

## TABLE 33-27: OCx/PWMx MODE TIMING REQUIREMENTS

| AC CHAF      | RACTERIS | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |          |      |          |       |            |  |

|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|----------|-------|------------|--|