Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, Motor Control PWM, POR, PWM, WDT               |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 48K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 30x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gm306-e-mr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name     | Pin<br>Type | Buffer<br>Type | PPS | Description                                               |  |  |  |

|--------------|-------------|----------------|-----|-----------------------------------------------------------|--|--|--|

| U1CTS        | ı           | ST             | Yes | UART1 Clear-to-Send.                                      |  |  |  |

| U1RTS        | 0           | _              | Yes | UART1 Ready-to-Send.                                      |  |  |  |

| U1RX         | ı           | ST             | Yes | UART1 receive.                                            |  |  |  |

| U1TX         | 0           | _              | Yes | UART1 transmit.                                           |  |  |  |

| U2CTS        | ı           | ST             | Yes | UART2 Clear-to-Send.                                      |  |  |  |

| U2RTS        | 0           | _              | Yes | UART2 Ready-to-Send.                                      |  |  |  |

| U2RX         | 1           | ST             | Yes | UART2 receive.                                            |  |  |  |

| U2TX         | 0           | _              | Yes | UART2 transmit.                                           |  |  |  |

| U3CTS        | - 1         | ST             | Yes | UART3 Clear-to-Send.                                      |  |  |  |

| U3RTS        | 0           | _              | Yes | UART3 Ready-to-Send.                                      |  |  |  |

| U3RX         | I           | ST             | Yes | UART3 receive.                                            |  |  |  |

| U3TX         | 0           | 1              | Yes | UART3 transmit.                                           |  |  |  |

| U4CTS        | 1           | ST             | Yes | UART4 Clear-to-Send.                                      |  |  |  |

| U4RTS        | 0           | _              | Yes | UART4 Ready-to-Send.                                      |  |  |  |

| U4RX         | I           | ST             | Yes | UART4 receive.                                            |  |  |  |

| U4TX         | 0           | _              | Yes | UART4 transmit.                                           |  |  |  |

| SCK1         | I/O         | ST             | No  | Synchronous serial clock input/output for SPI1.           |  |  |  |

| SDI1         | I           | ST             | No  | SPI1 data in.                                             |  |  |  |

| <u>SDO</u> 1 | 0           | _              | No  | SPI1 data out.                                            |  |  |  |

| SS1          | I/O         | ST             | No  | SPI1 slave synchronization or frame pulse I/O.            |  |  |  |

| SCK2         | I/O         | ST             | Yes | Synchronous serial clock input/output for SPI2.           |  |  |  |

| SDI2         | I           | ST             | Yes | SPI2 data in.                                             |  |  |  |

| SDO2         | 0           | _              | Yes | SPI2 data out.                                            |  |  |  |

| SS2          | I/O         | ST             | Yes | SPI2 slave synchronization or frame pulse I/O.            |  |  |  |

| SCK3         | I/O         | ST             | Yes | Synchronous serial clock input/output for SPI3.           |  |  |  |

| SDI3         | I           | ST             | Yes | SPI3 data in.                                             |  |  |  |

| SDO3         | 0           | _              | Yes | SPI3 data out.                                            |  |  |  |

| SS3          | I/O         | ST             | Yes | SPI3 slave synchronization or frame pulse I/O.            |  |  |  |

| SCL1         | I/O         | ST             | No  | Synchronous serial clock input/output for I2C1.           |  |  |  |

| SDA1         | I/O         | ST             | No  | Synchronous serial data input/output for I2C1.            |  |  |  |

| ASCL1        | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C1. |  |  |  |

| ASDA1        | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C1.  |  |  |  |

| SCL2         | I/O         | ST             | No  | Synchronous serial clock input/output for I2C2.           |  |  |  |

| SDA2         | I/O         | ST             | No  | Synchronous serial data input/output for I2C2.            |  |  |  |

| ASCL2        | 1/0         | ST             | No  | Alternate synchronous serial clock input/output for I2C2. |  |  |  |

| ASDA2        | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C2.  |  |  |  |

| TMS          | I           | ST             | No  | JTAG Test mode select pin.                                |  |  |  |

| TCK          | l           | ST             | No  | JTAG test clock input pin.                                |  |  |  |

| TDI          |             | ST             | No  | JTAG test data input pin.                                 |  |  |  |

| TDO          | 0           |                | No  | JTAG test data output pin.                                |  |  |  |

Legend:CMOS = CMOS compatible input or output<br/>ST = Schmitt Trigger input with CMOS levels<br/>PPS = Peripheral Pin SelectAnalog = Analog input<br/>O = Output<br/>TTL = TTL input bufferP = Power<br/>I = Input

**Note 1:** This pin is not available on all devices. For more information, see the "**Pin Diagrams**" section for pin availability.

2: AVDD must be connected at all times.

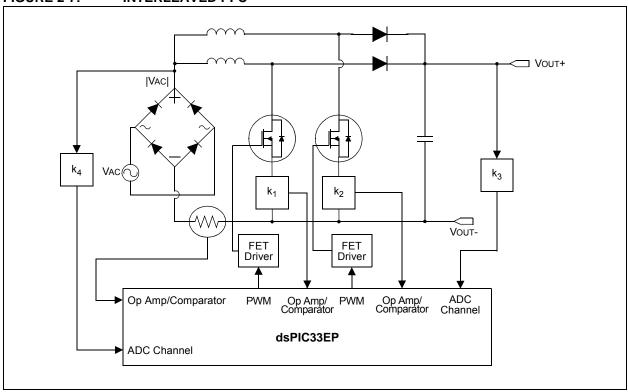

FIGURE 2-7: INTERLEAVED PFC

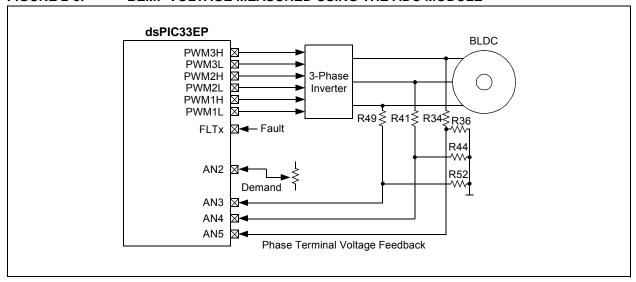

FIGURE 2-8: BEMF VOLTAGE MEASURED USING THE ADC MODULE

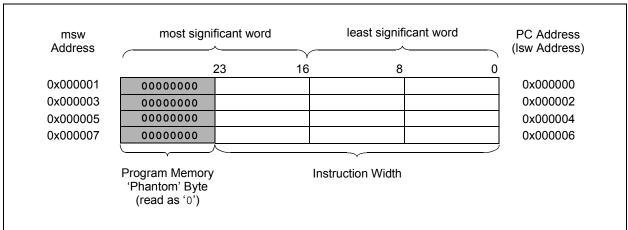

## 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-4).

Program memory addresses are always word-aligned on the lower word and addresses are incremented or decremented by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGM3XX/6XX/7XX devices reserve the addresses between 0x000000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000 of Flash memory, with the actual address for the start of code at address, 0x0000002 of Flash memory.

A more detailed discussion of the interrupt vector tables is provided in **Section 7.1** "Interrupt Vector **Table**".

FIGURE 4-4: PROGRAM MEMORY ORGANIZATION

TABLE 4-41: OP AMP/COMPARATOR REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|---------------|

| CMSTAT      | 0A80  | PSIDL  | _      | _      | C5EVT  | C4EVT    | C3EVT    | C2EVT    | C1EVT    | _        | -        | _        | C5OUT    | C4OUT    | C3OUT    | C2OUT    | C1OUT    | 0000          |

| CVR1CON     | 0A82  | _      | _      | _      | _      | CVRR1    | VREFSEL  | _        | _        | CVREN    | CVROE    | CVRR0    | CVRSS    | CVR3     | CVR2     | CVR1     | CVR0     | 0000          |

| CM1CON      | 0A84  | CON    | COE    | CPOL   | _      | -        | OPMODE   | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM1MSKSRC   | 0A86  | _      | _      | _      | _      | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM1MSKCON   | 0A88  | HLMS   | -      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM1FLTR     | 0A8A  | _      | -      | _      |        | ı        | _        | ı        | _        | _        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM2CON      | 0A8C  | CON    | COE    | CPOL   |        | ı        | OPMODE   | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | 1        | _        | CCH1     | CCH0     | 0000          |

| CM2MSKSRC   | 0A8E  | _      | -      | _      |        | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM2MSKCON   | 0A90  | HLMS   | -      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM2FLTR     | 0A92  | _      | -      |        |        |          | _        | I        | _        | _        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM3CON      | 0A94  | CON    | COE    | CPOL   | _      | -        | OPMODE   | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM3MSKSRC   | 0A96  | _      | _      | _      | _      | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM3MSKCON   | 0A98  | HLMS   | _      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM3FLTR     | 0A9A  | _      | _      | _      | _      | -        | _        | 1        | _        | _        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM4CON      | 0A9C  | CON    | COE    | CPOL   | _      | -        | _        | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM4MSKSRC   | 0A9E  | _      | _      | _      | _      | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM4MSKCON   | 0AA0  | HLMS   | _      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM4FLTR     | 0AA2  | _      | -      | _      |        | ı        | _        | I        | _        | _        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM5CON      | 0AA4  | CON    | COE    | CPOL   |        | ı        | OPMODE   | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | 1        | _        | CCH1     | CCH0     | 0000          |

| CM5MSKSRC   | 0AA6  | _      | -      | _      |        | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM5MSKCON   | 0AA8  | HLMS   | _      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM5FLTR     | 0AAA  | _      | _      |        | _      | ı        | -        | ı        | _        | _        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CVR2CON     | 0AB4  | _      | _      | _      | _      | CVRR1    | VREFSEL  | _        | _        | CVREN    | CVROE    | CVRR0    | CVRSS    | CVR3     | CVR2     | CVR1     | CVR0     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 11-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION) (CONTINUED)

| Function Name | Register                                  | Configuration Bits                                                                                                                                                                          |

|---------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYNCI1        | RPINR37                                   | SYNCI1R<6:0>                                                                                                                                                                                |

| DTCMP1        | RPINR38                                   | DTCMP1R<6:0>                                                                                                                                                                                |

| DTCMP2        | RPINR39                                   | DTCMP2R<6:0>                                                                                                                                                                                |

| DTCMP3        | RPINR39                                   | DTCMP3R<6:0>                                                                                                                                                                                |

| DTCMP4        | RPINR40                                   | DTCMP4R<6:0>                                                                                                                                                                                |

| DTCMP5        | RPINR40                                   | DTCMP5R<6:0>                                                                                                                                                                                |

| DTCMP6        | RPINR41                                   | DTCMP6R<6:0>                                                                                                                                                                                |

|               | SYNCI1 DTCMP1 DTCMP2 DTCMP3 DTCMP4 DTCMP5 | SYNCI1         RPINR37           DTCMP1         RPINR38           DTCMP2         RPINR39           DTCMP3         RPINR39           DTCMP4         RPINR40           DTCMP5         RPINR40 |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

<sup>2:</sup> This input is available on dsPIC33EPXXXGM6XX/7XX devices only.

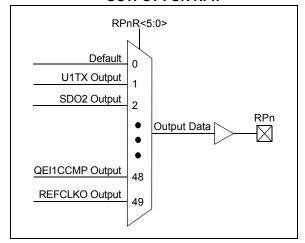

### 11.4.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-30 through Register 11-42). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

### 11.4.5.1 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-to-one and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

### REGISTER 11-20: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26<sup>(1)</sup>

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      |       |       |       | C2RXR<6:0> | >     |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------|-------|-------|-------|

| _     |       |       |       | C1RXR<6:0> | >     |       |       |

| bit 7 |       |       |       |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 C2RXR<6:0>: Assign CAN2 RX Input (C2RX) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111100 = Input tied to RPI124

•

.

0000001 = Input tied to CMP1

0000000 = Input tied to Vss

bit 7 **Unimplemented:** Read as '0'

bit 6-0 C1RXR<6:0>: Assign CAN1 RX Input (C1RX) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111100 = Input tied to RPI124

•

•

•

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

**Note 1:** This register is not available on dsPIC33EPXXXGM3XX devices.

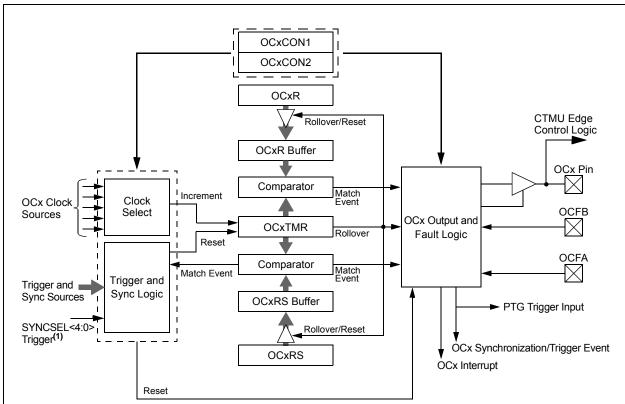

### 15.0 OUTPUT COMPARE

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24EFamily Reference Manual", "Output Compare" (DS70005157), which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The output compare module can select one of eight available clock sources for its time base. The module compares the value of the timer with the value of one or two Compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Note: See the "dsPIC33/PIC24 Family Reference Manual", "Output Compare" (DS70005157) for OCxR and OCxRS register restrictions.

### FIGURE 15-1: OUTPUT COMPARE x MODULE BLOCK DIAGRAM

**Note 1:** The Trigger/Sync source is enabled by default and is set to Timer2 as a source. This timer must be enabled for proper OCx module operation or the Trigger/Sync source must be changed to another source option.

### REGISTER 16-25: PWMCAPx: PWMx PRIMARY TIME BASE CAPTURE REGISTER

| R-0                            | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |  |

|--------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| PWMCAPx<15:8> <sup>(1,2)</sup> |     |     |     |     |     |     |     |  |

| bit 15 bit                     |     |     |     |     |     |     |     |  |

| R-0               | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |  |  |

|-------------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| PWMCAPx<7:0>(1,2) |     |     |     |     |     |     |     |  |  |

| bit 7             |     |     |     |     |     |     |     |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PWMCAPx<15:0>:** PWMx Captured Time Base Value bits<sup>(1,2)</sup>

The value in this register represents the captured PWMx time base value when a leading edge is detected on the current-limit input.

- **Note 1:** The capture feature is only available on a primary output (PWMxH).

- 2: This feature is active only after LEB processing on the current-limit input signal is complete.

### 20.1 UART Helpful Tips

- In multi-node direct connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pullup or pull-down resistor on the RX pin, depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

2. The first character received on wake-up from Sleep mode, caused by activity on the UxRX pin of the UART module, will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid. This is to be expected.

# 25.0 PERIPHERAL TRIGGER GENERATOR (PTG) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Peripheral Trigger Generator (PTG)" (DS70669), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

### 25.1 Module Introduction

The Peripheral Trigger Generator (PTG) provides a means to schedule complex, high-speed peripheral operations that would be difficult to achieve using software. The PTG module uses 8-bit commands, called "steps", that the user writes to the PTG Queue register (PTGQUE0-PTQUE15), which performs operations, such as wait for input signal, generate output trigger and wait for timer.

The PTG module has the following major features:

- · Multiple Clock Sources

- · Two 16-Bit General Purpose Timers

- · Two 16-Bit General Limit Counters

- · Configurable for Rising or Falling Edge Triggering

- · Generates Processor Interrupts to Include:

- Four configurable processor interrupts

- Interrupt on a step event in Single-Step mode

- Interrupt on a PTG Watchdog Timer time-out

- Able to Receive Trigger Signals from these Peripherals:

- ADC

- PWM

- Output Compare

- Input Capture

- Op Amp/Comparator

- INT2

- Able to Trigger or Synchronize to these Peripherals:

- Watchdog Timer

- Output Compare

- Input Capture

- ADC

- PWM

- Op Amp/Comparator

### REGISTER 26-3: CM4CON: OP AMP/COMPARATOR 4 CONTROL REGISTER

| R/W-0  | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | R/W-0               | R/W-0 |

|--------|-------|-------|-----|-----|-----|---------------------|-------|

| CON    | COE   | CPOL  | _   | _   | _   | CEVT <sup>(2)</sup> | COUT  |

| bit 15 |       |       |     |     |     |                     | bit 8 |

| R/W-0                 | R/W-0                 | U-0 | R/W-0               | U-0 | U-0 | R/W-0               | R/W-0               |

|-----------------------|-----------------------|-----|---------------------|-----|-----|---------------------|---------------------|

| EVPOL1 <sup>(2)</sup> | EVPOL0 <sup>(2)</sup> | _   | CREF <sup>(1)</sup> | _   | _   | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |

| bit 7                 |                       |     |                     |     |     |                     | bit 0               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 CON: Op Amp/Comparator Enable bit

1 = Comparator is enabled0 = Comparator is disabled

bit 14 **COE:** Comparator Output Enable bit

1 = Comparator output is present on the CxOUT pin

0 = Comparator output is internal only

bit 13 **CPOL:** Comparator Output Polarity Select bit

1 = Comparator output is inverted

0 = Comparator output is not inverted

bit 12-10 **Unimplemented:** Read as '0' bit 9 **CEVT:** Comparator Event bit<sup>(2)</sup>

1 = Comparator event, according to the EVPOL<1:0> settings, occurred; disables future triggers and interrupts until the bit is cleared

0 = Comparator event did not occur

bit 8 **COUT:** Comparator Output bit

When CPOL = 0 (non-inverted polarity):

1 = VIN+ > VIN-

0 = VIN+ < VIN-

When CPOL = 1 (inverted polarity):

1 = VIN+ < VIN-

0 = VIN+ > VIN-

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- 2: After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator Event bit, CEVT (CMxCON<9>), and the Comparator Combined Interrupt Flag, CMPIF (IFS1<2>), must be cleared before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

### 32.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM™ Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- · Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- · Third-party development tools

# 32.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows®, Linux and Mac OS® X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

### Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- · Multiple projects

- · Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

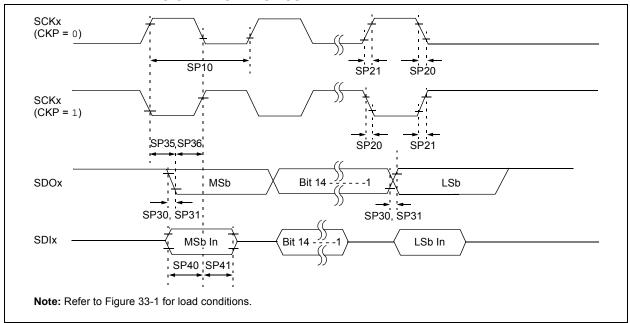

FIGURE 33-18: SPI2 AND SPI3 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

TABLE 33-35: SPI2 AND SPI3 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING REQUIREMENTS

| AC CHA | RACTERIST             | ICS                                        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |   |    |       |                             |  |  |  |

|--------|-----------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|-------|-----------------------------|--|--|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>              | Min. Typ. <sup>(2)</sup> Max.                                                                                                                                                                                                                    |   |    | Units | Conditions                  |  |  |  |

| SP10   | FscP                  | Maximum SCKx Frequency                     | ı                                                                                                                                                                                                                                                |   | 9  | MHz   | -40°C to +125°C<br>(Note 3) |  |  |  |

| SP20   | TscF                  | SCKx Output Fall Time                      | 1                                                                                                                                                                                                                                                |   | _  | ns    | See Parameter DO32 (Note 4) |  |  |  |

| SP21   | TscR                  | SCKx Output Rise Time                      | -                                                                                                                                                                                                                                                |   | _  | ns    | See Parameter DO31 (Note 4) |  |  |  |

| SP30   | TdoF                  | SDOx Data Output Fall Time                 |                                                                                                                                                                                                                                                  | _ | _  | ns    | See Parameter DO32 (Note 4) |  |  |  |

| SP31   | TdoR                  | SDOx Data Output Rise Time                 | _                                                                                                                                                                                                                                                | _ | _  | ns    | See Parameter DO31 (Note 4) |  |  |  |

| SP35   | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge     | _                                                                                                                                                                                                                                                | 6 | 20 | ns    |                             |  |  |  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to First SCKx Edge  | 30                                                                                                                                                                                                                                               |   | _  | ns    |                             |  |  |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge | 30                                                                                                                                                                                                                                               | _ | _  | ns    |                             |  |  |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge  | 30                                                                                                                                                                                                                                               |   | _  | ns    |                             |  |  |  |

- **Note 1:** These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

TABLE 33-44: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                     |      |       |                                |

|--------------------|-----------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>              | Min.                                                                                                                                                                                                                                             | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |

| SP70               | FscP                  | Maximum SCK1 Input Frequency               | _                                                                                                                                                                                                                                                | _                   | 25   | MHz   | (Note 3)                       |

| SP72               | TscF                  | SCK1 Input Fall Time                       | _                                                                                                                                                                                                                                                | _                   | I    | ns    | See Parameter<br>DO32 (Note 4) |

| SP73               | TscR                  | SCK1 Input Rise Time                       | _                                                                                                                                                                                                                                                | _                   | ı    | ns    | See Parameter<br>DO31 (Note 4) |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                 | _                                                                                                                                                                                                                                                | _                   | I    | ns    | See Parameter<br>DO32 (Note 4) |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                 | _                                                                                                                                                                                                                                                |                     | _    | ns    | See Parameter<br>DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge  | _                                                                                                                                                                                                                                                | 6                   | 20   | ns    |                                |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to First SCK1 Edge  | 20                                                                                                                                                                                                                                               |                     | _    | ns    |                                |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCK1 Edge | 20                                                                                                                                                                                                                                               | _                   | _    | ns    |                                |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge  | 15                                                                                                                                                                                                                                               | _                   | _    | ns    |                                |

| SP50               | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓ Input            | 120                                                                                                                                                                                                                                              |                     | _    | ns    |                                |

| SP51               | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance     | 10                                                                                                                                                                                                                                               | _                   | 50   | ns    | (Note 4)                       |

| SP52               | TscH2ssH<br>TscL2ssH  | SS1 ↑ after SCK1 Edge                      | 1.5 Tcy + 40                                                                                                                                                                                                                                     | _                   | _    | ns    | (Note 4)                       |

| SP60               | TssL2doV              | SDO1 Data Output Valid after SS1 Edge      | _                                                                                                                                                                                                                                                | _                   | 50   | ns    |                                |

- Note 1: These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.

TABLE 33-52: OP AMP/COMPARATOR SPECIFICATIONS

| DC CHARACTERISTICS            |                 |                                           | Standard Operating Conditions (see Note 3): 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |                     |              |        |                                                 |  |  |

|-------------------------------|-----------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|--------|-------------------------------------------------|--|--|

| Param<br>No.                  | Symbol          | Characteristic                            | Min.                                                                                                                                                                                                                                                          | Typ. <sup>(1)</sup> | Max.         | Units  | Conditions                                      |  |  |

| Comparator AC Characteristics |                 |                                           |                                                                                                                                                                                                                                                               |                     |              |        |                                                 |  |  |

| CM10                          | TRESP           | Response Time                             |                                                                                                                                                                                                                                                               | 19                  | _            | ns     | V+ input step of 100 mV, V- input held at VDD/2 |  |  |

| CM11                          | TMC2OV          | Comparator Mode<br>Change to Output Valid |                                                                                                                                                                                                                                                               | _                   | 10           | μs     |                                                 |  |  |

| Compa                         | rator DC Ch     | aracteristics                             |                                                                                                                                                                                                                                                               |                     |              |        |                                                 |  |  |

| CM30                          | Voffset         | Comparator Offset Voltage                 | _                                                                                                                                                                                                                                                             | ±20                 | ±75          | mV     |                                                 |  |  |

| CM31                          | VHYST           | Input Hysteresis Voltage                  | _                                                                                                                                                                                                                                                             | 30                  | _            | mV     |                                                 |  |  |

| CM32                          | TRISE/<br>TFALL | Comparator Output<br>Rise/Fall Time       | _                                                                                                                                                                                                                                                             | 20                  | _            | ns     | 1 pF load capacitance on input                  |  |  |

| CM33                          | VGAIN           | Open-Loop Voltage Gain                    | _                                                                                                                                                                                                                                                             | 90                  | _            | db     |                                                 |  |  |

| CM34                          | VICM            | Input Common-Mode<br>Voltage              | AVss                                                                                                                                                                                                                                                          | _                   | AVDD         | V      |                                                 |  |  |

| Op Am                         | p AC Chara      | cteristics                                |                                                                                                                                                                                                                                                               | •                   |              |        |                                                 |  |  |

| CM20                          | SR              | Slew Rate                                 | _                                                                                                                                                                                                                                                             | 9                   | _            | V/µs   | 10 pF load                                      |  |  |

| CM21a                         | Рм              | Phase Margin                              |                                                                                                                                                                                                                                                               | 68                  | _            | Degree | G = 100V/V; 10 pF load                          |  |  |

| CM22                          | Gм              | Gain Margin                               | _                                                                                                                                                                                                                                                             | 20                  | _            | db     | G = 100V/V; 10 pF load                          |  |  |

| CM23a                         | GBW             | Gain Bandwidth                            | _                                                                                                                                                                                                                                                             | 10                  | _            | MHz    | 10 pF load                                      |  |  |

| Op Am                         | p DC Chara      | cteristics                                |                                                                                                                                                                                                                                                               |                     |              |        |                                                 |  |  |

| CM40                          | VCMR            | Common-Mode Input<br>Voltage Range        | AVss                                                                                                                                                                                                                                                          | _                   | AVDD         | V      |                                                 |  |  |

| CM41                          | CMRR            | Common-Mode<br>Rejection Ratio            | _                                                                                                                                                                                                                                                             | 40                  | _            | db     | VCM = AVDD/2                                    |  |  |

| CM42                          | VOFFSET         | Op Amp Offset Voltage                     | _                                                                                                                                                                                                                                                             | ±20                 | ±70          | mV     |                                                 |  |  |

| CM43                          | VGAIN           | Open-Loop Voltage Gain                    | 1                                                                                                                                                                                                                                                             | 90                  | _            | db     |                                                 |  |  |

| CM44                          | los             | Input Offset Current                      | _                                                                                                                                                                                                                                                             | _                   | _            | 1      | See pad leakage currents in Table 33-10         |  |  |

| CM45                          | lB              | Input Bias Current                        | _                                                                                                                                                                                                                                                             | _                   | _            | _      | See pad leakage<br>currents in Table 33-10      |  |  |

| CM46                          | lout            | Output Current                            | _                                                                                                                                                                                                                                                             | _                   | 420          | μA     | With minimum value of RFEEDBACK (CM48)          |  |  |

| CM48                          | RFEEDBACK       | Feedback Resistance<br>Value              | 8                                                                                                                                                                                                                                                             | _                   | _            | kΩ     | (Note 2)                                        |  |  |

| CM49a                         | Vout            | Output Voltage                            | AVss + 0.075                                                                                                                                                                                                                                                  | _                   | AVDD - 0.075 | V      | ΙΟυτ = 420 μΑ                                   |  |  |

- **Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- 2: Resistances can vary by ±10% between op amps.

- **3:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 33-12 for the minimum and maximum BOR values.

TABLE 33-58: ADCx MODULE SPECIFICATIONS (10-BIT MODE)

| AC CHARACTERISTICS |        |                                               | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) <sup>(1)</sup> Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |          |           |       |                                                                              |  |

|--------------------|--------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|-------|------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                | Min.                                                                                                                                                                                                                                                            | Тур.     | Max.      | Units | Conditions                                                                   |  |

|                    |        | ADC A                                         | ccuracy (                                                                                                                                                                                                                                                       | 10-Bit N | lode)     |       |                                                                              |  |

| AD20b              | Nr     | Resolution                                    | 10 Data Bits                                                                                                                                                                                                                                                    |          |           | bits  |                                                                              |  |

| AD21b              | INL    | Integral Nonlinearity                         | -0.625                                                                                                                                                                                                                                                          | _        | 0.625     | LSb   | -40°C ≤ TA ≤ +85°C (Note 2)                                                  |  |

|                    |        |                                               | -1.5                                                                                                                                                                                                                                                            | _        | 1.5       | LSb   | $+85^{\circ}\text{C} < \text{TA} \le +125^{\circ}\text{C} \text{ (Note 2)}$  |  |

| AD22b              | DNL    | Differential Nonlinearity                     | -0.25                                                                                                                                                                                                                                                           |          | 0.25      | LSb   | $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C} \text{ (Note 2)}$ |  |

|                    |        |                                               | -0.25                                                                                                                                                                                                                                                           |          | 0.25      | LSb   | $+85^{\circ}\text{C} < \text{TA} \le +125^{\circ}\text{C} \text{ (Note 2)}$  |  |

| AD23b              | GERR   | Gain Error                                    | -2.5                                                                                                                                                                                                                                                            | _        | 2.5       | LSb   | -40°C ≤ TA ≤ +85°C (Note 2)                                                  |  |

|                    |        |                                               | -2.5                                                                                                                                                                                                                                                            | _        | 2.5       | LSb   | +85°C < TA ≤ +125°C (Note 2)                                                 |  |

| AD24b              | Eoff   | Offset Error                                  | -1.25                                                                                                                                                                                                                                                           | _        | 1.25      | LSb   | -40°C ≤ TA ≤ +85°C (Note 2)                                                  |  |

|                    |        |                                               | -1.25                                                                                                                                                                                                                                                           | _        | 1.25      | LSb   | +85°C < TA ≤ +125°C ( <b>Note 2</b> )                                        |  |

| AD25b              | _      | Monotonicity                                  | _                                                                                                                                                                                                                                                               | _        | _         | _     | Guaranteed                                                                   |  |

|                    |        | Dynamic P                                     | erforman                                                                                                                                                                                                                                                        | ce (10-E | Bit Mode) |       |                                                                              |  |

| AD30b              | THD    | Total Harmonic Distortion <sup>(3)</sup>      | _                                                                                                                                                                                                                                                               | 64       | _         | dB    |                                                                              |  |

| AD31b              | SINAD  | Signal to Noise and Distortion <sup>(3)</sup> | _                                                                                                                                                                                                                                                               | 57       | _         | dB    |                                                                              |  |

| AD32b              | SFDR   | Spurious Free Dynamic<br>Range <sup>(3)</sup> | _                                                                                                                                                                                                                                                               | 72       | _         | dB    |                                                                              |  |

| AD33b              | FNYQ   | Input Signal Bandwidth <sup>(3)</sup>         | _                                                                                                                                                                                                                                                               | 550      |           | kHz   |                                                                              |  |

| AD34b              | ENOB   | Effective Number of Bits <sup>(3)</sup>       | _                                                                                                                                                                                                                                                               | 9.4      | _         | bits  |                                                                              |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, may have degraded performance. Refer to Parameter BO10 in Table 33-12 for the minimum and maximum BOR values.

- 2: For all accuracy specifications, VINL = AVSS = VREFL = 0V and AVDD = VREFH = 3.6V.

- 3: Parameters are characterized but not tested in manufacturing.

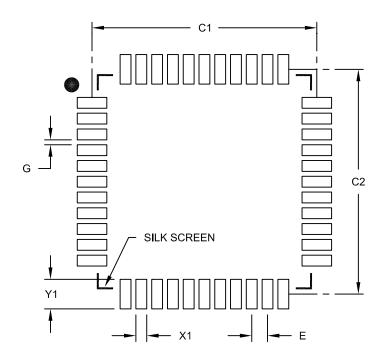

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |      |          |      |

|--------------------------|-------------|------|----------|------|

| Dimension                | MIN         | NOM  | MAX      |      |

| Contact Pitch            | Е           |      | 0.80 BSC |      |

| Contact Pad Spacing      | C1          |      | 11.40    |      |

| Contact Pad Spacing      | C2          |      | 11.40    |      |

| Contact Pad Width (X44)  | X1          |      |          | 0.55 |

| Contact Pad Length (X44) | Y1          |      |          | 1.50 |

| Distance Between Pads    | G           | 0.25 |          |      |

### Notes

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

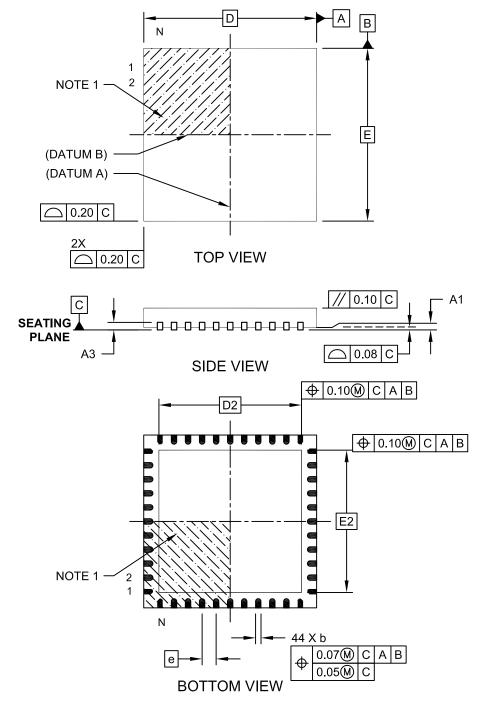

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-103C Sheet 1 of 2

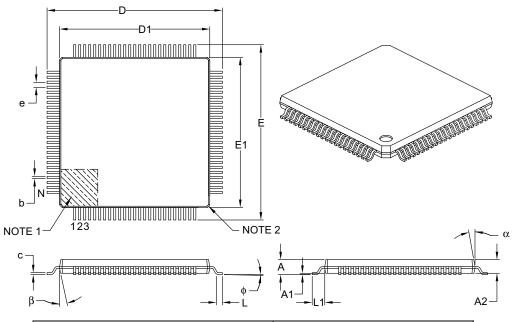

### 100-Lead Plastic Thin Quad Flatpack (PT) - 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |          |      |  |

|--------------------------|------------------|-------------|----------|------|--|

|                          | Dimension Limits | MIN         | NOM      | MAX  |  |

| Number of Leads          | N                |             |          |      |  |

| Lead Pitch               | е                |             | 0.40 BSC |      |  |

| Overall Height           | A                | ı           | _        | 1.20 |  |

| Molded Package Thickness | A2               | 0.95        | 1.00     | 1.05 |  |

| Standoff                 | A1               | 0.05        | _        | 0.15 |  |

| Foot Length              | L                | 0.45        | 0.60     | 0.75 |  |

| Footprint                | L1               | 1.00 REF    |          |      |  |

| Foot Angle               | ф                | 0°          | 3.5°     | 7°   |  |

| Overall Width            | E                | 14.00 BSC   |          |      |  |

| Overall Length           | D                | 14.00 BSC   |          |      |  |

| Molded Package Width     | E1               | 12.00 BSC   |          |      |  |

| Molded Package Length    | D1               | 12.00 BSC   |          |      |  |

| Lead Thickness           | С                | 0.09        | _        | 0.20 |  |

| Lead Width               | b                | 0.13        | 0.18     | 0.23 |  |

| Mold Draft Angle Top     | α                | 11°         | 12°      | 13°  |  |

| Mold Draft Angle Bottom  | β                | 11°         | 12°      | 13°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B