Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000                       |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 48K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gm310-e-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4-10: PWM GENERATOR 2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7    | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|---------|---------|---------|-----------|-----------|-----------|-----------|----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON2     | 0C40  | FLTSTAT | CLSTAT  | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS      | DTC1     | DTC0    | DTCP     | _        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON2      | 0C42  | PENH    | PENL    | POLH    | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL    | OVRDAT1  | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | C000          |

| FCLCON2     | 0C44  | IFLTMOD | CLSRC4  | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD     | FLTSRC4  | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 00F8          |

| PDC2        | 0C46  |         |         |         |         |           |           |           | PDC2      | <15:0>   |         |          |          |          |          | •        | •        | 0000          |

| PHASE2      | 0C48  |         |         |         |         |           |           |           | PHASE     | 2<15:0>  |         |          |          |          |          |          |          | 0000          |

| DTR2        | 0C4A  | _       | _       |         |         |           |           |           |           | DTR2     | <13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR2     | 0C4C  | _       | _       |         |         |           |           |           |           | ALTDTR   | 2<13:0> |          |          |          |          |          |          | 0000          |

| SDC2        | 0C4E  |         | •       |         |         |           |           |           | SDC2      | <15:0>   |         |          |          |          |          |          |          | 0000          |

| SPHASE2     | 0C50  |         |         |         |         |           |           |           | SPHAS     | =2<15:0> |         |          |          |          |          |          |          | 0000          |

| TRIG2       | 0C52  |         |         |         |         |           |           |           | TRGCM     | IP<15:0> |         |          |          |          |          |          |          | 0000          |

| TRGCON2     | 0C54  | TRGDIV3 | TRGDIV2 | TRGDIV1 | TRGDIV0 | _         | _         | _         | _         | _        | _       | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP2     | 0C78  |         |         |         |         |           |           |           | PWMCA     | P2<15:0> |         |          |          |          |          | •        | •        | 0000          |

| LEBCON2     | 0C5A  | PHR     | PHF     | PLR     | PLF     | FLTLEBEN  | CLLEBEN   | —         | —         | —        | _       | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY2     | 0C5C  | _       | _       | _       | _       |           | -         |           | •         |          | LEB<1   | 1:0>     | -        |          |          | •        | •        | 0000          |

| AUXCON2     | 0C5E  | _       | _       | _       | _       | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | BLANKSEL0 | —        | _       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-11: PWM GENERATOR 3 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7    | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|---------|---------|---------|-----------|-----------|-----------|-----------|----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON3     | 0C60  | FLTSTAT | CLSTAT  | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS      | DTC1     | DTC0    | DTCP     |          | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON3      | 0C62  | PENH    | PENL    | POLH    | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL    | OVRDAT1  | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | C000          |

| FCLCON3     | 0C64  | IFLTMOD | CLSRC4  | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD     | FLTSRC4  | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 00F8          |

| PDC3        | 0C66  |         |         |         |         |           |           |           | PDC3      | <15:0>   |         |          |          |          |          |          |          | 0000          |

| PHASE3      | 0C68  |         |         |         |         |           |           |           | PHASE     | 3<15:0>  |         |          |          |          |          |          |          | 0000          |

| DTR3        | 0C6A  | _       | _       |         |         |           |           |           |           | DTR3     | <13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR3     | 0C6C  | _       | -       |         |         |           |           |           |           | ALTDTR   | 3<13:0> |          |          |          |          |          |          | 0000          |

| SDC3        | 0C6E  |         |         |         |         |           |           |           | SDC3      | <15:0>   |         |          |          |          |          |          |          | 0000          |

| SPHASE3     | 0C70  |         |         |         |         |           |           |           | SPHASE    | E3<15:0> |         |          |          |          |          |          |          | 0000          |

| TRIG3       | 0C72  |         |         |         |         |           |           |           | TRGCM     | IP<15:0> |         |          |          |          |          |          |          | 0000          |

| TRGCON3     | 0C74  | TRGDIV3 | TRGDIV2 | TRGDIV1 | TRGDIV0 | _         | _         | _         | _         | _        | _       | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP3     | 0C78  |         |         |         |         |           |           |           | PWMCA     | P3<15:0> |         |          |          |          |          |          |          | 0000          |

| LEBCON3     | 0C7A  | PHR     | PHF     | PLR     | PLF     | FLTLEBEN  | CLLEBEN   | _         | _         | _        | _       | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY3     | 0C7C  | _       | -       | _       | _       |           |           |           |           |          | LEB<    | 11:0>    |          |          |          |          |          | 0000          |

| AUXCON3     | 0C7E  | _       | -       | _       | _       | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | BLANKSEL0 | _        | _       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4-28: CAN2 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FOR dsPIC33EPXXXGM60X/7XX DEVICES <sup>(1)</sup> (CONTINUED | <b>TABLE 4-28</b> : | CAN2 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FO | )R dsPIC33EPXXXGM60X/7XX DEVICES <sup>(1)</sup> (CONTINUED) |

|--------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------|-------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------|-------------------------------------------------------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|----------|-------|-------|-------|-------|-------|-------|-------|---------------|

| C2RXF11SID  | 056C  | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | _     | EXIDE | —     | EID17 | EID16 | xxxx          |

| C2RXF11EID  | 056E  |        |        |        |        |        |        |       | E     | ID<15:0> |       |       |       |       |       |       |       | xxxx          |

| C2RXF12SID  | 0570  | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | _     | MIDE  | _     | EID17 | EID16 | xxxx          |

| C2RXF12EID  | 0572  |        |        |        |        |        |        |       | E     | ID<15:0> |       |       |       |       |       |       |       | xxxx          |

| C2RXF13SID  | 0574  | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | —     | MIDE  | —     | EID17 | EID16 | xxxx          |

| C2RXF13EID  | 0576  |        |        |        |        |        |        |       | E     | ID<15:0> |       |       |       |       |       |       |       | xxxx          |

| C2RXF14SID  | 0578  | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | —     | MIDE  | —     | EID17 | EID16 | xxxx          |

| C2RXF14EID  | 057A  |        |        |        |        |        |        |       | E     | ID<15:0> |       |       |       |       |       |       |       | xxxx          |

| C2RXF15SID  | 057C  | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2     | SID1  | SID0  | —     | MIDE  | _     | EID17 | EID16 | xxxx          |

| C2RXF15EID  | 057E  |        |        |        |        |        |        |       | E     | ID<15:0> |       |       |       |       |       |       |       | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers are not present on dsPIC33EPXXXGM3XX devices.

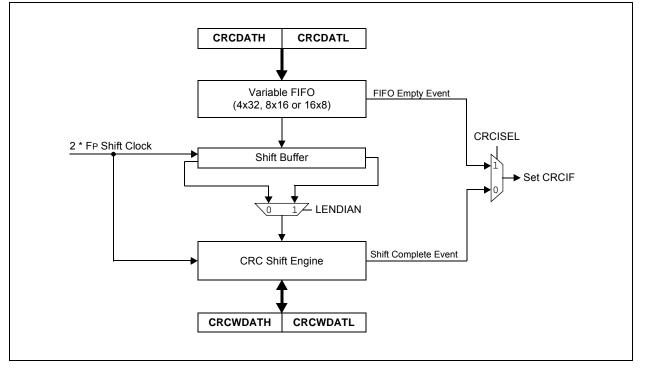

#### TABLE 4-29: PROGRAMMABLE CRC REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8         | Bit 7      | Bit 6   | Bit 5   | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|---------|---------|---------|---------|---------------|------------|---------|---------|-------|---------|-------|-------|-------|---------------|

| CRCCON1     | 0640  | CRCEN  | —      | CSIDL  | VWORD4  | VWORD3  | VWORD2  | VWORD1  | VWORD0        | CRCFUL     | CRCMPT  | CRCISEL | CRCGO | LENDIAN | —     | —     | —     | 0000          |

| CRCCON2     | 0642  | _      | _      | _      | DWIDTH4 | DWIDTH3 | DWIDTH2 | DWIDTH1 | DWIDTH0       | _          | _       | _       | PLEN4 | PLEN3   | PLEN2 | PLEN1 | PLEN0 | 0000          |

| CRCXORL     | 0644  |        |        |        |         |         |         |         | X<15:1>       |            |         |         |       |         |       |       | —     | 0000          |

| CRCXORH     | 0646  |        |        |        |         |         |         |         | X<31          | :16>       |         |         |       |         |       |       |       | 0000          |

| CRCDATL     | 0648  |        |        |        |         |         |         | CRC E   | Data Input Lo | w Word Re  | egister |         |       |         |       |       |       | 0000          |

| CRCDATH     | 064A  |        |        |        |         |         |         | CRC D   | ata Input Hi  | gh Word Re | egister |         |       |         |       |       |       | 0000          |

| CRCWDATL    | 064C  |        |        |        |         |         |         | CRC     | Result Low    | Word Regi  | ster    |         |       |         |       |       |       | 0000          |

| CRCWDATH    | 064E  |        |        |        |         |         |         | CRC     | Result High   | Word Reg   | ister   |         |       |         |       |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Shaded bits are not used in the operation of the programmable CRC module.

# dsPIC33EPXXXGM3XX/6XX/7XX

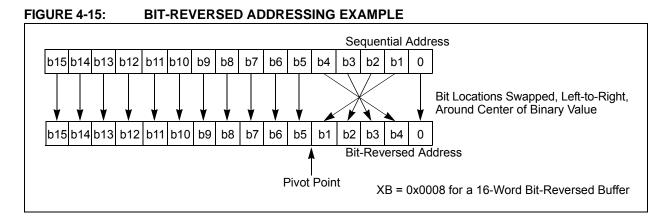

# TABLE 4-67: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      |    |    | Bit-Rev | ersed Ac | ldress  |

|----|----|-------|-----------|---------|----|----|---------|----------|---------|

| A3 | A2 | A1    | A0        | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0  | 0     | 1         | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0  | 1     | 0         | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0  | 1     | 1         | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1  | 0     | 0         | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1  | 0     | 1         | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1  | 1     | 0         | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1  | 1     | 1         | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0  | 0     | 0         | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0  | 0     | 1         | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0  | 1     | 0         | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0  | 1     | 1         | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1  | 0     | 0         | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1  | 0     | 1         | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1  | 1     | 0         | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1  | 1     | 1         | 15      | 1  | 1  | 1       | 1        | 15      |

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme, based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-increment Addressing mode

- Register Indirect without Post-increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- · CPU interrupt after half or full block transfer complete

- · Byte or word transfers

- Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM Start addresses after each block transfer complete)

- DMA request for each channel can be selected from any supported interrupt source

- · Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA<br>Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|----------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0      | 00000000                             | _                                                       | _                                                      |

| IC1 – Input Capture 1            | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2            | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3            | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4            | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1           | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2           | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3           | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4           | 00011010                             | _                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                    | 00000111                             | —                                                       | —                                                      |

| TMR3 – Timer3                    | 00001000                             | —                                                       | —                                                      |

| TMR4 – Timer4                    | 00011011                             | —                                                       | _                                                      |

| TMR5 – Timer5                    | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done               | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done               | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| SPI3 Transfer Done               | 01011011                             | 0x02A8(SPI3BUF)                                         | 0x02A8(SPI3BUF)                                        |

| UART1RX – UART1 Receiver         | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter      | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver         | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter      | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |

| UART3RX – UART3 Receiver         | 01010010                             | 0X0256(U3RXREG)                                         |                                                        |

| UART3TX – UART3 Transmitter      | 01010011                             | _                                                       | 0X0254(U3TXREG)                                        |

| UART4RX – UART4 Receiver         | 01011000                             | 0X02B6(U4RXREG)                                         |                                                        |

| UART4TX – UART4 Transmitter      | 01011001                             |                                                         | 0X02B4(U4TXREG)                                        |

#### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

| REGISTER 8-12: | DMARQC: DMA REQUEST COLLISION STATUS REGISTER |

|----------------|-----------------------------------------------|

|----------------|-----------------------------------------------|

| U-0           | U-0          | U-0                                 | U-0           | U-0               | U-0              | U-0                | U-0    |  |  |  |

|---------------|--------------|-------------------------------------|---------------|-------------------|------------------|--------------------|--------|--|--|--|

| —             | —            | —                                   | —             | —                 | —                | _                  | —      |  |  |  |

| bit 15        | •            | •                                   | •             |                   |                  | •                  | bit 8  |  |  |  |

|               |              |                                     |               |                   |                  |                    |        |  |  |  |

| U-0           | U-0          | U-0                                 | U-0           | R-0               | R-0              | R-0                | R-0    |  |  |  |

| —             | —            | —                                   | —             | RQCOL3            | RQCOL2           | RQCOL1             | RQCOL0 |  |  |  |

| bit 7         |              |                                     |               |                   |                  |                    | bit C  |  |  |  |

|               |              |                                     |               |                   |                  |                    |        |  |  |  |

| Legend:       |              |                                     |               |                   |                  |                    |        |  |  |  |

| R = Readable  | e bit        | W = Writable                        | bit           | U = Unimpler      | mented bit, read | as '0'             |        |  |  |  |

| -n = Value at | POR          | '1' = Bit is set                    |               | '0' = Bit is cle  | ared             | x = Bit is unknown |        |  |  |  |

|               |              |                                     |               |                   |                  |                    |        |  |  |  |

| bit 15-4      | Unimplemen   | ted: Read as '                      | 0'            |                   |                  |                    |        |  |  |  |

| bit 3         | RQCOL3: Ch   | annel 3 Transf                      | er Request Co | ollision Flag bit |                  |                    |        |  |  |  |

|               |              | RCE and interr                      |               | uest collision a  | are detected     |                    |        |  |  |  |

|               | 0 = No reque | st collision is d                   | etected       |                   |                  |                    |        |  |  |  |

| bit 2         |              | annel 2 Transf                      |               | 0                 |                  |                    |        |  |  |  |

|               |              | RCE and interr                      | • •           | uest collision a  | are detected     |                    |        |  |  |  |

|               |              | st collision is d                   |               |                   |                  |                    |        |  |  |  |

| bit 1         |              | annel 1 Transf                      | -             | -                 |                  |                    |        |  |  |  |

|               |              | RCE and interr<br>st collision is d | •             | uest collision a  | are detected     |                    |        |  |  |  |

| bit 0         | RQCOL0: Ch   | annel 0 Transf                      | er Request Co | ollision Flag bit |                  |                    |        |  |  |  |

|               | 1 = User FOF | RCE and interr                      | unt-hased red | uest collision a  | are detected     |                    |        |  |  |  |

- 1 = User FORCE and interrupt-based request collision are detected

- 0 = No request collision is detected

| REGISTER 10-4: | <b>PMD4: PERIPHERAL</b> | MODULE DISABLE | CONTROL REGISTER 4 |

|----------------|-------------------------|----------------|--------------------|

|----------------|-------------------------|----------------|--------------------|

| U-0                   | U-0                | U-0              | U-0           | U-0           | U-0              | U-0                | U-0   |  |  |  |

|-----------------------|--------------------|------------------|---------------|---------------|------------------|--------------------|-------|--|--|--|

| _                     | —                  | —                | —             | —             | —                | —                  | —     |  |  |  |

| bit 15                |                    |                  |               |               |                  |                    | bit 8 |  |  |  |

|                       |                    |                  |               |               |                  |                    |       |  |  |  |

| U-0                   | U-0                | R/W-0            | U-0           | R/W-0         | R/W-0            | U-0                | U-0   |  |  |  |

| —                     | —                  | U4MD             | —             | REFOMD        | CTMUMD           | —                  | _     |  |  |  |

| bit 7                 |                    |                  |               |               |                  |                    | bit 0 |  |  |  |

| Logondi               |                    |                  |               |               |                  |                    |       |  |  |  |

| Legend:<br>R = Readal | bla bit            | W = Writable     | hit           | LI – Unimplon | contod hit rook  | 1 00 '0'           |       |  |  |  |

|                       |                    | '1' = Bit is set |               | 0 – Onimpien  | nented bit, read | x = Bit is unknown |       |  |  |  |

| -n = Value a          | alpur              |                  |               |               | areu             |                    | IOWII |  |  |  |

| bit 15-6              | Unimplemen         | ted: Read as 'd  | )'            |               |                  |                    |       |  |  |  |

| bit 5                 | -                  | 4 Module Disa    |               |               |                  |                    |       |  |  |  |

|                       | 1 = UART4 m        | odule is disable | ed            |               |                  |                    |       |  |  |  |

|                       | 0 <b>= UART4 m</b> | odule is enable  | ed            |               |                  |                    |       |  |  |  |

| bit 4                 | Unimplemen         | ted: Read as 'd  | )'            |               |                  |                    |       |  |  |  |

| bit 3                 | REFOMD: Re         | eference Clock   | Module Disabl | le bit        |                  |                    |       |  |  |  |

|                       | 1 = Reference      | e clock module   | is disabled   |               |                  |                    |       |  |  |  |

|                       | 0 = Reference      | e clock module   | is enabled    |               |                  |                    |       |  |  |  |

| bit 2                 | CTMUMD: C          | TMU Module Di    | isable bit    |               |                  |                    |       |  |  |  |

|                       |                    | odule is disable |               |               |                  |                    |       |  |  |  |

|                       | 0 = CTMU mo        | odule is enable  | d             |               |                  |                    |       |  |  |  |

| 11110                 |                    |                  | - 1           |               |                  |                    |       |  |  |  |

bit 1-0 Unimplemented: Read as '0'

### REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

| U-0                               | U-0 | R/W-0            | R/W-0  | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|-----------------------------------|-----|------------------|--------|-------------------|------------------|-----------------|--------|

| —                                 | —   | PWM6MD           | PWM5MD | PWM4MD            | PWM3MD           | PWM2MD          | PWM1MD |

| bit 15                            |     |                  |        |                   |                  |                 | bit 8  |

|                                   |     |                  |        |                   |                  |                 |        |

| U-0                               | U-0 | U-0              | U-0    | U-0               | U-0              | U-0             | R/W-0  |

| —                                 | —   | —                | —      | —                 | —                | —               | SPI3MD |

| bit 7                             |     |                  |        |                   |                  |                 | bit 0  |

|                                   |     |                  |        |                   |                  |                 |        |

| Legend:                           |     |                  |        |                   |                  |                 |        |

| R = Readable bit W = Writable bit |     |                  | bit    | U = Unimplem      | nented bit, read | l as '0'        |        |

| -n = Value at                     | POR | '1' = Bit is set |        | '0' = Bit is clea | ared             | x = Bit is unkn | iown   |

| bit 15-14 | Unimplemented: Read as '0'                              |

|-----------|---------------------------------------------------------|

| bit 13-8  | <b>PWM6MD:PWM1MD:</b> PWMx (x = 1-6) Module Disable bit |

|           | 1 = PWMx module is disabled                             |

|           | 0 = PWMx module is enabled                              |

| bit 7-1   | Unimplemented: Read as '0'                              |

| bit 0     | SPI3MD: SPI3 Module Disable bit                         |

|           | 1 = SPI3 module is disabled                             |

|           | 0 = SPI3 module is enabled                              |

© 2013-2014 Microchip Technology Inc.

| Input Name <sup>(1)</sup>       | Function Name | Register | Configuration Bits |

|---------------------------------|---------------|----------|--------------------|

| External Interrupt 1            | INT1          | RPINR0   | INT1R<6:0>         |

| External Interrupt 2            | INT2          | RPINR1   | INT2R<6:0>         |

| Timer2 External Clock           | T2CK          | RPINR3   | T2CKR<6:0>         |

| Input Capture 1                 | IC1           | RPINR7   | IC1R<6:0>          |

| Input Capture 2                 | IC2           | RPINR7   | IC2R<6:0>          |

| Input Capture 3                 | IC3           | RPINR8   | IC3R<6:0>          |

| Input Capture 4                 | IC4           | RPINR8   | IC4R<6:0>          |

| Input Capture 5                 | IC5           | RPINR9   | IC5R<6:0>          |

| Input Capture 6                 | IC6           | RPINR9   | IC6R<6:0>          |

| Input Capture 7                 | IC7           | RPINR10  | IC7R<6:0>          |

| Input Capture 8                 | IC8           | RPINR10  | IC8R<6:0>          |

| Output Compare Fault A          | OCFA          | RPINR11  | OCFAR<6:0>         |

| PWM Fault 1                     | FLT1          | RPINR12  | FLT1R<6:0>         |

| PWM Fault 2                     | FLT2          | RPINR12  | FLT2R<6:0>         |

| QEI1 Phase A                    | QEA1          | RPINR14  | QEA1R<6:0>         |

| QEI1 Phase B                    | QEB1          | RPINR14  | QEB1R<6:0>         |

| QEI1 Index                      | INDX1         | RPINR 15 | INDX1R<6:0>        |

| QEI1 Home                       | HOME1         | RPINR15  | HOM1R<6:0>         |

| QEI2 Phase A                    | QEA2          | RPINR16  | QEA2R<6:0>         |

| QEI2 Phase B                    | QEB2          | RPINR16  | QEB2R<6:0>         |

| QEI2 Index                      | INDX2         | RPINR17  | INDX2R<6:0>        |

| QEI2 Home                       | HOME2         | RPINR17  | HOM2R<6:0>         |

| UART1 Receive                   | U1RX          | RPINR18  | U1RXR<6:0>         |

| UART2 Receive                   | U2RX          | RPINR19  | U2RXR<6:0>         |

| SPI2 Data Input                 | SDI2          | RPINR22  | SDI2R<6:0>         |

| SPI2 Clock Input                | SCK2          | RPINR22  | SCK2R<6:0>         |

| SPI2 Slave Select               | SS2           | RPINR23  | SS2R<6:0>          |

| DCI Data Input                  | CSDI          | RPINR24  | CSDIR>6:0>         |

| DCI Clock Input                 | CSCK          | RPINR24  | CSCKR<6:0>         |

| DCI Frame Synchronization Input | COFS          | RPINR25  | COFSR<6:0>         |

| CAN1 Receive <sup>(2)</sup>     | C1RX          | RPINR26  | C1RXR<6:0>         |

| CAN2 Receive <sup>(2)</sup>     | C2RX          | RPINR26  | C2RXR<6:0>         |

| UART3 Receive                   | U3RX          | RPINR27  | U3RXR<6:0>         |

| UART3 Clear-to-Send             | U3CTS         | RPINR27  | U3CTSR<6:0>        |

| UART4 Receive                   | U4RX          | RPINR28  | U4RXR<6:0>         |

| UART4 Clear-to-Send             | U4CTS         | RPINR28  | U4CTSR<6:0>        |

| SPI3 Data Input                 | SDI3          | RPINR29  | SDI3R<6:0>         |

| SPI3 Clock Input                | SCK3          | RPINR29  | SCK3R<6:0>         |

| SPI3 Slave Select               | SS3           | RPINR 30 | SS3R<6:0>          |

**Note 1:** Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

2: This input is available on dsPIC33EPXXXGM6XX/7XX devices only.

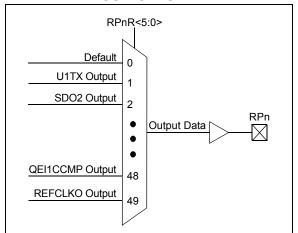

### 11.4.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-30 through Register 11-42). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-to-one and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADCx to convert the digital output logic level or to toggle a digital output on a comparator or ADCx input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

- g) The TRIS registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRIS register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRIS bit must be set to input for pins with only remappable input function(s) assigned.

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin is disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRIS register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

| R/W-0               | R/W-0                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                    | U-0                                                                            | U-0                     | U-0                    |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------|------------------------|

| TRGDIV3             | TRGDIV2                                                                                                                                                                                                                                                      | TRGDIV1                                                                                                                                                                                                                                                                                                                                                                                                                         | TRGDIV0                                                                                                                                                                                                                                                                                    |                                                                                                                                        | _                                                                              |                         | _                      |

| bit 15              |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                                |                         | bit                    |

| U-0                 | U-0                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                  | R/W-0                                                                          | R/W-0                   | R/W-0                  |

| _                   |                                                                                                                                                                                                                                                              | TRGSTRT5 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                         | TRGSTRT5 <sup>(1)</sup>                                                                                                                                                                                                                                                                    | TRGSTRT5 <sup>(1)</sup>                                                                                                                | TRGSTRT5 <sup>(1)</sup>                                                        | TRGSTRT5 <sup>(1)</sup> | TRGSTRT5 <sup>(1</sup> |

| bit 7               |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                                |                         | bit                    |

| Legend:             |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                                |                         |                        |

| R = Readabl         | e bit                                                                                                                                                                                                                                                        | W = Writable I                                                                                                                                                                                                                                                                                                                                                                                                                  | oit                                                                                                                                                                                                                                                                                        | U = Unimplem                                                                                                                           | ented bit, read                                                                | as '0'                  |                        |

| -n = Value at       | POR                                                                                                                                                                                                                                                          | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                            | '0' = Bit is clea                                                                                                                      | ared                                                                           | x = Bit is unkno        | own                    |

|                     |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                            |                                                                                                                                        |                                                                                |                         |                        |

| bit 15-12           | 1111 = Trigg<br>1110 = Trigg<br>1101 = Trigg<br>1001 = Trigg<br>1010 = Trigg<br>1001 = Trigg<br>1000 = Trigg<br>0111 = Trigg<br>0110 = Trigg<br>0101 = Trigg<br>0101 = Trigg<br>0011 = Trigg<br>0010 = Trigg<br>0001 = Trigg<br>0001 = Trigg<br>0000 = Trigg | >: Trigger # Ou<br>er output for ev<br>er output for ev | ery 16th trigge<br>ery 15th trigge<br>ery 15th trigge<br>ery 13th trigge<br>ery 12th trigge<br>ery 12th trigge<br>ery 10th trigger<br>ery 9th trigger<br>ery 8th trigger<br>ery 6th trigger<br>ery 5th trigger<br>ery 5th trigger<br>ery 3rd trigger<br>ery 2nd trigger<br>ery trigger eve | r event<br>r event<br>r event<br>r event<br>r event<br>r event<br>event<br>event<br>event<br>event<br>event<br>event<br>event<br>event |                                                                                |                         |                        |

| bit 11-6<br>bit 5-0 | TRGSTRT<5<br>111111 = Wa                                                                                                                                                                                                                                     | ait 63 PWM cyc                                                                                                                                                                                                                                                                                                                                                                                                                  | stscaler Start E<br>les before gen<br>es before gene                                                                                                                                                                                                                                       | rating the first t                                                                                                                     | its <sup>(1)</sup><br>trigger event af<br>rigger event afte<br>gger event afte | er the module is        | s enabled              |

# REGISTER 16-18: TRGCONx: PWMx TRIGGER CONTROL REGISTER

# **REGISTER 16-23: LEBDLYx: LEADING-EDGE BLANKING DELAY REGISTER x**

| U-0                               | U-0   | U-0              | U-0                                | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|-------------------|-------|-----------------|-------|

| —                                 | _     | —                | —                                  |                   | LEB   | <11:8>          |       |

| bit 15                            |       |                  |                                    |                   |       |                 | bit 8 |

|                                   |       |                  |                                    |                   |       |                 |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|                                   |       |                  | LEE                                | <7:0>             |       |                 |       |

| bit 7                             |       |                  |                                    |                   |       |                 | bit C |

|                                   |       |                  |                                    |                   |       |                 |       |

| Legend:                           |       |                  |                                    |                   |       |                 |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                   |       |                 |       |

| -n = Value at POR                 |       | '1' = Bit is set |                                    | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

# REGISTER 21-11: CxFEN1: CANx ACCEPTANCE FILTER ENABLE REGISTER 1

| R/W-1           | R/W-1 | R/W-1            | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | FLTE  | N<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-1           | R/W-1 | R/W-1            | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|                 |       |                  | FLTE  | N<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | pit   | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0

FLTEN<15:0>: Enable Filter n to Accept Messages bits

1 = Enables Filter n

0 = Disables Filter n

#### REGISTER 21-12: CxBUFPNT1: CANx FILTERS 0-3 BUFFER POINTER REGISTER 1

| R/W-0                         | R/W-0                                                                                              | R/W-0                                                                                                                              | R/W-0                                                                                                     | R/W-0                                              | R/W-0            | R/W-0                       | R/W-0 |

|-------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|-----------------------------|-------|

| F3BP3                         | F3BP2                                                                                              | F3BP1                                                                                                                              | F3BP0                                                                                                     | F2BP3                                              | F2BP2            | F2BP1                       | F2BP0 |

| bit 15                        | •                                                                                                  |                                                                                                                                    |                                                                                                           |                                                    |                  |                             | bit 8 |

| R/W-0                         | R/W-0                                                                                              | R/W-0                                                                                                                              | R/W-0                                                                                                     | R/W-0                                              | R/W-0            | R/W-0                       | R/W-0 |

| F1BP3                         | F1BP2                                                                                              | F1BP1                                                                                                                              | F1BP0                                                                                                     | F0BP3                                              | F0BP2            | F0BP1                       | F0BP0 |

| bit 7                         |                                                                                                    |                                                                                                                                    |                                                                                                           |                                                    |                  |                             | bit ( |

|                               |                                                                                                    |                                                                                                                                    |                                                                                                           |                                                    |                  |                             |       |

| Legend:                       |                                                                                                    |                                                                                                                                    |                                                                                                           |                                                    |                  |                             |       |

|                               |                                                                                                    |                                                                                                                                    |                                                                                                           |                                                    |                  |                             |       |

| R = Readable                  | e bit                                                                                              | W = Writable                                                                                                                       | bit                                                                                                       | U = Unimpler                                       | mented bit, read | d as '0'                    |       |

| R = Readable<br>-n = Value at |                                                                                                    | W = Writable<br>'1' = Bit is set                                                                                                   |                                                                                                           | 0 = Unimpler<br>0' = Bit is cle                    | ,                | t as '0'<br>x = Bit is unkr | nown  |

|                               |                                                                                                    |                                                                                                                                    |                                                                                                           |                                                    | ,                |                             | iown  |

| -n = Value at                 | POR                                                                                                |                                                                                                                                    | t                                                                                                         | ʻ0' = Bit is cle                                   | ,                |                             | iown  |

| -n = Value at                 | POR<br><b>F3BP&lt;3:0&gt;</b> :                                                                    | '1' = Bit is set                                                                                                                   | t<br>k for Filter 3 b                                                                                     | ʻ0' = Bit is cle                                   | ,                |                             | nown  |

| -n = Value at                 | POR<br><b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter                                                    | '1' = Bit is set<br>RX Buffer Mas                                                                                                  | k for Filter 3 b                                                                                          | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | iown  |

| -n = Value at                 | POR<br><b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter                                                    | '1' = Bit is set<br>RX Buffer Mas<br>hits received in                                                                              | k for Filter 3 b                                                                                          | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | iown  |

|                               | POR<br><b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter                                                    | '1' = Bit is set<br>RX Buffer Mas<br>hits received in                                                                              | k for Filter 3 b                                                                                          | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | nown  |

| -n = Value at                 | POR<br><b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter                                                    | '1' = Bit is set<br>RX Buffer Mas<br>hits received in                                                                              | k for Filter 3 b                                                                                          | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | nown  |

| -n = Value at                 | POR<br><b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter<br>1110 = Filter<br>0001 = Filter                  | '1' = Bit is set<br>RX Buffer Mas<br>hits received in                                                                              | k for Filter 3 b<br>n RX FIFO bu<br>n RX Buffer 14<br>n RX Buffer 1                                       | ʻ0' = Bit is cle<br>its<br>ffer                    | ,                |                             | nown  |

| -n = Value at                 | POR<br><b>F3BP&lt;3:0&gt;:</b><br>1111 = Filter<br>1110 = Filter<br>0001 = Filter<br>0000 = Filter | '1' = Bit is set<br>RX Buffer Mas<br>hits received in<br>hits received in<br>hits received in<br>hits received in                  | k for Filter 3 b<br>n RX FIFO bur<br>n RX Buffer 14<br>n RX Buffer 1<br>n RX Buffer 0                     | ʻ0' = Bit is cle<br>its<br>iffer                   | ,                | x = Bit is unkr             | iown  |

| -n = Value at<br>bit 15-12    | POR<br>F3BP<3:0>:<br>1111 = Filter<br>1110 = Filter                                                | '1' = Bit is set<br>RX Buffer Mas<br>hits received in<br>hits received in<br>hits received in<br>hits received in<br>RX Buffer Mas | k for Filter 3 b<br>n RX FIFO bur<br>n RX Buffer 14<br>n RX Buffer 1<br>n RX Buffer 0<br>k for Filter 2 b | ʻ0' = Bit is cle<br>its<br>ffer<br>its (same value | ared             | x = Bit is unkr             | iown  |

|  | REGISTER 24-2: | DCICON2: DCI CONTROL REGISTER 2 |

|--|----------------|---------------------------------|

|--|----------------|---------------------------------|

| r-0              | r-0                                                                                                                                            | r-0                                                        | r-0              | R/W-0            | R/W-0           | r-0             | R/W-0          |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------|------------------|-----------------|-----------------|----------------|--|--|--|

| r                | r                                                                                                                                              | r                                                          | r                | BLEN1            | BLEN0           | r               | COFSG3         |  |  |  |

| bit 15           |                                                                                                                                                |                                                            |                  |                  |                 |                 | bit 8          |  |  |  |

| <b>D</b> 4 4 4 0 | <b>DMU</b> O                                                                                                                                   | <b>D</b> 444 0                                             |                  | <b>D44 0</b>     | DAALO           | DAVA            | <b>D</b> 444 0 |  |  |  |

| R/W-0            | R/W-0                                                                                                                                          | R/W-0                                                      | r-0              | R/W-0            | R/W-0           | R/W-0           | R/W-0          |  |  |  |

| COFSG2<br>bit 7  | COFSG1                                                                                                                                         | COFSG0                                                     | r                | WS3              | WS2             | WS1             | WS0            |  |  |  |

|                  |                                                                                                                                                |                                                            |                  |                  |                 |                 |                |  |  |  |

| Legend:          |                                                                                                                                                | r = Reserved b                                             | it               |                  |                 |                 |                |  |  |  |

| R = Readab       | ole bit                                                                                                                                        | W = Writable b                                             | it               | U = Unimpler     | nented bit, rea | ad as '0'       |                |  |  |  |

| -n = Value a     | at POR                                                                                                                                         | '1' = Bit is set                                           |                  | '0' = Bit is cle | ared            | x = Bit is unki | nown           |  |  |  |

| bit 15-12        | Reserved: R                                                                                                                                    | and as '0'                                                 |                  |                  |                 |                 |                |  |  |  |

| bit 11-10        |                                                                                                                                                |                                                            | ontrol hito      |                  |                 |                 |                |  |  |  |

|                  |                                                                                                                                                | Buffer Length Co                                           |                  |                  |                 |                 |                |  |  |  |

|                  | 11 = Four data words will be buffered between interrupts                                                                                       |                                                            |                  |                  |                 |                 |                |  |  |  |

|                  | <ul> <li>10 = Three data words will be buffered between interrupts</li> <li>01 = Two data words will be buffered between interrupts</li> </ul> |                                                            |                  |                  |                 |                 |                |  |  |  |