Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, Motor Control PWM, POR, PWM, WDT               |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 48K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 49x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gm310-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### TABLE 4-12: PWM GENERATOR 4 REGISTER MAP

|             | • ••  |                                                              |                 |         |         |           |           |           |                  |          |         |          |          |          |          |          |          |               |

|-------------|-------|--------------------------------------------------------------|-----------------|---------|---------|-----------|-----------|-----------|------------------|----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15                                                       | Bit 14          | Bit 13  | Bit 12  | Bit 11    | Bit 10    | Bit 9     | Bit 8            | Bit 7    | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| PWMCON4     | 0C80  | FLTSTAT                                                      | CLSTAT          | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS             | DTC1     | DTC0    | DTCP     | _        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON4      | 0C82  | PENH                                                         | PENL            | POLH    | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL           | OVRDAT1  | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | C000          |

| FCLCON4     | 0C84  | IFLTMOD                                                      | CLSRC4          | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD            | FLTSRC4  | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 00F8          |

| PDC4        | 0C86  |                                                              | PDC3<15:0> 0000 |         |         |           |           |           |                  |          | 0000    |          |          |          |          |          |          |               |

| PHASE4      | 0C88  |                                                              |                 |         |         |           |           |           | PHASE            | 3<15:0>  |         |          |          |          |          |          |          | 0000          |

| DTR4        | 0C8A  | _                                                            | _               |         |         |           |           |           |                  | DTR3     | <13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR4     | 0C8C  | _                                                            | _               |         |         |           |           |           |                  | ALTDTR   | 3<13:0> |          |          |          |          |          |          | 0000          |

| SDC4        | 0C8E  |                                                              |                 |         |         |           |           |           | SDC4             | <15:0>   |         |          |          |          |          |          |          | 0000          |

| SPHASE4     | 0C90  |                                                              |                 |         |         |           |           |           | SPHASE           | 4<15:0>  |         |          |          |          |          |          |          | 0000          |

| TRIG4       | 0C92  |                                                              |                 |         |         |           |           |           | TRGCM            | P<15:0>  |         |          |          |          |          |          |          | 0000          |

| TRGCON4     | 0C94  | TRGDIV3                                                      | TRGDIV2         | TRGDIV1 | TRGDIV0 | —         | _         | _         |                  | _        | —       | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP4     | 0C98  |                                                              |                 |         |         |           |           |           | PWMCA            | P4<15:0> |         |          |          |          |          |          |          | 0000          |

| LEBCON4     | 0C9A  | PHR                                                          | PHF             | PLR     | PLF     | FLTLEBEN  | CLLEBEN   | -         | _                | _        | _       | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY4     | 0C9C  | —                                                            | _               | _       | _       |           |           |           |                  |          | LEB<    | 11:0>    |          |          |          |          |          | 0000          |

| AUXCON4     | 0C9E  | _                                                            | _               | _       | _       | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | <b>BLANKSEL0</b> | _        | _       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

| l egend:    | = un  | molemented read as '0' Reset values are shown in hexadecimal |                 |         |         |           |           |           |                  |          |         |          |          |          |          |          |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-13: PWM GENERATOR 5 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14       | Bit 13  | Bit 12  | Bit 11    | Bit 10    | Bit 9     | Bit 8     | Bit 7    | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|--------------|---------|---------|-----------|-----------|-----------|-----------|----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON5     | 0CA0  | FLTSTAT | CLSTAT       | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS      | DTC1     | DTC0    | DTCP     | _        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON5      | 0CA5  | PENH    | PENL         | POLH    | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL    | OVRDAT1  | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | C000          |

| FCLCON5     | 0CA4  | IFLTMOD | CLSRC4       | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD     | FLTSRC4  | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 00F8          |

| PDC5        | 0CA6  |         | PDC5<15:0> 0 |         |         |           |           |           |           |          |         | 0000     |          |          |          |          |          |               |

| PHASE5      | 0CA8  |         |              |         |         |           |           |           | PHASE     | 5<15:0>  |         |          |          |          |          |          |          | 0000          |

| DTR5        | 0CAA  | _       | _            |         |         |           |           |           |           | DTR5<    | 13:0>   |          |          |          |          |          |          | 0000          |

| ALTDTR5     | 0CAC  | _       | _            |         |         |           |           |           |           | ALTDTR   | 5<13:0> |          |          |          |          |          |          | 0000          |

| SDC5        | 0CAE  |         |              |         |         |           |           |           | SDC5      | <15:0>   |         |          |          |          |          |          |          | 0000          |

| SPHASE5     | 0CB0  |         |              |         |         |           |           |           | SPHASE    | =5<15:0> |         |          |          |          |          |          |          | 0000          |

| TRIG5       | 0CB2  |         |              |         |         |           |           |           | TRGCM     | 1P<15:0> |         |          |          |          |          |          |          | 0000          |

| TRGCON5     | 0CB4  | TRGDIV3 | TRGDIV2      | TRGDIV1 | TRGDIV0 | _         | _         | _         | _         | _        | _       | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP5     | 0CB8  |         |              |         |         |           |           |           | PWMCA     | P5<15:0> |         |          |          |          |          |          |          | 0000          |

| LEBCON5     | 0CBA  | PHR     | PHF          | PLR     | PLF     | FLTLEBEN  | CLLEBEN   | _         | _         | _        | _       | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY5     | 0CBC  | _       | _            | _       | _       |           |           |           |           |          | LEB<    | 11:0>    |          |          |          |          |          | 0000          |

| AUXCON5     | 0CBE  |         | -            | _       | _       | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | BLANKSEL0 | _        | _       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| <b>TABLE 4-17:</b> | I2C1 AND I2C2 REGISTER MAP |

|--------------------|----------------------------|

|--------------------|----------------------------|

| SFR<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                      | Bit 8      | Bit 7       | Bit 6   | Bit 5       | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|---------|--------|---------|--------|--------|--------|----------------------------|------------|-------------|---------|-------------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV     | 0200  | —       | _      | —       | -      | —      | _      | —                          | _          |             |         |             | I2C1 Receiv  | ve Register  |       |       |       | 0000          |

| I2C1TRN     | 0202  | —       | _      | _       | _      | —      | _      | —                          | _          |             |         |             | I2C1 Transr  | nit Register |       |       |       | OOFF          |

| I2C1BRG     | 0204  |         |        |         |        |        |        | В                          | aud Rate C | Generator R | egister |             |              |              |       |       |       | 0000          |

| I2C1CON     | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                     | SMEN       | GCEN        | STREN   | ACKDT       | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT    | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                     | ADD10      | IWCOL       | I2COV   | D_A         | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD     | 020A  | _       | _      | _       | _      | _      | _      |                            |            |             |         | I2C1 Addre  | ess Register |              |       |       |       | 0000          |

| I2C1MSK     | 020C  | _       | _      | _       | _      | _      | _      |                            |            |             | 12      | 2C1 Address | Mask Regis   | ster         |       |       |       | 0000          |

| I2C2RCV     | 0210  | _       | _      | _       | _      | _      | _      | _                          | -          |             |         |             | I2C2 Receiv  | ve Register  |       |       |       | 0000          |

| I2C2TRN     | 0212  | _       | _      | _       | _      | _      | _      | _                          | -          |             |         |             | I2C2 Transr  | nit Register |       |       |       | OOFF          |

| I2C2BRG     | 0214  |         |        |         |        |        |        | В                          | aud Rate C | Generator R | egister |             |              |              |       |       |       | 0000          |

| I2C2CON     | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                     | SMEN       | GCEN        | STREN   | ACKDT       | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT    | 0218  | ACKSTAT | TRSTAT | —       | _      | —      | BCL    | GCSTAT                     | ADD10      | IWCOL       | I2COV   | D_A         | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD     | 021A  | _       | _      | _       | _      | —      | _      | I2C2 Address Register 0    |            |             |         |             |              |              | 0000  |       |       |               |

| I2C2MSK     | 021C  |         | _      | —       | —      | —      | _      | I2C2 Address Mask Register |            |             |         |             |              |              | 0000  |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-18: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                        | Bit 7         | Bit 6    | Bit 5 | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|----------|--------|----------|--------|--------|--------|-------|------------------------------|---------------|----------|-------|-------------|--------|--------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0                         | WAKE          | LPBACK   | ABAUD | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1 | UTXINV | UTXISEL0 |        | UTXBRK | UTXEN  | UTXBF | TRMT                         | URXISEL1      | URXISEL0 | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _        |        | —        |        | —      | —      | —     |                              |               |          | UART1 | Fransmit Re | gister |        |        |       | xxxx          |

| U1RXREG     | 0226  | _        | _      | _        | _      | _      | _      | _     |                              |               |          | UART1 | Receive Re  | gister |        |        |       | 0000          |

| U1BRG       | 0228  |          |        |          |        |        |        | Ba    | ud Rate C                    | Generator Pre | scaler   |       |             |        |        |        |       | 0000          |

| U2MODE      | 0230  | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0                         | WAKE          | LPBACK   | ABAUD | URXINV      | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                         | URXISEL1      | URXISEL0 | ADDEN | RIDLE       | PERR   | FERR   | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _        | _      | _        | _      | _      | _      | _     |                              |               |          | UART2 | Fransmit Re | gister |        |        |       | xxxx          |

| U2RXREG     | 0236  | _        | —      | _        | _      | —      | _      | —     |                              |               |          | UART2 | Receive Re  | gister |        |        |       | 0000          |

| U2BRG       | 0238  |          |        |          |        |        |        | Ba    | aud Rate Generator Prescaler |               |          |       |             |        |        | 0000   |       |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

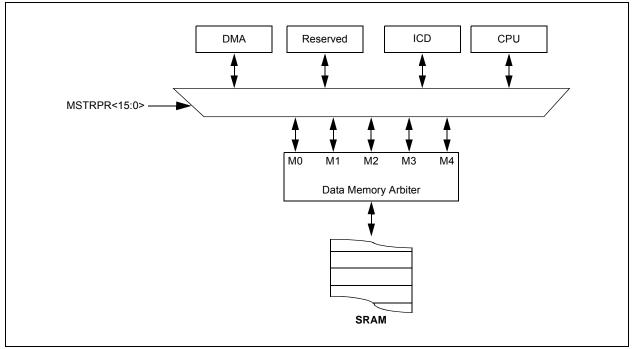

# 4.3.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest with M2 in between). Also, all the bus masters with priorities below

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-65.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

| TABLE 4-65: | DATA MEMORY BUS  |

|-------------|------------------|

|             | ARBITER PRIORITY |

| Drierity     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |  |  |  |  |  |

|--------------|-----------------------------------------|----------|--|--|--|--|--|

| Priority     | 0x0000                                  | 0x0020   |  |  |  |  |  |

| M0 (highest) | CPU                                     | DMA      |  |  |  |  |  |

| M1           | Reserved                                | CPU      |  |  |  |  |  |

| M2           | Reserved                                | Reserved |  |  |  |  |  |

| M3           | DMA                                     | Reserved |  |  |  |  |  |

| M4 (lowest)  | ICD                                     | ICD      |  |  |  |  |  |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

#### FIGURE 4-12: ARBITER ARCHITECTURE

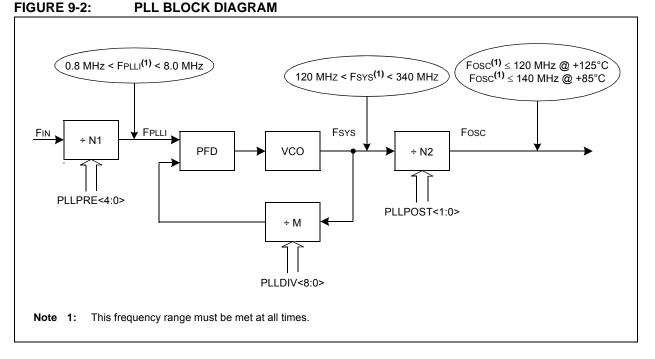

# 9.1 CPU Clocking System

The dsPIC33EPXXXGM3XX/6XX/7XX family of devices provides seven system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase-Locked Loop (PLL)

- FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

- · Secondary (LP) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = FOSC/2

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FOSC).

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FSYS).

#### EQUATION 9-2: Fosc CALCULATION

$$FOSC = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV < 8:0 > + 2)}{(PLLPRE < 4:0 > + 2) \times 2(PLLPOST < 1:0 > + 1)}\right)$$

Where:

N1 = PLLPRE<4:0> + 2 N2 = 2 x (PLLPOST<1:0> + 1) M = PLLDIV<8:0> + 2

#### EQUATION 9-3: Fvco CALCULATION

$FSYS = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV < 8:0 > + 2)}{(PLLPRE < 4:0 > + 2)}\right)$

## **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

| bit 5 | LOCK: PLL Lock Status bit (read-only)                                                                                                                                                     |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that PLL is in lock or PLL start-up timer is satisfied</li> <li>0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled</li> </ul> |

| bit 4 | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 3 | <b>CF:</b> Clock Fail Detect bit (read/clear by application) <sup>(5)</sup>                                                                                                               |

|       | <ul><li>1 = FSCM has detected clock failure</li><li>0 = FSCM has not detected clock failure</li></ul>                                                                                     |

| bit 2 | Unimplemented: Read as '0'                                                                                                                                                                |

| bit 1 | LPOSCEN: Secondary (LP) Oscillator Enable bit                                                                                                                                             |

|       | <ul><li>1 = Enables Secondary Oscillator (SOSC)</li><li>0 = Disables Secondary Oscillator</li></ul>                                                                                       |

| bit 0 | OSWEN: Oscillator Switch Enable bit                                                                                                                                                       |

|       | <ul> <li>1 = Requests oscillator switch to selection specified by the NOSC&lt;2:0&gt; bits</li> <li>0 = Oscillator switch is complete</li> </ul>                                          |

- **Note 1:** Writes to this register require an unlock sequence. Refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Oscillator"** (DS70580), available from the Microchip web site for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This register resets only on a Power-on Reset (POR).

- 4: Secondary Oscillator (SOSC) selection is valid on 64-pin and 100-pin devices, and defaults to FRC/N on 44-pin devices.

- 5: Only '0' should be written to the CF bit in order to clear it. If a '1' is written to CF, it will have the same effect as a detected clock failure, including an oscillator fail trap.

# 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "I/O Ports" (DS70000598) which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

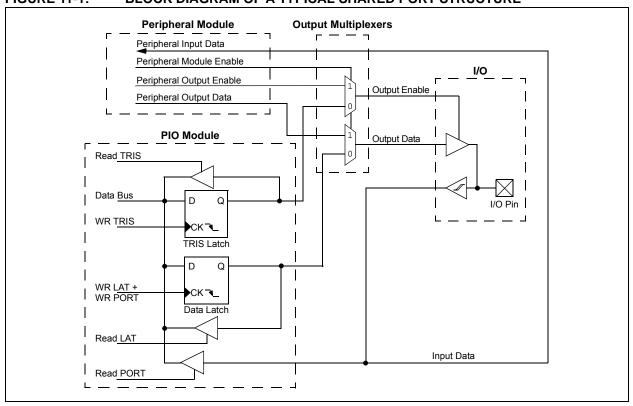

Many of the device pins are shared among the peripherals and the Parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

## 11.1 Parallel I/O (PIO) Ports

Generally, a Parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of

the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the Data Direction register bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device are disabled. This means the corresponding LATx and TRISx registers, and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

#### FIGURE 11-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

| U-0          | R/W-0                                      | R/W-0                                                                        | R/W-0     | R/W-0        | R/W-0                    | R/W-0       | R/W-0 |  |

|--------------|--------------------------------------------|------------------------------------------------------------------------------|-----------|--------------|--------------------------|-------------|-------|--|

|              |                                            |                                                                              |           | C2RXR<6:0>   |                          |             |       |  |

| bit 15       |                                            |                                                                              |           |              |                          |             | bit 8 |  |

|              |                                            |                                                                              |           |              |                          |             |       |  |

| U-0          | R/W-0                                      | R/W-0                                                                        | R/W-0     | R/W-0        | R/W-0                    | R/W-0       | R/W-0 |  |

| —            |                                            |                                                                              |           | C1RXR<6:0>   |                          |             |       |  |

| bit 7        |                                            |                                                                              |           |              |                          |             | bit ( |  |

|              |                                            |                                                                              |           |              |                          |             |       |  |

| Legend:      |                                            |                                                                              |           |              |                          |             |       |  |

| R = Readat   | ole bit                                    | W = Writable                                                                 | bit       | U = Unimplem | nented bit, rea          | d as '0'    |       |  |

| -n = Value a | at POR                                     | '1' = Bit is set '0' = Bit is c                                              |           |              | eared x = Bit is unknown |             |       |  |

|              | 11111100 =  <br>•<br>•<br>•<br>•<br>•<br>• | 1-2 for input pin<br>nput tied to RPI<br>nput tied to CM<br>nput tied to Vss | 124<br>P1 | ,            |                          |             |       |  |

| bit 7        |                                            | nted: Read as '                                                              |           |              |                          |             |       |  |

| bit 6-0      | C10VD-6.0                                  | >: Assign CAN1                                                               |           |              |                          | Do Dio hito |       |  |

# REGISTER 11-20: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26<sup>(1)</sup>

Note 1: This register is not available on dsPIC33EPXXXGM3XX devices.

#### REGISTER 11-36: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| U-0            | U-0                        | R/W-0                                | R/W-0 | R/W-0                   | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |

|----------------|----------------------------|--------------------------------------|-------|-------------------------|------------------|-----------------|-------|--|--|--|--|--|

| _              | —                          |                                      |       | RP55                    | R<5:0>           |                 |       |  |  |  |  |  |

| bit 15         |                            |                                      |       |                         |                  |                 | bit 8 |  |  |  |  |  |

| U-0            | U-0                        | R/W-0                                |       | D/M/ 0                  | D/M/ 0           | D/M/ O          | DAM 0 |  |  |  |  |  |

| 0-0            | 0-0                        | R/W-U                                | R/W-0 | R/W-0                   | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |

| — — RP54R<5:0> |                            |                                      |       |                         |                  |                 |       |  |  |  |  |  |

| bit 7          |                            |                                      |       |                         |                  |                 | bit 0 |  |  |  |  |  |

|                |                            |                                      |       |                         |                  |                 |       |  |  |  |  |  |

| Legend:        |                            |                                      |       |                         |                  |                 |       |  |  |  |  |  |

| R = Readabl    | le bit                     | W = Writable                         | bit   | U = Unimplen            | nented bit, read | d as '0'        |       |  |  |  |  |  |

| -n = Value at  | t POR                      | '1' = Bit is set                     |       | '0' = Bit is clea       | ared             | x = Bit is unkr | nown  |  |  |  |  |  |

| bit 15-14      | Unimpleme                  | nted: Read as '                      | 0'    |                         |                  |                 |       |  |  |  |  |  |

| bit 13-8       |                            | Peripheral Out<br>1-3 for peripheral | •     | n is Assigned to mbers) | RP55 Output I    | Pin bits        |       |  |  |  |  |  |

| bit 7-6        | Unimplemented: Read as '0' |                                      |       |                         |                  |                 |       |  |  |  |  |  |

| bit 5-0        | •                          |                                      |       |                         |                  |                 |       |  |  |  |  |  |

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-37: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0                                | U-0        | R/W-0           | R/W-0          | R/W-0                                   | R/W-0         | R/W-0    | R/W-0 |  |  |  |

|------------------------------------|------------|-----------------|----------------|-----------------------------------------|---------------|----------|-------|--|--|--|

| _                                  | —          |                 |                | RP57R<5:0>                              |               |          |       |  |  |  |

| bit 15                             |            |                 |                |                                         |               |          | bit 8 |  |  |  |

|                                    |            |                 |                |                                         |               |          |       |  |  |  |

| U-0                                | U-0        | R/W-0           | R/W-0          | R/W-0                                   | R/W-0         | R/W-0    | R/W-0 |  |  |  |

| —                                  | —          |                 |                | RP56R<                                  | <5:0>         |          |       |  |  |  |

| bit 7                              |            |                 |                |                                         |               |          | bit 0 |  |  |  |

|                                    |            |                 |                |                                         |               |          |       |  |  |  |

| Legend:                            |            |                 |                |                                         |               |          |       |  |  |  |

| R = Readab                         | le bit     | W = Writable    | bit            | U = Unimpleme                           | nted bit, rea | d as '0' |       |  |  |  |

| -n = Value at POR '1' = Bit is set |            |                 |                | '0' = Bit is cleared x = Bit is unknown |               |          |       |  |  |  |

|                                    |            |                 |                |                                         |               |          |       |  |  |  |

| bit 15-14                          | Unimplemen | ted: Read as '  | 0'             |                                         |               |          |       |  |  |  |

| bit 13-8                           | RP57R<5:0> | • Peripheral Ou | Itout Function | n is Assigned to RI                     | 257 Output    | Pin bits |       |  |  |  |

bit 13-8 **RP57R<5:0>:** Peripheral Output Function is Assigned to RP57 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP56R<5:0>:** Peripheral Output Function is Assigned to RP56 Output Pin bits (see Table 11-3 for peripheral function numbers)

NOTES:

# 19.1 I<sup>2</sup>C Control Registers

# REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| REGISTER     | 19-1: I2CxC                                                                                                                                                                              | ON: I2Cx CC                                                                                                                                                                                                        | ONTROL REG                          | SISTER                       |                                     |                 |           |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------|-------------------------------------|-----------------|-----------|--|--|--|--|--|

| R/W-0        | U-0                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                              | R/W-1, HC                           | R/W-0                        | R/W-0                               | R/W-0           | R/W-0     |  |  |  |  |  |

| I2CEN        |                                                                                                                                                                                          | I2CSIDL                                                                                                                                                                                                            | SCLREL                              | IPMIEN <sup>(1)</sup>        | A10M                                | DISSLW          | SMEN      |  |  |  |  |  |

| bit 15       |                                                                                                                                                                                          | •                                                                                                                                                                                                                  |                                     | ·                            |                                     |                 | bit 8     |  |  |  |  |  |

| R/W-0        | R/W-0                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                              | R/W-0, HC                           | R/W-0, HC                    | R/W-0, HC                           | R/W-0, HC       | R/W-0, HC |  |  |  |  |  |

| GCEN         | STREN                                                                                                                                                                                    | ACKDT                                                                                                                                                                                                              | ACKEN                               | RCEN                         | RSEN                                | SEN             |           |  |  |  |  |  |

| bit 7        |                                                                                                                                                                                          |                                                                                                                                                                                                                    |                                     | I                            |                                     |                 | bit       |  |  |  |  |  |

| Legend:      |                                                                                                                                                                                          | HC = Hardwa                                                                                                                                                                                                        | are Clearable bi                    | it                           |                                     |                 |           |  |  |  |  |  |

| R = Readab   | ole bit                                                                                                                                                                                  | W = Writable                                                                                                                                                                                                       | bit                                 | U = Unimpler                 | mented bit, read                    | d as '0'        |           |  |  |  |  |  |

| -n = Value a | t POR                                                                                                                                                                                    | '1' = Bit is set                                                                                                                                                                                                   | :                                   | '0' = Bit is cle             | ared                                | x = Bit is unkr | iown      |  |  |  |  |  |

| bit 15       | <b>12CEN:</b> 12Cx                                                                                                                                                                       | Enable bit                                                                                                                                                                                                         |                                     |                              |                                     |                 |           |  |  |  |  |  |

|              |                                                                                                                                                                                          |                                                                                                                                                                                                                    |                                     |                              | and SCLx pins a<br>ed by port funct |                 | ns        |  |  |  |  |  |

| bit 14       | Unimplemen                                                                                                                                                                               | ted: Read as                                                                                                                                                                                                       | '0'                                 |                              |                                     |                 |           |  |  |  |  |  |

| bit 13       | 12CSIDL: 12C                                                                                                                                                                             | x Stop in Idle                                                                                                                                                                                                     | Mode bit                            |                              |                                     |                 |           |  |  |  |  |  |

|              |                                                                                                                                                                                          |                                                                                                                                                                                                                    | peration when o<br>ation in Idle mo |                              | an Idle mode                        |                 |           |  |  |  |  |  |

| bit 12       | SCLREL: SCLx Release Control bit (when operating as I <sup>2</sup> C <sup>™</sup> slave)                                                                                                 |                                                                                                                                                                                                                    |                                     |                              |                                     |                 |           |  |  |  |  |  |

|              |                                                                                                                                                                                          | 1 = Releases SCLx clock                                                                                                                                                                                            |                                     |                              |                                     |                 |           |  |  |  |  |  |

|              |                                                                                                                                                                                          | 0 = Holds SCLx clock low (clock stretch)                                                                                                                                                                           |                                     |                              |                                     |                 |           |  |  |  |  |  |

|              |                                                                                                                                                                                          | If STREN = 1:<br>Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clears                                                                                     |                                     |                              |                                     |                 |           |  |  |  |  |  |

|              | at the beginning of every slave data byte transmission. Hardware clears at the end of every slave address byte reception. Hardware clears at the end of every slave data byte reception. |                                                                                                                                                                                                                    |                                     |                              |                                     |                 |           |  |  |  |  |  |

|              |                                                                                                                                                                                          | <u>If STREN = 0:</u>                                                                                                                                                                                               |                                     |                              |                                     |                 |           |  |  |  |  |  |

|              |                                                                                                                                                                                          | Bit is R/S (i.e., software can only write '1' to release clock). Hardware clears at the beginning of every slave data byte transmission. Hardware clears at the end of every slave address byte reception.         |                                     |                              |                                     |                 |           |  |  |  |  |  |

| hit 11       | -                                                                                                                                                                                        |                                                                                                                                                                                                                    |                                     |                              | -                                   |                 | eception. |  |  |  |  |  |

| bit 11       | <b>IPMIEN:</b> Intelligent Peripheral Management Interface (IPMI) Enable bit <sup>(1)</sup><br>1 = IPMI mode is enabled; all addresses are Acknowledged                                  |                                                                                                                                                                                                                    |                                     |                              |                                     |                 |           |  |  |  |  |  |

|              | <ul> <li>IPMI mode is enabled; all addresses are Acknowledged</li> <li>IPMI mode is disabled</li> </ul>                                                                                  |                                                                                                                                                                                                                    |                                     |                              |                                     |                 |           |  |  |  |  |  |

| bit 10       | A10M: 10-Bit                                                                                                                                                                             | Slave Addres                                                                                                                                                                                                       | s bit                               |                              |                                     |                 |           |  |  |  |  |  |

|              |                                                                                                                                                                                          | 1 = I2CxADD is a 10-bit slave address<br>0 = I2CxADD is a 7-bit slave address                                                                                                                                      |                                     |                              |                                     |                 |           |  |  |  |  |  |

| bit 9        | DISSLW: Disa                                                                                                                                                                             | DISSLW: Disable Slew Rate Control bit                                                                                                                                                                              |                                     |                              |                                     |                 |           |  |  |  |  |  |

|              |                                                                                                                                                                                          | control is disa<br>control is ena                                                                                                                                                                                  |                                     |                              |                                     |                 |           |  |  |  |  |  |

| bit 8        | SMEN: SMB                                                                                                                                                                                | SMEN: SMBus Input Levels bit                                                                                                                                                                                       |                                     |                              |                                     |                 |           |  |  |  |  |  |

|              | 1 = Enables I                                                                                                                                                                            | -                                                                                                                                                                                                                  | lds compliant v                     | vith the SMBu                | s specification                     |                 |           |  |  |  |  |  |

| bit 7        |                                                                                                                                                                                          | •                                                                                                                                                                                                                  |                                     | rating as I <sup>2</sup> C s | slave)                              |                 |           |  |  |  |  |  |

|              | 1 = Enables i<br>reception                                                                                                                                                               | <ul> <li>GCEN: General Call Enable bit (when operating as I<sup>2</sup>C slave)</li> <li>1 = Enables interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)</li> </ul> |                                     |                              |                                     |                 |           |  |  |  |  |  |

|              | 0 = General                                                                                                                                                                              | call address is                                                                                                                                                                                                    | disabled                            |                              |                                     |                 |           |  |  |  |  |  |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

# REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Start (or Repeated Start) bit has been detected last                                |

|       | 0 = Start bit was not detected last                                                                      |

|       | Hardware sets or clears when Start, Repeated Start or Stop is detected.                                  |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                        |

|       | 1 = Read – indicates data transfer is output from slave                                                  |

|       | 0 = Write – indicates data transfer is input to slave                                                    |

|       | Hardware sets or clears after reception of an I <sup>2</sup> C device address byte.                      |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                      |

|       | 1 = Receive is complete, I2CxRCV is full                                                                 |

|       | 0 = Receive is not complete, I2CxRCV is empty                                                            |

|       | Hardware sets when I2CxRCV is written with a received byte. Hardware clears when software reads I2CxRCV. |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                     |

|       | 1 = Transmit is in progress, I2CxTRN is full                                                             |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                               |

|       | Hardware sets when software writes to I2CxTRN. Hardware clears at completion of data transmission.       |

| R/W-0                                                                | R/W-0                                                                                                    | R/W-0                        | R/W-0                             | R/W-0             | R/W-0            | R/W-0           | R/W-0    |  |  |  |  |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------|-------------------|------------------|-----------------|----------|--|--|--|--|

| EDG1MOD                                                              | EDG1POL                                                                                                  | EDG1SEL3                     | EDG1SEL2                          | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT |  |  |  |  |

| bit 15                                                               | •                                                                                                        | •                            |                                   | •                 | •                |                 | bit 8    |  |  |  |  |

|                                                                      |                                                                                                          |                              |                                   |                   |                  |                 |          |  |  |  |  |

| R/W-0                                                                | R/W-0                                                                                                    | R/W-0                        | R/W-0                             | R/W-0             | R/W-0            | U-0             | U-0      |  |  |  |  |

| EDG2MOD                                                              | EDG2POL                                                                                                  | EDG2SEL3                     | L3 EDG2SEL2 EDG2SEL1 EDG2SEL0 — - |                   |                  |                 |          |  |  |  |  |

| bit 7                                                                |                                                                                                          |                              |                                   | •                 | •                |                 | bit 0    |  |  |  |  |

|                                                                      |                                                                                                          |                              |                                   |                   |                  |                 |          |  |  |  |  |

| Legend:                                                              |                                                                                                          |                              |                                   |                   |                  |                 |          |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                                                          |                              |                                   |                   |                  |                 |          |  |  |  |  |

| -n = Value at                                                        | POR                                                                                                      | '1' = Bit is set             |                                   | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |  |  |  |  |

|                                                                      |                                                                                                          |                              |                                   |                   |                  |                 |          |  |  |  |  |

| bit 15                                                               | EDG1MOD: E                                                                                               | Edge 1 Edge Sa               | ampling Mode                      | Selection bit     |                  |                 |          |  |  |  |  |

|                                                                      | •                                                                                                        | edge-sensitive               |                                   |                   |                  |                 |          |  |  |  |  |

|                                                                      | •                                                                                                        | level-sensitive              |                                   |                   |                  |                 |          |  |  |  |  |

| bit 14                                                               |                                                                                                          | dge 1 Polarity               |                                   | I                 |                  |                 |          |  |  |  |  |

|                                                                      |                                                                                                          | programmed f<br>programmed f |                                   |                   |                  |                 |          |  |  |  |  |

| bit 13-10                                                            | -                                                                                                        | :0>: Edge 1 So               | -                                 |                   |                  |                 |          |  |  |  |  |

| 51115-10                                                             | 1111 = Fosc                                                                                              | <b>0</b> >. Euge 1 00        |                                   | 2                 |                  |                 |          |  |  |  |  |

|                                                                      | 1111 = FOSC<br>1110 = OSCI pin                                                                           |                              |                                   |                   |                  |                 |          |  |  |  |  |

|                                                                      | 1101 = FRC oscillator                                                                                    |                              |                                   |                   |                  |                 |          |  |  |  |  |

|                                                                      | 1100 = Reserved                                                                                          |                              |                                   |                   |                  |                 |          |  |  |  |  |

|                                                                      | 1011 = Internal LPRC oscillator                                                                          |                              |                                   |                   |                  |                 |          |  |  |  |  |

|                                                                      | 1010 = Reserved<br>100x = Reserved                                                                       |                              |                                   |                   |                  |                 |          |  |  |  |  |

|                                                                      | 01xx = Reser                                                                                             | rved                         |                                   |                   |                  |                 |          |  |  |  |  |

|                                                                      | 0011 = CTED1 pin                                                                                         |                              |                                   |                   |                  |                 |          |  |  |  |  |

|                                                                      | 0010 = CTED2 pin                                                                                         |                              |                                   |                   |                  |                 |          |  |  |  |  |

|                                                                      | 0001 = OC1 module<br>0000 = Timer1 module                                                                |                              |                                   |                   |                  |                 |          |  |  |  |  |

| bit 9                                                                | EDG2STAT: E                                                                                              | Edge 2 Status b              | it                                |                   |                  |                 |          |  |  |  |  |

|                                                                      |                                                                                                          | -                            |                                   | vritten to contro | I the edge sou   | rce.            |          |  |  |  |  |

|                                                                      | Indicates the status of Edge 2 and can be written to control the edge source.<br>1 = Edge 2 has occurred |                              |                                   |                   |                  |                 |          |  |  |  |  |

|                                                                      | •                                                                                                        | as not occurred              |                                   |                   |                  |                 |          |  |  |  |  |

| bit 8                                                                | EDG1STAT: Edge 1 Status bit                                                                              |                              |                                   |                   |                  |                 |          |  |  |  |  |

|                                                                      |                                                                                                          | -                            | 1 and can be v                    | written to contro | ol the edge sour | rce.            |          |  |  |  |  |

|                                                                      | 1 = Edge 1 ha                                                                                            | as not occurred              | I                                 |                   |                  |                 |          |  |  |  |  |

| bit 7                                                                | •                                                                                                        | Edge 2 Edge Sa               |                                   | Selection bit     |                  |                 |          |  |  |  |  |

|                                                                      |                                                                                                          | edge-sensitive               |                                   |                   |                  |                 |          |  |  |  |  |

|                                                                      | -                                                                                                        | level-sensitive              |                                   |                   |                  |                 |          |  |  |  |  |

| bit 6                                                                | EDG2POL: E                                                                                               | dge 2 Polarity               | Select bit                        |                   |                  |                 |          |  |  |  |  |

|                                                                      |                                                                                                          | programmed f                 |                                   |                   |                  |                 |          |  |  |  |  |

|                                                                      | 0 = Edge 2 is                                                                                            | programmed f                 | or a negative e                   | edge response     |                  |                 |          |  |  |  |  |

|                                                                      | he TGEN bit is<br>0G2SELx bits fi                                                                        |                              |                                   |                   | selected as the  | e Edge 2 sourc  | e in the |  |  |  |  |

## REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

# 24.2 DCI Control Registers

# REGISTER 24-1: DCICON1: DCI CONTROL REGISTER 1

| 1<br>bit 14 Re<br>bit 13 De<br>1<br>0<br>bit 12 Re<br>bit 11 DI                                                                                                                                                                                                                                                                                                     | e bit<br>POR<br>CIEN: DCI M<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                           | e is disabled                                                                                                                     | t              | r-0<br>r<br>U = Unimplem<br>'0' = Bit is clea | r-0<br>r<br>ented bit, read a | CSCKE<br>R/W-0<br>COFSM1<br>as '0'<br>x = Bit is unkno | COFSD<br>bit 8<br>R/W-0<br>COFSM0<br>bit 0 |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------|-------------------------------|--------------------------------------------------------|--------------------------------------------|--|--|--|

| R/W-0         UNFM         bit 7         Legend:         R = Readable         -n = Value at         bit 15       D0         bit 14       Re         bit 13       D0         bit 13       D0         bit 13       D0         bit 13       D0         bit 14       Re         bit 13       D0         bit 14       Re         bit 13       D0         bit 14       D1 | CSDOM<br>e bit<br>POR<br>CIEN: DCI M<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                  | DJST<br>r = Reserved bi<br>W = Writable bi<br>'1' = Bit is set<br>lodule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0' | r<br>t<br>t    | r<br>U = Unimplem                             | r<br>ented bit, read a        | COFSM1                                                 | R/W-0<br>COFSM0<br>bit (                   |  |  |  |

| UNFM<br>bit 7<br>Legend:<br>R = Readable<br>-n = Value at<br>bit 15 D0<br>1<br>0<br>bit 14 Re<br>bit 13 D0<br>1<br>0<br>bit 12 Re<br>bit 12 Re                                                                                                                                                                                                                      | CSDOM<br>e bit<br>POR<br>CIEN: DCI M<br>= DCI module<br>= DCI module<br>eserved: Rea<br>CISIDL: DCI<br>= Module will                  | DJST<br>r = Reserved bi<br>W = Writable bi<br>'1' = Bit is set<br>lodule Enable bit<br>e is enabled<br>e is disabled<br>ad as '0' | r<br>t<br>t    | r<br>U = Unimplem                             | r<br>ented bit, read a        | COFSM1                                                 | COFSM0<br>bit (                            |  |  |  |