Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| Product Status            | Active                                                                           |

| Core Processor            | dsPIC                                                                            |

| Core Size                 | 16-Bit                                                                           |

| Speed                     | 60 MIPs                                                                          |

| Connectivity              | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals               | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| lumber of I/O             | 35                                                                               |

| Program Memory Size       | 512KB (170K x 24)                                                                |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AAM Size                  | 48K x 8                                                                          |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| ata Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type           | Internal                                                                         |

| perating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Nounting Type             | Surface Mount                                                                    |

| ackage / Case             | 44-TQFP                                                                          |

| Supplier Device Package   | 44-TQFP (10x10)                                                                  |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gm604-e-pt |

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER<sup>(3)</sup> (CONTINUED)

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup>

1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

bit 2 SFA: Stack Frame Active Status bit

1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and DSWPAG values

0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space

bit 1 RND: Rounding Mode Select bit

1 = Biased (conventional) rounding is enabled

0 = Unbiased (convergent) rounding is enabled

IF: Integer or Fractional Multiplier Mode Select bit

1 = Integer mode is enabled for DSP multiply0 = Fractional mode is enabled for DSP multiply

Note 1: This bit is always read as '0'.

bit 0

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

3: Refer to the "dsPIC33/PIC24 Family Reference Manual", "CPU" (DS70359) for more detailed information.

#### TABLE 4-46: PORTA REGISTER MAP FOR dsPIC33EPXXXGM310/710 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14  | Bit 13 | Bit 12      | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-------------|-------|--------|---------|--------|-------------|------------|--------|-------|-------|--------|-------|-------|--------|--------|-------|-------|--------|---------------|

| TRISA       | 0E00  | TRISA  | <15:14> | _      |             |            | TRISA< | 12:7> |       |        | _     | _     | TRISA4 | _      | _     | TRISA | <1:0>  | DF9F          |

| PORTA       | 0E02  | RA<1   | 5:14>   | _      |             |            | RA<12  | :7>   |       |        | _     | _     | RA4    | I      | _     | RA<   | 1:0>   | 0000          |

| LATA        | 0E04  | LATA<  | 15:14>  | _      |             | LATA<12:7> |        |       |       |        | ı     | 1     | LATA4  | ı      | 1     | LATA  | <1:0>  | 0000          |

| ODCA        | 0E06  | ODCA<  | <15:14> | _      |             |            | ODCA<  | 12:7> |       |        | _     | _     | ODCA4  | -      | -     | ODCA  | <1:0>  | 0000          |

| CNENA       | 0E08  | CNIEA  | <15:14> | _      |             |            | CNIEA< | 12:7> |       |        | _     | _     | CNIEA4 | I      | _     | CNIEA | ·<1:0> | 0000          |

| CNPUA       | 0E0A  | CNPUA  | <15:14> | _      |             |            | CNPUA< | 12:7> |       |        | ı     | 1     | CNPUA4 | ı      | 1     | CNPU  | A<1:0> | 0000          |

| CNPDA       | 0E0C  | CNPDA  | <15:14> | _      | CNPDA<12:7> |            |        | 1     | -     | CNPDA4 | I     |       | CNPD   | A<1:0> | 0000  |       |        |               |

| ANSELA      | 0E0E  | ANSA<  | :15:14> | _      | ANSA<       | 12:11>     | _      | ANSA9 | _     | _      | _     | _     | ANSA4  | I      | _     | ANSA  | <1:0>  | 1813          |

dsPIC33EPXXXGM3XX/6XX/7XX

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-47: PORTA REGISTER MAP FOR dsPIC33EPXXXGM306/706 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11      | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | AII<br>Resets |

|-------------|-------|--------|--------|--------|--------|-------------|--------|-------|-------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISA       | 0E00  | _      | _      | _      |        |             | TRISA< | 12:7> |       |       | _     | _     | TRISA4 |       | _     | TRISA | ·<1:0> | DF9F          |

| PORTA       | 0E02  | _      | _      |        |        |             | RA<12  | 2:7>  |       |       | _     | _     | RA4    | _     | _     | RA<   | 1:0>   | 0000          |

| LATA        | 0E04  | _      | _      | 1      |        | LATA<12:    |        |       |       |       | 1     | _     | LATA4  | _     | _     | LATA  | <1:0>  | 0000          |

| ODCA        | 0E06  | 1      | _      | 1      |        |             | ODCA<  | 12:7> |       |       | _     | _     | ODCA4  | _     | _     | ODCA  | <1:0>  | 0000          |

| CNENA       | 0E08  | _      | _      |        |        |             | CNIEA< | 12:7> |       |       | _     | _     | CNIEA4 | _     | _     | CNIEA | \<1:0> | 0000          |

| CNPUA       | 0E0A  | -      | _      | 1      |        |             | CNPUA< | 12:7> |       |       | 1     | _     | CNPUA4 | -     | _     | CNPU  | A<1:0> | 0000          |

| CNPDA       | 0E0C  |        | _      | I      |        | CNPDA<12:7> |        |       |       |       | 1     | _     | CNPDA4 | _     | _     | CNPD  | A<1:0> | 0000          |

| ANSELA      | 0E0E  | _      | _      |        | ANSA<  | 12:11>      | _      | ANSA9 | _     |       | _     | _     | ANSA4  | _     | _     | ANSA  | <1:0>  | 1813          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-48: PORTA REGISTER MAP FOR dsPIC33EPXXXGM304/604 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10                       | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3     | Bit 2     | Bit 1     | Bit 0 | AII<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|------------------------------|-------|--------|-------|-------|-------|------------|-----------|-----------|-----------|-------|---------------|

| TRISA       | 0E00  | _      | _      |        | _      | _      |                              | TRISA | <10:7> |       | _     | _     | TRISA<4:0> |           | DF9F      |           |       |               |

| PORTA       | 0E02  | _      | _      | 1      | _      | _      |                              | RA<1  | 0:7>   |       | _     | _     |            | RA<4:0>   |           |           |       | 0000          |

| LATA        | 0E04  | _      | _      |        | _      | _      |                              | LATA< | 10:7>  |       | _     | _     |            | LATA<4:0> |           |           | 0000  |               |

| ODCA        | 0E06  | -      | _      | 1      | -      | 1      |                              | ODCA< | <10:7> |       | 1     | -     |            | (         | ODCA<4:0  | >         |       | 0000          |

| CNENA       | 0E08  | _      | _      | I      |        | I      |                              | CNIEA | <10:7> |       | 1     |       |            | (         | CNIEA<4:0 | >         |       | 0000          |

| CNPUA       | 0E0A  | _      | _      | I      |        | -      |                              | CNPUA | <10:7> |       | -     |       |            | C         | NPUA<4:0  | >         |       | 0000          |

| CNPDA       | 0E0C  | -      | _      | 1      | -      | 1      | - CNPDA<10:7> — — CNPDA<4:0> |       | 0000   |       |       |       |            |           |           |           |       |               |

| ANSELA      | 0E0E  | _      | _      | 1      | _      | _      | _                            | ANSA9 | _      | _     | _     | _     | ANSA4      | _         | ,         | ANSA<2:0> | >     | 1813          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-52: PORTC REGISTER MAP FOR dsPIC33EPXXXGM310/710 DEVICES

| SFR<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13 | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|---------|--------|--------|--------|-----------|--------|-------|-------|---------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISC       | 0E20  | TRISC15 | -      |        |        |           |        |       |       | TRISC<1 | 3:0>  |       |       |       |       |       |       | BFFF          |

| PORTC       | 0E22  | RC15    | -      |        |        |           |        |       |       | RC<13:  | 0>    |       |       |       |       |       |       | xxxx          |

| LATC        | 0E24  | LATC15  | _      |        |        |           |        |       |       | LATC<13 | 3:0>  |       |       |       |       |       |       | xxxx          |

| ODCC        | 0E26  | ODCC15  | _      |        |        |           |        |       |       | ODCC<1  | 3:0>  |       |       |       |       |       |       | 0000          |

| CNENC       | 0E28  | CNIEC15 | _      |        |        |           |        |       |       | CNIEC<1 | 3:0>  |       |       |       |       |       |       | 0000          |

| CNPUC       | 0E2A  | CNPUC15 | _      |        |        |           |        |       |       | CNPUC<1 | 3:0>  |       |       |       |       |       |       | 0000          |

| CNPDC       | 0E2C  | CNPDC15 | _      |        |        |           |        |       |       | CNPDC<1 | 3:0>  |       |       |       |       |       |       | 0000          |

| ANSELC      | 0E2E  |         | _      | -      | A      | NSC<12:10 | >      | _     | _     | -       | _     |       |       | ANSC  | <5:0> |       |       | 0807          |

dsPIC33EPXXXGM3XX/6XX/7XX

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-53: PORTC REGISTER MAP FOR dsPIC33EPXXXGM306/706 DEVICES

| SFR<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13         | Bit 12        | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | AII<br>Resets |

|-------------|-------|---------|--------|----------------|---------------|--------|--------|-------|-------|---------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISC       | 0E20  | TRISC15 | _      |                |               |        |        |       |       | TRISC<1 | 3:0>  |       |       |       |       |       |       | BFFF          |

| PORTC       | 0E22  | RC15    | _      |                |               |        |        |       |       | RC<13:  | 0>    |       |       |       |       |       |       | xxxx          |

| LATC        | 0E24  | LATC15  |        |                | LATC<13:0> xx |        |        |       |       |         |       |       |       |       | xxxx  |       |       |               |

| ODCC        | 0E26  | ODCC15  |        |                |               |        |        |       |       | ODCC<1  | 3:0>  |       |       |       |       |       |       | 0000          |

| CNENC       | 0E28  | CNIEC15 |        |                |               |        |        |       |       | CNIEC<1 | 3:0>  |       |       |       |       |       |       | 0000          |

| CNPUC       | 0E2A  | CNPUC15 |        |                |               |        |        |       |       | CNPUC<1 | 3:0>  |       |       |       |       |       |       | 0000          |

| CNPDC       | 0E2C  | CNPDC15 |        | CNPDC<13:0> 00 |               |        |        |       |       |         |       |       | 0000  |       |       |       |       |               |

| ANSELC      | 0E2E  | 1       | _      | _              |               |        |        | _     | _     | _       | _     |       | •     | ANSC  | <5:0> |       | •     | 0807          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-54: PORTC REGISTER MAP FOR dsPIC33EPXXXGM304/604 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-----------|-------|-------|-------|-------|--------|-------|-------|-------|-------|---------------|

| TRISC       | 0E20  | _      | _      | 1      | _      | _      |        |           |       |       |       | TRISC | C<9:0> |       |       |       |       | BFFF          |

| PORTC       | 0E22  | _      | _      | -      | _      | _      | -      |           |       |       |       | RC<   | 9:0>   |       |       |       |       | xxxx          |

| LATC        | 0E24  | _      | _      | -      | _      | _      | -      | 1170.00   |       |       |       |       |        |       |       | xxxx  |       |               |

| ODCC        | 0E26  | _      | _      | -      | _      | _      | -      |           |       |       |       | ODC   | C<9:0> |       |       |       |       | 0000          |

| CNENC       | 0E28  | _      | _      | -      | _      | _      | -      |           |       |       |       | CNIE  | C<9:0> |       |       |       |       | 0000          |

| CNPUC       | 0E2A  | _      | _      | -      | _      | _      | -      |           |       |       |       | CNPU  | C<9:0> |       |       |       |       | 0000          |

| CNPDC       | 0E2C  |        | _      | 1      | _      | -      | -      | CNPDC<9   |       |       |       |       |        |       | 0000  |       |       |               |

| ANSELC      | 0E2E  | _      | _      | _      | _      | _      | _      | ANSC<5:0> |       |       |       |       |        |       |       | 0807  |       |               |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/C-0 | R/C-0 | R-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-----|-------|

| OA     | OB    | SA    | SB    | OAB   | SAB   | DA  | DC    |

| bit 15 |       |       |       |       |       |     | bit 8 |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|-----|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA  | N     | OV    | Z     | С     |

| bit 7                |                      |                      |     |       |       |       | bit 0 |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-5 **IPL<2:0>:** CPU Interrupt Priority Level Status bits<sup>(2,3)</sup>

111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled

110 = CPU Interrupt Priority Level is 6 (14)

101 = CPU Interrupt Priority Level is 5 (13)

100 = CPU Interrupt Priority Level is 4 (12)

011 = CPU Interrupt Priority Level is 3 (11)

010 = CPU Interrupt Priority Level is 2 (10)

001 = CPU Interrupt Priority Level is 1 (9)

000 = CPU Interrupt Priority Level is 0 (8)

Note 1: For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

#### **REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2**

| R/W-1  | R/W-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-------|--------|-----|-----|-----|-----|-------|

| GIE    | DISI  | SWTRAP | _   | _   | _   | _   | _     |

| bit 15 | •     |        |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|--------|--------|--------|

| _     | _   | _   | _   | _   | INT2EP | INT1EP | INT0EP |

| bit 7 |     |     |     |     |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 GIE: Global Interrupt Enable bit

1 = Interrupts and associated IECx bits are enabled

0 = Interrupts are disabled, but traps are still enabled

bit 14 DISI: DISI Instruction Status bit

> 1 = DISI instruction is active 0 = DISI instruction is not active

bit 13 **SWTRAP:** Software Trap Status bit

1 = Software trap is enabled

0 = Software trap is disabled

bit 12-3 Unimplemented: Read as '0'

bit 2 INT2EP: External Interrupt 2 Edge Detect Polarity Select bit

1 = Interrupt on negative edge

0 = Interrupt on positive edge

bit 1 INT1EP: External Interrupt 1 Edge Detect Polarity Select bit

> 1 = Interrupt on negative edge 0 = Interrupt on positive edge

bit 0 INTOEP: External Interrupt 0 Edge Detect Polarity Select bit

1 = Interrupt on negative edge

0 = Interrupt on positive edge

#### REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R-1 | R-1  | R-1    | R-1   |

|-------|-----|-----|-----|-----|------|--------|-------|

| _     | _   | _   | _   |     | LSTC | H<3:0> |       |

| bit 7 |     |     |     |     |      |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-4 Unimplemented: Read as '0'

bit 3-0 LSTCH<3:0>: Last DMA Controller Channel Active Status bits

1111 = No DMA transfer has occurred since system Reset

1110 = Reserved

•

0100 = Reserved

0011 = Last data transfer was handled by Channel 3

0010 = Last data transfer was handled by Channel 2

0001 = Last data transfer was handled by Channel 1

0000 = Last data transfer was handled by Channel 0

#### 11.4.4 INPUT MAPPING

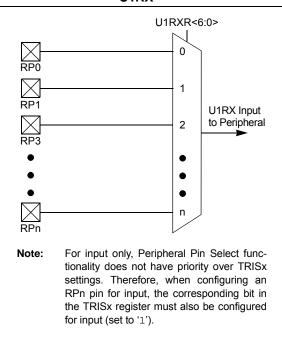

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-29). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

# FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.4.4.1 Virtual Connections

dsPIC33EPXXXGM3XX/6XX/7XX devices support virtual (internal) connections to the output of the op amp/comparator module (see Figure 26-1 in Section 26.0 "Op Amp/Comparator Module") and the PTG module (see Section 25.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXGM3XX/6XX/7XX devices support virtual connections to the filtered QEIx module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module").

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of `b00000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEIx module allows peripherals to be connected to the QEIx digital filter input. To utilize this filter, the QEIx module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEIx digital filter

#### EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43

```

RPINR15 = 0x2500; /* Connect the QEI1 HOME1 input to RP37 (pin 43) */

RPINR7 = 0x009; /* Connect the IC1 input to the digital filter on the FHOME1 input */

QEI1IOC = 0x4000; /* Enable the QEI digital filter */

QEI1CON = 0x8000; /* Enable the QEI module */

```

#### REGISTER 11-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-----------|-------|-------|-------|

| _      |       |       |       | IC2R<6:0> |       |       |       |

| bit 15 |       |       |       |           |       |       | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-----------|-------|-------|-------|

| _     |       |       |       | IC1R<6:0> |       |       |       |

| bit 7 |       |       |       |           |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 IC2R<6:0>: Assign Input Capture 2 (IC2) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111100 = Input tied to RPI124

•

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7 **Unimplemented:** Read as '0'

bit 6-0 IC1R<6:0>: Assign Input Capture 1 (IC1) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111100 = Input tied to RPI124

•

•

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

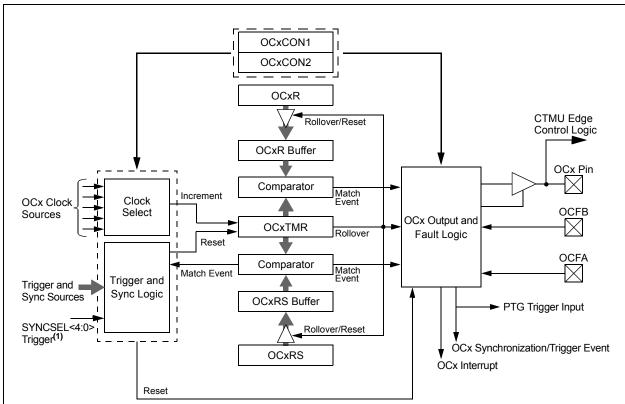

#### 15.0 OUTPUT COMPARE

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24EFamily Reference Manual", "Output Compare" (DS70005157), which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The output compare module can select one of eight available clock sources for its time base. The module compares the value of the timer with the value of one or two Compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Note: See the "dsPIC33/PIC24 Family Reference Manual", "Output Compare" (DS70005157) for OCxR and OCxRS register restrictions.

#### FIGURE 15-1: OUTPUT COMPARE x MODULE BLOCK DIAGRAM

**Note 1:** The Trigger/Sync source is enabled by default and is set to Timer2 as a source. This timer must be enabled for proper OCx module operation or the Trigger/Sync source must be changed to another source option.

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

```

bit 6-4

SYNCSRC<2:0>: Synchronous Source Selection bits<sup>(1)</sup>

111 = Reserved

100 = Reserved

011 = PTG017<sup>(2)</sup>

010 = PTG016<sup>(2)</sup>

001 = Reserved

000 = SYNCI1

bit 3-0

SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits<sup>(1)</sup>

1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event

0001 = 1:2 Postscaler generates Special Event Trigger on every second compare match event

0000 = 1:1 Postscaler generates Special Event Trigger on every compare match event

```

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

#### REGISTER 16-25: PWMCAPx: PWMx PRIMARY TIME BASE CAPTURE REGISTER

| R-0                            | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |

|--------------------------------|-----|-----|-----|-----|-----|-----|-------|--|

| PWMCAPx<15:8> <sup>(1,2)</sup> |     |     |     |     |     |     |       |  |

| bit 15                         |     |     |     |     |     |     | bit 8 |  |

| R-0                           | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |

|-------------------------------|-----|-----|-----|-----|-----|-----|-------|--|

| PWMCAPx<7:0> <sup>(1,2)</sup> |     |     |     |     |     |     |       |  |

| bit 7                         |     |     |     |     |     |     | bit 0 |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PWMCAPx<15:0>:** PWMx Captured Time Base Value bits<sup>(1,2)</sup>

The value in this register represents the captured PWMx time base value when a leading edge is detected on the current-limit input.

- **Note 1:** The capture feature is only available on a primary output (PWMxH).

- 2: This feature is active only after LEB processing on the current-limit input signal is complete.

#### REGISTER 21-6: CXINTF: CANX INTERRUPT FLAG REGISTER

| U-0    | U-0 | R-0  | R-0  | R-0  | R-0   | R-0   | R-0   |

|--------|-----|------|------|------|-------|-------|-------|

| _      | _   | TXBO | TXBP | RXBP | TXWAR | RXWAR | EWARN |

| bit 15 |     |      |      |      |       |       | bit 8 |

| R/C-0 | R/C-0 | R/C-0 | U-0 | R/C-0  | R/C-0  | R/C-0 | R/C-0 |

|-------|-------|-------|-----|--------|--------|-------|-------|

| IVRIF | WAKIF | ERRIF | _   | FIFOIF | RBOVIF | RBIF  | TBIF  |

| bit 7 |       |       |     |        |        |       | bit 0 |

Legend:C = Writable bit, but only '0' can be written to clear the bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

| bit 15-14 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 13    | TXBO: Transmitter in Error State Bus Off bit                                       |

|           | 1 = Transmitter is in Bus Off state                                                |

|           | 0 = Transmitter is not in Bus Off state                                            |

| bit 12    | TXBP: Transmitter in Error State Bus Passive bit                                   |

|           | 1 = Transmitter is in Bus Passive state                                            |

|           | 0 = Transmitter is not in Bus Passive state                                        |

| bit 11    | RXBP: Receiver in Error State Bus Passive bit                                      |

|           | 1 = Receiver is in Bus Passive state                                               |

|           | 0 = Receiver is not in Bus Passive state                                           |

| bit 10    | TXWAR: Transmitter in Error State Warning bit                                      |

|           | 1 = Transmitter is in Error Warning state                                          |

|           | 0 = Transmitter is not in Error Warning state                                      |

| bit 9     | RXWAR: Receiver in Error State Warning bit                                         |

|           | 1 = Receiver is in Error Warning state                                             |

|           | 0 = Receiver is not in Error Warning state                                         |

| bit 8     | <b>EWARN</b> : Transmitter or Receiver in Error State Warning bit                  |

|           | 1 = Transmitter or receiver is in Error Warning state                              |

| 1.11.7    | 0 = Transmitter or receiver is not in Error Warning state                          |

| bit 7     | IVRIF: Invalid Message Interrupt Flag bit                                          |

|           | 1 = Interrupt request has occurred                                                 |

| h:4 C     | 0 = Interrupt request has not occurred                                             |

| bit 6     | WAKIF: Bus Wake-up Activity Interrupt Flag bit                                     |

|           | 1 = Interrupt request has occurred 0 = Interrupt request has not occurred          |

| bit 5     | ·                                                                                  |

| DIL 5     | <b>ERRIF:</b> Error Interrupt Flag bit (multiple sources in CxINTF<13:8> register) |

|           | 1 = Interrupt request has occurred 0 = Interrupt request has not occurred          |

| bit 4     | Unimplemented: Read as '0'                                                         |

| bit 4     | FIFOIF: FIFO Almost Full Interrupt Flag bit                                        |

| DIL 3     | . •                                                                                |

|           | 1 = Interrupt request has occurred 0 = Interrupt request has not occurred          |

| bit 2     | RBOVIF: RX Buffer Overflow Interrupt Flag bit                                      |

| DIL Z     |                                                                                    |

|           | 1 = Interrupt request has occurred 0 = Interrupt request has not occurred          |

|           | o – interrupt request rias not occurred                                            |

#### REGISTER 21-18: CxFMSKSEL1: CANx FILTERS 7-0 MASK SELECTION REGISTER 1

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| F7MSK1 | F7MSK0 | F6MSK1 | F6MSK0 | F5MSK1 | F5MSK0 | F4MSK1 | F4MSK0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| F3MSK1 | F3MSK0 | F2MSK1 | F2MSK0 | F1MSK1 | F1MSK0 | F0MSK1 | F0MSK0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

bit 1-0

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **F7MSK<1:0>:** Mask Source for Filter 7 bit

11 = Reserved

10 = Acceptance Mask 2 registers contain mask

01 = Acceptance Mask 1 registers contain mask

bit 13-12

F6MSK<1:0>: Mask Source for Filter 6 bit (same values as bits 15-14)

F5MSK<1:0>: Mask Source for Filter 5 bit (same values as bits 15-14)

F5MSK<1:0>: Mask Source for Filter 5 bit (same values as bits 15-14)

F4MSK<1:0>: Mask Source for Filter 4 bit (same values as bits 15-14)

F3MSK<1:0>: Mask Source for Filter 3 bit (same values as bits 15-14)

F2MSK<1:0>: Mask Source for Filter 2 bit (same values as bits 15-14)

F1MSK<1:0>: Mask Source for Filter 1 bit (same values as bits 15-14)

F0MSK<1:0>: Mask Source for Filter 0 bit (same values as bits 15-14)

#### REGISTER 23-6: ADxCHS0: ADCx INPUT CHANNEL 0 SELECT REGISTER<sup>(3)</sup> (CONTINUED)

```

bit 7

CHONA: Channel 0 Negative Input Select for Sample MUXA bit

1 = Channel 0 negative input is AN1<sup>(1)</sup>

0 = Channel 0 negative input is VREFL

bit 6

Unimplemented: Read as '0'

CH0SA<5:0>: Channel 0 Positive Input Select for Sample MUXA bits(1,4,5)

bit 5-0

111111 = Channel 0 positive input is (AN63) unconnected

111110 = Channel 0 positive input is (AN62) the CTMU temperature voltage

111101 = Channel 0 positive input is (AN61) reserved

110010 = Channel 0 positive input is (AN50) reserved

110001 = Channel 0 positive input is AN49

110000 = Channel 0 positive input is AN48

101111 = Channel 0 positive input is AN47

101110 = Channel 0 positive input is AN46

011010 = Channel 0 positive input is AN26

011001 = Channel 0 positive input is AN25 or Op Amp 5 output voltage<sup>(2)</sup>

011000 = Channel 0 positive input is AN24

000111 = Channel 0 positive input is AN7

000110 = Channel 0 positive input is AN6 or Op Amp 3 output voltage<sup>(2)</sup>

000101 = Channel 0 positive input is AN5

000100 = Channel 0 positive input is AN4

000011 = Channel 0 positive input is AN3 or Op Amp 1 output voltage<sup>(2)</sup>

000010 = Channel 0 positive input is AN2

000001 = Channel 0 positive input is AN1

000000 = Channel 0 positive input is AN0 or Op Amp 2 output voltage<sup>(2)</sup>

```

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality are enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: If the op amp is selected (OPMODE bit (CMxCON<10>) = 1), the OAx input is used; otherwise, the ANx input is used.

- 3: See the "Pin Diagrams" section for the available analog channels for each device.

- **4:** Analog input selections for ADC1 are shown here. AN32-AN63 selections are not available for ADC2. The CH0SB5 and CH0SA5 bits are 'Reserved' for ADC2 and should be programmed to '0'.

- 5: Analog inputs, AN32-AN49, are available only when the ADCx is working in 10-bit mode.

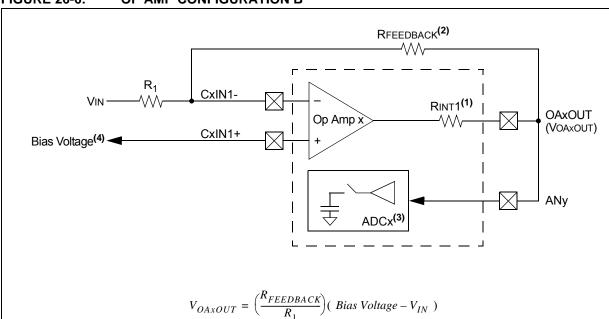

#### 26.1.2 OP AMP CONFIGURATION B

Figure 26-6 shows a typical inverting amplifier circuit with the output of the op amp (OAxOUT) externally routed to a separate analog input pin (ANy) on the device. This op amp configuration is slightly different in terms of the op amp output and the ADCx input connection, therefore, RINT1 is not included in the transfer function. However, this configuration requires the designer to externally route the op amp output (OAxOUT) to another analog input pin (ANy). See Table 33-52 in Section 33.0 "Electrical Characteristics" for the typical value of RINT1. Table 33-57 and Table 33-58 in Section 33.0 "Electrical Characteristics" describe the minimum sample time (TSAMP) requirements for the ADCx module in this configuration.

Figure 26-6 also defines the equation to be used to calculate the expected voltage at point, VOAXOUT. This is the typical inverting amplifier equation.

#### 26.2 Op Amp/Comparator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/

Devices.aspx?dDocName=en555464

#### 26.2.1 KEY RESOURCES

- "Op Amp/Comparator" (DS70000357) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

FIGURE 26-6: OP AMP CONFIGURATION B

Note 1: See Table 33-56 for the Typical value.

2: See Table 33-52 for the Minimum value for the feedback resistor.

3: See Table 33-59 and Table 33-60 for the Minimum Sample Time (TSAMP).

4: CVREF10 or CVREF20 are two options that are available for supplying bias voltage to the op amps.

TABLE 31-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |                    | Assembly Syntax            | Description                                                 | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------------------|----------------------------|-------------------------------------------------------------|---------------|----------------|--------------------------|

| 8 BSW              |                      | BSW.C Ws,Wb Write( |                            | Write C bit to Ws <wb></wb>                                 | 1             | 1              | None                     |

|                    |                      | BSW.Z              | Ws,Wb                      | Write Z bit to Ws <wb></wb>                                 | 1             | 1              | None                     |

| 9                  | BTG                  | BTG                | f,#bit4                    | Bit Toggle f                                                | 1             | 1              | None                     |

|                    |                      | BTG                | Ws,#bit4                   | Bit Toggle Ws                                               | 1             | 1              | None                     |

| 10                 | BTSC                 | BTSC               | f,#bit4                    | Bit Test f, Skip if Clear                                   | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSC               | Ws,#bit4                   | Bit Test Ws, Skip if Clear                                  | 1             | 1<br>(2 or 3)  | None                     |

| 11                 | BTSS                 | BTSS               | f,#bit4                    | Bit Test f, Skip if Set                                     | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSS               | Ws,#bit4                   | Bit Test Ws, Skip if Set                                    | 1             | 1<br>(2 or 3)  | None                     |

| 12                 | BTST                 | BTST               | f,#bit4                    | Bit Test f                                                  | 1             | 1              | Z                        |

|                    |                      | BTST.C             | Ws,#bit4                   | Bit Test Ws to C                                            | 1             | 1              | С                        |

|                    |                      | BTST.Z             | Ws,#bit4                   | Bit Test Ws to Z                                            | 1             | 1              | Z                        |

|                    |                      | BTST.C             | Ws,Wb                      | Bit Test Ws <wb> to C</wb>                                  | 1             | 1              | С                        |

|                    |                      | BTST.Z             | Ws,Wb                      | Bit Test Ws <wb> to Z</wb>                                  | 1             | 1              | Z                        |

| 13                 | BTSTS                | BTSTS              | f,#bit4                    | Bit Test then Set f                                         | 1             | 1              | Z                        |

|                    |                      | BTSTS.C            | Ws,#bit4                   | Bit Test Ws to C, then Set                                  | 1             | 1              | С                        |

|                    |                      | BTSTS.Z            | Ws,#bit4                   | Bit Test Ws to Z, then Set                                  | 1             | 1              | Z                        |

| 14                 | CALL                 | CALL               | lit23                      | Call subroutine                                             | 2             | 4              | SFA                      |

|                    |                      | CALL               | Wn                         | Call indirect subroutine                                    | 1             | 4              | SFA                      |

|                    |                      | CALL.L             | Wn                         | Call indirect subroutine (long address)                     | 1             | 4              | SFA                      |

| 15                 | CLR                  | CLR                | f                          | f = 0x0000                                                  | 1             | 1              | None                     |

|                    |                      | CLR                | WREG                       | WREG = 0x0000                                               | 1             | 1              | None                     |

|                    |                      | CLR                | Ws                         | Ws = 0x0000                                                 | 1             | 1              | None                     |

|                    |                      | CLR                | Acc, Wx, Wxd, Wy, Wyd, AWB | Clear Accumulator                                           | 1             | 1              | OA,OB,SA,<br>SB          |

| 16                 | CLRWDT               | CLRWDT             |                            | Clear Watchdog Timer                                        | 1             | 1              | WDTO,Sleep               |

| 17                 | COM                  | COM                | f                          | $f = \overline{f}$                                          | 1             | 1              | N,Z                      |

| 17                 |                      | COM                | f,WREG                     | WREG = $\overline{f}$                                       | 1             | 1              | N,Z                      |

|                    |                      | COM                | Ws, Wd                     | $Wd = \overline{Ws}$                                        | 1             | 1              | N,Z                      |

| 18                 | CP                   | CP                 | f                          | Compare f with WREG                                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP                 | Wb,#lit8                   | Compare Wb with lit8                                        | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP                 | Wb,Ws                      | Compare Wb with Ws (Wb – Ws)                                | 1             | 1              | C,DC,N,OV,Z              |

| 19                 | CP0                  | CP0                | f                          | Compare f with 0x0000                                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP0                | Ws                         | Compare Ws with 0x0000                                      | 1             | 1              | C,DC,N,OV,Z              |

| 20                 | CPB                  | CPB                | f                          | Compare f with WREG, with Borrow                            | 1             | 1              | C,DC,N,OV,Z              |

| 20                 |                      | CPB                | Wb,#lit8                   | Compare Wb with lit8, with Borrow                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB                | Wb,Ws                      | Compare Wb with Ws, with Borrow (Wb – Ws – $\overline{C}$ ) | 1             | 1              | C,DC,N,OV,Z              |

| 21                 | CPSEQ                | CPSEQ              | Wb,Wn                      | Compare Wb with Wn, skip if =                               | 1             | 1<br>(2 or 3)  | None                     |

|                    | CPBEQ                | CPBEQ              | Wb,Wn,Expr                 | Compare Wb with Wn, branch if =                             | 1             | 1 (5)          | None                     |

| 22                 | CPSGT                | CPSGT              | Wb,Wn                      | Compare Wb with Wn, skip if >                               | 1             | 1<br>(2 or 3)  | None                     |

|                    | CPBGT                | CPBGT              | Wb,Wn,Expr                 | Compare Wb with Wn, branch if >                             | 1             | 1 (5)          | None                     |

| 23                 | CPSLT                | CPSLT              | Wb,Wn                      | Compare Wb with Wn, skip if <                               | 1             | 1<br>(2 or 3)  | None                     |

|                    | CPBLT                | CPBLT              | Wb,Wn,Expr                 | Compare Wb with Wn, branch if <                             | 1             | 1 (5)          | None                     |

| 24                 | CPSNE                | CPSNE              | Wb,Wn                      | Compare Wb with Wn, skip if ≠                               | 1             | 1<br>(2 or 3)  | None                     |

|                    | CPBNE                | CPBNE              | Wb,Wn,Expr                 | Compare Wb with Wn, branch if ≠                             | 1             | 1 (5)          | None                     |

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

# 32.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM™ and dsPICDEM™ demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELoq® security ICs, CAN, IrDA®, PowerSmart battery management, SEEVAL® evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 32.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

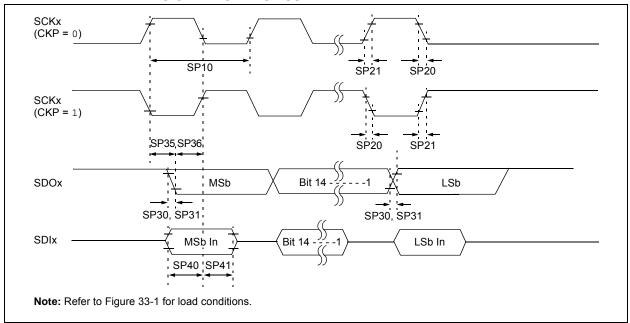

FIGURE 33-18: SPI2 AND SPI3 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

TABLE 33-35: SPI2 AND SPI3 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                     |      |       |                             |

|--------------------|-----------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>              | Min.                                                                                                                                                                                                                                             | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP10               | FscP                  | Maximum SCKx Frequency                     |                                                                                                                                                                                                                                                  |                     | 9    | MHz   | -40°C to +125°C<br>(Note 3) |

| SP20               | TscF                  | SCKx Output Fall Time                      | 1                                                                                                                                                                                                                                                |                     | _    | ns    | See Parameter DO32 (Note 4) |

| SP21               | TscR                  | SCKx Output Rise Time                      | -                                                                                                                                                                                                                                                |                     | _    | ns    | See Parameter DO31 (Note 4) |

| SP30               | TdoF                  | SDOx Data Output Fall Time                 |                                                                                                                                                                                                                                                  | _                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP31               | TdoR                  | SDOx Data Output Rise Time                 | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge     | _                                                                                                                                                                                                                                                | 6                   | 20   | ns    |                             |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to First SCKx Edge  | 30                                                                                                                                                                                                                                               |                     | _    | ns    |                             |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge  | 30                                                                                                                                                                                                                                               |                     | _    | ns    |                             |

- **Note 1:** These parameters are characterized, but are not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

TABLE 33-60: ADCx CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | Standard Operating Conditions (see Note 1): 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |           |                     |       |       |                                   |  |  |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------|-------|-------|-----------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                                                | Min.      | Typ. <sup>(4)</sup> | Max.  | Units | Conditions                        |  |  |

| Clock Parameters   |        |                                                                                                                                                                                                                                                               |           |                     |       |       |                                   |  |  |

| AD50               | TAD    | ADCx Clock Period                                                                                                                                                                                                                                             | 75        | _                   | _     | ns    |                                   |  |  |

| AD51               | trc    | ADCx Internal RC Oscillator Period                                                                                                                                                                                                                            | _         | 250                 | _     | ns    |                                   |  |  |

|                    |        | Con                                                                                                                                                                                                                                                           | version F | Rate                |       |       |                                   |  |  |

| AD55               | tconv  | Conversion Time                                                                                                                                                                                                                                               | _         | 12 TAD              | _     | _     |                                   |  |  |

| AD56               | FCNV   | Throughput Rate                                                                                                                                                                                                                                               | _         | _                   | 1.1   | Msps  | Using simultaneous sampling       |  |  |

| AD57a              | Тѕамр  | Sample Time When Sampling Any ANx Input                                                                                                                                                                                                                       | 2 TAD     | _                   | _     | _     |                                   |  |  |

| AD57b              | Тѕамр  | Sample Time When Sampling the Op Amp Outputs                                                                                                                                                                                                                  | 4 TAD     | _                   | _     | _     |                                   |  |  |

|                    |        | Timin                                                                                                                                                                                                                                                         | g Param   | eters               |       |       |                                   |  |  |

| AD60               | tPCS   | Conversion Start from Sample Trigger <sup>(2)</sup>                                                                                                                                                                                                           | 2 TAD     | _                   | 3 TAD | _     | Auto-convert trigger not selected |  |  |

| AD61               | tpss   | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2)</sup>                                                                                                                                                                                                 | 2 TAD     |                     | 3 TAD |       |                                   |  |  |

| AD62               | tcss   | Conversion Completion to Sample Start (ASAM = 1) <sup>(2)</sup>                                                                                                                                                                                               | _         | 0.5 TAD             | _     | _     |                                   |  |  |

| AD63               | tDPU   | Time to Stabilize Analog Stage from ADC Off to ADC On <sup>(2)</sup>                                                                                                                                                                                          | _         | _                   | 20    | μS    | (Note 3)                          |  |  |

- Note 1: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 33-12 for the minimum and maximum BOR values.

- 2: Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

- 3: The parameter, tDPU, is the time required for the ADCx module to stabilize at the appropriate level when the module is turned on (AD1CON1<ADON> = 1). During this time, the ADCx result is indeterminate.

- 4: These parameters are characterized, but not tested in manufacturing.

| F                                                      |     | Reset Sequence                                                             | 1  | 15 |

|--------------------------------------------------------|-----|----------------------------------------------------------------------------|----|----|

| Flash Program Memory                                   | 103 | Interrupt Vector                                                           |    |    |

| Control Registers                                      |     | Details (table)                                                            |    |    |

| Operations                                             |     | Interrupt Vector Table (IVT)                                               |    |    |

| RTSP Operation                                         |     | Interrupt Vector Table (table)                                             | 11 | 16 |

| Table Instructions                                     |     | J                                                                          |    |    |

| Flexible Configuration                                 |     | -                                                                          | 4. |    |

| _                                                      |     | JTAG Boundary Scan Interface                                               |    |    |

| G                                                      |     | JTAG Interface                                                             | 4  | 16 |

| Getting Started with 16-Bit DSCs                       | 21  | M                                                                          |    |    |

| Connection Requirements                                |     | Memory Maps                                                                |    |    |

| CPU Logic Filter Capacitor Connection (VCAP)           |     | EDS                                                                        | (  | 94 |

| Decoupling Capacitors                                  |     | Memory Organization                                                        |    |    |

| External Oscillator Pins                               |     | Microchip Internet Web Site                                                |    |    |

| ICSP Pins                                              |     | Modulo Addressing                                                          |    |    |

| Master Clear (MCLR) Pin                                |     | Applicability                                                              |    |    |

| Oscillator Value Conditions on Device Start-up         |     | Operation Example                                                          |    |    |

| Unused I/Os                                            | 24  | Start and End Address                                                      |    |    |

| Н                                                      |     | W Address Register Selection                                               | 9  | 98 |

| High-Speed PWM                                         | 220 | MPLAB Assembler, Linker, Librarian                                         | 43 | 30 |

| Control Registers                                      |     | MPLAB ICD 3 In-Circuit Debugger                                            | 43 | 31 |

| Faults                                                 |     | MPLAB PM3 Device Programmer                                                | 43 | 31 |

| High-Temperature Electrical Characteristics            |     | MPLAB REAL ICE In-Circuit Emulator System                                  | 43 | 31 |

| Absolute Maximum Ratings                               |     | MPLAB X Integrated Development                                             |    |    |

| High-Voltage Detect (HVD)                              |     | Environment Software                                                       |    |    |

| _                                                      |     | MPLAB X SIM Software Simulator                                             |    |    |

| 1                                                      |     | MPLIB Object Librarian                                                     |    |    |

| I/O Ports                                              | 163 | MPLINK Object Linker                                                       | 43 | 30 |

| Configuring Analog/Digital Port Pins                   | 164 | 0                                                                          |    |    |

| Helpful Tips                                           | 173 |                                                                            |    |    |

| Open-Drain Configuration                               | 164 | Op Amp                                                                     | 24 | ۰, |

| Parallel I/O (PIO)                                     | 163 | Application Considerations                                                 |    |    |

| Write/Read Timing                                      | 164 | Configuration A  Configuration B                                           |    |    |

| In-Circuit Debugger                                    | 418 | Op Amp/Comparator                                                          |    |    |

| In-Circuit Emulation                                   |     | Control Registers                                                          |    |    |

| In-Circuit Serial Programming (ICSP)411,               |     | Resources                                                                  |    |    |

| Input Capture                                          |     | Oscillator Configuration                                                   |    |    |

| Control Registers                                      |     | CPU Clocking System                                                        |    |    |

| Input Change Notification (ICN)                        |     | Output Compare                                                             |    |    |

| Instruction Addressing Modes                           |     | Control Registers                                                          |    |    |

| File Register Instructions Fundamental Modes Supported |     |                                                                            |    |    |

| MAC Instructions                                       |     | Р                                                                          |    |    |

| MCU Instructions                                       |     | Packaging                                                                  | 50 | 07 |

| Move and Accumulator Instructions                      |     | Details                                                                    |    |    |

| Other Instructions                                     |     | Marking                                                                    |    |    |

| Instruction Set                                        | • . | Parallel Master Port (PMP)                                                 |    |    |

| Overview                                               | 422 | Peripheral Module Disable (PMD)                                            |    |    |

| Summary                                                | 419 | Peripheral Pin Select (PPS)                                                |    |    |

| Interfacing Program and Data Memory Spaces             |     | Input Sources, Maps Input to Function                                      |    |    |

| Inter-Integrated Circuit (I <sup>2</sup> C)            |     | Output Selection for Remappable Pins                                       |    |    |

| Control Registers                                      |     | Peripheral Trigger Generator (PTG) Module                                  |    |    |

| Internal LPRC Oscillator                               |     | PICkit 3 In-Circuit Debugger/Programmer<br>Pinout I/O Descriptions (table) |    |    |

| Use with WDT                                           | 417 | PMP                                                                        |    | IC |

| Internet Address                                       | 536 | Control Registers                                                          | 3( | ۵e |

| Interrupt Controller                                   |     | Power-Saving Features                                                      |    |    |

| Control and Status Registers                           |     | Clock Frequency and Switching                                              |    |    |

| IECx                                                   |     | Instruction-Based Modes                                                    |    |    |

| IFSx                                                   |     | Idle                                                                       |    |    |

| INTCON1                                                |     | Sleep                                                                      |    |    |

| INTCON2                                                |     | Interrupts Coincident with Power Save                                      |    | -  |

| INTCON3                                                |     | Instructions                                                               | 1  | 54 |

| INTCON4                                                |     | PPS                                                                        | •• |    |

| INTTREG                                                |     | Control Registers                                                          | 17 | 75 |

| IPCx                                                   | 1ZU | <del>-</del>                                                               |    |    |