Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betalls                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 35                                                                               |

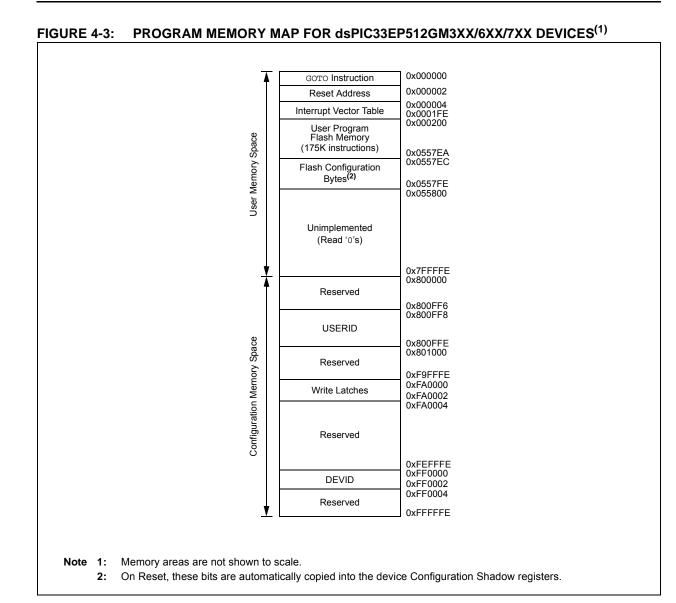

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 48K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8×8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gm604-i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: | <b>PINOUT I/O DESCRIPTIONS (</b> | CONTINUED) |

|------------|----------------------------------|------------|

|            |                                  |            |

| Pin Name                                      | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                                   |  |  |  |  |  |

|-----------------------------------------------|-------------|----------------|-----|-----------------------------------------------------------------------------------------------|--|--|--|--|--|

| PMA0                                          | I/O         | TTL/ST         | No  | Parallel Master Port Address Bit 0 input (Buffered Slave modes) and                           |  |  |  |  |  |

|                                               |             |                |     | output (Master modes).                                                                        |  |  |  |  |  |

| PMA1                                          | I/O         | TTL/ST         | No  | Parallel Master Port Address Bit 1 input (Buffered Slave modes) and                           |  |  |  |  |  |

| PMA2-PMA13                                    | ο           |                | No  | output (Master modes).<br>Parallel Master Port Address Bits 2-13 (Demultiplexed Master modes) |  |  |  |  |  |

| PMBE                                          | ŏ           |                | No  | Parallel Master Port Byte Enable strobe.                                                      |  |  |  |  |  |

| PMCS1, PMCS2                                  | ŏ           | _              | No  | Parallel Master Port Chip Select 1 and 2 strobe.                                              |  |  |  |  |  |

| PMD0-PMD7                                     | I/O         | TTL/ST         | No  | Parallel Master Port Data (Demultiplexed Master mode) or                                      |  |  |  |  |  |

|                                               |             |                |     | Address/Data (Multiplexed Master modes).                                                      |  |  |  |  |  |

| PMRD                                          | 0           |                | No  | Parallel Master Port Read strobe.                                                             |  |  |  |  |  |

| PMWR                                          | 0           | _              | No  | Parallel Master Port Write strobe.                                                            |  |  |  |  |  |

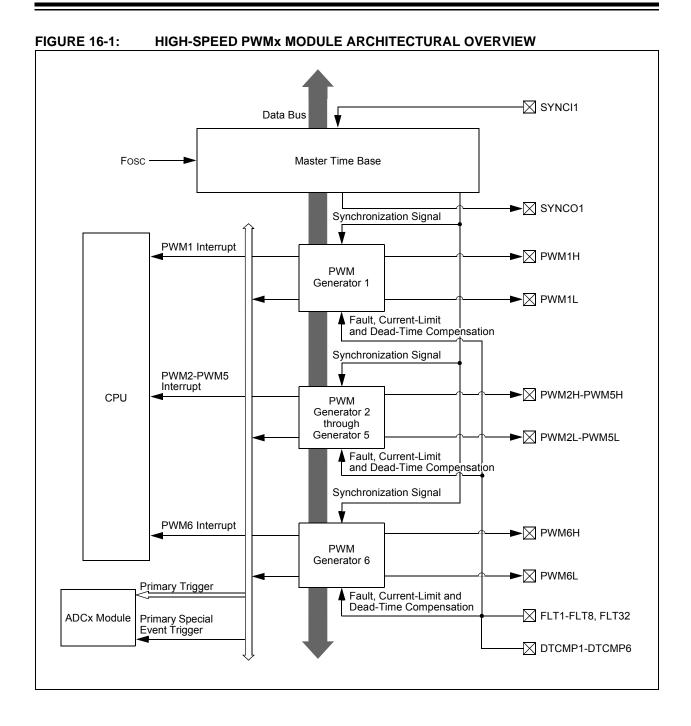

| FLT1-FLT2 <sup>(1)</sup>                      | I           | ST             | Yes | PWMx Fault Inputs 1 through 2.                                                                |  |  |  |  |  |

| FLT3-FLT8 <sup>(1)</sup>                      | I           | ST             | No  | PWMx Fault Inputs 3 through 8                                                                 |  |  |  |  |  |

| FLT32                                         | I           | ST             | No  | PWMx Fault Input 32                                                                           |  |  |  |  |  |

| DTCMP1-DTCMP6 <sup>(1)</sup>                  | I           | ST             | Yes | PWMx Dead-Time Compensation Inputs 1 through 6.                                               |  |  |  |  |  |

| PWM1L-PWM6L <sup>(1)</sup>                    | 0           | _              | No  | PWMx Low Outputs 1 through 7.                                                                 |  |  |  |  |  |

| PWM1H-PWM6H <sup>(1)</sup>                    | 0           | _              | No  | PWMx High Outputs 1 through 7.                                                                |  |  |  |  |  |

| SYNCI1 <sup>(1)</sup> , SYNCI2 <sup>(1)</sup> | I           | ST             | Yes | PWMx Synchronization Input 1.                                                                 |  |  |  |  |  |

| SYNCO1, SYNCO2 <sup>(1)</sup>                 | 0           | —              | Yes | , ,                                                                                           |  |  |  |  |  |

| PGED1                                         | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 1.                               |  |  |  |  |  |

| PGEC1                                         | I           | ST             | No  | Clock input pin for Programming/Debugging Communication Channel 1                             |  |  |  |  |  |

| PGED2                                         | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 2.                               |  |  |  |  |  |

| PGEC2                                         | I           | ST             | No  | Clock input pin for Programming/Debugging Communication Channel 2                             |  |  |  |  |  |

| PGED3                                         | I/O         | ST             | No  | Data I/O pin for Programming/Debugging Communication Channel 3.                               |  |  |  |  |  |

| PGEC3                                         | Ι           | ST             | No  | Clock input pin for Programming/Debugging Communication Channel 3                             |  |  |  |  |  |

| MCLR                                          | I/P         | ST             | No  | Master Clear (Reset) input. This pin is an active-low Reset to the device.                    |  |  |  |  |  |

| AVdd <sup>(2)</sup>                           | Р           | Р              | No  | Positive supply for analog modules. This pin must be connected at all times.                  |  |  |  |  |  |

| AVss                                          | Р           | Р              | No  | Ground reference for analog modules.                                                          |  |  |  |  |  |

| Vdd                                           | Р           | _              | No  | Positive supply for peripheral logic and I/O pins.                                            |  |  |  |  |  |

| VCAP                                          | Р           | —              | No  | CPU logic filter capacitor connection.                                                        |  |  |  |  |  |

| Vss                                           | Р           | _              | No  | Ground reference for logic and I/O pins.                                                      |  |  |  |  |  |

| VREF+                                         | I           | Analog         | No  | Analog voltage reference (high) input.                                                        |  |  |  |  |  |

| VREF-                                         | Ι           | Analog         | No  | Analog voltage reference (low) input.                                                         |  |  |  |  |  |

| Legend: CMOS = CM<br>ST = Schmit              |             |                |     |                                                                                               |  |  |  |  |  |

CMOS compatible input or output egena: ST = Schmitt Trigger input with CMOS levels O = Output PPS = Peripheral Pin Select TTL = TTL input buffer

Note 1: This pin is not available on all devices. For more information, see the "Pin Diagrams" section for pin availability.

2: AVDD must be connected at all times.

# **REGISTER 3-2:** CORCON: CORE CONTROL REGISTER<sup>(3)</sup> (CONTINUED)

| bit 3 | IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup><br>1 = CPU Interrupt Priority Level is greater than 7<br>0 = CPU Interrupt Priority Level is 7 or less                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | SFA: Stack Frame Active Status bit                                                                                                                                                                                |

|       | <ul> <li>1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and DSWPAG values</li> <li>0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space</li> </ul> |

| bit 1 | RND: Rounding Mode Select bit                                                                                                                                                                                     |

|       | <ul> <li>1 = Biased (conventional) rounding is enabled</li> <li>0 = Unbiased (convergent) rounding is enabled</li> </ul>                                                                                          |

| bit 0 | IF: Integer or Fractional Multiplier Mode Select bit                                                                                                                                                              |

|       | <ul><li>1 = Integer mode is enabled for DSP multiply</li><li>0 = Fractional mode is enabled for DSP multiply</li></ul>                                                                                            |

|       |                                                                                                                                                                                                                   |

- **Note 1:** This bit is always read as '0'.

- 2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

- 3: Refer to the "dsPIC33/PIC24 Family Reference Manual", "CPU" (DS70359) for more detailed information.

| IABLE 4     | 4-0:  | 00     | IPUIC                                              |          |         | SIER W  | AP      |       |            |             |               |        |          |          |          |          |          |               |

|-------------|-------|--------|----------------------------------------------------|----------|---------|---------|---------|-------|------------|-------------|---------------|--------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14                                             | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8      | Bit 7       | Bit 6         | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| OC1CON1     | 0900  | _      | —                                                  | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | ENFLTB     | ENFLTA      | —             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2     | 0902  | FLTMD  | FLTOUT                                             | FLTTRIEN | OCINV   | —       | _       | _     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS       | 0904  |        |                                                    |          |         |         |         | Ou    | Itput Comp | are 1 Seco  | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC1R        | 0906  |        |                                                    |          |         |         |         |       | Output     | Compare 7   | 1 Register    |        |          |          |          |          |          | xxxx          |

| OC1TMR      | 0908  |        | Output Compare 1 Timer Value Register         xxxx |          |         |         |         |       |            | xxxx        |               |        |          |          |          |          |          |               |

| OC2CON1     | 090A  | _      | —                                                  | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | ENFLTB     | ENFLTA      | -             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC2CON2     | 090C  | FLTMD  | FLTOUT                                             | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS       | 090E  |        |                                                    |          |         |         |         | Ou    | Itput Comp | are 2 Seco  | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC2R        | 0910  |        |                                                    |          |         |         |         |       | Output     | Compare 2   | 2 Register    |        |          |          |          |          |          | xxxx          |

| OC2TMR      | 0912  |        |                                                    |          |         |         | -       | Ou    | tput Comp  | are 2 Time  | r Value Regis | ster   |          | -        |          |          |          | xxxx          |

| OC3CON1     | 0914  | —      | _                                                  | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2     | 0916  | FLTMD  | FLTOUT                                             | FLTTRIEN | OCINV   | _       | —       | _     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS       | 0918  |        | Output Compare 3 Secondary Register xxxx           |          |         |         |         |       |            |             |               |        |          |          |          |          |          |               |

| OC3R        | 091A  |        | Output Compare 3 Register xxxx                     |          |         |         |         |       |            |             |               |        |          |          |          |          |          |               |

| OC3TMR      | 091C  |        |                                                    |          |         |         | -       | Ou    | tput Comp  | are 3 Time  | r Value Regis | ster   |          | -        |          |          |          | xxxx          |

| OC4CON1     | 091E  | —      | _                                                  | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC4CON2     | 0920  | FLTMD  | FLTOUT                                             | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC4RS       | 0922  |        |                                                    |          |         |         |         | Ou    | tput Comp  | oare 4 Seco | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC4R        | 0924  |        |                                                    |          |         |         |         |       | Output     | Compare 4   | 4 Register    |        |          |          |          |          |          | xxxx          |

| OC4TMR      | 0926  |        |                                                    |          |         |         |         | Ou    | tput Comp  | are 4 Time  | r Value Regis | ster   |          |          |          |          |          | xxxx          |

| OC5CON1     | 0928  |        | _                                                  | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC5CON2     | 092A  | FLTMD  | FLTOUT                                             | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC5RS       | 092C  |        |                                                    |          |         |         |         | Ou    | tput Comp  | are 5 Seco  | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC5R        | 092E  |        |                                                    |          |         |         |         |       | Output     | Compare &   | 5 Register    |        |          |          |          |          |          | xxxx          |

| OC5TMR      | 0930  |        |                                                    |          |         |         |         | Ou    | tput Comp  | are 5 Time  | r Value Regis | ster   |          |          |          |          |          | xxxx          |

| OC6CON1     | 0932  | —      | —                                                  | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | ENFLTB     | ENFLTA      | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC6CON2     | 0934  | FLTMD  | FLTOUT                                             | FLTTRIEN | OCINV   | —       | —       | —     | OC32       | OCTRIG      | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC6RS       | 0936  |        |                                                    |          |         |         |         | Ou    | <u> </u>   |             | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC6R        | 0938  |        |                                                    |          |         |         |         |       | Output     | Compare 6   | 6 Register    |        |          |          |          |          |          | xxxx          |

| OC6TMR      | 093A  |        |                                                    |          |         |         |         | Out   | tput Comp  | are 6 Time  | r Value Regis | ster   |          |          |          |          |          | xxxx          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4     | 4-33: | PERI   | PHERA                     | L PIN 3   | ELECI  | INPUT      | <b>KEGISI</b> |             | , FOK q | SPIC33      |             |       |           | ICE3       |          |       |       |               |

|-------------|-------|--------|---------------------------|-----------|--------|------------|---------------|-------------|---------|-------------|-------------|-------|-----------|------------|----------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14                    | Bit 13    | Bit 12 | Bit 11     | Bit 10        | Bit 9       | Bit 8   | Bit 7       | Bit 6       | Bit 5 | Bit 4     | Bit 3      | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| RPINR0      | 06A0  | _      |                           |           |        | INT1R<6:0> | >             |             |         | _           | —           | _     | _         | _          | _        | _     | _     | 0000          |

| RPINR1      | 06A2  | —      | —                         | _         | _      | —          | —             | _           | _       | —           |             |       |           | INT2R<6:0> | •        |       |       | 0000          |

| RPINR3      | 06A6  | _      | _                         | _         | _      | _          | _             | _           | _       | _           |             |       | -         | T2CKR<6:0  | >        |       |       | 0000          |

| RPINR7      | 06AE  | —      |                           |           |        | IC2R<6:0>  |               |             |         | —           |             |       |           | IC1R<6:0>  |          |       |       | 0000          |

| RPINR8      | 06B0  | _      | IC4R<6:0>                 |           |        |            |               |             | —       |             |             |       | IC3R<6:0> |            |          |       | 0000  |               |

| RPINR9      | 06B2  | _      |                           | IC6R<6:0> |        |            |               |             |         | _           |             |       |           | IC5R<6:0>  |          |       |       | 0000          |

| RPINR10     | 06B4  | _      |                           |           |        | IC8R<6:0>  |               | — IC7R<6:0> |         |             |             |       |           |            |          | 0000  |       |               |

| RPINR11     | 06B6  | —      | —                         | -         | —      | —          | _             |             | _       | —           |             |       | (         | OCFAR<6:0  | >        |       |       | 0000          |

| RPINR12     | 06B8  | _      |                           |           |        | FLT2R<6:0  | >             |             |         | _           |             |       |           | FLT1R<6:0> | >        |       |       | 0000          |

| RPINR14     | 06BC  | —      |                           |           |        | QEB1R<6:0  | >             |             |         | —           | QEA1R<6:0>  |       |           |            |          |       | 0000  |               |

| RPINR15     | 06BE  | —      | HOME1R<6:0> — INDX1R<6:0> |           |        |            |               |             |         | INDX1R<6:0> |             |       |           |            |          | 0000  |       |               |

| RPINR16     | 06C0  | —      | QEB2R<6:0> — QEA2R<6:0>   |           |        |            |               |             |         | QEA2R<6:0>  |             |       |           |            |          | 0000  |       |               |

| RPINR17     | 06C2  | —      |                           |           | н      | OME2R<6:   | 0>            |             |         | —           | INDX2R<6:0> |       |           |            |          | 0000  |       |               |

| RPINR18     | 06C4  | —      | —                         | _         | —      | —          | _             | —           | —       | —           | U1RXR<6:0>  |       |           |            |          | 0000  |       |               |

| RPINR19     | 06C6  | —      | —                         | _         | —      | —          | —             | —           | —       |             |             |       | I         | J2RXR<6:0  | >        |       |       | 0000          |

| RPINR22     | 06CC  | —      |                           |           | :      | SCK2R<6:0  | >             |             |         | —           |             |       |           | SDI2R<6:0> | >        |       |       | 0000          |

| RPINR23     | 06CE  | —      | —                         | _         | —      | —          | —             | —           | —       |             |             |       |           | SS2R<6:0>  |          |       |       | 0000          |

| RPINR24     | 06D0  | —      |                           |           | (      | CSCKR<6:0  | >             |             |         | —           |             |       |           | CSDIR<6:0> | >        |       |       | 0000          |

| RPINR25     | 06D2  | —      | —                         | _         | —      | —          | —             | —           | —       |             |             |       | (         | COFSR<6:0  | >        |       |       | 0000          |

| RPINR26     | 06D4  | —      |                           |           |        | C2RXR<6:0  | >             |             |         | —           |             |       | (         | C1RXR<6:0  | >        |       |       | 0000          |

| RPINR27     | 06D6  | —      |                           |           | ι      | J3CTSR<6:( | )>            |             |         | —           |             |       | l         | J3RXR<6:0  | >        |       |       | 0000          |

| RPINR28     | 06D8  | —      |                           |           | ι      | J4CTSR<6:( | )>            |             |         | —           |             |       | l         | J4RXR<6:0  | >        |       |       | 0000          |

| RPINR29     | 06DA  | —      |                           |           |        | SCK3R<6:0  | >             |             |         | —           |             |       |           | SDI3R<6:0> | <b>`</b> |       |       | 0000          |

| RPINR30     | 06DC  | —      | —                         | —         | —      | —          | —             |             | —       | —           |             |       |           | SS3R<6:0>  |          |       | •     | 0000          |

| RPINR37     | 06EA  | —      |                           |           | S      | YNCI1R<6:  | 0>            |             |         | —           |             | —     | _         | —          |          | _     |       | 0000          |

| RPINR38     | 06EC  | _      |                           |           |        | TCMP1R<6   |               |             |         | —           | _           | —     |           | —          | —        | _     | —     | 0000          |

| RPINR39     | 06EE  | _      |                           |           |        | TCMP3R<6   | -             |             |         | —           |             |       | D         | TCMP2R<6:  | 0>       |       |       | 0000          |

| RPINR40     | 06F0  | —      |                           |           | D      | TCMP5R<6   | :0>           |             |         | —           |             |       | D         | TCMP4R<6:  | 0>       |       |       | 0000          |

| RPINR41     | 06F2  | —      | —                         | —         | —      | —          | —             | —           | —       | —           |             |       | D         | TCMP6R<6:  | 0>       |       |       | 0000          |

#### TABLE 4-33: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXGM60X/7XX DEVICES

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

| U-0          | U-0                                                                                                                                                                                                                                     | U-0                     | U-0            | U-0              | U-0              | U-0             | U-0   |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------|------------------|------------------|-----------------|-------|--|--|--|--|

| _            | _                                                                                                                                                                                                                                       | —                       | _              | —                | _                | _               | _     |  |  |  |  |

| bit 15       | ·                                                                                                                                                                                                                                       |                         |                |                  |                  |                 | bit 8 |  |  |  |  |

|              |                                                                                                                                                                                                                                         |                         |                |                  |                  |                 |       |  |  |  |  |

| U-0          | U-0                                                                                                                                                                                                                                     | U-0                     | U-0            | R-1              | R-1              | R-1             | R-1   |  |  |  |  |

| —            | —                                                                                                                                                                                                                                       | —                       | _              | LSTCH<3:0>       |                  |                 |       |  |  |  |  |

| bit 7        |                                                                                                                                                                                                                                         |                         |                |                  |                  |                 | bit 0 |  |  |  |  |

|              |                                                                                                                                                                                                                                         |                         |                |                  |                  |                 |       |  |  |  |  |

| Legend:      |                                                                                                                                                                                                                                         |                         |                |                  |                  |                 |       |  |  |  |  |

| R = Readab   | ole bit                                                                                                                                                                                                                                 | W = Writable            | bit            | U = Unimpler     | mented bit, read | as '0'          |       |  |  |  |  |

| -n = Value a | at POR                                                                                                                                                                                                                                  | '1' = Bit is set        |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |

|              |                                                                                                                                                                                                                                         |                         |                |                  |                  |                 |       |  |  |  |  |

| bit 15-4     | Unimplemen                                                                                                                                                                                                                              | ted: Read as 'o         | o'             |                  |                  |                 |       |  |  |  |  |

| bit 3-0      | LSTCH<3:0>                                                                                                                                                                                                                              | : Last DMA Co           | ntroller Chanr | nel Active Statu | is bits          |                 |       |  |  |  |  |

|              | 1111 = No DI<br>1110 = Rese                                                                                                                                                                                                             | MA transfer has<br>rved | s occurred sin | ice system Res   | set              |                 |       |  |  |  |  |

|              | •                                                                                                                                                                                                                                       |                         |                |                  |                  |                 |       |  |  |  |  |

|              | •                                                                                                                                                                                                                                       |                         |                |                  |                  |                 |       |  |  |  |  |

|              | •                                                                                                                                                                                                                                       |                         |                |                  |                  |                 |       |  |  |  |  |

|              | 0100 = Reserved<br>0011 = Last data transfer was handled by Channel 3<br>0010 = Last data transfer was handled by Channel 2<br>0001 = Last data transfer was handled by Channel 1<br>0000 = Last data transfer was handled by Channel 0 |                         |                |                  |                  |                 |       |  |  |  |  |

0000 = Last data transfer was handled by Channel 0

### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation. For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## **10.4** Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled, using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

Note: If a PMD bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

| U-0          | R/W-0     | R/W-0                                 | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|-----------|---------------------------------------|-------|-------------------|-----------------|-----------------|-------|

| —            |           |                                       |       | IC6R<6:0>         |                 |                 |       |

| bit 15       |           |                                       |       |                   |                 |                 | bit 8 |

|              |           |                                       |       |                   |                 |                 |       |

| U-0          | R/W-0     | R/W-0                                 | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| _            |           |                                       |       | IC5R<6:0>         |                 |                 |       |

| bit 7        |           |                                       |       |                   |                 |                 | bit 0 |

|              |           |                                       |       |                   |                 |                 |       |

| Legend:      |           |                                       |       |                   |                 |                 |       |

| R = Readab   | ole bit   | W = Writable                          | bit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR    | '1' = Bit is set                      |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              |           |                                       |       |                   |                 |                 |       |

| bit 15       | Unimpleme | ented: Read as '                      | 0'    |                   |                 |                 |       |

| bit 14-8     |           | Assign Input Ca<br>11-2 for input pin |       |                   | onding RPn P    | in bits         |       |

|              | 1111100 = | Input tied to RPI                     | 124   |                   |                 |                 |       |

|              | •         |                                       |       |                   |                 |                 |       |

|              | •         |                                       |       |                   |                 |                 |       |

|              | 0000001 = | Input tied to CM                      | P1    |                   |                 |                 |       |

|              | 0000000 = | Input tied to Vss                     | ;     |                   |                 |                 |       |

| bit 7        | Unimpleme | ented: Read as '                      | 0'    |                   |                 |                 |       |

| bit 6-0      |           | Assign Input Ca<br>11-2 for input pin |       |                   | onding RPn P    | in bits         |       |

|              | 1111100 = | Input tied to RPI                     | 124   |                   |                 |                 |       |

|              | •         |                                       |       |                   |                 |                 |       |

|              | •         |                                       |       |                   |                 |                 |       |

|              | 0000001 = | Input tied to CM                      | P1    |                   |                 |                 |       |

|              |           | Input tied to Vss                     |       |                   |                 |                 |       |

|              |           |                                       |       |                   |                 |                 |       |

#### REGISTER 11-6: RPINR9: PERIPHERAL PIN SELECT INPUT REGISTER 9

NOTES:

#### REGISTER 16-6: STCON2: PWMx SECONDARY MASTER CLOCK DIVIDER SELECT REGISTER 2

| U-0            | U-0 | U-0          | U-0 | U-0                                | U-0   | U-0           | U-0   |  |  |

|----------------|-----|--------------|-----|------------------------------------|-------|---------------|-------|--|--|

| —              | —   | —            | —   | —                                  | —     | —             | _     |  |  |

| bit 15         |     |              |     |                                    |       |               | bit 8 |  |  |

|                |     |              |     |                                    |       |               |       |  |  |

| U-0            | U-0 | U-0          | U-0 | U-0                                | R/W-0 | R/W-0         | R/W-0 |  |  |

| —              | —   | —            | —   | —                                  | P     | CLKDIV<2:0>(1 | )     |  |  |

| bit 7          |     |              |     |                                    |       |               | bit 0 |  |  |

|                |     |              |     |                                    |       |               |       |  |  |

| Legend:        |     |              |     |                                    |       |               |       |  |  |

| R = Readable I | bit | W = Writable | bit | U = Unimplemented bit, read as '0' |       |               |       |  |  |

| R – Reauable bit  |                  | 0 – Unimplemented bit, read |                    |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved

- 110 = Divide-by-64

- 101 = Divide-by-32

- 100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

#### REGISTER 26-2: CMxCON: OP AMP/COMPARATOR x CONTROL REGISTER (x = 1, 2, 3 OR 5) (CONTINUED)

| bit 7-6 | EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits <sup>(3)</sup>                                                                                        |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 11 = Trigger/event/interrupt generated on any change of the comparator output (while $CEVT = 0$ )                                                              |

|         | 10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator<br>output (while CEVT = 0)                           |

|         | If CPOL = 1 (inverted polarity):<br>Low-to-high transition of the comparator output.                                                                           |

|         | If CPOL = 0 (non-inverted polarity):<br>High-to-low transition of the comparator output.                                                                       |

|         | 01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity selected comparator<br>output (while CEVT = 0)                           |

|         | If CPOL = 1 (inverted polarity):                                                                                                                               |

|         | High-to-low transition of the comparator output.                                                                                                               |

|         | If CPOL = 0 (non-inverted polarity):                                                                                                                           |

|         | Low-to-high transition of the comparator output.                                                                                                               |

|         | 00 = Trigger/event/interrupt generation is disabled.                                                                                                           |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                     |

| bit 4   | CREF: Comparator Reference Select bit (VIN+ input) <sup>(1)</sup>                                                                                              |

|         | <ul> <li>1 = VIN+ input connects to internal CVREFIN voltage</li> <li>0 = VIN+ input connects to CxIN1+ pin</li> </ul>                                         |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                     |

| bit 1-0 | CCH<1:0>: Op Amp/Comparator Channel Select bits <sup>(1)</sup>                                                                                                 |

|         | 11 = Inverting input of op amp/comparator connects to CxIN4- pin                                                                                               |

|         | <ul> <li>10 = Inverting input of op amp/comparator connects to CxIN3- pin</li> <li>01 = Inverting input of op amp/comparator connects to CxIN2- pin</li> </ul> |

|         | 00 = Inverting input of op amp/comparator connects to CxIN2- pin                                                                                               |

| Note 1: | Inputs that are selected and not available will be tied to Vss. See the " <b>Pin Diagrams</b> " section for available                                          |

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- **2:** The op amp and the comparator can be used simultaneously in these devices. The OPMODE bit only enables the op amp while the comparator is still functional.

- **3:** After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator Event bit, CEVT (CMxCON<9>), and the Comparator Combined Interrupt Flag, CMPIF (IFS1<2>), **must be cleared** before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax | Description                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------|-----------------|---------------------------------------------------|---------------|----------------|--------------------------|

| 53                 | NEG                  | NEG    | Acc             | Negate Accumulator                                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG    | f               | $f = \overline{f} + 1$                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG    | f,WREG          | WREG = $\overline{f}$ + 1                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG    | Ws,Wd           | $Wd = \overline{Ws} + 1$                          | 1             | 1              | C,DC,N,OV,Z              |

| 54                 | NOP                  | NOP    |                 | No Operation                                      | 1             | 1              | None                     |

|                    |                      | NOPR   |                 | No Operation                                      | 1             | 1              | None                     |

| 55                 | POP                  | POP    | f               | Pop f from Top-of-Stack (TOS)                     | 1             | 1              | None                     |

|                    |                      | POP    | Wdo             | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1              | None                     |

|                    |                      | POP.D  | Wnd             | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2              | None                     |

|                    |                      | POP.S  |                 | Pop Shadow Registers                              | 1             | 1              | All                      |

| 56                 | PUSH                 | PUSH   | f               | Push f to Top-of-Stack (TOS)                      | 1             | 1              | None                     |

|                    |                      | PUSH   | Wso             | Push Wso to Top-of-Stack (TOS)                    | 1             | 1              | None                     |

|                    |                      | PUSH.D | Wns             | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)     | 1             | 2              | None                     |

|                    |                      | PUSH.S |                 | Push Shadow Registers                             | 1             | 1              | None                     |

| 57                 | PWRSAV               | PWRSAV | #lit1           | Go into Sleep or Idle mode                        | 1             | 1              | WDTO,Sleep               |

| 58                 | RCALL                | RCALL  | Expr            | Relative Call                                     | 1             | 4              | SFA                      |

|                    |                      | RCALL  | Wn              | Computed Call                                     | 1             | 4              | SFA                      |

| 59                 | REPEAT               | REPEAT | #lit15          | Repeat Next Instruction lit15 + 1 times           | 1             | 1              | None                     |

|                    |                      | REPEAT | Wn              | Repeat Next Instruction (Wn) + 1 times            | 1             | 1              | None                     |

| 60                 | RESET                | RESET  |                 | Software device Reset                             | 1             | 1              | None                     |

| 61                 | RETFIE               | RETFIE |                 | Return from interrupt                             | 1             | 6 (5)          | SFA                      |

| 62                 | RETLW                | RETLW  | #lit10,Wn       | Return with literal in Wn                         | 1             | 6 (5)          | SFA                      |

| 63                 | RETURN               | RETURN |                 | Return from Subroutine                            | 1             | 6 (5)          | SFA                      |

| 64                 | RLC                  | RLC    | f               | f = Rotate Left through Carry f                   | 1             | 1              | C,N,Z                    |

|                    |                      | RLC    | f,WREG          | WREG = Rotate Left through Carry f                | 1             | 1              | C,N,Z                    |

|                    |                      | RLC    | Ws,Wd           | Wd = Rotate Left through Carry Ws                 | 1             | 1              | C,N,Z                    |

| 65                 | RLNC                 | RLNC   | f               | f = Rotate Left (No Carry) f                      | 1             | 1              | N,Z                      |

|                    |                      | RLNC   | f,WREG          | WREG = Rotate Left (No Carry) f                   | 1             | 1              | N,Z                      |

|                    |                      | RLNC   | Ws,Wd           | Wd = Rotate Left (No Carry) Ws                    | 1             | 1              | N,Z                      |

| 66                 | RRC                  | RRC    | f               | f = Rotate Right through Carry f                  | 1             | 1              | C,N,Z                    |

|                    |                      | RRC    | f,WREG          | WREG = Rotate Right through Carry f               | 1             | 1              | C,N,Z                    |

|                    |                      | RRC    | Ws,Wd           | Wd = Rotate Right through Carry Ws                | 1             | 1              | C,N,Z                    |

| 67                 | RRNC                 | RRNC   | f               | f = Rotate Right (No Carry) f                     | 1             | 1              | N,Z                      |

|                    |                      | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f                  | 1             | 1              | N,Z                      |

| <u></u>            | a. a                 | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws                   | 1             | 1              | N,Z                      |

| 68                 | SAC                  | SAC    | Acc,#Slit4,Wdo  | Store Accumulator                                 | 1             | 1              | None                     |

| 60                 | 0.5                  | SAC.R  | Acc,#Slit4,Wdo  | Store Rounded Accumulator                         | 1             | 1              | None                     |

| 69<br>70           | SE                   | SE     | Ws,Wnd          | Wnd = sign-extended Ws<br>f = 0xFFFF              | 1             | 1<br>1         | C,N,Z                    |

| 10                 | SETM                 | SETM   | f<br>WREG       | WREG = 0xFFFF                                     | 1             | 1              | None<br>None             |

|                    |                      | SETM   |                 | WREG = 0XFFFF<br>Ws = 0XFFFF                      | 1             | 1              | None                     |

| 71                 | SFTAC                | SETM   | Ws<br>Acc,Wn    | Arithmetic Shift Accumulator by (Wn)              | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | SFTAC  | Acc,#Slit6      | Arithmetic Shift Accumulator by Slit6             | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

#### TABLE 31-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

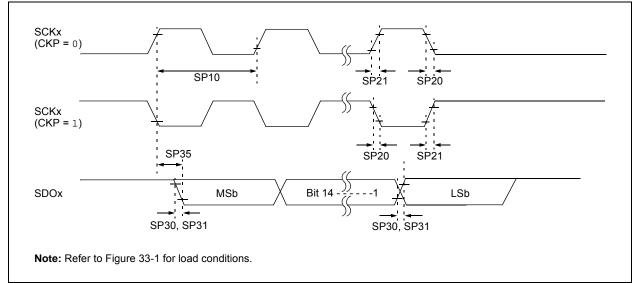

| <b>TABLE 33-32:</b> | SPI2 AND SPI3 MAXIMUM DATA/CLOCK RATE SUMMARY |

|---------------------|-----------------------------------------------|

|---------------------|-----------------------------------------------|

| AC CHARACTERISTICS   |                                          |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |

| 15 MHz               | Table 33-33                              | _                                           | —                                                     | 0,1 | 0,1 | 0,1 |  |

| 9 MHz                | —                                        | Table 33-34                                 | —                                                     | 1   | 0,1 | 1   |  |

| 9 MHz                | —                                        | Table 33-35                                 | —                                                     | 0   | 0,1 | 1   |  |

| 15 MHz               | —                                        | —                                           | Table 33-36                                           | 1   | 0   | 0   |  |

| 11 MHz               | _                                        | _                                           | Table 33-37                                           | 1   | 1   | 0   |  |

| 15 MHz               | _                                        | _                                           | Table 33-38                                           | 0   | 1   | 0   |  |

| 11 MHz               | _                                        | _                                           | Table 33-39                                           | 0   | 0   | 0   |  |

### FIGURE 33-15: SPI2 AND SPI3 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

| AC CHARACTERISTICS                 |        |                                   | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |                 |      |                                                                  |  |  |  |

|------------------------------------|--------|-----------------------------------|------------------------------------------------------|------|-----------------|------|------------------------------------------------------------------|--|--|--|

| Param<br>No.                       | Symbol | Characteristic                    | Min.                                                 | Тур. | Typ. Max. Units |      | Conditions                                                       |  |  |  |

| ADC Accuracy (12-Bit Mode) – VREF- |        |                                   |                                                      |      |                 |      |                                                                  |  |  |  |

| AD20a                              | Nr     | Resolution                        | 12 data bits                                         |      |                 | bits |                                                                  |  |  |  |

| AD21a                              | INL    | Integral Nonlinearity             | -3                                                   | _    | +3              | LSb  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V <b>(Note 2)</b> |  |  |  |

| AD22a                              | DNL    | Differential Nonlinearity         | ≥ 1                                                  |      | < 1             | LSb  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V (Note 2)        |  |  |  |

| AD23a                              | Gerr   | Gain Error                        | -10                                                  | _    | 10              | LSb  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V <b>(Note 2)</b> |  |  |  |

| AD24a                              | EOFF   | Offset Error                      | -5                                                   | _    | 5               | LSb  | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V <b>(Note 2)</b> |  |  |  |

| AD25a                              | —      | Monotonicity                      | _                                                    | _    | —               |      | Guaranteed                                                       |  |  |  |

| Dynamic Performance (12-Bit Mode)  |        |                                   |                                                      |      |                 |      |                                                                  |  |  |  |

| AD30a                              | THD    | Total Harmonic Distortion         | _                                                    |      | -75             | dB   |                                                                  |  |  |  |

| AD31a                              | SINAD  | Signal to Noise and<br>Distortion | 68.5                                                 | 69.5 | _               | dB   |                                                                  |  |  |  |

| AD32a                              | SFDR   | Spurious Free Dynamic<br>Range    | 80                                                   | _    | _               | dB   |                                                                  |  |  |  |

| AD33a                              | Fnyq   | Input Signal Bandwidth            | _                                                    | _    | 250             | kHz  |                                                                  |  |  |  |

| AD34a                              | ENOB   | Effective Number of Bits          | 11.09                                                | 11.3 | _               | bits |                                                                  |  |  |  |

#### TABLE 33-57: ADCx MODULE SPECIFICATIONS (12-BIT MODE)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 33-12 for the minimum and maximum BOR values.

2: For all accuracy specifications, VINL = AVSS = VREFL = 0V and AVDD = VREFH = 3.6V.

# dsPIC33EPXXXGM3XX/6XX/7XX

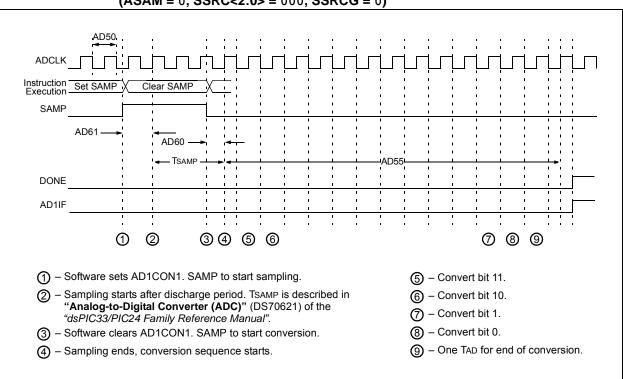

#### FIGURE 33-38: ADC1 CONVERSION (12-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000, SSRCG = 0)

#### 35.1 Package Marking Information (Continued)

64-Lead TQFP (10x10x1 mm)

Example

100-Lead TQFP (12x12x1 mm)

100-Lead TQFP (14x14x1 mm)

121-Lead TFBGA (10x10x1.1 mm)

Example

Example

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

NOTES: