Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT   |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | ·                                                                                 |

| RAM Size                   | 48K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) |                                                                                   |

| Data Converters            | A/D 18x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 44-QFN (8x8)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gm604t-i-ml |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXXGM3XX/6XX/7XX

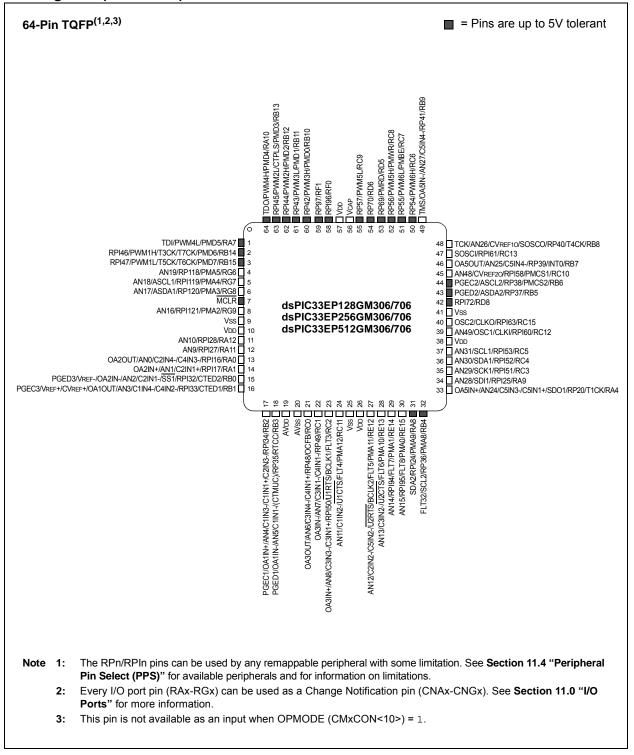

### **Pin Diagrams (Continued)**

# Pin Diagrams (Continued)

|        |             |              |              | c            | dsPIC33   | EP128G<br>EP256G<br>EP512G | M310/71   | 0         |           |           |           |

|--------|-------------|--------------|--------------|--------------|-----------|----------------------------|-----------|-----------|-----------|-----------|-----------|

|        | 1           | 2            | 3            | 4            | 5         | 6                          | 7         | 8         | 9         | 10        | 11        |

| /<br>R | A10         | <b>R</b> B13 | <b>R</b> G13 | <b>R</b> B10 | RG0       | RF1                        | O<br>Vdd  | O<br>NC   | RD12      | RC6       | O<br>RB9  |

|        |             | O<br>RG15    | RB12         | RB11         | RF7       | RF0                        | O<br>VCAP | RD5       | RC7       | ⊖<br>Vss  | O<br>RB8  |

| (<br>R | <b>B</b> 14 |              | RG12         | RG14         | RF6       |                            | RC9       | RC8       |           | O<br>RC13 | O<br>RC10 |

| (<br>F | RD1         | RB15         | RA7          | O<br>NC      | O<br>NC   | O<br>NC                    | RD6       | RD13      | O<br>RB7  | O<br>NC   | RB6       |

|        | RD4         | RD3          | O<br>RG6     | RD2          | O<br>NC   | RG1                        | ⊖<br>NC   | O<br>RA15 | RD8       | RB5       | O<br>RA14 |

| M      |             | O<br>RG8     | O<br>RG9     | O<br>RG7     | ⊖<br>Vss  |                            | ◯<br>NC   | O<br>Vdd  | O<br>RC12 | ⊖<br>Vss  | O<br>RC15 |

|        | C<br>RE8    | O<br>RE9     | O<br>RG10    |              | O<br>Vdd  | ⊖<br>Vss                   | ⊖<br>Vss  | O<br>NC   | O<br>RF5  | O<br>RG3  | O<br>RF4  |

|        | )<br>A12    | O<br>RA11    | O<br>NC      | ◯<br>NC      |           | O<br>VDD                   | ◯<br>NC   | O<br>RA9  | O<br>RC3  | O<br>RC5  | O<br>RG2  |

|        |             | O<br>RA1     | O<br>RB3     | O<br>AVDD    | O<br>RC11 | O<br>RG11                  | O<br>RE12 | O<br>NC   |           | O<br>RE1  | O<br>RC4  |

|        | C<br>RB0    | O<br>RB1     | O<br>RF10    | O<br>RC0     |           | O<br>RF12                  | O<br>RE14 | O<br>Vdd  | O<br>RD15 | O<br>RA4  | O<br>RE0  |

|        | C<br>RB2    | O<br>RF9     | )<br>AVss    | O<br>RC1     | O<br>RC2  | O<br>RF13                  | O<br>RE13 | O<br>RE15 | O<br>RD14 | RA8       | RB4       |

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

## 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

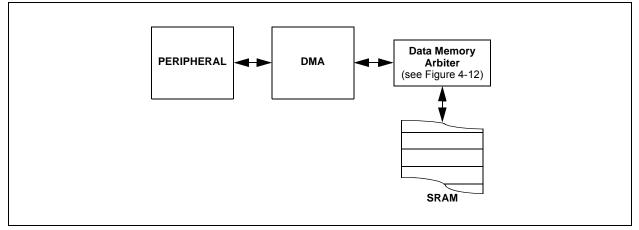

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Direct Memory Access (DMA)" (DS70348), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The data memory bus arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. The peripherals supported by the DMA Controller include:

- CAN

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

- DCI

- PMP

- Timers

Refer to Table 8-1 for a complete list of supported peripherals.

### FIGURE 8-1: PERIPHERAL TO DMA CONTROLLER

| U-0                                | U-0         | U-0                                             | U-0              | U-0                                | U-0                | U-0   | U-0   |  |  |

|------------------------------------|-------------|-------------------------------------------------|------------------|------------------------------------|--------------------|-------|-------|--|--|

| —                                  | —           | —                                               | —                | —                                  | —                  |       | —     |  |  |

| bit 15                             |             |                                                 |                  |                                    |                    |       | bit 8 |  |  |

|                                    |             |                                                 |                  |                                    |                    |       |       |  |  |

| U-0                                | U-0         | U-0                                             | U-0              | R-0                                | R-0                | R-0   | R-0   |  |  |

| —                                  | —           | —                                               | —                | PPST3                              | PPST2              | PPST1 | PPST0 |  |  |

| bit 7                              |             |                                                 |                  |                                    |                    |       | bit 0 |  |  |

|                                    |             |                                                 |                  |                                    |                    |       |       |  |  |

| Legend:                            |             |                                                 |                  |                                    |                    |       |       |  |  |

| R = Readable bit W = Writable bit  |             |                                                 | bit              | U = Unimplemented bit, read as '0' |                    |       |       |  |  |

| -n = Value at POR '1' = Bit is set |             |                                                 | '0' = Bit is cle | ared                               | x = Bit is unknown |       |       |  |  |

|                                    |             |                                                 |                  |                                    |                    |       |       |  |  |

| bit 15-4                           | Unimplemen  | Unimplemented: Read as '0'                      |                  |                                    |                    |       |       |  |  |

| bit 3                              | PPST3: Char | PPST3: Channel 3 Ping-Pong Mode Status Flag bit |                  |                                    |                    |       |       |  |  |

|                                    |             | B register is se                                |                  |                                    |                    |       |       |  |  |

|                                    | 0 = DMA3ST  | A register is se                                | lected           |                                    |                    |       |       |  |  |

| bit 2                              | PPST2: Char | nnel 2 Ping-Por                                 | ng Mode Statu    | is Flag bit                        |                    |       |       |  |  |

|                                    |             | B register is se                                |                  |                                    |                    |       |       |  |  |

|                                    | 0 = DMA2ST  | A register is se                                | lected           |                                    |                    |       |       |  |  |

| bit 1                              | PPST1: Char | nnel 1 Ping-Por                                 | ng Mode Statu    | is Flag bit                        |                    |       |       |  |  |

|                                    | 1 = DMA1ST  | B register is se                                | lected           |                                    |                    |       |       |  |  |

|                                    | 0 = DMA1ST  | A register is se                                | lected           |                                    |                    |       |       |  |  |

| bit 0                              | PPST0: Char | nnel 0 Ping-Por                                 | ng Mode Statu    | is Flag bit                        |                    |       |       |  |  |

bit 0 PPST0: Channel 0 Ping-Pong Mode Status Flag bit

1 = DMA0STB register is selected

0 = DMA0STA register is selected

| R/W-0        | R/W-0                                               | R/W-1                                                                                                               | R/W-1                | R/W-0                                 | R/W-0              | R/W-0           | R/W-0     |  |  |  |

|--------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------|--------------------|-----------------|-----------|--|--|--|

| ROI          | DOZE2 <sup>(3)</sup>                                | DOZE1 <sup>(3)</sup>                                                                                                | DOZE0 <sup>(3)</sup> | DOZEN <sup>(1,4)</sup>                | FRCDIV2            | FRCDIV1         | FRCDIV0   |  |  |  |

| bit 15       |                                                     |                                                                                                                     |                      |                                       |                    |                 | bit 8     |  |  |  |

|              |                                                     |                                                                                                                     |                      |                                       |                    |                 |           |  |  |  |

| R/W-0        | R/W-1                                               | U-0                                                                                                                 | R/W-0                | R/W-0                                 | R/W-0              | R/W-0           | R/W-0     |  |  |  |

| PLLPOST      | 1 PLLPOST0                                          |                                                                                                                     | PLLPRE4              | PLLPRE3                               | PLLPRE2            | PLLPRE1         | PLLPRE0   |  |  |  |

| bit 7        |                                                     |                                                                                                                     |                      |                                       |                    |                 | bit (     |  |  |  |

| <del></del>  |                                                     |                                                                                                                     |                      |                                       |                    |                 |           |  |  |  |

| Legend:      | la hit                                              |                                                                                                                     | L:4                  | II — Ilucius da un                    | antad bit waar     | L == (0'        |           |  |  |  |

| R = Readab   |                                                     | W = Writable                                                                                                        |                      | •                                     | nented bit, read   |                 |           |  |  |  |

| -n = Value a | IL POR                                              | '1' = Bit is set                                                                                                    |                      | '0' = Bit is clea                     | ared               | x = Bit is unkr | IOWI      |  |  |  |

| bit 15       | ROI: Recover                                        | on Interrupt b                                                                                                      | it                   |                                       |                    |                 |           |  |  |  |

|              |                                                     | will clear the D                                                                                                    |                      |                                       |                    |                 |           |  |  |  |

|              |                                                     | will have no ef                                                                                                     |                      | OZEN bit                              |                    |                 |           |  |  |  |

| bit 14-12    | DOZE<2:0>:                                          | Processor Clo                                                                                                       | ck Reduction         | Select bits <sup>(3)</sup>            |                    |                 |           |  |  |  |

|              | 111 = Fcy div                                       |                                                                                                                     |                      |                                       |                    |                 |           |  |  |  |

|              | 110 = Fcy div                                       | •                                                                                                                   |                      |                                       |                    |                 |           |  |  |  |

|              |                                                     | 101 = Fcy divided by 32<br>100 = Fcy divided by 16                                                                  |                      |                                       |                    |                 |           |  |  |  |

|              |                                                     | 011 = FCY divided by 16<br>011 = FCY divided by 8 (default)                                                         |                      |                                       |                    |                 |           |  |  |  |

|              | 010 = FCY div                                       |                                                                                                                     |                      |                                       |                    |                 |           |  |  |  |

|              | 001 = Fcy div                                       |                                                                                                                     |                      |                                       |                    |                 |           |  |  |  |

|              | 000 = Fcy divided by 1                              |                                                                                                                     |                      |                                       |                    |                 |           |  |  |  |

| bit 11       |                                                     | e Mode Enable                                                                                                       |                      |                                       |                    |                 |           |  |  |  |

|              |                                                     |                                                                                                                     |                      | etween the perip                      |                    | nd the processo | or clocks |  |  |  |

| hit 10 0     |                                                     | •                                                                                                                   | •                    | ratio are forced<br>r Postscaler bits |                    |                 |           |  |  |  |

| bit 10-8     |                                                     |                                                                                                                     | RC Oscillator        | Posiscaler bits                       | 5                  |                 |           |  |  |  |

|              | 111 = FRC divided by 256<br>110 = FRC divided by 64 |                                                                                                                     |                      |                                       |                    |                 |           |  |  |  |

|              | 101 = FRC divided by 32                             |                                                                                                                     |                      |                                       |                    |                 |           |  |  |  |

|              | 100 = FRC divided by 16                             |                                                                                                                     |                      |                                       |                    |                 |           |  |  |  |

|              | 011 = FRC divided by 8                              |                                                                                                                     |                      |                                       |                    |                 |           |  |  |  |

|              |                                                     | 010 = FRC divided by 4<br>001 = FRC divided by 2                                                                    |                      |                                       |                    |                 |           |  |  |  |

|              |                                                     | ivided by 1 (de                                                                                                     | fault)               |                                       |                    |                 |           |  |  |  |

| bit 7-6      |                                                     | •                                                                                                                   |                      | r Select bits (als                    | so denoted as      | N2', PLL posts  | caler)    |  |  |  |

|              | 11 = Output o                                       | PLLPOST<1:0>: PLL VCO Output Divider Select bits (also denoted as 'N2', PLL postscaler)<br>11 = Output divided by 8 |                      |                                       |                    |                 |           |  |  |  |

|              |                                                     | 10 = Reserved                                                                                                       |                      |                                       |                    |                 |           |  |  |  |

|              | 01 = Output c<br>00 = Output c                      | livided by 4 (de                                                                                                    | efault)              |                                       |                    |                 |           |  |  |  |

| bit 5        | -                                                   | ted: Read as '                                                                                                      | 0'                   |                                       |                    |                 |           |  |  |  |

|              | -                                                   |                                                                                                                     |                      | n interment a                         |                    |                 |           |  |  |  |

|              | This bit is cleared                                 |                                                                                                                     |                      |                                       | uis.               |                 |           |  |  |  |

|              | This register resets<br>The DOZE<2:0> b             | -                                                                                                                   |                      |                                       | hit is clear. If D |                 | writes to |  |  |  |

|              | OZE<2:0> b<br>OZE<2:0> are ig                       | -                                                                                                                   |                      |                                       | on is oreal. If D  | ∪∠∟iv – ⊥, ally |           |  |  |  |

|              |                                                     |                                                                                                                     |                      |                                       |                    |                 | -         |  |  |  |

## REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup>

4: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

| bit 4 | SPI2MD: SPI2 Module Disable bit              |

|-------|----------------------------------------------|

|       | 1 = SPI2 module is disabled                  |

|       | 0 = SPI2 module is enabled                   |

| bit 3 | SPI1MD: SPI1 Module Disable bit              |

|       | 1 = SPI1 module is disabled                  |

|       | 0 = SPI1 module is enabled                   |

| bit 2 | C2MD: CAN2 Module Disable bit <sup>(1)</sup> |

|       | 1 = CAN2 module is disabled                  |

|       | 0 = CAN2 module is enabled                   |

| bit 1 | C1MD: CAN1 Module Disable bit <sup>(1)</sup> |

|       | 1 = CAN1 module is disabled                  |

|       | 0 = CAN1 module is enabled                   |

| bit 0 | AD1MD: ADC1 Module Disable bit               |

|       | 1 = ADC1 module is disabled                  |

|       | 0 = ADC1 module is enabled                   |

|       |                                              |

Note 1: These bits are available on dsPIC33EPXXXGM6XX/7XX devices only.

| U-0          | D 44/ 0                                                              |                                                   |                            | DAMA                 |                | DAMA               |            |

|--------------|----------------------------------------------------------------------|---------------------------------------------------|----------------------------|----------------------|----------------|--------------------|------------|

|              | R/W-0                                                                | R/W-0                                             | R/W-0                      | R/W-0                | R/W-0          | R/W-0              | R/W-0      |

|              |                                                                      |                                                   |                            | U4CTSR<6:0>          | >              |                    | h:t 0      |

| pit 15       |                                                                      |                                                   |                            |                      |                |                    | bit 8      |

| U-0          | R/W-0                                                                | R/W-0                                             | R/W-0                      | R/W-0                | R/W-0          | R/W-0              | R/W-0      |

| _            |                                                                      |                                                   |                            | U4RXR<6:0>           |                |                    |            |

| bit 7        |                                                                      |                                                   |                            |                      |                |                    | bit 0      |

| Legend:      |                                                                      |                                                   |                            |                      |                |                    |            |

| R = Readab   | ole bit                                                              | W = Writable                                      | d as '0'                   |                      |                |                    |            |

| -n = Value a | at POR                                                               | '1' = Bit is set                                  |                            | '0' = Bit is cleared |                | x = Bit is unknown |            |

|              |                                                                      | <b>0&gt;:</b> Assign UAR<br>1-2 for input pin     |                            |                      | o the Correspo | onding RPn/RPI     | n Pin bits |

|              | (see Table 1 <sup>-</sup><br>1111111 = I<br>•<br>•                   | 1-2 for input pin<br>nput tied to RP <sup>7</sup> | selection nun<br>124       |                      | o the Corresp  | onding RPn/RPI     | n Pin bits |

|              | (see Table 1 <sup>-</sup><br>1111111 =  <br>•<br>•<br>•<br>0000001 = | 1-2 for input pin                                 | selection nun<br>124<br>P1 |                      | o the Corresp  | onding RPn/RPI     | n Pin bits |

| bit 7        | (see Table 1'<br>1111111 =  <br>0000001 =  <br>0000000 =             | 1-2 for input pin<br>nput tied to RP              | selection nun<br>124<br>P1 |                      | o the Correspo | onding RPn/RPI     | n Pin bits |

## REGISTER 11-22: RPINR28: PERIPHERAL PIN SELECT INPUT REGISTER 28

| R/W-0<br>R/W-0                         | R/W-0<br>R/W-0<br>W = Writable H<br>'1' = Bit is set<br>ted: Read as '0        |                                                                                                                                                                      | R/W-0<br>DTCMP5R<6:(<br>R/W-0<br>DTCMP4R<6:(<br>U = Unimplen<br>'0' = Bit is cle                        | R/W-0<br>)>                                                                                                                                                                                                  | R/W-0<br>R/W-0<br>d as '0'<br>x = Bit is unkr                                                                                                                                                                                                               | R/W-0<br>bit 8<br>R/W-0<br>bit 0                                                                                                                                                                                                                                          |

|----------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nimplemen                              | W = Writable I<br>'1' = Bit is set                                             | bit                                                                                                                                                                  | R/W-0<br>DTCMP4R<6:(<br>U = Unimplen                                                                    | R/W-0<br>)>                                                                                                                                                                                                  | d as '0'                                                                                                                                                                                                                                                    | R/W-0<br>bit 0                                                                                                                                                                                                                                                            |

| nimplemen                              | W = Writable I<br>'1' = Bit is set                                             | bit                                                                                                                                                                  | DTCMP4R<6:(<br>U = Unimplen                                                                             | )>                                                                                                                                                                                                           | d as '0'                                                                                                                                                                                                                                                    | R/W-0<br>bit 0                                                                                                                                                                                                                                                            |

| nimplemen                              | W = Writable I<br>'1' = Bit is set                                             | bit                                                                                                                                                                  | DTCMP4R<6:(<br>U = Unimplen                                                                             | )>                                                                                                                                                                                                           | d as '0'                                                                                                                                                                                                                                                    | bit 0                                                                                                                                                                                                                                                                     |

| nimplemen                              | W = Writable I<br>'1' = Bit is set                                             | bit                                                                                                                                                                  | DTCMP4R<6:(<br>U = Unimplen                                                                             | )>                                                                                                                                                                                                           | d as '0'                                                                                                                                                                                                                                                    | bit 0                                                                                                                                                                                                                                                                     |

| nimplemen                              | '1' = Bit is set                                                               |                                                                                                                                                                      | U = Unimplen                                                                                            | nented bit, rea                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                           |

| nimplemen                              | '1' = Bit is set                                                               |                                                                                                                                                                      | •                                                                                                       |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                           |

| nimplemen                              | '1' = Bit is set                                                               |                                                                                                                                                                      | •                                                                                                       |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             | nown                                                                                                                                                                                                                                                                      |

| nimplemen                              | '1' = Bit is set                                                               |                                                                                                                                                                      | •                                                                                                       |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             | nown                                                                                                                                                                                                                                                                      |

| nimplemen                              |                                                                                |                                                                                                                                                                      | '0' = Bit is cle                                                                                        | ared                                                                                                                                                                                                         | x = Bit is unkr                                                                                                                                                                                                                                             | nown                                                                                                                                                                                                                                                                      |

| nimplemen                              | ted: Read as 'o                                                                | 0,                                                                                                                                                                   |                                                                                                         |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                           |

| 111100 <b>= In</b>                     | put tied to RPI                                                                | 124                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                           |

|                                        |                                                                                |                                                                                                                                                                      |                                                                                                         |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                           |

| nimplemen                              | ted: Read as '0                                                                | 0'                                                                                                                                                                   |                                                                                                         |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                           |

| TCMP4R<6<br>ee Table 11<br>111100 = In | : <b>0&gt;:</b> Assign PW<br>-2 for input pin<br>aput tied to RPI              | VM Dead-Tim<br>selection nur<br>124                                                                                                                                  |                                                                                                         | n Input 4 to th                                                                                                                                                                                              | e Correspondin                                                                                                                                                                                                                                              | g RPn Pin bits                                                                                                                                                                                                                                                            |

| )<br>r<br>1                            | 00000 = Ir<br>himplemen<br>CCMP4R<6<br>ee Table 11<br>11100 = Ir<br>00001 = Ir | 00000 = Input tied to Vss<br>implemented: Read as '<br>CMP4R<6:0>: Assign PV<br>e Table 11-2 for input pin<br>11100 = Input tied to RPI<br>00001 = Input tied to CMI | ee Table 11-2 for input pin selection nur<br>11100 = Input tied to RPI124<br>00001 = Input tied to CMP1 | 00000 = Input tied to Vss<br><b>implemented:</b> Read as '0'<br><b>CMP4R&lt;6:0&gt;:</b> Assign PWM Dead-Time Compensation<br>te Table 11-2 for input pin selection numbers)<br>11100 = Input tied to RPI124 | 00000 = Input tied to Vss<br><b>implemented:</b> Read as '0'<br><b>CCMP4R&lt;6:0&gt;:</b> Assign PWM Dead-Time Compensation Input 4 to the<br>the Table 11-2 for input pin selection numbers)<br>11100 = Input tied to RPI124<br>00001 = Input tied to CMP1 | 00000 = Input tied to Vss<br><b>implemented:</b> Read as '0'<br><b>CCMP4R&lt;6:0&gt;:</b> Assign PWM Dead-Time Compensation Input 4 to the Corresponding<br>the Table 11-2 for input pin selection numbers)<br>11100 = Input tied to RPI124<br>00001 = Input tied to CMP1 |

# dsPIC33EPXXXGM3XX/6XX/7XX

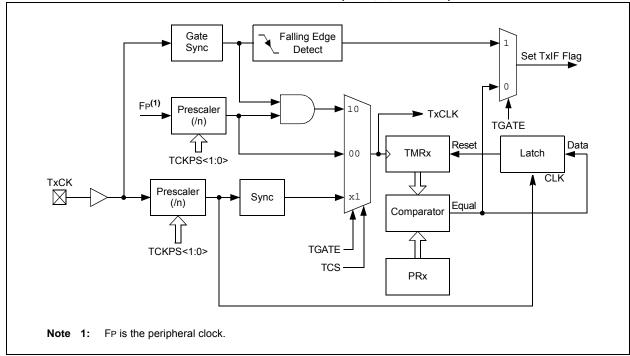

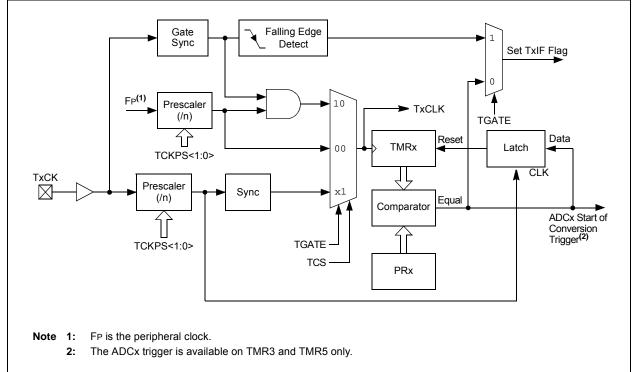

### FIGURE 13-1: TYPE B TIMER BLOCK DIAGRAM (x = 2, 4, 6 AND 8)

### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits 11111 = OCxRS compare event is used for synchronization 11110 = INT2 is the source for compare timer synchronization 11101 = INT1 is the source for compare timer synchronization 11100 = CTMU trigger is the source for compare timer synchronization 11011 = ADC1 interrupt is the source for compare timer synchronization 11010 = Analog Comparator 3 is the source for compare timer synchronization 11001 = Analog Comparator 2 is the source for compare timer synchronization 11000 = Analog Comparator 1 is the source for compare timer synchronization 10111 = Input Capture 8 interrupt is the source for compare timer synchronization 10110 = Input Capture 7 interrupt is the source for compare timer synchronization 10101 = Input Capture 6 interrupt is the source for compare timer synchronization 10100 = Input Capture 5 interrupt is the source for compare timer synchronization 10011 = Input Capture 4 interrupt is the source for compare timer synchronization 10010 = Input Capture 3 interrupt is the source for compare timer synchronization 10001 = Input Capture 2 interrupt is the source for compare timer synchronization 10000 = Input Capture 1 interrupt is the source for compare timer synchronization 01111 = GP Timer5 is the source for compare timer synchronization 01110 = GP Timer4 is the source for compare timer synchronization 01101 = GP Timer3 is the source for compare timer synchronization 01100 = GP Timer2 is the source for compare timer synchronization 01011 = GP Timer1 is the source for compare timer synchronization 01010 = PTGx trigger is the source for compare timer synchronization<sup>(3)</sup> 01001 = Compare timer is unsynchronized 01000 = Output Compare 8 is the source for compare timer synchronization<sup>(1,2)</sup> 00111 = Output Compare 7 is the source for compare timer synchronization<sup>(1,2)</sup> 00110 = Output Compare 6 is the source for compare timer synchronization<sup>(1,2)</sup> 00101 = Output Compare 5 is the source for compare timer synchronization<sup>(1,2)</sup> 00100 = Output Compare 4 is the source for compare timer synchronization<sup>(1,2)</sup> 00011 = Output Compare 3 is the source for compare timer synchronization<sup>(1,2)</sup> 00010 = Output Compare 2 is the source for compare timer synchronization<sup>(1,2)</sup> 00001 = Output Compare 1 is the source for compare timer synchronization<sup>(1,2)</sup> 00000 = Compare timer is unsynchronized

- Note 1: Do not use the OCx module as its own synchronization or trigger source.

- 2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

- 3: Each Output Compare x module (OCx) has one PTG Trigger/Sync source. See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO4 = OC1, OC5 PTGO5 = OC2, OC6 PTGO6 = OC3, OC7 PTGO7 = OC4, OC8

| R/W-0            | R/W-0                                         | R/W-0            | R/W-0            | R/W-0                              | R/W-0          | R/W-0              | R/W-0  |  |  |

|------------------|-----------------------------------------------|------------------|------------------|------------------------------------|----------------|--------------------|--------|--|--|

| F7MSK1           | F7MSK0                                        | F6MSK1           | F6MSK0           | F5MSK1                             | F5MSK0         | F4MSK1             | F4MSK0 |  |  |

| bit 15           |                                               |                  |                  |                                    |                |                    | bit 8  |  |  |

|                  |                                               |                  |                  |                                    |                |                    |        |  |  |

| R/W-0            | R/W-0                                         | R/W-0            | R/W-0            | R/W-0                              | R/W-0          | R/W-0              | R/W-0  |  |  |

| F3MSK1           | F3MSK0                                        | F2MSK1           | F2MSK0           | F1MSK1                             | F1MSK0         | F0MSK1             | F0MSK0 |  |  |

| bit 7            |                                               |                  |                  |                                    |                |                    | bit 0  |  |  |

|                  |                                               |                  |                  |                                    |                |                    |        |  |  |

| Legend:          |                                               |                  |                  |                                    |                |                    |        |  |  |

| R = Readable bit |                                               | W = Writable bit |                  | U = Unimplemented bit, read as '0' |                |                    |        |  |  |

| -n = Value at    | POR                                           | '1' = Bit is set |                  | '0' = Bit is cle                   | ared           | x = Bit is unknown |        |  |  |

|                  |                                               |                  |                  |                                    |                |                    |        |  |  |

| bit 15-14        | F7MSK<1:0>                                    | : Mask Source    | for Filter 7 bit | I                                  |                |                    |        |  |  |

|                  | 11 = Reserve                                  | ed               |                  |                                    |                |                    |        |  |  |

|                  | 10 = Acceptance Mask 2 registers contain mask |                  |                  |                                    |                |                    |        |  |  |

|                  |                                               | nce Mask 1 reg   | •                |                                    |                |                    |        |  |  |

|                  | •                                             | nce Mask 0 reg   |                  |                                    |                |                    |        |  |  |

| bit 13-12        | F6MSK<1:0>                                    | : Mask Source    | for Filter 6 bit | (same values                       | as bits 15-14) |                    |        |  |  |

| bit 11-10        | F5MSK<1:0>                                    | : Mask Source    | for Filter 5 bit | (same values                       | as bits 15-14) |                    |        |  |  |

| bit 9-8          | F4MSK<1:0>                                    | : Mask Source    | for Filter 4 bit | (same values                       | as bits 15-14) |                    |        |  |  |

| bit 7-6          | F3MSK<1:0>                                    | : Mask Source    | for Filter 3 bit | (same values                       | as bits 15-14) |                    |        |  |  |

| bit 5-4          | F2MSK<1:0>                                    | : Mask Source    | for Filter 2 bit | (same values                       | as bits 15-14) |                    |        |  |  |

|                  |                                               |                  |                  |                                    |                |                    |        |  |  |

F1MSK<1:0>: Mask Source for Filter 1 bit (same values as bits 15-14)

FOMSK<1:0>: Mask Source for Filter 0 bit (same values as bits 15-14)

### REGISTER 21-18: CxFMSKSEL1: CANx FILTERS 7-0 MASK SELECTION REGISTER 1

bit 3-2

bit 1-0

| R/W-0         | R/W-0                             | R/W-0                          | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0    |  |  |  |

|---------------|-----------------------------------|--------------------------------|-----------------|-------------------|------------------|-----------------|----------|--|--|--|

| EDG1MOD       | EDG1POL                           | EDG1SEL3                       | EDG1SEL2        | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT |  |  |  |

| bit 15        | •                                 | •                              |                 | •                 | •                |                 | bit 8    |  |  |  |

|               |                                   |                                |                 |                   |                  |                 |          |  |  |  |

| R/W-0         | R/W-0                             | R/W-0                          | R/W-0           | R/W-0             | R/W-0            | U-0             | U-0      |  |  |  |

| EDG2MOD       | EDG2POL                           | EDG2SEL3                       | EDG2SEL2        | EDG2SEL1          | EDG2SEL0         | —               | —        |  |  |  |

| bit 7         | ·                                 | ·                              |                 | •                 | •                |                 | bit 0    |  |  |  |

|               |                                   |                                |                 |                   |                  |                 |          |  |  |  |

| Legend:       |                                   |                                |                 |                   |                  |                 |          |  |  |  |

| R = Readable  | bit                               | W = Writable                   | oit             | U = Unimplem      | nented bit, read | l as '0'        |          |  |  |  |

| -n = Value at | POR                               | '1' = Bit is set               |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |  |  |  |

|               |                                   |                                |                 |                   |                  |                 |          |  |  |  |

| bit 15        | EDG1MOD: E                        | Edge 1 Edge Sa                 | ampling Mode    | Selection bit     |                  |                 |          |  |  |  |

|               | •                                 | edge-sensitive                 |                 |                   |                  |                 |          |  |  |  |

|               | •                                 | level-sensitive                |                 |                   |                  |                 |          |  |  |  |

| bit 14        |                                   | dge 1 Polarity                 |                 |                   |                  |                 |          |  |  |  |

|               |                                   | programmed f<br>programmed f   |                 |                   |                  |                 |          |  |  |  |

| bit 13-10     | -                                 | :0>: Edge 1 So                 | -               |                   |                  |                 |          |  |  |  |

| DIL 13-10     | 1111 = Fosc                       | <b>0&gt;.</b> Euge 130         |                 | 5                 |                  |                 |          |  |  |  |

|               | 1110 = OSCI                       | pin                            |                 |                   |                  |                 |          |  |  |  |

|               | 1101 = FRC oscillator             |                                |                 |                   |                  |                 |          |  |  |  |

|               | 1100 = Reserved                   |                                |                 |                   |                  |                 |          |  |  |  |

|               | 1011 = Intern<br>1010 = Reser     | al LPRC oscilla                | itor            |                   |                  |                 |          |  |  |  |

|               | 1010 = Reser<br>100x = Reser      |                                |                 |                   |                  |                 |          |  |  |  |

|               | 01xx = Reser                      |                                |                 |                   |                  |                 |          |  |  |  |

|               | 0011 = CTED                       |                                |                 |                   |                  |                 |          |  |  |  |

|               | 0010 = CTED<br>0001 = OC1 r       | •                              |                 |                   |                  |                 |          |  |  |  |

|               | 0001 = OCT1                       |                                |                 |                   |                  |                 |          |  |  |  |

| bit 9         |                                   | Edge 2 Status b                | it              |                   |                  |                 |          |  |  |  |

|               |                                   | -                              |                 | vritten to contro | I the edge sou   | rce.            |          |  |  |  |

|               | 1 = Edge 2 h                      | as occurred                    |                 |                   | 0                |                 |          |  |  |  |

|               | 0 = Edge 2 ha                     | as not occurred                | 1               |                   |                  |                 |          |  |  |  |

| bit 8         |                                   | Edge 1 Status b                |                 |                   |                  |                 |          |  |  |  |

|               |                                   | -                              | 1 and can be v  | vritten to contro | ol the edge sour | rce.            |          |  |  |  |

|               | 1 = Edge 1 ha                     | as occurred<br>as not occurred | I               |                   |                  |                 |          |  |  |  |

| bit 7         | •                                 | Edge 2 Edge Sa                 |                 | Selection bit     |                  |                 |          |  |  |  |

|               |                                   | edge-sensitive                 |                 |                   |                  |                 |          |  |  |  |

|               | -                                 | level-sensitive                |                 |                   |                  |                 |          |  |  |  |

| bit 6         | EDG2POL: E                        | dge 2 Polarity                 | Select bit      |                   |                  |                 |          |  |  |  |

|               |                                   | programmed f                   |                 |                   |                  |                 |          |  |  |  |

|               | 0 = Edge 2 is                     | programmed f                   | or a negative e | edge response     |                  |                 |          |  |  |  |

|               | he TGEN bit is<br>0G2SELx bits fi |                                |                 |                   | selected as the  | e Edge 2 sourc  | e in the |  |  |  |

# REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

### REGISTER 23-1: ADxCON1: ADCx CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Clock Source Select bits<br><u>If SSRCG = 1:</u><br>111 = Reserved<br>110 = PTGO15 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>101 = PTGO14 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>100 = PTGO13 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>011 = PTGO12 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion<br>001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion<br>000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion<br><u>If SSRCG = 0:</u><br>111 = Internal counter ends sampling and starts conversion (auto-convert)<br>110 = CTMU ends sampling and starts conversion |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 101 = PWM secondary Special Event Trigger ends sampling and starts conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | 100 = Timer5 compare ends sampling and starts conversion<br>011 = PWM primary Special Event Trigger ends sampling and starts conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | 010 = Timer3 compare ends sampling and starts conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | <ul><li>001 = Active transition on the INTO pin ends sampling and starts conversion</li><li>000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | See SSRC<2:0> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 3   | SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS<1:0> = $01 \text{ or } 1x$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>In 12-Bit Mode (AD12B = 1), SIMSAM is Unimplemented and is Read as '0':</li> <li>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x), or samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01)</li> <li>0 = Samples multiple channels individually in sequence</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| bit 2   | ASAM: ADCx Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |