Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 48K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 30x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

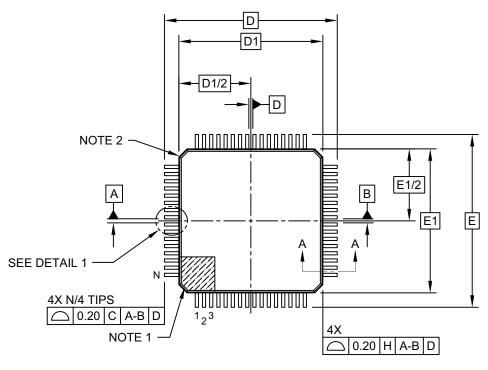

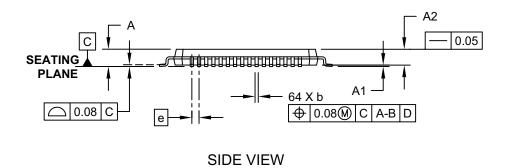

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gm706-e-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-1: PINOUT I/O DESCRIPTIONS

| Pin Name                                    | Pin<br>Type | Buffer<br>Type         | PPS              | Description                                                                                                                                                                        |

|---------------------------------------------|-------------|------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN49                                    | Ι           | Analog                 | No               | Analog Input Channels 0-49.                                                                                                                                                        |

| CLKI                                        | I           | ST/<br>CMOS            | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |

| CLKO                                        | 0           | _                      | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                                        | I           | ST/                    | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |

| OSC2                                        | I/O         | CMOS<br>—              | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |

| SOSCI                                       | I           | ST/<br>CMOS            | No               | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                     |

| SOSCO                                       | 0           | _                      | No               | 32.768 kHz low-power oscillator crystal output.                                                                                                                                    |

| IC1-IC8                                     | I           | ST                     | Yes              | Input Capture Inputs 1 through 8.                                                                                                                                                  |

| OCFA<br>OCFB<br>OC1-OC8                     | <br> <br>   | ST<br>ST               | Yes<br>No<br>Yes | Output Compare Fault A input (for compare channels).<br>Output Compare Fault B input (for compare channels).<br>Output Compare 1 through 8.                                        |

| INT0                                        |             | ST                     | No               | External Interrupt 0.                                                                                                                                                              |

| INT1                                        | l i         | ST                     | Yes              | External Interrupt 1.                                                                                                                                                              |

| INT2                                        | 1           | ST                     | Yes              | External Interrupt 2.                                                                                                                                                              |

| INT3                                        | I.          | ST                     | No               | External Interrupt 3.                                                                                                                                                              |

| INT4                                        | Ι           | ST                     | No               | External Interrupt 4.                                                                                                                                                              |

| RA0-RA4, RA7-RA12,<br>RA14-RA15             | I/O         | ST                     | Yes              | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                                    | I/O         | ST                     | Yes              | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                              | I/O         | ST                     | Yes              | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD1-RD6, RD8,<br>RD12-RD15                  | I/O         | ST                     | Yes              | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE0-RE1, RE8-RE9,<br>RE12-RE15              | I/O         | ST                     | Yes              | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0-RF1, RF4-RF7,<br>RF9-RF10,<br>RF12-RF13 | I/O         | ST                     | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG0-RG3,<br>RG6-RG15                        | I/O         | ST                     | Yes              | PORTG is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                                        | Ι           | ST                     | No               | Timer1 external clock input.                                                                                                                                                       |

| T2CK                                        |             | ST                     | Yes              | Timer2 external clock input.                                                                                                                                                       |

| T3CK                                        |             | ST                     | No               | Timer3 external clock input.                                                                                                                                                       |

| T4CK<br>T5CK                                |             | ST<br>ST               | No<br>No         | Timer4 external clock input.                                                                                                                                                       |

| T6CK                                        |             | ST                     | NO               | Timer5 external clock input.<br>Timer6 external clock input.                                                                                                                       |

| T7CK                                        |             | ST                     | No               | Timer7 external clock input.                                                                                                                                                       |

| T8CK                                        | l i         | ST                     | No               | Timer8 external clock input.                                                                                                                                                       |

| T9CK                                        | i           | ST                     | No               | Timer9 external clock input.                                                                                                                                                       |

| Legend: CMOS = CM<br>ST = Schmit            | tt Trigg    | mpatible<br>er input v | vith CN          | or output Analog = Analog input P = Power<br>IOS levels O = Output I = Input                                                                                                       |

| PPS = Perip                                 |             |                        |                  | TTL = TTL input buffer<br>es. For more information. see the " <b>Pin Diagrams</b> " section for pin                                                                                |

Note 1: This pin is not available on all devices. For more information, see the "Pin Diagrams" section for pin availability.

2: AVDD must be connected at all times.

#### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0            | U-0 | U-0            | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-----|----------------|-------|--------------|------------------|--------|-------|

| —              |     | —              | —     | —            | —                | —      | —     |

| bit 15         |     |                |       |              |                  |        | bit 8 |

|                |     |                |       |              |                  |        |       |

| W-0            | W-0 | W-0            | W-0   | W-0          | W-0              | W-0    | W-0   |

|                |     |                | NVMKI | EY<7:0>      |                  |        |       |

| bit 7          |     |                |       |              |                  |        | bit 0 |

|                |     |                |       |              |                  |        |       |

| Legend:        |     |                |       |              |                  |        |       |

| R = Readable I | bit | W = Writable b | oit   | U = Unimpler | mented bit, read | as '0' |       |

|                |     |                |       |              |                  |        |       |

'0' = Bit is cleared

bit 15-8 Unimplemented: Read as '0'

-n = Value at POR

bit 7-0 NVMKEY<7:0>: NVM Key Register (write-only) bits

'1' = Bit is set

#### REGISTER 5-5: NVMSRCADRH: NONVOLATILE DATA MEMORY UPPER ADDRESS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-x | R/W-x | R/W-x | R/W-x    | R/W-x      | R/W-x | R/W-x | R/W-x |

|-------|-------|-------|----------|------------|-------|-------|-------|

|       |       |       | NVMSRCAD | DRH<23:16> |       |       |       |

| bit 7 |       |       |          |            |       |       | bit 0 |

|       |       |       |          |            |       |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMSRCADRH<23:16>: Nonvolatile Data Memory Upper Address bits

x = Bit is unknown

|                                | Vector  | IRQ        |                   | Interrupt Bit Location |          |              |  |

|--------------------------------|---------|------------|-------------------|------------------------|----------|--------------|--|

| Interrupt Source               | #       | #          | IVT Address       | Flag                   | Enable   | Priority     |  |

| SPI3E – SPI3 Error             | 98      | 90         | 0x0000C8          | IFS5<10>               | IEC5<10> | IPC22<10:8>  |  |

| SPI3 – SPI3 Transfer Done      | 99      | 91         | 0x0000CA          | IFS5<11>               | IEC5<11> | IPC22<14:12> |  |

| Reserved                       | 100-101 | 92-93      | 0x0000CC-0x0000CE | _                      | _        | —            |  |

| PWM1 – PWM Generator 1         | 102     | 94         | 0x0000D0          | IFS5<14>               | IEC5<14> | IPC23<10:8>  |  |

| PWM2 – PWM Generator 2         | 103     | 95         | 0x0000D2          | IFS5<15>               | IEC5<15> | IPC23<14:12> |  |

| PWM3 – PWM Generator 3         | 104     | 96         | 0x0000D4          | IFS6<0>                | IEC6<0>  | IPC24<2:0>   |  |

| PWM4 – PWM Generator 4         | 105     | 97         | 0x0000D6          | IFS6<1>                | IEC6<1>  | IPC24<6:4>   |  |

| PWM5 – PWM Generator 5         | 106     | 98         | 0x0000D8          | IFS6<2>                | IEC6<2>  | IPC24<10:8>  |  |

| PWM6 – PWM Generator 6         | 107     | 99         | 0x0000DA          | IFS6<3>                | IEC6<3>  | IPC24<14:12> |  |

| Reserved                       | 108-149 | 100-141    | 0x0000DC-0x00012E | _                      | _        | —            |  |

| ICD – ICD Application          | 150     | 142        | 0x000142          | IFS8<14>               | IEC8<14> | IPC35<10:8>  |  |

| JTAG – JTAG Programming        | 151     | 143        | 0x000130          | IFS8<15>               | IEC8<15> | IPC35<14:12> |  |

| Reserved                       | 152     | 144        | 0x000134          | _                      | —        | —            |  |

| PTGSTEP – PTG Step             | 153     | 145        | 0x000136          | IFS9<1>                | IEC9<1>  | IPC36<6:4>   |  |

| PTGWDT – PTG Watchdog Time-out | 154     | 146        | 0x000138          | IFS9<2>                | IEC9<2>  | IPC36<10:8>  |  |

| PTG0 – PTG Interrupt 0         | 155     | 147        | 0x00013A          | IFS9<3>                | IEC9<3>  | IPC36<14:12> |  |

| PTG1 – PTG Interrupt 1         | 156     | 148        | 0x00013C          | IFS9<4>                | IEC9<4>  | IPC37<2:0>   |  |

| PTG2 – PTG Interrupt 2         | 157     | 149        | 0x00013E          | IFS9<5>                | IEC9<5>  | IPC37<6:4>   |  |

| PTG3 – PTG Interrupt 3         | 158     | 150        | 0x000140          | IFS9<6>                | IEC9<6>  | IPC37<10:8>  |  |

| Reserved                       | 159-245 | 151-245    | 0x000142-0x0001FE | _                      | _        | _            |  |

|                                | Lowe    | est Natura | Order Priority    |                        |          |              |  |

#### TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGM6XX/7XX devices only.

**2:** This interrupt source is not available on 44-pin devices.

| U-0          | R/W-0     | R/W-0                                 | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|-----------|---------------------------------------|-------|-------------------|-----------------|-----------------|-------|

| —            |           |                                       |       | IC6R<6:0>         |                 |                 |       |

| bit 15       |           |                                       |       |                   |                 |                 | bit 8 |

|              |           |                                       |       |                   |                 |                 |       |

| U-0          | R/W-0     | R/W-0                                 | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| _            |           |                                       |       | IC5R<6:0>         |                 |                 |       |

| bit 7        |           |                                       |       |                   |                 |                 | bit 0 |

|              |           |                                       |       |                   |                 |                 |       |

| Legend:      |           |                                       |       |                   |                 |                 |       |

| R = Readab   | ole bit   | W = Writable                          | bit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR    | '1' = Bit is set                      |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              |           |                                       |       |                   |                 |                 |       |

| bit 15       | Unimpleme | ented: Read as '                      | 0'    |                   |                 |                 |       |

| bit 14-8     |           | Assign Input Ca<br>11-2 for input pin |       |                   | onding RPn P    | in bits         |       |

|              | 1111100 = | Input tied to RPI                     | 124   |                   |                 |                 |       |

|              | •         |                                       |       |                   |                 |                 |       |

|              | •         |                                       |       |                   |                 |                 |       |

|              | 0000001 = | Input tied to CM                      | P1    |                   |                 |                 |       |

|              | 0000000 = | Input tied to Vss                     | ;     |                   |                 |                 |       |

| bit 7        | Unimpleme | ented: Read as '                      | 0'    |                   |                 |                 |       |

| bit 6-0      |           | Assign Input Ca<br>11-2 for input pin |       |                   | onding RPn P    | in bits         |       |

|              | 1111100 = | Input tied to RPI                     | 124   |                   |                 |                 |       |

|              | •         |                                       |       |                   |                 |                 |       |

|              | •         |                                       |       |                   |                 |                 |       |

|              | 0000001 = | Input tied to CM                      | P1    |                   |                 |                 |       |

|              |           | Input tied to Vss                     |       |                   |                 |                 |       |

|              |           |                                       |       |                   |                 |                 |       |

#### REGISTER 11-6: RPINR9: PERIPHERAL PIN SELECT INPUT REGISTER 9

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = Capture timer is unsynchronized

- 11110 = Capture timer is unsynchronized

- 11101 = Capture timer is unsynchronized

- 11100 = CTMU trigger is the source for the capture timer synchronization

- 11011 = ADC1 interrupt is the source for the capture timer synchronization<sup>(5)</sup>

- 11010 = Analog Comparator 3 is the source for the capture timer synchronization<sup>(5)</sup>

- 11001 = Analog Comparator 2 is the source for the capture timer synchronization<sup>(5)</sup>

- 11000 = Analog Comparator 1 is the source for the capture timer synchronization<sup>(5)</sup>

- 10111 = Input Capture 8 interrupt is the source for the capture timer synchronization

- 10110 = Input Capture 7 interrupt is the source for the capture timer synchronization 10101 = Input Capture 6 interrupt is the source for the capture timer synchronization

- 10100 = Input Capture 5 interrupt is the source for the capture timer synchronization

- 10011 = Input Capture 4 interrupt is the source for the capture timer synchronization

- 10010 = Input Capture 3 interrupt is the source for the capture timer synchronization

- 10001 = Input Capture 2 interrupt is the source for the capture timer synchronization

- 10000 = Input Capture 1 interrupt is the source for the capture timer synchronization

- 01111 = GP Timer5 is the source for the capture timer synchronization

- 01110 = GP Timer4 is the source for the capture timer synchronization

- 01101 = GP Timer3 is the source for the capture timer synchronization 01100 = GP Timer2 is the source for the capture timer synchronization

- 01100 = GP Timer2 is the source for the capture timer synchronization 01011 = GP Timer1 is the source for the capture timer synchronization

- 01011 = OF Time is the source for the capture time synchronization (6)

- 01001 = Capture timer is unsynchronized

- 01000 = Output Compare 8 is the source for the capture timer synchronization

- 00111 = Output Compare 7 is the source for the capture timer synchronization

- 00110 = Output Compare 6 is the source for the capture timer synchronization

- 00101 = Output Compare 5 is the source for the capture timer synchronization

- 00100 = Output Compare 4 is the source for the capture timer synchronization

- 00011 = Output Compare 3 is the source for the capture timer synchronization

- 00010 = Output Compare 2 is the source for the capture timer synchronization

- 00001 = Output Compare 1 is the source for the capture timer synchronization

- 00000 = Capture timer is unsynchronized

- **Note 1:** The IC32 bit in both the Odd and Even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x module (ICx) has one PTG input source. See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1, IC5

PTGO9 = IC2, IC6

PTGO10 = IC3, IC7

PTGO11 = IC4, IC8

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXGM3XX/6XX/7XX devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring: PWMLOCK = 0.

To gain write access to these locked registers, the user application must write two consecutive values of 0xABCD and 0x4321 to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWM1 WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

| -                                                                                                | -                                     | high externally in order to clear and disable the fault<br>ter requires unlock sequence                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mov #0xabc<br>mov #0x432<br>mov #0x000<br>mov w10, F<br>mov w11, F<br>mov w0, FC                 | 21, w11<br>00, w0<br>PWMKEY<br>PWMKEY | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |

|                                                                                                  |                                       | larity using the IOCON1 register<br>er requires unlock sequence                                                                                                                                                                                                                                   |

| <pre>mov #0xabc<br/>mov #0x432<br/>mov #0xF00<br/>mov w10, F<br/>mov w11, F<br/>mov w0, IC</pre> | 21, w11<br>20, w0<br>PWMKEY<br>PWMKEY | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |

| R/W-0           | R/W-0         | R/W-0                                          | R/W-0              | R/W-0                              | R/W-0                                    | U-0               | U-0           |  |

|-----------------|---------------|------------------------------------------------|--------------------|------------------------------------|------------------------------------------|-------------------|---------------|--|

| PHR             | PHF           | PLR                                            | PLF                | FLTLEBEN                           | CLLEBEN                                  |                   |               |  |

| bit 15          |               |                                                |                    |                                    |                                          |                   | bit           |  |

| U-0             | U-0           | R/W-0                                          | R/W-0              | R/W-0                              | R/W-0                                    | R/W-0             | R/W-0         |  |

| _               | _             | BCH <sup>(1)</sup>                             | BCL <sup>(1)</sup> | BPHH                               | BPHL                                     | BPLH              | BPLL          |  |

| bit 7           |               | 20                                             |                    |                                    |                                          |                   | bit           |  |

| Legend:         |               |                                                |                    |                                    |                                          |                   |               |  |

| R = Readable    | bit           | W = Writable                                   | bit                | U = Unimpler                       | nented bit, read                         | l as '0'          |               |  |

| -n = Value at F | POR           | '1' = Bit is set                               |                    | '0' = Bit is cle                   | ared                                     | x = Bit is unkr   | nown          |  |

| bit 15          |               | H Rising Edge                                  | Triggor Enabl      | o hit                              |                                          |                   |               |  |

| JIL 15          |               | • •                                            |                    |                                    | Blanking count                           | ter               |               |  |

|                 |               |                                                |                    | sing edge of PV                    |                                          |                   |               |  |

| bit 14          | PHF: PWMxH    | H Falling Edge                                 | Trigger Enab       | le bit                             |                                          |                   |               |  |

|                 |               |                                                |                    |                                    | e Blanking coun                          | ter               |               |  |

|                 | 0             | 0 0                                            | 0                  | Illing edge of P                   | WMxH                                     |                   |               |  |

| bit 13          |               | Rising Edge                                    |                    |                                    |                                          |                   |               |  |

|                 |               |                                                |                    | sing edge of PV                    | Blanking count                           | er                |               |  |

| bit 12          |               | _uge blanking                                  |                    |                                    | VIVIAE                                   |                   |               |  |

|                 |               |                                                |                    |                                    | Blanking count                           | ter               |               |  |

|                 | Ų             | 0                                              | 00                 | alling edge of P                   | Ų                                        |                   |               |  |

| bit 11          |               | •                                              | • •                | anking Enable I                    |                                          |                   |               |  |

|                 |               |                                                |                    | he selected Fail to the selected   |                                          |                   |               |  |

| bit 10          | CLLEBEN: C    | Current-Limit Le                               | ading-Edge E       | Blanking Enable                    | e bit                                    |                   |               |  |

|                 |               |                                                |                    | he selected cur<br>to the selected | rrent-limit input<br>I current-limit inj | put               |               |  |

| bit 9-6         | Unimplemen    | ted: Read as '                                 | 0'                 |                                    |                                          |                   |               |  |

| bit 5           | BCH: Blankin  | ng in Selected I                               | Blanking Sign      | al High Enable                     | bit <sup>(1)</sup>                       |                   |               |  |

|                 |               | nking (of currer                               |                    |                                    | nals) when seled                         | cted blanking s   | ignal is high |  |

| bit 4           | BCL: Blankin  | g in Selected E                                | Blanking Signa     | al Low Enable b                    | <sub>Dit</sub> (1)                       |                   |               |  |

|                 |               | nking (of currer                               |                    |                                    | nals) when seled                         | cted blanking s   | ignal is low  |  |

| bit 3           | BPHH: Blank   | <b>3PHH:</b> Blanking in PWMxH High Enable bit |                    |                                    |                                          |                   |               |  |

|                 |               | nking (of currer                               |                    |                                    | nals) when PWN                           | /IxH output is h  | igh           |  |

| bit 2           | BPHL: Blanki  | ing in PWMxH                                   | Low Enable b       | pit                                |                                          |                   |               |  |

|                 |               | nking (of currer                               |                    |                                    | nals) when PWN                           | /IxH output is lo | W             |  |

| bit 1           | BPLH: Blanki  | ing in PWMxL                                   | High Enable I      | oit                                |                                          |                   |               |  |

|                 |               | nking (of currer                               |                    |                                    | als) when PWN                            | /lxL output is hi | gh            |  |

|                 | 0 = No blanki | ing when PWM                                   | xL output is h     | igh                                |                                          |                   |               |  |

| bit 0           |               |                                                | -                  | -                                  |                                          |                   |               |  |

#### REGISTER 16-22: LEBCONX: LEADING-EDGE BLANKING CONTROL REGISTER x

Note 1: The blanking signal is selected via the BLANKSELx bits in the AUXCONx register.

### REGISTER 17-19: INTxHLDH: INTERVAL TIMERX HOLD HIGH WORD REGISTER

| R/W-0                                                                | R/W-0                                                              | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|--------------------------------------------------------------------|-------|-------|----------|-------|-------|-------|

|                                                                      |                                                                    |       | INTHL | D<31:24> |       |       |       |

| bit 15                                                               |                                                                    |       |       |          |       |       | bit 8 |

|                                                                      |                                                                    |       |       |          |       |       |       |

| R/W-0                                                                | R/W-0                                                              | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|                                                                      |                                                                    |       | INTHL | D<23:16> |       |       |       |

| bit 7                                                                |                                                                    |       |       |          |       |       | bit 0 |

|                                                                      |                                                                    |       |       |          |       |       |       |

| Legend:                                                              |                                                                    |       |       |          |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                    |       |       |          |       |       |       |

| -n = Value at P                                                      | ue at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |       |          | nown  |       |       |

| •                                                                    |                                                                    |       |       |          |       |       |       |

bit 15-0 INTHLD<31:16>: Holding Register for Reading and Writing INTxTMRH bits

#### REGISTER 17-20: INTxHLDL: INTERVAL TIMERx HOLD LOW WORD REGISTER

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                                                                      |       |                  | INTHL | .D<15:8>                                |       |       |       |

| bit 15                                                               |       |                  |       |                                         |       |       | bit 8 |

|                                                                      |       |                  |       |                                         |       |       |       |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                                                                      |       |                  | INTH  | LD<7:0>                                 |       |       |       |

| bit 7                                                                |       |                  |       |                                         |       |       | bit 0 |

|                                                                      |       |                  |       |                                         |       |       |       |

| Legend:                                                              |       |                  |       |                                         |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                                         |       |       |       |

| -n = Value at P                                                      | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |

|                                                                      |       |                  |       |                                         |       |       |       |

bit 15-0 INTHLD<15:0>: Holding Register for Reading and Writing INTxTMRL bits

### 23.2 ADCx Helpful Tips

- 1. The SMPIx control bits in the ADxCON2 registers:

- a) Determine when the ADCx interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the ADxCON2 register is set to '1', this determines when the ADCx analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADCx Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADCx buffer used in this mode. The ADCx Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using the DMA peripheral.

- When the DMA module is disabled (ADDMAEN = 0), the ADCx has 16 result buffers. ADCx conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1.c) above. There is no relationship between the ANx input being measured and which ADCx buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is enabled (ADDMAEN = 1), the ADCx module has only 1 ADCx result buffer (i.e., ADC1BUF0) per ADCx peripheral and the ADCx conversion result must be read, either by the CPU or DMA Controller, before the next ADCx conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (ADxCON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADCx. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (ADxCON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

- 5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for AN0, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUXA selections use AN0-AN2. Carefully study the ADCx block diagram to determine the configuration that will best suit your application. Configuration examples are available in the "dsPIC33/PIC24 Family Reference Manual", "Analog-to-Digital Converter (ADC)" (DS70621)

## 25.0 PERIPHERAL TRIGGER GENERATOR (PTG) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Peripheral Trigger Generator (PTG)" (DS70669), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

#### 25.1 Module Introduction

The Peripheral Trigger Generator (PTG) provides a means to schedule complex, high-speed peripheral operations that would be difficult to achieve using software. The PTG module uses 8-bit commands, called "steps", that the user writes to the PTG Queue register (PTGQUE0-PTQUE15), which performs operations, such as wait for input signal, generate output trigger and wait for timer.

The PTG module has the following major features:

- Multiple Clock Sources

- Two 16-Bit General Purpose Timers

- Two 16-Bit General Limit Counters

- Configurable for Rising or Falling Edge Triggering

- Generates Processor Interrupts to Include:

- Four configurable processor interrupts

- Interrupt on a step event in Single-Step modeInterrupt on a PTG Watchdog Timer time-out

- Able to Receive Trigger Signals from these Peripherals:

- ADC

- PWM

- Output Compare

- Input Capture

- Op Amp/Comparator

- INT2

- Able to Trigger or Synchronize to these Peripherals:

- Watchdog Timer

- Output Compare

- Input Capture

- ADC

- PWM

- Op Amp/Comparator

| R/W-0           | R/W-0                          | R/W-0                                | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|-----------------|--------------------------------|--------------------------------------|-----------------|------------------|------------------|-----------------|---------|

| PTGCLK2         | PTGCLK1                        | PTGCLK0                              | PTGDIV4         | PTGDIV3          | PTGDIV2          | PTGDIV1         | PTGDIV0 |

| bit 15          | •                              |                                      |                 |                  |                  |                 | bit 8   |

|                 |                                |                                      |                 |                  |                  |                 |         |

| R/W-0           | R/W-0                          | R/W-0                                | R/W-0           | U-0              | R/W-0            | R/W-0           | R/W-0   |

| PTGPWD3         | PTGPWD2                        | PTGPWD1                              | PTGPWD0         | —                | PTGWDT2          | PTGWDT1         | PTGWDT0 |

| bit 7           |                                |                                      |                 |                  |                  |                 | bit 0   |

| Legend:         |                                |                                      |                 |                  |                  |                 |         |

| R = Readable    | bit                            | W = Writable                         | bit             | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at F | POR                            | '1' = Bit is set                     |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|                 |                                |                                      |                 | <b>a</b>         |                  |                 |         |

| bit 15-13       |                                | >: Select PTG                        | Module Clock    | Source bits      |                  |                 |         |

|                 | 111 = Reserv<br>110 = Reserv   |                                      |                 |                  |                  |                 |         |

|                 |                                | odule clock so                       | urce will be T3 | CLK              |                  |                 |         |

|                 |                                | odule clock so                       |                 |                  |                  |                 |         |

|                 |                                | odule clock so                       |                 |                  |                  |                 |         |

|                 |                                | odule clock so<br>odule clock so     |                 |                  |                  |                 |         |

|                 |                                | odule clock so                       |                 |                  |                  |                 |         |

| bit 12-8        | PTGDIV<4:0>                    | -: PTG Module                        | Clock Presca    | ler (divider) bi | ts               |                 |         |

|                 | 11111 = Divid<br>11110 = Divid |                                      |                 |                  |                  |                 |         |

|                 | •                              |                                      |                 |                  |                  |                 |         |

|                 | •                              |                                      |                 |                  |                  |                 |         |

|                 | 00001 = Divic<br>00000 = Divic | •                                    |                 |                  |                  |                 |         |

| bit 7-4         | PTGPWD<3:0                     | <b>0&gt;:</b> PTG Trigge             | er Output Pulse | e-Width bits     |                  |                 |         |

|                 |                                | gger outputs ar                      |                 |                  |                  |                 |         |

|                 | 1110 = All trig                | gger outputs ar                      | e 15 PIG cloc   | k cycles wide    |                  |                 |         |

|                 | •                              |                                      |                 |                  |                  |                 |         |

|                 | •                              |                                      |                 |                  |                  |                 |         |

|                 |                                | gger outputs ar<br>gger outputs ar   |                 |                  |                  |                 |         |

| bit 3           | Unimplement                    | ted: Read as '                       | 0'              |                  |                  |                 |         |

| bit 2-0         | PTGWDT<2:0                     | D>: Select PTO                       | Watchdog Tir    | mer Time-out (   | Count Value bits | 3               |         |

|                 |                                | log Timer will t                     |                 |                  |                  |                 |         |

|                 |                                | log Timer will t<br>log Timer will t |                 |                  |                  |                 |         |

|                 |                                | log Timer will t                     |                 |                  |                  |                 |         |

|                 |                                | log Timer will t                     |                 |                  |                  |                 |         |

|                 | 010 = Watchd                   | loa Timer will t                     | ime-out after 1 | 6 PTG clocks     |                  |                 |         |

|                 |                                |                                      |                 |                  |                  |                 |         |

|                 | 001 = Watchd                   | log Timer will t                     | ime-out after 8 |                  |                  |                 |         |

#### REGISTER 25-2: PTGCON: PTG CONTROL REGISTER

# REGISTER 25-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER<sup>(1,2)</sup> (CONTINUED)

| bit 4   | OC1CS: Clock Source for OC1 bit                                                                                                                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Generates clock pulse when the broadcast command is executed                                                                                                                               |

|         | 0 = Does not generate clock pulse when the broadcast command is executed                                                                                                                       |

| bit 3   | OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| bit 2   | OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| bit 1   | OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| bit 0   | OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                             |

|         | <ul> <li>1 = Generates trigger/synchronization when the broadcast command is executed</li> <li>0 = Does not generate trigger/synchronization when the broadcast command is executed</li> </ul> |

| Note 1: | This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and                                                                                                       |

- PTGSTRT = 1).

- 2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

# REGISTER 27-10: ALRMVAL (WHEN ALRMPTR<1:0> = 00): ALARM MINUTES AND SECONDS VALUE REGISTER

| U-0    | R/W-x   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| —      | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                                                                  |                      |                    |  |

|-------------------|------------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                                 | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15    | Unimplemented: Read as '0'                                          |

|-----------|---------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

| bit 7     | Unimplemented: Read as '0'                                          |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

|           |                                                                     |

#### 29.2 Programmable CRC Control Registers

#### REGISTER 29-1: CRCCON1: CRC CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0 | R-0    | R-0    | R-0    | R-0    | R-0    |

|--------|-----|-------|--------|--------|--------|--------|--------|

| CRCEN  | —   | CSIDL | VWORD4 | VWORD3 | VWORD2 | VWORD1 | VWORD0 |

| bit 15 |     |       |        |        |        |        | bit 8  |

| R-0    | R-1    | R/W-0   | R/W-0 | R/W-0   | U-0 | U-0 | U-0   |

|--------|--------|---------|-------|---------|-----|-----|-------|

| CRCFUL | CRCMPT | CRCISEL | CRCGO | LENDIAN | —   | —   | —     |

| bit 7  |        |         |       |         |     |     | bit 0 |

| Legend:           |                                                                 |                      |                    |  |

|-------------------|-----------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | eadable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                                | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15   | CRCEN: CRC Enable bit                                                                                                                                                             |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>1 = CRC module is enabled</li> <li>0 = CRC module is disabled; all state machines, pointers and CRCWDAT/CRCDAT are reset, other<br/>SFRs are not reset</li> </ul>        |

| bit 14   | Unimplemented: Read as '0'                                                                                                                                                        |

| bit 13   | CSIDL: CRC Stop in Idle Mode bit                                                                                                                                                  |

|          | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                           |

| bit 12-8 | VWORD<4:0>: Valid Word Pointer Value bits                                                                                                                                         |

|          | Indicates the number of valid words in the FIFO; has a maximum value of 8 when PLEN<4:0> > 7 or 16 when PLEN<4:0> $\leq$ 7                                                        |

| bit 7    | CRCFUL: CRC FIFO Full bit                                                                                                                                                         |

|          | 1 = FIFO is full<br>0 = FIFO is not full                                                                                                                                          |

| bit 6    | CRCMPT: CRC FIFO Empty Bit                                                                                                                                                        |

|          | <ul><li>1 = FIFO is empty</li><li>0 = FIFO is not empty</li></ul>                                                                                                                 |

| bit 5    | CRCISEL: CRC Interrupt Selection bit                                                                                                                                              |

|          | <ul> <li>1 = Interrupt on FIFO empty; final word of data is still shifting through CRC</li> <li>0 = Interrupt on shift complete and CRCWDAT results are ready</li> </ul>          |

| bit 4    | CRCGO: CRC Start bit                                                                                                                                                              |

|          | <ul> <li>1 = Start CRC serial shifter</li> <li>0 = CRC serial shifter is turned off</li> </ul>                                                                                    |

| bit 3    | LENDIAN: Data Word Little-Endian Configuration bit                                                                                                                                |

|          | <ul> <li>1 = Data word is shifted into the CRC starting with the LSb (little endian)</li> <li>0 = Data word is shifted into the CRC starting with the MSb (big endian)</li> </ul> |

| bit 2-0  | Unimplemented: Read as '0'                                                                                                                                                        |

|          |                                                                                                                                                                                   |

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |              | Description                        | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-----------------|--------------|------------------------------------|---------------|----------------|--------------------------|

| 72                 | SL                   | SL f            |              | f = Left Shift f                   | 1             | 1              | C,N,OV,Z                 |

|                    |                      | SL              | f,WREG       | WREG = Left Shift f                | 1             | 1              | C,N,OV,Z                 |

|                    |                      | SL              | Ws,Wd        | Wd = Left Shift Ws                 | 1             | 1              | C,N,OV,Z                 |

|                    |                      | SL              | Wb,Wns,Wnd   | Wnd = Left Shift Wb by Wns         | 1             | 1              | N,Z                      |

|                    |                      | SL              | Wb,#lit5,Wnd | Wnd = Left Shift Wb by lit5        | 1             | 1              | N,Z                      |

| 73                 | SUB                  | SUB             | Acc          | Subtract Accumulators              | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | SUB             | f            | f = f – WREG                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUB             | f,WREG       | WREG = f – WREG                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUB             | #lit10,Wn    | Wn = Wn - lit10                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUB             | Wb,Ws,Wd     | Wd = Wb – Ws                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUB             | Wb,#lit5,Wd  | Wd = Wb – lit5                     | 1             | 1              | C,DC,N,OV,Z              |

| 74                 | SUBB                 | SUBB            | f            | $f = f - WREG - (\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBB            | f,WREG       | WREG = $f - WREG - (\overline{C})$ | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBB            | #lit10,Wn    | $Wn = Wn - lit10 - (\overline{C})$ | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBB            | Wb,Ws,Wd     | $Wd = Wb - Ws - (\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBB            | Wb,#lit5,Wd  | $Wd = Wb - lit5 - (\overline{C})$  | 1             | 1              | C,DC,N,OV,Z              |

| 75                 | SUBR                 | SUBR            | f            | f = WREG – f                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBR            | f,WREG       | WREG = WREG – f                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBR            | Wb,Ws,Wd     | Wd = Ws – Wb                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBR            | Wb,#lit5,Wd  | Wd = lit5 – Wb                     | 1             | 1              | C,DC,N,OV,Z              |

| 76                 | SUBBR                | SUBBR           | f            | $f = WREG - f - (\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBBR           | f,WREG       | WREG = WREG – f – $(\overline{C})$ | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBBR           | Wb,Ws,Wd     | $Wd = Ws - Wb - (\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | SUBBR           | Wb,#lit5,Wd  | $Wd = lit5 - Wb - (\overline{C})$  | 1             | 1              | C,DC,N,OV,Z              |

| 77                 | SWAP                 | SWAP.b          | Wn           | Wn = nibble swap Wn                | 1             | 1              | None                     |

|                    |                      | SWAP            | Wn           | Wn = byte swap Wn                  | 1             | 1              | None                     |

| 78                 | TBLRDH               | TBLRDH          | Ws,Wd        | Read Prog<23:16> to Wd<7:0>        | 1             | 5              | None                     |

| 79                 | TBLRDL               | TBLRDL          | Ws,Wd        | Read Prog<15:0> to Wd              | 1             | 5              | None                     |

| 80                 | TBLWTH               | TBLWTH          | Ws,Wd        | Write Ws<7:0> to Prog<23:16>       | 1             | 2              | None                     |

| 81                 | TBLWTL               | TBLWTL          | Ws,Wd        | Write Ws to Prog<15:0>             | 1             | 2              | None                     |

| 82                 | ULNK                 | ULNK            |              | Unlink Frame Pointer               | 1             | 1              | SFA                      |

| 83                 | XOR                  | XOR             | f            | f = f .XOR. WREG                   | 1             | 1              | N,Z                      |

|                    |                      | XOR             | f,WREG       | WREG = f .XOR. WREG                | 1             | 1              | N,Z                      |

|                    |                      | XOR             | #lit10,Wn    | Wd = lit10 .XOR. Wd                | 1             | 1              | N,Z                      |

|                    |                      | XOR             | Wb,Ws,Wd     | Wd = Wb .XOR. Ws                   | 1             | 1              | N,Z                      |

|                    |                      | XOR             | Wb,#lit5,Wd  | Wd = Wb .XOR. lit5                 | 1             | 1              | N,Z                      |

| 84                 | ZE                   | ZE              | Ws,Wnd       | Wnd = Zero-extend Ws               | 1             | 1              | C,Z,N                    |

#### TABLE 31-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

# dsPIC33EPXXXGM3XX/6XX/7XX

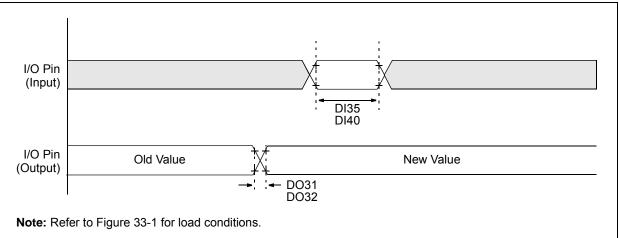

#### TABLE 33-20: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |            |

|--------------------|--------|-----------------------------------|-------------------------------------------------------|---------------------|------|-------|------------|

| Param<br>No.       | Symbol | Characteristic                    | Min.                                                  | Тур. <sup>(1)</sup> | Max. | Units | Conditions |

| DO31               | TioR   | Port Output Rise Time             | _                                                     | 5                   | 10   | ns    |            |

| DO32               | TIOF   | Port Output Fall Time             |                                                       | 5                   | 10   | ns    |            |

| DI35               | TINP   | INTx Pin High or Low Time (input) | 20                                                    | _                   | _    | ns    |            |

| DI40               | Trbp   | CNx High or Low Time (input)      | 2                                                     | _                   | _    | Тсү   |            |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

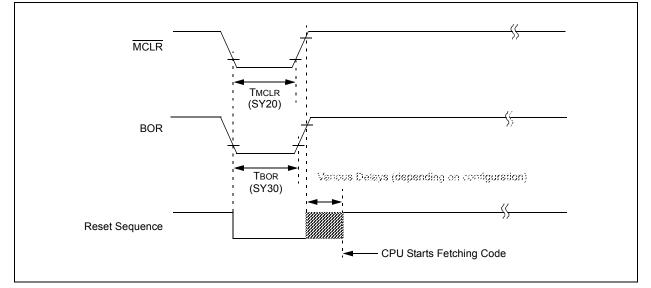

#### FIGURE 33-4: BOR AND MASTER CLEAR RESET TIMING CHARACTERISTICS

| AC CHARACTERISTICS                 |        |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 1): 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |      |       |                                                                  |  |  |  |

|------------------------------------|--------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------------------------------------------------|--|--|--|

| Param<br>No.                       | Symbol | Characteristic                    | Min.                                                                                                                                                                                                                                                                                             | Тур. | Max. | Units | Conditions                                                       |  |  |  |

| ADC Accuracy (12-Bit Mode) – VREF- |        |                                   |                                                                                                                                                                                                                                                                                                  |      |      |       |                                                                  |  |  |  |

| AD20a                              | Nr     | Resolution                        | 12 data bits                                                                                                                                                                                                                                                                                     |      |      | bits  |                                                                  |  |  |  |

| AD21a                              | INL    | Integral Nonlinearity             | -3                                                                                                                                                                                                                                                                                               | _    | +3   | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V <b>(Note 2)</b> |  |  |  |

| AD22a                              | DNL    | Differential Nonlinearity         | ≥ 1                                                                                                                                                                                                                                                                                              |      | < 1  | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V (Note 2)        |  |  |  |