Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT  |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 48K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 30x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gm706-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|--|

| SFR<br>Name | Addr. | Bit 15                                 | Bit 14                                    | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8     | Bit 7      | Bit 6         | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|----------------------------------------|-------------------------------------------|----------|---------|---------|---------|-------|-----------|------------|---------------|--------|----------|----------|----------|----------|----------|---------------|

| OC7CON1     | 093C  | _                                      | —                                         | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | ENFLTB    | ENFLTA     | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC7CON2     | 093E  | FLTMD                                  | FLTOUT                                    | FLTTRIEN | OCINV   |         | —       | —     | OC32      | OCTRIG     | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC7RS       | 0940  | Output Compare 7 Secondary Register xx |                                           |          |         |         |         |       |           | xxxx       |               |        |          |          |          |          |          |               |

| OC7R        | 0942  |                                        | Output Compare 7 Register xxx             |          |         |         |         |       | xxxx      |            |               |        |          |          |          |          |          |               |

| OC7TMR      | 0944  |                                        |                                           |          |         |         |         | Out   | put Compa | are 7 Time | r Value Regis | ster   |          |          |          |          |          | xxxx          |

| OC8CON1     | 0946  | _                                      | —                                         | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | —     | ENFLTB    | ENFLTA     | _             | OCFLTB | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC8CON2     | 0948  | FLTMD                                  | FLTOUT                                    | FLTTRIEN | OCINV   |         | —       | —     | OC32      | OCTRIG     | TRIGSTAT      | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC8RS       | 094A  |                                        |                                           |          |         |         |         | Ou    | tput Comp | are 8 Seco | ondary Regis  | ter    |          |          |          |          |          | xxxx          |

| OC8R        | 094C  |                                        |                                           |          |         |         |         |       | Output    | Compare 8  | 8 Register    |        |          |          |          |          |          | xxxx          |

| OC8TMR      | 094E  |                                        | Output Compare 8 Timer Value Register xxx |          |         |         |         |       | xxxx      |            |               |        |          |          |          |          |          |               |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXGM3XX DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8  | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-----------------------|--------|--------|-------|--------|--------|--------|--------|--------|--------|---------------|

| PMD1        | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD                 | DCIMD  | I2C1MD | U2MD  | U1MD   | SPI2MD | SPI1MD | —      | —      | AD1MD  | 0000          |

| PMD2        | 0762  | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD                 | IC1MD  | OC8MD  | OC7MD | OC6MD  | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3        | 0764  | T9MD   | T8MD   | T7MD   | T6MD   | _      | CMPMD  | RTCCMD <sup>(1)</sup> | PMPMD  | CRCMD  | _     | QEI2MD | _      | U3MD   | _      | I2C2MD | ADC2MD | 0000          |

| PMD4        | 0766  | _      | _      | _      | _      | _      | _      | _                     | _      | _      | _     | U4MD   | _      | REFOMD | CTMUMD | _      | _      | 0000          |

| PMD6        | 076A  | _      | _      | PWM6MD | PWM5MD | PWM4MD | PWM3MD | PWM2MD                | PWM1MD | _      | _     | _      | _      | _      | _      | _      | SPI3MD | 0000          |

|             |       |        |        |        |        |        |        |                       |        |        |       |        | DMA0MD |        |        |        |        |               |

| PMD7        | 076C  |        |        |        |        |        |        |                       |        |        |       |        | DMA1MD | PTGMD  |        |        |        |               |

| PMD7        | 0760  | _      | _      | _      | _      | _      | _      | _                     | _      | _      | _     | _      | DMA2MD | PIGMD  | _      | _      | _      | 0000          |

|             |       |        |        |        |        |        |        |                       |        |        |       |        | DMA3MD |        |        |        |        |               |

Legend:

— = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1:

The RTCCMD bit is not available on 44-pin devices.

| R/W-0                               | U-0   | R/W-0 | R/W-0  | R/W-0                                | R-0 | R-0   | R-0   |  |  |

|-------------------------------------|-------|-------|--------|--------------------------------------|-----|-------|-------|--|--|

| VAR                                 | —     | US1   | US0    | EDT                                  | DL2 | DL1   | DL0   |  |  |

| bit 15                              |       |       |        |                                      |     |       | bit 8 |  |  |

|                                     |       |       |        |                                      |     |       |       |  |  |

| R/W-0                               | R/W-0 | R/W-1 | R/W-0  | R/C-0                                | R-0 | R/W-0 | R/W-0 |  |  |

| SATA                                | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup>                  | SFA | RND   | IF    |  |  |

| bit 7                               |       | •     |        |                                      |     |       | bit 0 |  |  |

|                                     |       |       |        |                                      |     |       |       |  |  |

| Legend:                             |       |       |        |                                      |     |       |       |  |  |

| P = Peadable bit $W = Writable bit$ |       |       | hit    | II = II nimplemented bit read as '0' |     |       |       |  |  |

# REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legena:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

bit 15 VAR: Variable Exception Processing Latency Control bit 1 = Variable exception processing latency is enabled 0 = Fixed exception processing latency is enabled

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| R/W-0                                                                                                                                                        | R/W-0                                                                                                        | R/W-0                              | R/W-0                              | R/W-0                               | R/W-0           | R/W-0          | R/W-0 |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|-------------------------------------|-----------------|----------------|-------|--|--|--|

| NSTDIS                                                                                                                                                       | OVAERR                                                                                                       | OVBERR                             | COVAERR                            | COVBERR                             | OVATE           | OVBTE          | COVTE |  |  |  |

| bit 15                                                                                                                                                       | OWNERRY                                                                                                      | OVBENIN                            | 00 WILLIN                          | OOVBENIN                            | OWNE            | OVDIE          | bit 8 |  |  |  |

|                                                                                                                                                              |                                                                                                              |                                    |                                    |                                     |                 |                |       |  |  |  |

| R/W-0                                                                                                                                                        | R/W-0                                                                                                        | R/W-0                              | R/W-0                              | R/W-0                               | R/W-0           | R/W-0          | U-0   |  |  |  |

| SFTACERR                                                                                                                                                     | DIV0ERR                                                                                                      | DMACERR                            | MATHERR                            | ADDRERR                             | STKERR          | OSCFAIL        |       |  |  |  |

| bit 7                                                                                                                                                        |                                                                                                              |                                    |                                    |                                     |                 |                | bit ( |  |  |  |

| Legend:                                                                                                                                                      |                                                                                                              |                                    |                                    |                                     |                 |                |       |  |  |  |

| R = Readable                                                                                                                                                 | bit                                                                                                          | W = Writable                       | bit                                | U = Unimplem                        | ented bit, read | as '0'         |       |  |  |  |

| -n = Value at F                                                                                                                                              | POR                                                                                                          | '1' = Bit is set                   |                                    | '0' = Bit is clea                   | ired            | x = Bit is unk | nown  |  |  |  |

|                                                                                                                                                              |                                                                                                              |                                    |                                    |                                     |                 |                |       |  |  |  |

| bit 15                                                                                                                                                       |                                                                                                              | errupt Nesting                     |                                    |                                     |                 |                |       |  |  |  |

|                                                                                                                                                              |                                                                                                              | nesting is disa                    |                                    |                                     |                 |                |       |  |  |  |

| L:1 4 4                                                                                                                                                      | -                                                                                                            | nesting is ena                     |                                    | -1                                  |                 |                |       |  |  |  |

| bit 14                                                                                                                                                       |                                                                                                              |                                    | Overflow Trap F<br>erflow of Accur | •                                   |                 |                |       |  |  |  |

|                                                                                                                                                              | •                                                                                                            | •                                  | y overflow of A                    |                                     |                 |                |       |  |  |  |

| bit 13                                                                                                                                                       | -                                                                                                            |                                    | Overflow Trap F                    |                                     |                 |                |       |  |  |  |

|                                                                                                                                                              | 1 = Trap was                                                                                                 | s caused by ov                     | erflow of Accur                    | mulator B                           |                 |                |       |  |  |  |

|                                                                                                                                                              | 0 = Trap was                                                                                                 | s not caused by                    | y overflow of A                    | ccumulator B                        |                 |                |       |  |  |  |

| bit 12                                                                                                                                                       | COVAERR: Accumulator A Catastrophic Overflow Trap Flag bit                                                   |                                    |                                    |                                     |                 |                |       |  |  |  |

| <ul> <li>1 = Trap was caused by catastrophic overflow of Accumulator A</li> <li>0 = Trap was not caused by catastrophic overflow of Accumulator A</li> </ul> |                                                                                                              |                                    |                                    |                                     |                 |                |       |  |  |  |

| bit 11                                                                                                                                                       |                                                                                                              |                                    | -                                  | Overflow Trap F                     |                 |                |       |  |  |  |

|                                                                                                                                                              |                                                                                                              |                                    |                                    | flow of Accumu                      |                 |                |       |  |  |  |

|                                                                                                                                                              | •                                                                                                            | •                                  | •                                  | overflow of Accu                    |                 |                |       |  |  |  |

| bit 10                                                                                                                                                       | OVATE: Acc                                                                                                   | umulator A Ov                      | erflow Trap En                     | able bit                            |                 |                |       |  |  |  |

|                                                                                                                                                              | 1 = Trap ove<br>0 = Trap is d                                                                                | erflow of Accun<br>lisabled        | nulator A                          |                                     |                 |                |       |  |  |  |

| bit 9                                                                                                                                                        | OVBTE: Acc                                                                                                   | cumulator B Ov                     | verflow Trap En                    | able bit                            |                 |                |       |  |  |  |

|                                                                                                                                                              | 1 = Trap ove<br>0 = Trap is d                                                                                | erflow of Accun<br>lisabled        | ulator B                           |                                     |                 |                |       |  |  |  |

| bit 8                                                                                                                                                        | COVTE: Cat                                                                                                   | tastrophic Ove                     | flow Trap Enal                     | ole bit                             |                 |                |       |  |  |  |

|                                                                                                                                                              | 1 = Trap on<br>0 = Trap is d                                                                                 |                                    | verflow of Accu                    | mulator A or B i                    | s enabled       |                |       |  |  |  |

| bit 7                                                                                                                                                        | SFTACERR                                                                                                     | : Shift Accumu                     | lator Error Stat                   | us bit                              |                 |                |       |  |  |  |

|                                                                                                                                                              |                                                                                                              | •                                  | •                                  | alid accumulator<br>invalid accumul |                 |                |       |  |  |  |

| bit 6 <b>DIV0ERR:</b> Divide-by-Zero Error Status bit                                                                                                        |                                                                                                              |                                    |                                    |                                     |                 |                |       |  |  |  |

|                                                                                                                                                              | 1 = Math error trap was caused by a divide-by-zero<br>0 = Math error trap was not caused by a divide-by-zero |                                    |                                    |                                     |                 |                |       |  |  |  |

| bit 5                                                                                                                                                        | DMACERR:                                                                                                     | DMA Controlle                      | er Trap Flag bit                   |                                     |                 |                |       |  |  |  |

|                                                                                                                                                              | 1 = DMA Controller trap has occurred                                                                         |                                    |                                    |                                     |                 |                |       |  |  |  |

|                                                                                                                                                              |                                                                                                              | ntroller trap ha                   |                                    |                                     |                 |                |       |  |  |  |

| bit 4                                                                                                                                                        |                                                                                                              | Math Error Sta                     |                                    |                                     |                 |                |       |  |  |  |

|                                                                                                                                                              |                                                                                                              | or trap has occ<br>or trap has not |                                    |                                     |                 |                |       |  |  |  |

|                                                                                                                                                              |                                                                                                              |                                    |                                    |                                     |                 |                |       |  |  |  |

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| U-0          | U-0                                          | U-0              | U-0             | U-0                                | U-0   | U-0                | U-0   |  |  |  |

|--------------|----------------------------------------------|------------------|-----------------|------------------------------------|-------|--------------------|-------|--|--|--|

| _            | —                                            | _                | _               | —                                  | —     | —                  | _     |  |  |  |

| bit 15       |                                              |                  |                 | •                                  |       |                    | bit 8 |  |  |  |

|              |                                              |                  |                 |                                    |       |                    |       |  |  |  |

| U-0          | U-0                                          | R/W-0            | R/W-0           | U-0                                | U-0   | U-0                | U-0   |  |  |  |

| —            | _                                            | DAE              | DOOVR           |                                    | —     | —                  | —     |  |  |  |

| bit 7        | •                                            |                  |                 | •                                  |       |                    | bit 0 |  |  |  |

|              |                                              |                  |                 |                                    |       |                    |       |  |  |  |

| Legend:      |                                              |                  |                 |                                    |       |                    |       |  |  |  |

| R = Readab   | ole bit                                      | W = Writable     | bit             | U = Unimplemented bit, read as '0' |       |                    |       |  |  |  |

| -n = Value a | at POR                                       | '1' = Bit is set | t               | '0' = Bit is cle                   | eared | x = Bit is unknown |       |  |  |  |

|              |                                              |                  |                 |                                    |       |                    |       |  |  |  |

| bit 15-6     | Unimplemen                                   | ted: Read as     | '0'             |                                    |       |                    |       |  |  |  |

| bit 5        | DAE: DMA A                                   | ddress Error S   | Soft Trap Statu | s bit                              |       |                    |       |  |  |  |

|              | 1 = DMA address error soft trap has occurred |                  |                 |                                    |       |                    |       |  |  |  |

|              | 0 = DMA add                                  | ress error soft  | trap has not o  | ccurred                            |       |                    |       |  |  |  |

| bit 4        | DOOVR: DO                                    | Stack Overflow   | v Soft Trap Sta | itus bit                           |       |                    |       |  |  |  |

|              | 1 = DO stack                                 | overflow soft ti | rap has occurr  | ed                                 |       |                    |       |  |  |  |

|              |                                              |                  |                 |                                    |       |                    |       |  |  |  |

### REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

|         | 0 = DO stack overflow soft trap has not occurred |

|---------|--------------------------------------------------|

| bit 3-0 | Unimplemented: Read as '0'                       |

## REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-----|-----|-----|-----|-----|-------|

| —       | —   | —   | —   | _   | —   | —   | —     |

| bit 15  | •   |     | •   |     | •   |     | bit 8 |

|         |     |     |     |     |     |     |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

| —       | —   | —   | —   | _   | —   | —   | SGHT  |

| bit 7   |     |     | •   |     | •   |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-1 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

bit 0 SGHT: Software Generated Hard Trap Status bit

- 1 = Software generated hard trap has occurred

- 0 = Software generated hard trap has not occurred

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Direct Memory Access (DMA)" (DS70348), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

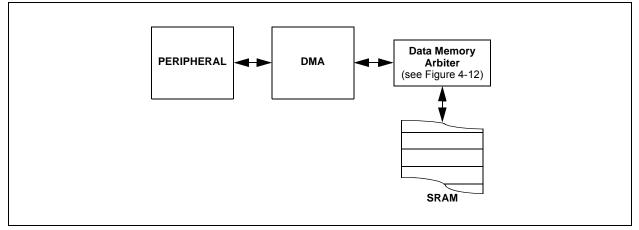

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The data memory bus arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. The peripherals supported by the DMA Controller include:

- CAN

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

- DCI

- PMP

- Timers

Refer to Table 8-1 for a complete list of supported peripherals.

## FIGURE 8-1: PERIPHERAL TO DMA CONTROLLER

### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0               |

|--------|-----|-----|-----|-----|-----|-----|---------------------|

| —      | —   | —   | —   | —   | —   | —   | IC32 <sup>(1)</sup> |

| bit 15 |     |     |     |     |     |     | bit 8               |

| R/W-0                 | R/W/HS-0                | U-0 | R/W-0       | R/W-1       | R/W-1       | R/W-0       | R/W-1       |

|-----------------------|-------------------------|-----|-------------|-------------|-------------|-------------|-------------|

| ICTRIG <sup>(2)</sup> | TRIGSTAT <sup>(3)</sup> |     | SYNCSEL4(4) | SYNCSEL3(4) | SYNCSEL2(4) | SYNCSEL1(4) | SYNCSEL0(4) |

| bit 7                 |                         |     |             |             |             |             | bit 0       |

| Legend:           | HS = Hardware Settable<br>bit |                             |                    |

|-------------------|-------------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit              | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-9 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

- bit 8 IC32: Input Capture x 32-Bit Timer Mode Select bit (Cascade mode)<sup>(1)</sup>

- 1 = Odd ICx and Even ICx form a single 32-bit input capture module

0 = Cascade module operation is disabled

- bit 7 ICTRIG: Input Capture x Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source is used to trigger the input capture timer (Trigger mode)

- Input source is used to synchronize the input capture timer to the timer of another module (Synchronization mode)

#### bit 6 TRIGSTAT: Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

- bit 5 Unimplemented: Read as '0'

- **Note 1:** The IC32 bit in both the Odd and Even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- **4:** Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x module (ICx) has one PTG input source. See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1, IC5

PTGO9 = IC2, IC6

PTGO10 = IC3, IC7

PTGO10 = IC3, IC7PTGO11 = IC4, IC8

### REGISTER 16-5: STCON: PWMx SECONDARY TIME BASE CONTROL REGISTER (CONTINUED)

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

### REGISTER 16-6: STCON2: PWMx SECONDARY MASTER CLOCK DIVIDER SELECT REGISTER 2

| U-0            | U-0 | U-0          | U-0 | U-0                                | U-0                         | U-0   | U-0   |

|----------------|-----|--------------|-----|------------------------------------|-----------------------------|-------|-------|

| —              | —   | —            | —   | —                                  | —                           | —     | _     |

| bit 15         |     |              |     |                                    |                             |       | bit 8 |

|                |     |              |     |                                    |                             |       |       |

| U-0            | U-0 | U-0          | U-0 | U-0                                | R/W-0                       | R/W-0 | R/W-0 |

| —              | —   | —            | —   | —                                  | PCLKDIV<2:0> <sup>(1)</sup> |       |       |

| bit 7          |     |              |     |                                    | bit                         |       |       |

|                |     |              |     |                                    |                             |       |       |

| Legend:        |     |              |     |                                    |                             |       |       |

| R = Readable I | bit | W = Writable | bit | U = Unimplemented bit, read as '0' |                             |       |       |

| R – Reauable bit  |                  | 0 – Unimplemented bit, read |                    |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved

- 110 = Divide-by-64

- 101 = Divide-by-32

- 100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# REGISTER 16-16: DTRx: PWMx DEAD-TIME REGISTER

| U-0                               | U-0   | R/W-0            | R/W-0                              | R/W-0                | R/W-0  | R/W-0              | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|----------------------|--------|--------------------|-------|

|                                   | —     |                  |                                    | DTR                  | <13:8> |                    |       |

| bit 15                            | •     |                  |                                    |                      |        |                    | bit 8 |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0  | R/W-0              | R/W-0 |

|                                   |       |                  | DTR                                | x<7:0>               |        |                    |       |

| bit 7                             |       |                  |                                    |                      |        |                    | bit 0 |

| Legend:                           |       |                  |                                    |                      |        |                    |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                      |        |                    |       |

| -n = Value at POR                 |       | '1' = Bit is set |                                    | '0' = Bit is cleared |        | x = Bit is unknown |       |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

### REGISTER 16-17: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0                           | U-0   | R/W-0            | R/W-0                              | R/W-0                | R/W-0    | R/W-0              | R/W-0 |

|-------------------------------|-------|------------------|------------------------------------|----------------------|----------|--------------------|-------|

| —                             | _     |                  |                                    | ALTDT                | Rx<13:8> |                    |       |

| bit 15                        |       |                  |                                    |                      |          |                    | bit 8 |

|                               |       |                  |                                    |                      |          |                    |       |

| R/W-0                         | R/W-0 | R/W-0            | R/W-0                              | R/W-0                | R/W-0    | R/W-0              | R/W-0 |

|                               |       |                  | ALTD                               | TRx<7:0>             |          |                    |       |

| bit 7                         |       |                  |                                    |                      |          |                    | bit C |

|                               |       |                  |                                    |                      |          |                    |       |

| Legend:                       |       |                  |                                    |                      |          |                    |       |

| R = Readable bit W = Writable |       | oit              | U = Unimplemented bit, read as '0' |                      |          |                    |       |

| -n = Value at POR             |       | '1' = Bit is set |                                    | '0' = Bit is cleared |          | x = Bit is unknown |       |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

# 21.3 CAN Control Registers

# REGISTER 21-1: CxCTRL1: CANx CONTROL REGISTER 1

| U-0                              | U-0        | R/W-0            | R/W-0                | R/W-0                              | R/W-1  | R/W-0              | R/W-0  |  |

|----------------------------------|------------|------------------|----------------------|------------------------------------|--------|--------------------|--------|--|

| —                                | —          | CSIDL            | ABAT                 | CANCKS                             | REQOP2 | REQOP1             | REQOP0 |  |

| bit 15                           |            |                  |                      |                                    |        |                    | bit 8  |  |

|                                  |            |                  |                      |                                    |        |                    |        |  |

| R-1                              | R-0        | R-0              | U-0                  | R/W-0                              | U-0    | U-0                | R/W-0  |  |

| OPMODE2                          | OPMODE1    | OPMODE0          | _                    | CANCAP                             | —      |                    | WIN    |  |

| bit 7                            | •          |                  |                      | •                                  |        |                    | bit 0  |  |

|                                  |            |                  |                      |                                    |        |                    |        |  |

| Legend:                          |            |                  |                      |                                    |        |                    |        |  |

| R = Readable I                   | bit        | W = Writable b   | pit                  | U = Unimplemented bit, read as '0' |        |                    |        |  |

| -n = Value at POR '1' = Bit is s |            | '1' = Bit is set | '0' = Bit is cleared |                                    | ared   | x = Bit is unknown |        |  |

|                                  |            |                  |                      |                                    |        |                    |        |  |

| bit 15-14                        | Unimplemen | ted: Read as '0  | )'                   |                                    |        |                    |        |  |

|          | 1                                                                 |

|----------|-------------------------------------------------------------------|

| bit 13   | CSIDL: CANx Stop in Idle Mode bit                                 |

|          | 1 = Discontinues module operation when device enters Idle mode    |

|          | 0 = Continues module operation in Idle mode                       |

| bit 12   | ABAT: Abort All Pending Transmissions bit                         |

|          | 1 = Signals all transmit buffers to abort transmission            |

|          | 0 = Module will clear this bit when all transmissions are aborted |

| bit 11   | CANCKS: CANx Module Clock (FCAN) Source Select bit                |

|          | 1 = FCAN is equal to 2 * FP                                       |

|          | 0 = FCAN is equal to FP                                           |

| bit 10-8 | REQOP<2:0>: Request Operation Mode bits                           |

|          | 111 = Set Listen All Messages mode                                |

|          | 110 = Reserved<br>101 = Reserved                                  |

|          | 100 = Set Configuration mode                                      |

|          | 011 = Set Listen Only mode                                        |

|          | 010 = Set Loopback mode                                           |

|          | 001 = Set Disable mode                                            |

|          | 000 = Set Normal Operation mode                                   |

| bit 7-5  | OPMODE<2:0>: Operation Mode bits                                  |

|          | 111 = Module is in Listen All Messages mode                       |

|          | 110 = Reserved<br>101 = Reserved                                  |

|          | 100 = Module is in Configuration mode                             |

|          | 011 = Module is in Listen Only mode                               |

|          | 010 = Module is in Loopback mode                                  |

|          | 001 = Module is in Disable mode                                   |

|          | 000 = Module is in Normal Operation mode                          |

| bit 4    | Unimplemented: Read as '0'                                        |

| bit 3    | CANCAP: CANx Message Receive Timer Capture Event Enable bit       |

|          | 1 = Enables input capture based on CAN message receive            |

|          | 0 = Disables CAN capture                                          |

| bit 2-1  | Unimplemented: Read as '0'                                        |

| bit 0    | WIN: SFR Map Window Select bit                                    |

|          | 1 = Uses filter window                                            |

|          | 0 = Uses buffer window                                            |

### REGISTER 21-6: CxINTF: CANx INTERRUPT FLAG REGISTER (CONTINUED)

| bit 1 | RBIF: RX Buffer Interrupt Flag bit                     |

|-------|--------------------------------------------------------|

|       | <ol> <li>Interrupt request has occurred</li> </ol>     |

|       | 0 = Interrupt request has not occurred                 |

| bit 0 | TBIF: TX Buffer Interrupt Flag bit                     |

|       | <ol> <li>I = Interrupt request has occurred</li> </ol> |

|       | O = Interrupt request has not accurred.                |

#### 0 = Interrupt request has not occurred

### REGISTER 21-7: CxINTE: CANx INTERRUPT ENABLE REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|-------|-------|-------|-----|--------|--------|-------|-------|

| IVRIE | WAKIE | ERRIE | —   | FIFOIE | RBOVIE | RBIE  | TBIE  |

| bit 7 |       |       |     |        |        |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                                                                         |

|----------|----------------------------------------------------------------------------------------------------|

| bit 7    | IVRIE: Invalid Message Interrupt Enable bit                                                        |

|          | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |

| bit 6    | WAKIE: Bus Wake-up Activity Interrupt Enable bit                                                   |

|          | <ul><li>1 = Interrupt request is enabled</li><li>0 = Interrupt request is not enabled</li></ul>    |

| bit 5    | ERRIE: Error Interrupt Enable bit                                                                  |

|          | <ul><li>1 = Interrupt request is enabled</li><li>0 = Interrupt request is not enabled</li></ul>    |

| bit 4    | Unimplemented: Read as '0'                                                                         |

| bit 3    | FIFOIE: FIFO Almost Full Interrupt Enable bit                                                      |

|          | <ul><li>1 = Interrupt request is enabled</li><li>0 = Interrupt request is not enabled</li></ul>    |

| bit 2    | RBOVIE: RX Buffer Overflow Interrupt Enable bit                                                    |

|          | <ul><li>1 = Interrupt request is enabled</li><li>0 = Interrupt request is not enabled</li></ul>    |

| bit 1    | RBIE: RX Buffer Interrupt Enable bit                                                               |

|          | <ul><li>1 = Interrupt request is enabled</li><li>0 = Interrupt request is not enabled</li></ul>    |

| bit 0    | TBIE: TX Buffer Interrupt Enable bit                                                               |

|          | <ul><li>1 = Interrupt request is enabled</li><li>0 = Interrupt request is not enabled</li></ul>    |

|          |                                                                                                    |

| R/W-0         | R/W-0         | R/W-0                                                                   | R/W-0            | R/W-0                              | R/W-0            | R/W-0              | R/W-0 |  |  |  |

|---------------|---------------|-------------------------------------------------------------------------|------------------|------------------------------------|------------------|--------------------|-------|--|--|--|

| F7BP3         | F7BP2         | F7BP1                                                                   | F7BP0            | F6BP3                              | F6BP2            | F6BP1              | F6BP0 |  |  |  |

| bit 15        |               |                                                                         |                  |                                    |                  |                    | bit 8 |  |  |  |

|               |               |                                                                         |                  |                                    |                  |                    |       |  |  |  |

| R/W-0         | R/W-0         | R/W-0                                                                   | R/W-0            | R/W-0                              | R/W-0            | R/W-0              | R/W-0 |  |  |  |

| F5BP3         | F5BP2         | F5BP1                                                                   | F5BP0            | F4BP3                              | F4BP2            | F4BP1              | F4BP0 |  |  |  |

| bit 7         |               |                                                                         |                  |                                    |                  |                    | bit 0 |  |  |  |

| [             |               |                                                                         |                  |                                    |                  |                    |       |  |  |  |

| Legend:       |               |                                                                         |                  |                                    |                  |                    |       |  |  |  |

| R = Readable  | e bit         | W = Writable bit                                                        |                  | U = Unimplemented bit, read as '0' |                  |                    |       |  |  |  |

| -n = Value at | POR           | '1' = Bit is set                                                        |                  | '0' = Bit is cleared               |                  | x = Bit is unknown |       |  |  |  |

|               |               |                                                                         |                  |                                    |                  |                    |       |  |  |  |

| bit 15-12     |               | RX Buffer Masl                                                          |                  |                                    |                  |                    |       |  |  |  |

|               |               | hits received in                                                        |                  | -                                  |                  |                    |       |  |  |  |

|               | 1110 = Filter | hits received ir                                                        | NRX Buffer 14    | 4                                  |                  |                    |       |  |  |  |

|               | •             |                                                                         |                  |                                    |                  |                    |       |  |  |  |

|               | •             |                                                                         |                  |                                    |                  |                    |       |  |  |  |

|               | 0001 = Filter | hits received in                                                        | NRX Buffer 1     |                                    |                  |                    |       |  |  |  |

|               | 0000 = Filter | hits received in                                                        | n RX Buffer 0    |                                    |                  |                    |       |  |  |  |

| bit 11-8      | F6BP<3:0>:    | RX Buffer Masl                                                          | k for Filter 6 b | oits (same value                   | es as bits 15-12 |                    |       |  |  |  |

| bit 7-4       | F5BP<3:0>:    | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits 15-12) |                  |                                    |                  |                    |       |  |  |  |

|               |               |                                                                         |                  |                                    |                  |                    |       |  |  |  |

# REGISTER 21-13: CxBUFPNT2: CANx FILTERS 4-7 BUFFER POINTER REGISTER 2

#### REGISTER 21-14: CxBUFPNT3: CANx FILTERS 8-11 BUFFER POINTER REGISTER 3

F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits 15-12)

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| F11BP3 | F11BP2 | F11BP1 | F11BP0 | F10BP3 | F10BP2 | F10BP1 | F10BP0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-0  |

| F9BP3  | F9BP2  | F9BP1  | F9BP0  | F8BP3  | F8BP2  | F8BP1  | F8BP0  |

| bit 7  |        |        |        |        |        |        | bit 0  |

|        |        |        |        |        |        |        |        |

| Logond |        |        |        |        |        |        |        |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-12 | F11BP<3:0>: RX Buffer Mask for Filter 11 bits<br>1111 = Filter hits received in RX FIFO buffer<br>1110 = Filter hits received in RX Buffer 14<br>• |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 0001 = Filter hits received in RX Buffer 1<br>0000 = Filter hits received in RX Buffer 0                                                           |

| bit 11-8  | F10BP<3:0>: RX Buffer Mask for Filter 10 bits (same values as bits 15-12)                                                                          |

| bit 7-4   | F9BP<3:0>: RX Buffer Mask for Filter 9 bits (same values as bits 15-12)                                                                            |

| bit 3-0   | F8BP<3:0>: RX Buffer Mask for Filter 8 bits (same values as bits 15-12)                                                                            |

© 2013-2014 Microchip Technology Inc.

bit 3-0

## REGISTER 23-1: ADxCON1: ADCx CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Clock Source Select bits<br><u>If SSRCG = 1:</u><br>111 = Reserved<br>110 = PTGO15 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>101 = PTGO14 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>100 = PTGO13 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>011 = PTGO12 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion<br>001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion<br>000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion<br><u>If SSRCG = 0:</u><br>111 = Internal counter ends sampling and starts conversion (auto-convert)<br>110 = CTMU ends sampling and starts conversion |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 101 = PWM secondary Special Event Trigger ends sampling and starts conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | 100 = Timer5 compare ends sampling and starts conversion<br>011 = PWM primary Special Event Trigger ends sampling and starts conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | 010 = Timer3 compare ends sampling and starts conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | <ul><li>001 = Active transition on the INTO pin ends sampling and starts conversion</li><li>000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | See SSRC<2:0> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 3   | SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS<1:0> = $01 \text{ or } 1x$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>In 12-Bit Mode (AD12B = 1), SIMSAM is Unimplemented and is Read as '0':</li> <li>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x), or samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01)</li> <li>0 = Samples multiple channels individually in sequence</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| bit 2   | ASAM: ADCx Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = Sampling begins immediately after last conversion; SAMP bit is auto-set</li> <li>0 = Sampling begins when SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| bit 1   | SAMP: ADCx Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = ADCx Sample-and-Hold amplifiers are sampling</li> <li>0 = ADCx Sample-and-Hold amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If</li> <li>SSRC&lt;2:0&gt; = 000, software can write '0' to end sampling and start conversion. If SSRC&lt;2:0&gt; ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 0   | DONE: ADCx Conversion Status bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = ADCx conversion cycle is completed.</li> <li>0 = ADCx conversion has not started or is in progress</li> <li>Automatically set by hardware when A/D conversion is complete. Software can write '0' to clear DONE status (software not allowed to write '1'). Clearing this bit does NOT affect any operation in progress.</li> <li>Automatically cleared by hardware at the start of a new conversion.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Note 1: | See Section 25.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

2: Do not clear the DONE bit in software if ADCx Sample Auto-Start bit is enabled (ASAM = 1).

| U-0                                                     | U-0        | U-0              | U-0                                                 | U-0                  | U-0                                | U-0                | R/W-0   |  |

|---------------------------------------------------------|------------|------------------|-----------------------------------------------------|----------------------|------------------------------------|--------------------|---------|--|

| _                                                       | —          | —                | _                                                   | _                    | —                                  | —                  | ADDMAEN |  |