Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT   |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 48K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | -                                                                                 |

| Data Converters            | A/D 30x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gm706t-i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "CPU" (DS70359), which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

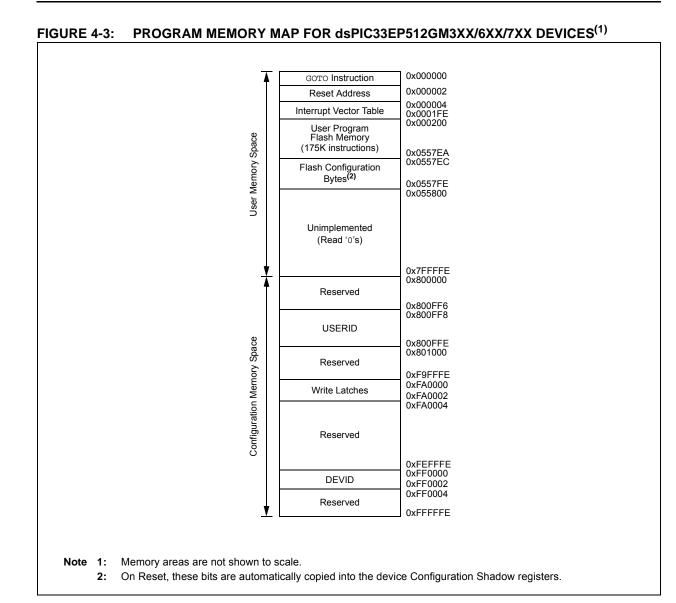

The CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word, with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle, effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

### 3.1 Registers

The dsPIC33EPXXXGM3XX/6XX/7XX devices have sixteen 16-bit Working registers in the programmer's model. Each of the Working registers can act as a data, address or address offset register. The 16th Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

### 3.2 Instruction Set

The device instruction set has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

### 3.3 Data Space Addressing

The Base Data Space can be addressed as 4K words or 8 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operate solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EP devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Space boundary is device-specific.

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space at any 16K program word boundary. The program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Data Space Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. Refer to "Data Memory" (DS70595) and "Program Memory" (DS70613) in the "dsPIC33/ PIC24 Family Reference Manual" for more details on EDS, PSV and table accesses.

On dsPIC33EP devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

### 3.4 Addressing Modes

The CPU supports these addressing modes:

- · Inherent (no operand)

- Relative

- Literal

- Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

### TABLE 4-14: PWM GENERATOR 6 REGISTER MAP

|          |       |         |                  |         |               |              |           |           |                  |          |         |          |          |          | -        |          |          | 1             |

|----------|-------|---------|------------------|---------|---------------|--------------|-----------|-----------|------------------|----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| SFR Name | Addr. | Bit 15  | Bit 14           | Bit 13  | Bit 12        | Bit 11       | Bit 10    | Bit 9     | Bit 8            | Bit 7    | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| PWMCON6  | 0CC0  | FLTSTAT | CLSTAT           | TRGSTAT | FLTIEN        | CLIEN        | TRGIEN    | ITB       | MDCS             | DTC1     | DTC0    | DTCP     | -        | MTBS     | CAM      | XPRES    | IUE      | 0000          |

| IOCON6   | 0CC2  | PENH    | PENL             | POLH    | POLL          | PMOD1        | PMOD0     | OVRENH    | OVRENL           | OVRDAT1  | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | C000          |

| FCLCON6  | 0CC4  | IFLTMOD | CLSRC4           | CLSRC3  | CLSRC2        | CLSRC1       | CLSRC0    | CLPOL     | CLMOD            | FLTSRC4  | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 00F8          |

| PDC6     | 0CC6  |         | PDC6<15:0> 00    |         |               |              |           |           |                  | 0000     |         |          |          |          |          |          |          |               |

| PHASE6   | 0CC8  |         | PHASE6<15:0> 000 |         |               |              |           |           | 0000             |          |         |          |          |          |          |          |          |               |

| DTR6     | 0CCA  | _       | _                |         | DTR6<13:0>    |              |           |           |                  |          | 0000    |          |          |          |          |          |          |               |

| ALTDTR6  | 00000 | _       | _                |         | ALTDTR6<13:0> |              |           |           |                  |          | 0000    |          |          |          |          |          |          |               |

| SDC6     | 0CCE  |         |                  |         |               |              |           |           | SDC6             | <15:0>   |         |          |          |          |          |          |          | 0000          |

| SPHASE6  | 0CD0  |         |                  |         |               |              |           |           | SPHASE           | 6<15:0>  |         |          |          |          |          |          |          | 0000          |

| TRIG6    | 0CD2  |         |                  |         |               |              |           |           | TRGCM            | P<15:0>  |         |          |          |          |          |          |          | 0000          |

| TRGCON6  | 0CD4  | TRGDIV3 | TRGDIV2          | TRGDIV1 | TRGDIV0       | _            | —         | —         | _                | _        | —       | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP6  | 0CD8  |         |                  |         |               |              |           |           | PWMCAF           | P6<15:0> |         |          |          | •        |          |          |          | 0000          |

| LEBCON6  | 0CDA  | PHR     | PHF              | PLR     | PLF           | FLTLEBEN     | CLLEBEN   | —         | —                | —        | _       | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY6  | 0CDC  | _       | -                | _       | _             |              |           |           | •                | •        | LEB<    | 11:0>    |          | •        | •        |          |          | 0000          |

| AUXCON6  | 0CDE  | _       | _                | _       | _             | BLANKSEL3    | BLANKSEL2 | BLANKSEL1 | <b>BLANKSEL0</b> | _        | _       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

| Logondi  |       |         | 1                |         |               | wn in hovede |           |           |                  |          |         |          |          |          |          |          |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| SFR<br>Name | Addr. | Bit 15 | Bit 14          | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8        | Bit 7  | Bit 6   | Bit 5    | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|--------|-----------------|----------|----------|----------|----------|----------|--------------|--------|---------|----------|----------|--------|--------|--------|--------|---------------|

| QEI2CON     | 05C0  | QEIEN  | _               | QEISIDL  | PIMOD2   | PIMOD1   | PIMOD0   | IMV1     | IMV0         | —      | INTDIV2 | INTDIV1  | INTDIV0  | CNTPOL | GATEN  | CCM1   | CCM0   | 0000          |

| QEI2IOC     | 05C2  | QCAPEN | FLTREN          | QFDIV2   | QFDIV1   | QFDIV0   | OUTFNC1  | OUTFNC0  | SWPAB        | HOMPOL | IDXPOL  | QEBPOL   | QEAPOL   | HOME   | INDEX  | QEB    | QEA    | 000x          |

| QEI2STAT    | 05C4  | —      |                 | PCHEQIRQ | PCHEQIEN | PCLEQIRQ | PCLEQIEN | POSOVIRQ | POSOVIEN     | PCIIRQ | PCIIEN  | VELOVIRQ | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS2CNTL    | 05C6  |        |                 |          |          |          |          | F        | POSCNT<15:   | )>     |         |          |          |        |        |        |        | 0000          |

| POS2CNTH    | 05C8  |        |                 |          |          |          |          | P        | OSCNT<31:1   | 6>     |         |          |          |        |        |        |        | 0000          |

| POS2HLD     | 05CA  |        |                 |          |          |          |          | ł        | POSHLD<15:(  | )>     |         |          |          |        |        |        |        | 0000          |

| VEL2CNT     | 05CC  |        |                 |          |          |          |          | ,        | VELCNT<15:0  | )>     |         |          |          |        |        |        |        | 0000          |

| INT2TMRL    | 05CE  |        |                 |          |          |          |          |          | INTTMR<15:0  | )>     |         |          |          |        |        |        |        | 0000          |

| INT2TMRH    | 05D0  |        |                 |          |          |          |          | I        | NTTMR<31:1   | 6>     |         |          |          |        |        |        |        | 0000          |

| INT2HLDL    | 05D2  |        |                 |          |          |          |          |          | INTHLD<15:0  | >      |         |          |          |        |        |        |        | 0000          |

| INT2HLDH    | 05D4  |        |                 |          |          |          |          | I        | NTHLD<31:10  | 6>     |         |          |          |        |        |        |        | 0000          |

| INDX2CNTL   | 05D6  |        |                 |          |          |          |          | I        | NDXCNT<15:   | 0>     |         |          |          |        |        |        |        | 0000          |

| INDX2CNTH   | 05D8  |        |                 |          |          |          |          | II       | NDXCNT<31:1  | 6>     |         |          |          |        |        |        |        | 0000          |

| INDX2HLD    | 05DA  |        |                 |          |          |          |          | I        | NDXHLD<15:   | 0>     |         |          |          |        |        |        |        | 0000          |

| QEI2GECL    | 05DC  |        |                 |          |          |          |          |          | QEIGEC<15:0  | )>     |         |          |          |        |        |        |        | 0000          |

| QEI2ICL     | 05DC  |        |                 |          |          |          |          |          | QEIIC<15:0>  | •      |         |          |          |        |        |        |        | 0000          |

| QEI2GECH    | 05DE  |        |                 |          |          |          |          | (        | QEIGEC<31:1  | 6>     |         |          |          |        |        |        |        | 0000          |

| QEI2ICH     | 05DE  |        | QEIIC<31:16> 0  |          |          |          |          |          | 0000         |        |         |          |          |        |        |        |        |               |

| QEI2LECL    | 05E0  |        | QEILEC<15:0> 00 |          |          |          |          |          | 0000         |        |         |          |          |        |        |        |        |               |

| QEI2LECH    | 05E2  |        |                 |          |          |          |          | (        | QEILEC<31:10 | 6>     |         |          |          |        |        |        |        | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-41: OP AMP/COMPARATOR REGISTER MAP

| SFR<br>Name      | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|------------------|-------|--------|--------|--------|--------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|---------------|

| CMSTAT           | 0A80  | PSIDL  | _      | —      | C5EVT  | C4EVT    | C3EVT    | C2EVT    | C1EVT    | —        | _        | _        | C5OUT    | C4OUT    | C3OUT    | C2OUT    | C1OUT    | 0000          |

| CVR1CON          | 0A82  | _      |        | _      | _      | CVRR1    | VREFSEL  | —        | _        | CVREN    | CVROE    | CVRR0    | CVRSS    | CVR3     | CVR2     | CVR1     | CVR0     | 0000          |

| CM1CON           | 0A84  | CON    | COE    | CPOL   | _      | _        | OPMODE   | CEVT     | COUT     | EVPOL1   | EVPOL0   | —        | CREF     | _        | —        | CCH1     | CCH0     | 0000          |

| CM1MSKSRC        | 0A86  | -      | -      | _      |        | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM1MSKCON        | 0A88  | HLMS   |        | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM1FLTR          | 0A8A  | _      | _      | _      | _      | _        | _        | —        | —        | —        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM2CON           | 0A8C  | CON    | COE    | CPOL   | _      | _        | OPMODE   | CEVT     | COUT     | EVPOL1   | EVPOL0   | —        | CREF     | _        | —        | CCH1     | CCH0     | 0000          |

| CM2MSKSRC        | 0A8E  | _      | _      | _      | _      | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM2MSKCON        | 0A90  | HLMS   | -      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM2FLTR          | 0A92  | -      | -      | _      |        | _        | _        | _        | _        | _        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM3CON           | 0A94  | CON    | COE    | CPOL   |        | _        | OPMODE   | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM3MSKSRC        | 0A96  | -      | -      | _      |        | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| <b>CM3MSKCON</b> | 0A98  | HLMS   | -      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM3FLTR          | 0A9A  | _      |        | _      | _      | _        | _        | _        | _        | —        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM4CON           | 0A9C  | CON    | COE    | CPOL   | _      | _        | -        | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM4MSKSRC        | 0A9E  | _      | _      | _      | _      | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM4MSKCON        | 0AA0  | HLMS   | _      | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM4FLTR          | 0AA2  | _      | _      | _      | _      | _        | _        | _        | _        | —        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CM5CON           | 0AA4  | CON    | COE    | CPOL   | _      | _        | OPMODE   | CEVT     | COUT     | EVPOL1   | EVPOL0   | _        | CREF     | _        | _        | CCH1     | CCH0     | 0000          |

| CM5MSKSRC        | 0AA6  | _      | _      | _      | _      | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 | SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 | 0000          |

| CM5MSKCON        | 0AA8  | HLMS   |        | OCEN   | OCNEN  | OBEN     | OBNEN    | OAEN     | OANEN    | NAGS     | PAGS     | ACEN     | ACNEN    | ABEN     | ABNEN    | AAEN     | AANEN    | 0000          |

| CM5FLTR          | 0AAA  | —      |        | _      | _      | _        |          | —        | _        | —        | CFSEL2   | CFSEL1   | CFSEL0   | CFLTREN  | CFDIV2   | CFDIV1   | CFDIV0   | 0000          |

| CVR2CON          | 0AB4  | —      | _      | _      | _      | CVRR1    | VREFSEL  | _        | _        | CVREN    | CVROE    | CVRR0    | CVRSS    | CVR3     | CVR2     | CVR1     | CVR0     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33EPXXXGM3XX/6XX/7XX

| REGISTER 7-1: SI | R: CPU STATUS REGISTER <sup>(1)</sup> |

|------------------|---------------------------------------|

|------------------|---------------------------------------|

| R/W-0                | R/W-0                | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|----------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                   | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                      |                      |       |       |       |       | bit 8 |

|                      |                      |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA    | N     | OV    | Z     | С     |

| bit 7                |                      |                      |       |       |       |       | bit 0 |

| Legend:           | C = Clearable bit |                      |                    |

|-------------------|-------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>                                                                                                                                                                                                                                                    |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled</li> <li>110 = CPU Interrupt Priority Level is 6 (14)</li> <li>101 = CPU Interrupt Priority Level is 5 (13)</li> <li>100 = CPU Interrupt Priority Level is 4 (12)</li> <li>011 = CPU Interrupt Priority Level is 3 (11)</li> </ul> |

|         | 010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8)                                                                                                                                                                             |

**Note 1:** For complete register details, see Register 3-1.

2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

### 8.1 DMA Controller Registers

Each DMA Controller Channel x (where x = 0 through 3) contains the following registers:

- 16-bit DMA Channel x Control Register (DMAxCON)

- 16-bit DMA Channel x IRQ Select Register (DMAxREQ)

- 32-bit DMA Channel x Start Address Register A (DMAxSTAL/H)

- 32-bit DMA Channel x Start Address Register B (DMAxSTBL/H)

- 16-bit DMA Channel x Peripheral Address Register (DMAxPAD)

- 14-bit DMA Channel x Transfer Count Register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADRL/H) are common to all DMA Controller channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The interrupt flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding interrupt enable control bits (DMAxIE) are located in an IECx register in the interrupt controller and the corresponding interrupt priority control bits (DMAxIP) are located in an IPCx register in the interrupt controller.

### **REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER**

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|--------|-------|-------|-------|-------|-----|-----|-------|

| CHEN   | SIZE  | DIR   | HALF  | NULLW | —   | —   | —     |

| bit 15 |       |       |       |       |     |     | bit 8 |

|        |       |       |       |       |     |     |       |

| U-0   | U-0 | R/W-0  | R/W-0  | U-0 | U-0 | R/W-0 | R/W-0 |

|-------|-----|--------|--------|-----|-----|-------|-------|

| —     | —   | AMODE1 | AMODE0 | —   | _   | MODE1 | MODE0 |

| bit 7 |     |        |        |     |     |       | bit 0 |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

| bit 15   | CHEN: Channel Enable bit                                                                                                                              |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15   | 1 = Channel is enabled                                                                                                                                |

|          | 0 = Channel is disabled                                                                                                                               |

| bit 14   | SIZE: Data Transfer Size bit                                                                                                                          |

| DIL 14   | 1 = Byte                                                                                                                                              |

|          | 0 = Word                                                                                                                                              |

| bit 13   | <b>DIR:</b> Transfer Direction bit (source/destination bus select)                                                                                    |

| DIC 15   | 1 = Reads from RAM address, writes to peripheral address                                                                                              |

|          | 0 = Reads from peripheral address, writes to RAM address                                                                                              |

| bit 12   | HALF: Block Transfer Interrupt Select bit                                                                                                             |

| DIL 12   | · · · · · · · · · · · · · · · · · · ·                                                                                                                 |

|          | <ul> <li>1 = Initiates interrupt when half of the data has been moved</li> <li>0 = Initiates interrupt when all of the data has been moved</li> </ul> |

| bit 11   | NULLW: Null Data Peripheral Write Mode Select bit                                                                                                     |

|          | •                                                                                                                                                     |

|          | <ul> <li>1 = Null data write to peripheral in addition to RAM write (DIR bit must also be clear)</li> <li>0 = Normal operation</li> </ul>             |

| bit 10-6 | Unimplemented: Read as '0'                                                                                                                            |

|          | •                                                                                                                                                     |

| bit 5-4  | AMODE<1:0>: DMA Channel Addressing Mode Select bits                                                                                                   |

|          | 11 = Reserved<br>10 = Peripheral Indirect mode                                                                                                        |

|          | 01 = Register Indirect without Post-Increment mode                                                                                                    |

|          | 00 = Register Indirect with Post-Increment mode                                                                                                       |

| bit 3-2  | Unimplemented: Read as '0'                                                                                                                            |

| bit 1-0  | <b>MODE&lt;1:0&gt;:</b> DMA Channel Operating Mode Select bits                                                                                        |

| bit 1-0  | 11 = One-Shot, Ping-Pong modes are enabled (one block transfer from/to each DMA buffer)                                                               |

|          | 10 = Continuous, Ping-Pong modes are enabled                                                                                                          |

|          | 01 = One-Shot, Ping-Pong modes are disabled                                                                                                           |

|          | 00 = Continuous, Ping-Pong modes are disabled                                                                                                         |

|          |                                                                                                                                                       |

| R/W-0        | R/W-0                                   | R/W-1                           | R/W-1                | R/W-0                                 | R/W-0              | R/W-0           | R/W-0     |

|--------------|-----------------------------------------|---------------------------------|----------------------|---------------------------------------|--------------------|-----------------|-----------|

| ROI          | DOZE2 <sup>(3)</sup>                    | DOZE1 <sup>(3)</sup>            | DOZE0 <sup>(3)</sup> | DOZEN <sup>(1,4)</sup>                | FRCDIV2            | FRCDIV1         | FRCDIV0   |

| bit 15       |                                         |                                 |                      |                                       |                    |                 | bit 8     |

|              |                                         |                                 |                      |                                       |                    |                 |           |

| R/W-0        | R/W-1                                   | U-0                             | R/W-0                | R/W-0                                 | R/W-0              | R/W-0           | R/W-0     |

| PLLPOST      | 1 PLLPOST0                              |                                 | PLLPRE4              | PLLPRE3                               | PLLPRE2            | PLLPRE1         | PLLPRE0   |

| bit 7        |                                         |                                 |                      |                                       |                    |                 | bit (     |

| <del></del>  |                                         |                                 |                      |                                       |                    |                 |           |

| Legend:      | la hit                                  |                                 | L:4                  | II — Ilucius da un                    | antad bit waar     | L == (0'        |           |

| R = Readab   |                                         | W = Writable                    |                      | •                                     | nented bit, read   |                 |           |

| -n = Value a | IL POR                                  | '1' = Bit is set                |                      | '0' = Bit is clea                     | ared               | x = Bit is unkr | IOWI      |

| bit 15       | ROI: Recover                            | on Interrupt b                  | it                   |                                       |                    |                 |           |

|              |                                         | will clear the D                |                      |                                       |                    |                 |           |

|              |                                         | will have no ef                 |                      | OZEN bit                              |                    |                 |           |

| bit 14-12    | DOZE<2:0>:                              | Processor Clo                   | ck Reduction         | Select bits <sup>(3)</sup>            |                    |                 |           |

|              | 111 = Fcy div                           |                                 |                      |                                       |                    |                 |           |

|              | 110 = Fcy div                           | •                               |                      |                                       |                    |                 |           |

|              | 101 = FCY div                           |                                 |                      |                                       |                    |                 |           |

|              | 100 = FCY div<br>011 = FCY div          | /ided by 16<br>/ided by 8 (defa | ault)                |                                       |                    |                 |           |

|              | 010 = FCY div                           |                                 |                      |                                       |                    |                 |           |

|              | 001 = Fcy div                           |                                 |                      |                                       |                    |                 |           |

|              | 000 = FCY div                           | •                               |                      |                                       |                    |                 |           |

| bit 11       |                                         | e Mode Enable                   |                      |                                       |                    |                 |           |

|              |                                         |                                 |                      | etween the perip                      |                    | nd the processo | or clocks |

| hit 10 0     |                                         | •                               | •                    | ratio are forced<br>r Postscaler bits |                    |                 |           |

| bit 10-8     |                                         |                                 | RC Oscillator        | Posiscaler bits                       | 5                  |                 |           |

|              | 111 = FRC di<br>110 = FRC di            |                                 |                      |                                       |                    |                 |           |

|              | 101 <b>= FRC di</b>                     | •                               |                      |                                       |                    |                 |           |

|              | 100 <b>= FRC di</b>                     |                                 |                      |                                       |                    |                 |           |

|              | 011 = FRC di                            |                                 |                      |                                       |                    |                 |           |

|              | 010 = FRC di<br>001 = FRC di            | •                               |                      |                                       |                    |                 |           |

|              |                                         | ivided by 1 (de                 | fault)               |                                       |                    |                 |           |

| bit 7-6      |                                         | •                               |                      | r Select bits (als                    | so denoted as      | N2', PLL posts  | caler)    |

|              | 11 = Output o                           | livided by 8                    | -                    |                                       |                    | -               | ·         |

|              | 10 = Reserve                            |                                 |                      |                                       |                    |                 |           |

|              | 01 = Output c<br>00 = Output c          | livided by 4 (de                | efault)              |                                       |                    |                 |           |

| bit 5        | -                                       | ted: Read as '                  | 0'                   |                                       |                    |                 |           |

|              | -                                       |                                 |                      | n interment a                         |                    |                 |           |

|              | This bit is cleared                     |                                 |                      |                                       | uis.               |                 |           |

|              | This register resets<br>The DOZE<2:0> b | -                               |                      |                                       | hit is clear. If D |                 | writes to |

|              | OZE<2:0> b<br>OZE<2:0> are ig           | -                               |                      |                                       | on is oreal. If D  | ∪∠∟iv – ⊥, ally |           |

|              |                                         |                                 |                      |                                       |                    |                 | -         |

### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup>

4: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| REGISTER 10-4: | <b>PMD4: PERIPHERAL</b> | MODULE DISABLE | CONTROL REGISTER 4 |

|----------------|-------------------------|----------------|--------------------|

|----------------|-------------------------|----------------|--------------------|

| U-0                               | U-0                                    | U-0              | U-0                                                                           | U-0           | U-0             | U-0      | U-0   |

|-----------------------------------|----------------------------------------|------------------|-------------------------------------------------------------------------------|---------------|-----------------|----------|-------|

| _                                 | —                                      | —                | —                                                                             | —             | —               | —        | —     |

| bit 15                            |                                        |                  |                                                                               |               |                 |          | bit 8 |

|                                   |                                        |                  |                                                                               |               |                 |          |       |

| U-0                               | U-0                                    | R/W-0            | U-0                                                                           | R/W-0         | R/W-0           | U-0      | U-0   |

| —                                 | —                                      | U4MD             | —                                                                             | REFOMD        | CTMUMD          | —        | _     |

| bit 7                             |                                        |                  |                                                                               |               |                 |          | bit 0 |

| Logondi                           |                                        |                  |                                                                               |               |                 |          |       |

| Legend:                           | bla bit                                | M - Mritabla     | hit                                                                           | LI – Unimplon | contod hit rook | 1 00 '0' |       |

| R = Readable bit W = Writable bit |                                        |                  | U = Unimplemented bit, read as '0'<br>'0' = Bit is cleared x = Bit is unknown |               |                 |          |       |

| -n = Value a                      | alpur                                  | '1' = Bit is set |                                                                               |               | areu            |          | IOWII |

| bit 15-6                          | Unimplemen                             | ted: Read as 'd  | )'                                                                            |               |                 |          |       |

| bit 5                             | -                                      | 4 Module Disa    |                                                                               |               |                 |          |       |

|                                   | 1 = UART4 m                            | odule is disable | ed                                                                            |               |                 |          |       |

|                                   | 0 <b>= UART4 m</b>                     | odule is enable  | ed                                                                            |               |                 |          |       |

| bit 4                             | Unimplemen                             | ted: Read as 'd  | )'                                                                            |               |                 |          |       |

| bit 3                             | REFOMD: Re                             | eference Clock   | Module Disabl                                                                 | le bit        |                 |          |       |

|                                   | 1 = Reference clock module is disabled |                  |                                                                               |               |                 |          |       |

|                                   | 0 = Reference                          | e clock module   | is enabled                                                                    |               |                 |          |       |

| bit 2                             | CTMUMD: C                              | TMU Module Di    | isable bit                                                                    |               |                 |          |       |

|                                   |                                        | odule is disable |                                                                               |               |                 |          |       |

|                                   | 0 = CTMU mo                            | odule is enable  | d                                                                             |               |                 |          |       |

| 11110                             |                                        |                  | - 1                                                                           |               |                 |          |       |

bit 1-0 Unimplemented: Read as '0'

### REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

| U-0           | U-0   | R/W-0            | R/W-0                                                    | R/W-0        | R/W-0            | R/W-0    | R/W-0  |

|---------------|-------|------------------|----------------------------------------------------------|--------------|------------------|----------|--------|

| —             | —     | PWM6MD           | PWM5MD                                                   | PWM4MD       | PWM3MD           | PWM2MD   | PWM1MD |

| bit 15        |       |                  |                                                          |              |                  |          | bit 8  |

|               |       |                  |                                                          |              |                  |          |        |

| U-0           | U-0   | U-0              | U-0                                                      | U-0          | U-0              | U-0      | R/W-0  |

| —             | —     | —                | —                                                        | —            | —                | —        | SPI3MD |

| bit 7         |       |                  |                                                          |              |                  |          | bit 0  |

|               |       |                  |                                                          |              |                  |          |        |

| Legend:       |       |                  |                                                          |              |                  |          |        |

| R = Readable  | e bit | W = Writable     | bit                                                      | U = Unimplem | nented bit, read | l as '0' |        |

| -n = Value at | POR   | '1' = Bit is set | '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |              |                  | iown     |        |

| bit 15-14 | Unimplemented: Read as '0'                              |

|-----------|---------------------------------------------------------|

| bit 13-8  | <b>PWM6MD:PWM1MD:</b> PWMx (x = 1-6) Module Disable bit |

|           | 1 = PWMx module is disabled                             |

|           | 0 = PWMx module is enabled                              |

| bit 7-1   | Unimplemented: Read as '0'                              |

| bit 0     | SPI3MD: SPI3 Module Disable bit                         |

|           | 1 = SPI3 module is disabled                             |

|           | 0 = SPI3 module is enabled                              |

© 2013-2014 Microchip Technology Inc.

| U-0                | R/W-0                                                                                                                                    | R/W-0                                                                                                              | R/W-0                                                | R/W-0             | R/W-0           | R/W-0           | R/W-0          |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------|-----------------|-----------------|----------------|

|                    |                                                                                                                                          |                                                                                                                    |                                                      | DTCMP3R<6:0       | )>              |                 |                |

| bit 15             |                                                                                                                                          |                                                                                                                    |                                                      |                   |                 |                 | bit 8          |

|                    |                                                                                                                                          |                                                                                                                    |                                                      |                   |                 |                 |                |

| U-0                | R/W-0                                                                                                                                    | R/W-0                                                                                                              | R/W-0                                                | R/W-0             | R/W-0           | R/W-0           | R/W-0          |

| —                  |                                                                                                                                          |                                                                                                                    |                                                      | DTCMP2R<6:0       | )>              |                 |                |

| bit 7              |                                                                                                                                          |                                                                                                                    |                                                      |                   |                 |                 | bit 0          |

|                    |                                                                                                                                          |                                                                                                                    |                                                      |                   |                 |                 |                |

| Legend:            |                                                                                                                                          |                                                                                                                    |                                                      |                   |                 |                 |                |

| R = Readab         | le bit                                                                                                                                   | W = Writable                                                                                                       | bit                                                  | U = Unimplem      | nented bit, rea | id as '0'       |                |

| -n = Value a       | t POR                                                                                                                                    | '1' = Bit is set                                                                                                   |                                                      | '0' = Bit is clea | ared            | x = Bit is unkr | nown           |

|                    | DTCMP3R<6<br>(see Table 11                                                                                                               | nted: Read as '<br>6:0>: Assign PV<br>I-2 for input pin<br>nput tied to RPI                                        | VM Dead-Tim<br>selection nun                         |                   | n Input 3 to th | e Correspondin  | g RPn Pin bits |

| bit 15<br>bit 14-8 | DTCMP3R<6<br>(see Table 11<br>1111100 = H<br>•<br>•<br>•<br>0000001 = H                                                                  | 6:0>: Assign PV<br>I-2 for input pin<br>nput tied to RPI<br>nput tied to CM                                        | VM Dead-Tim<br>selection nun<br>124<br>P1            |                   | n Input 3 to th | e Corresponding | g RPn Pin bits |

| bit 14-8           | DTCMP3R<6<br>(see Table 11<br>1111100 = H<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | 5:0>: Assign PV<br>I-2 for input pin<br>nput tied to RPI<br>nput tied to CM<br>nput tied to Vss                    | VM Dead-Tim<br>selection nun<br>124<br>P1            |                   | n Input 3 to th | e Correspondin  | g RPn Pin bits |

|                    | DTCMP3R<6<br>(see Table 11<br>1111100 = H<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | 5:0>: Assign PV<br>I-2 for input pin<br>nput tied to RPI<br>nput tied to CM<br>nput tied to Vss<br>nted: Read as ' | VM Dead-Tim<br>selection nun<br>124<br>P1<br>3<br>0' | nbers)            |                 | e Corresponding | -              |

### REGISTER 11-27: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39

### REGISTER 17-2: QEIXIOC: QEIX I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control bit

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control and SWPAB Pin Swapping bit

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 0 QEA: Status of QEAx Input Pin After Polarity Control and SWPAB Pin Swapping bit

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

### 21.0 CONTROLLER AREA NETWORK (CAN) MODULE (dsPIC33EPXXXGM6XX/7XX DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Enhanced Controller Area Network (ECAN™)"** (DS70353), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

### 21.1 Overview

The Controller Area Network (CAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/ protocol was designed to allow communications within noisy environments. The dsPIC33EPXXXGM6XX/7XX devices contain two CAN modules.

The CAN module is a communication controller, implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details. The CAN module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and Extended Data Frames

- 0-8 Bytes of Data Length

- Programmable Bit Rate, up to 1 Mbit/sec

- Automatic Response to Remote Transmission Requests

- Up to 8 Transmit Buffers with Application Specified Prioritization and Abort Capability (each buffer can contain up to 8 bytes of data)

- Up to 32 Receive Buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 Full (Standard/Extended Identifier) Acceptance Filters

- Three Full Acceptance Filter Masks

- DeviceNet<sup>™</sup> Addressing Support

- Programmable Wake-up Functionality with Integrated Low-Pass Filter

- Programmable Loopback mode supports Self-Test Operation

- Signaling via Interrupt Capabilities for all CAN Receiver and Transmitter Error States

- · Programmable Clock Source

- Programmable Link to Input Capture 2 (IC2) module for Timestamping and Network Synchronization

- · Low-Power Sleep and Idle modes

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

33EPXXXGM3XX/6XX

0

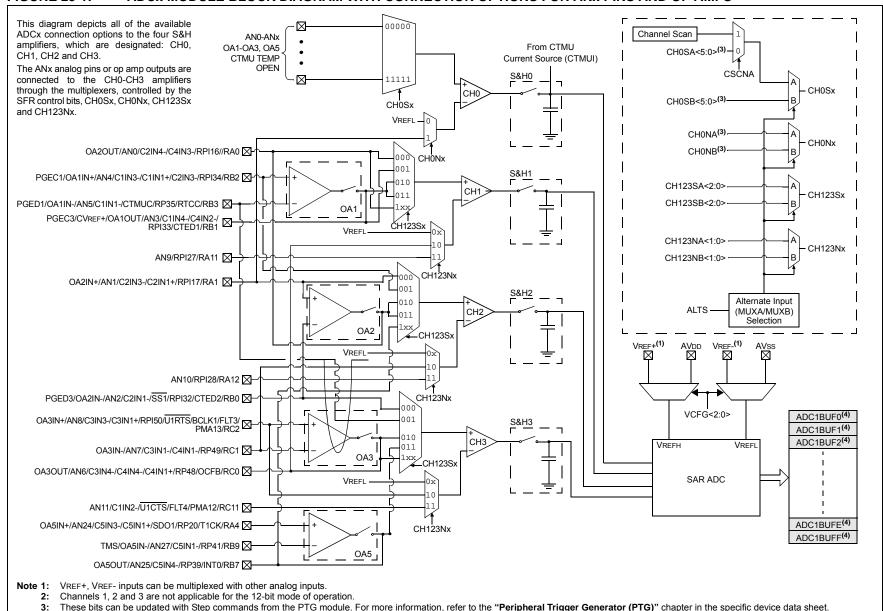

4: When ADDMAEN (ADxCON4<8>) = 1, enabling DMA, only ADCxBUF0 is used.

### ADCX MODULE BLOCK DIAGRAM WITH CONNECTION OPTIONS FOR ANX PINS AND OP AMPS

x = Bit is unknown

### REGISTER 25-10: PTGADJ: PTG ADJUST REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0 | R/W-0           | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|----------------|-------|-----------------|-------|--------------|------------------|----------|-------|

|                |       |                 | PTGA  | DJ<15:8>     |                  |          |       |

| bit 15         |       |                 |       |              |                  |          | bit 8 |

|                |       |                 |       |              |                  |          |       |

| R/W-0          | R/W-0 | R/W-0           | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                |       |                 | PTGA  | DJ<7:0>      |                  |          |       |

| bit 7          |       |                 |       |              |                  |          | bit 0 |

|                |       |                 |       |              |                  |          |       |

| Legend:        |       |                 |       |              |                  |          |       |

| R = Readable I | bit   | W = Writable bi | t     | U = Unimpler | mented bit, reac | l as '0' |       |

|                |       |                 |       |              |                  |          |       |

'0' = Bit is cleared

### REGISTER 25-11: PTGL0: PTG LITERAL 0 REGISTER<sup>(1)</sup>

'1' = Bit is set

-n = Value at POR

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | PTGL0 | <15:8> |       |       |       |

| bit 15 |       |       |       |        |       |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGL  | 0<7:0> |       |       |       |

| bit 7  |       |       |       |        |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 **PTGL0<15:0>:** PTG Literal 0 Register bits

This register holds the 16-bit value to be written to the AD1CHS0 register with the  ${\tt PTGCTRL}$  Step command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

bit 15-0 **PTGADJ<15:0>:** PTG Adjust Register bits This register holds user-supplied data to be added to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 register with the PTGADD command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

### REGISTER 25-12: PTGQPTR: PTG STEP QUEUE POINTER REGISTER<sup>(1)</sup>

| U-0             | U-0 | U-0              | U-0                                       | U-0                                | U-0         | U-0   | U-0   |

|-----------------|-----|------------------|-------------------------------------------|------------------------------------|-------------|-------|-------|

| —               |     | —                | _                                         | —                                  | —           | —     | —     |

| bit 15          |     |                  |                                           |                                    |             |       | bit 8 |

|                 |     |                  |                                           |                                    |             |       |       |

| U-0             | U-0 | U-0              | R/W-0                                     | R/W-0                              | R/W-0       | R/W-0 | R/W-0 |

| —               | —   | —                |                                           |                                    | PTGQPTR<4:0 | >     |       |

| bit 7           |     |                  |                                           |                                    |             |       | bit 0 |

|                 |     |                  |                                           |                                    |             |       |       |

| Legend:         |     |                  |                                           |                                    |             |       |       |

| R = Readable b  | bit | W = Writable     | bit                                       | U = Unimplemented bit, read as '0' |             |       |       |

| -n = Value at P | OR  | '1' = Bit is set | t '0' = Bit is cleared x = Bit is unknown |                                    |             | nown  |       |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 **PTGQPTR<4:0>:** PTG Step Queue Pointer Register bits This register points to the currently active Step command in the step queue.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

### **REGISTER 25-13: PTGQUEX: PTG STEP QUEUE REGISTER x (x = 0-15)**<sup>(1,3)</sup>

| R/W-0  | R/W-0                        | R/W-0 | R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

|--------|------------------------------|-------|-----------|----------------------|-------|-------|-------|

|        |                              |       | STEP(2x + | · 1)<7:0> <b>(2)</b> |       |       |       |

| bit 15 |                              |       |           |                      |       |       | bit 8 |

|        |                              |       |           |                      |       |       |       |

| R/W-0  | R/W-0                        | R/W-0 | R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

|        | STEP(2x)<7:0> <sup>(2)</sup> |       |           |                      |       |       |       |

| bit 7  |                              |       |           |                      |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8STEP(2x + 1)<7:0>: PTG Step Queue Pointer Register bits<sup>(2)</sup><br/>A queue location for storage of the STEP(2x +1) command byte.bit 7-0STEP(2x)<7:0>: PTG Step Queue Pointer Register bits<sup>(2)</sup>

A queue location for storage of the STEP(2x) command byte.

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: Refer to Table 25-1 for the Step command encoding.

- 3: The Step registers maintain their values on any type of Reset.

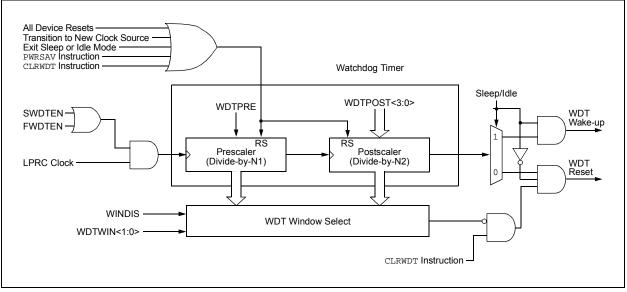

### 30.5 Watchdog Timer (WDT)

For dsPIC33EPXXXGM3XX/6XX/7XX devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

### 30.5.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT time-out period (TwDT), as shown in Parameter SY12 in Table 33-21.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

### FIGURE 30-2: WDT BLOCK DIAGRAM

### 30.5.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3,2>) needs to be cleared in software after the device wakes up.

### 30.5.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

### 30.5.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<6>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

© 2013-2014 Microchip Technology Inc.

## 32.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 32.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

| DC CHARACTERISTICS |                     |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |       |            |      |         |  |

|--------------------|---------------------|------|-------------------------------------------------------|-------|------------|------|---------|--|

| Parameter No.      | Тур. <sup>(2)</sup> | Max. | Doze<br>Ratio                                         | Units | Conditions |      |         |  |

| Doze Current (IDC  | DZE) <sup>(1)</sup> |      |                                                       |       |            |      |         |  |

| DC73a              | 20                  | 53   | 1:2                                                   | mA    | 40%0       | 3.3V | 70 MIPS |  |

| DC73g              | 8                   | 30   | 1:128                                                 | mA    | -40°C      |      |         |  |

| DC70a              | 19                  | 53   | 1:2                                                   | mA    | +25°C      | 3.3V | 60 MIPS |  |

| DC70g              | 8                   | 30   | 1:128                                                 | mA    | +25 C      |      |         |  |

| DC71a              | 20                  | 53   | 1:2                                                   | mA    | +85°C      | 3.3V | 60 MIPS |  |

| DC71g              | 10                  | 30   | 1:128                                                 | mA    | +00 C      |      |         |  |

| DC72a              | 25                  | 42   | 1:2                                                   | mA    | +125°C     | 3.3V | 50 MIPS |  |

| DC72g              | 12                  | 30   | 1:128                                                 | mA    | +125 C     |      |         |  |

### TABLE 33-9: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

• Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as outputs and driving low

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- CPU executing

```

while(1)

{

NOP();

}

```

- · JTAG is disabled

- 2: Data in the "Typical" column is at 3.3V, +25°C unless otherwise specified.

### 33.2 AC Characteristics and Timing Parameters

This section defines the dsPIC33EPXXXGM3XX/6XX/ 7XX AC characteristics and timing parameters.

### TABLE 33-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)                                                                                                                           |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AC CHARACTERISTICS | Operating temperature -40°C ≤ TA ≤ +85°C for Industrial<br>-40°C ≤ TA ≤ +125°C for Extended<br>Operating voltage VDD range as described in <b>Section 33.1 "DC</b><br><b>Characteristics</b> ". |  |  |  |

|                    |                                                                                                                                                                                                 |  |  |  |

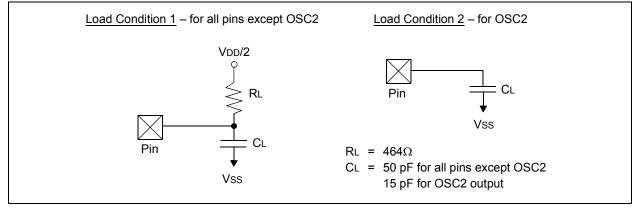

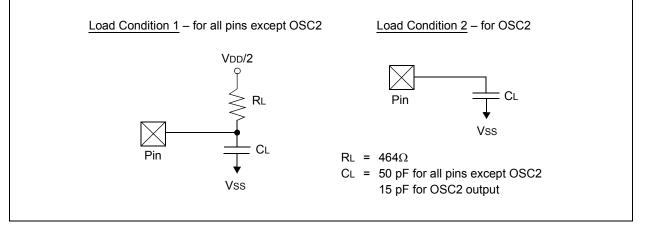

### FIGURE 33-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 33-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   | pF    | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Cio    | All I/O Pins and OSC2 | —    | —    | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            | _    | —    | 400  | pF    | In l <sup>2</sup> C™ mode                                           |

### 34.2 AC Characteristics and Timing Parameters