Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT   |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 48K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) |                                                                                   |

| Data Converters            | A/D 30x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gm706t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| REGISTER 8-12: | DMARQC: DMA REQUEST COLLISION STATUS REGISTER |

|----------------|-----------------------------------------------|

|----------------|-----------------------------------------------|

| U-0                                                     | U-0                                                               | U-0                                 | U-0           | U-0               | U-0                | U-0    | U-0    |  |  |  |

|---------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------|---------------|-------------------|--------------------|--------|--------|--|--|--|

| —                                                       | —                                                                 | —                                   | —             | —                 | —                  | _      | —      |  |  |  |

| bit 15                                                  | •                                                                 |                                     | •             |                   |                    | •      | bit 8  |  |  |  |

|                                                         |                                                                   |                                     |               |                   |                    |        |        |  |  |  |

| U-0                                                     | U-0                                                               | U-0                                 | U-0           | R-0               | R-0                | R-0    | R-0    |  |  |  |

| —                                                       | —                                                                 | —                                   | —             | RQCOL3            | RQCOL2             | RQCOL1 | RQCOL0 |  |  |  |

| bit 7                                                   |                                                                   |                                     |               |                   |                    |        | bit C  |  |  |  |

|                                                         |                                                                   |                                     |               |                   |                    |        |        |  |  |  |

| Legend:                                                 |                                                                   |                                     |               |                   |                    |        |        |  |  |  |

| R = Readable                                            | e bit                                                             | W = Writable                        | bit           | U = Unimpler      | mented bit, read   | as '0' |        |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared |                                                                   |                                     |               |                   | x = Bit is unknown |        |        |  |  |  |

|                                                         |                                                                   |                                     |               |                   |                    |        |        |  |  |  |

| bit 15-4                                                | Unimplemented: Read as '0'                                        |                                     |               |                   |                    |        |        |  |  |  |

| bit 3                                                   | RQCOL3: Channel 3 Transfer Request Collision Flag bit             |                                     |               |                   |                    |        |        |  |  |  |

|                                                         | 1 = User FORCE and interrupt-based request collision are detected |                                     |               |                   |                    |        |        |  |  |  |

|                                                         | 0 = No request collision is detected                              |                                     |               |                   |                    |        |        |  |  |  |

| bit 2                                                   | RQCOL2: Channel 2 Transfer Request Collision Flag bit             |                                     |               |                   |                    |        |        |  |  |  |

|                                                         | 1 = User FORCE and interrupt-based request collision are detected |                                     |               |                   |                    |        |        |  |  |  |

|                                                         |                                                                   | st collision is d                   |               |                   |                    |        |        |  |  |  |

| bit 1                                                   |                                                                   | annel 1 Transf                      | -             | -                 |                    |        |        |  |  |  |

|                                                         |                                                                   | RCE and interr<br>st collision is d | •             | uest collision a  | are detected       |        |        |  |  |  |

| bit 0                                                   | RQCOL0: Ch                                                        | annel 0 Transf                      | er Request Co | ollision Flag bit |                    |        |        |  |  |  |

|                                                         | 1 = User FORCE and interrunt-based request collision are detected |                                     |               |                   |                    |        |        |  |  |  |

- 1 = User FORCE and interrupt-based request collision are detected

- 0 = No request collision is detected

NOTES:

## 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled

- The LPRC clock continues to run in Sleep mode if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled

The device wakes up from Sleep mode on any of the these events:

- · Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby mode when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

## 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions

- · The WDT is automatically cleared

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

## 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

| bit 4 | SPI2MD: SPI2 Module Disable bit                     |

|-------|-----------------------------------------------------|

|       | 1 = SPI2 module is disabled                         |

|       | 0 = SPI2 module is enabled                          |

| bit 3 | SPI1MD: SPI1 Module Disable bit                     |

|       | 1 = SPI1 module is disabled                         |

|       | 0 = SPI1 module is enabled                          |

| bit 2 | C2MD: CAN2 Module Disable bit <sup>(1)</sup>        |

|       | 1 = CAN2 module is disabled                         |

|       | 0 = CAN2 module is enabled                          |

| bit 1 | <b>C1MD:</b> CAN1 Module Disable bit <sup>(1)</sup> |

|       | 1 = CAN1 module is disabled                         |

|       | 0 = CAN1 module is enabled                          |

| bit 0 | AD1MD: ADC1 Module Disable bit                      |

|       | 1 = ADC1 module is disabled                         |

|       | 0 = ADC1 module is enabled                          |

|       |                                                     |

Note 1: These bits are available on dsPIC33EPXXXGM6XX/7XX devices only.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADCx to convert the digital output logic level or to toggle a digital output on a comparator or ADCx input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

- g) The TRIS registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRIS register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRIS bit must be set to input for pins with only remappable input function(s) assigned.

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin is disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRIS register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

| REGISTER 11-7: | RPINR10: PERIPHERAL PIN SELECT INPUT REGISTER 10 |

|----------------|--------------------------------------------------|

|                |                                                  |

| U-0          | R/W-0                                                                                                                      | R/W-0                          | R/W-0 | R/W-0                | R/W-0           | R/W-0              | R/W-0 |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------|----------------------|-----------------|--------------------|-------|--|--|--|--|

| _            |                                                                                                                            |                                |       | IC8R<6:0>            |                 |                    |       |  |  |  |  |

| bit 15       |                                                                                                                            |                                |       |                      |                 |                    | bit 8 |  |  |  |  |

| U-0          | DAMO                                                                                                                       |                                | DAMO  | DAALO                |                 | DAMO               | DAVO  |  |  |  |  |

| 0-0          | R/W-0                                                                                                                      | R/W-0                          | R/W-0 | R/W-0<br>IC7R<6:0>   | R/W-0           | R/W-0              | R/W-0 |  |  |  |  |

| bit 7        |                                                                                                                            |                                |       | IC/R<0.02            |                 |                    | bit 0 |  |  |  |  |

|              |                                                                                                                            |                                |       |                      |                 |                    |       |  |  |  |  |

| Legend:      |                                                                                                                            |                                |       |                      |                 |                    |       |  |  |  |  |

| R = Readab   | le bit                                                                                                                     | W = Writable                   | bit   | U = Unimplen         | nented bit, rea | ad as '0'          |       |  |  |  |  |

| -n = Value a | t POR                                                                                                                      | '1' = Bit is set               |       | '0' = Bit is cleared |                 | x = Bit is unknown |       |  |  |  |  |

|              |                                                                                                                            |                                |       |                      |                 |                    |       |  |  |  |  |

| bit 15       | Unimplemen                                                                                                                 | ted: Read as '                 | 0'    |                      |                 |                    |       |  |  |  |  |

| bit 14-8     | IC8R<6:0>: Assign Input Capture 8 (IC8) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |                                |       |                      |                 |                    |       |  |  |  |  |

|              | 1111100 = lr                                                                                                               | 1111100 = Input tied to RPI124 |       |                      |                 |                    |       |  |  |  |  |

|              | •                                                                                                                          |                                |       |                      |                 |                    |       |  |  |  |  |

|              | •                                                                                                                          |                                |       |                      |                 |                    |       |  |  |  |  |

|              | 0000001 = lr                                                                                                               | nput tied to CM                | P1    |                      |                 |                    |       |  |  |  |  |

|              | 0000000 = Ir                                                                                                               | nput tied to Vss               |       |                      |                 |                    |       |  |  |  |  |

| bit 7        | Unimplemen                                                                                                                 | Unimplemented: Read as '0'     |       |                      |                 |                    |       |  |  |  |  |

| bit 6-0      | -                                                                                                                          |                                |       |                      |                 |                    |       |  |  |  |  |

|              | •                                                                                                                          |                                |       |                      |                 |                    |       |  |  |  |  |

|              | •                                                                                                                          |                                |       |                      |                 |                    |       |  |  |  |  |

|              |                                                                                                                            | nput tied to CM                |       |                      |                 |                    |       |  |  |  |  |

| R/W-0<br>R/W-0                         | R/W-0<br>R/W-0<br>W = Writable H<br>'1' = Bit is set<br>ted: Read as '0        |                                                                                                                                                                      | R/W-0<br>DTCMP5R<6:(<br>R/W-0<br>DTCMP4R<6:(<br>U = Unimplen<br>'0' = Bit is cle                        | R/W-0<br>)>                                                                                                                                                                                                  | R/W-0<br>R/W-0<br>d as '0'<br>x = Bit is unkr                                                                                                                                                                                                               | R/W-0<br>bit 8<br>R/W-0<br>bit 0                                                                                                                                                                                                                                          |

|----------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nimplemen                              | W = Writable I<br>'1' = Bit is set                                             | bit                                                                                                                                                                  | R/W-0<br>DTCMP4R<6:(<br>U = Unimplen                                                                    | R/W-0<br>)>                                                                                                                                                                                                  | d as '0'                                                                                                                                                                                                                                                    | R/W-0<br>bit 0                                                                                                                                                                                                                                                            |

| nimplemen                              | W = Writable I<br>'1' = Bit is set                                             | bit                                                                                                                                                                  | DTCMP4R<6:(<br>U = Unimplen                                                                             | )>                                                                                                                                                                                                           | d as '0'                                                                                                                                                                                                                                                    | R/W-0<br>bit 0                                                                                                                                                                                                                                                            |

| nimplemen                              | W = Writable I<br>'1' = Bit is set                                             | bit                                                                                                                                                                  | DTCMP4R<6:(<br>U = Unimplen                                                                             | )>                                                                                                                                                                                                           | d as '0'                                                                                                                                                                                                                                                    | bit 0                                                                                                                                                                                                                                                                     |

| nimplemen                              | W = Writable I<br>'1' = Bit is set                                             | bit                                                                                                                                                                  | DTCMP4R<6:(<br>U = Unimplen                                                                             | )>                                                                                                                                                                                                           | d as '0'                                                                                                                                                                                                                                                    | bit 0                                                                                                                                                                                                                                                                     |

| nimplemen                              | '1' = Bit is set                                                               |                                                                                                                                                                      | U = Unimplen                                                                                            | nented bit, rea                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                           |

| nimplemen                              | '1' = Bit is set                                                               |                                                                                                                                                                      | •                                                                                                       |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                           |

| nimplemen                              | '1' = Bit is set                                                               |                                                                                                                                                                      | •                                                                                                       |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             | nown                                                                                                                                                                                                                                                                      |

| nimplemen                              | '1' = Bit is set                                                               |                                                                                                                                                                      | •                                                                                                       |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             | nown                                                                                                                                                                                                                                                                      |

| nimplemen                              |                                                                                |                                                                                                                                                                      | '0' = Bit is cle                                                                                        | ared                                                                                                                                                                                                         | x = Bit is unkr                                                                                                                                                                                                                                             | nown                                                                                                                                                                                                                                                                      |

| nimplemen                              | ted: Read as 'o                                                                | 0,                                                                                                                                                                   |                                                                                                         |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                           |

| 111100 <b>= In</b>                     | put tied to RPI                                                                | 124                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                           |

|                                        |                                                                                |                                                                                                                                                                      |                                                                                                         |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                           |

| nimplemen                              | ted: Read as '0                                                                | 0'                                                                                                                                                                   |                                                                                                         |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                           |

| TCMP4R<6<br>ee Table 11<br>111100 = In | : <b>0&gt;:</b> Assign PW<br>-2 for input pin<br>aput tied to RPI              | VM Dead-Tim<br>selection nur<br>124                                                                                                                                  |                                                                                                         | n Input 4 to th                                                                                                                                                                                              | e Correspondin                                                                                                                                                                                                                                              | g RPn Pin bits                                                                                                                                                                                                                                                            |

| )<br>r<br>1                            | 00000 = Ir<br>himplemen<br>CCMP4R<6<br>ee Table 11<br>11100 = Ir<br>00001 = Ir | 00000 = Input tied to Vss<br>implemented: Read as '<br>CMP4R<6:0>: Assign PV<br>e Table 11-2 for input pin<br>11100 = Input tied to RPI<br>00001 = Input tied to CMI | ee Table 11-2 for input pin selection nur<br>11100 = Input tied to RPI124<br>00001 = Input tied to CMP1 | 00000 = Input tied to Vss<br><b>implemented:</b> Read as '0'<br><b>CMP4R&lt;6:0&gt;:</b> Assign PWM Dead-Time Compensation<br>te Table 11-2 for input pin selection numbers)<br>11100 = Input tied to RPI124 | 00000 = Input tied to Vss<br><b>implemented:</b> Read as '0'<br><b>CCMP4R&lt;6:0&gt;:</b> Assign PWM Dead-Time Compensation Input 4 to the<br>the Table 11-2 for input pin selection numbers)<br>11100 = Input tied to RPI124<br>00001 = Input tied to CMP1 | 00000 = Input tied to Vss<br><b>implemented:</b> Read as '0'<br><b>CCMP4R&lt;6:0&gt;:</b> Assign PWM Dead-Time Compensation Input 4 to the Corresponding<br>the Table 11-2 for input pin selection numbers)<br>11100 = Input tied to RPI124<br>00001 = Input tied to CMP1 |

## dsPIC33EPXXXGM3XX/6XX/7XX

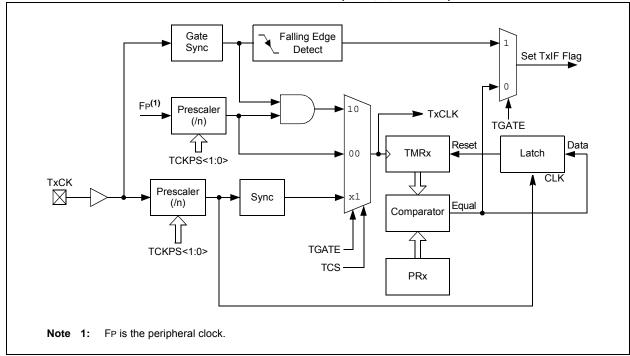

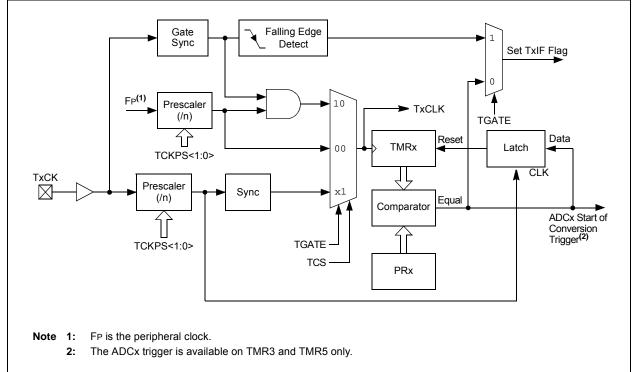

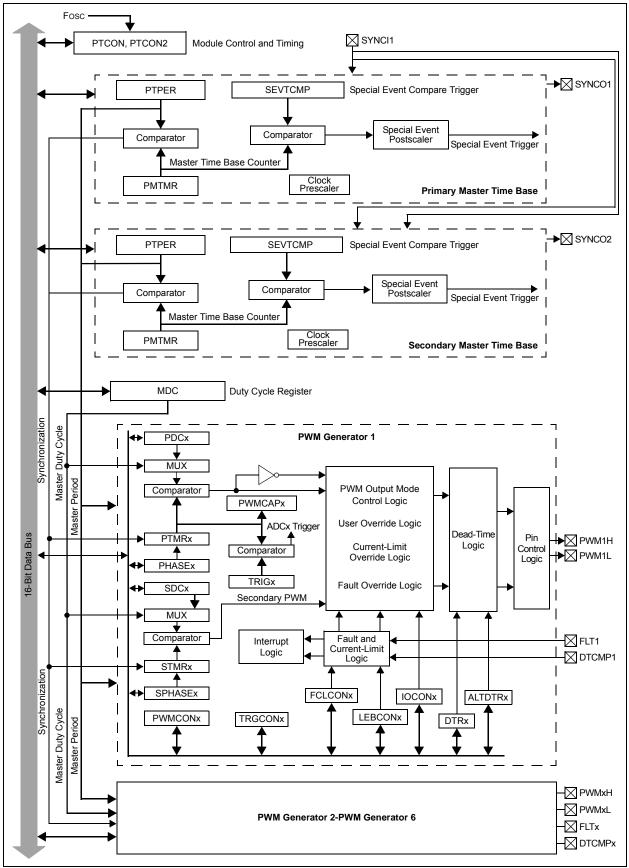

#### FIGURE 13-1: TYPE B TIMER BLOCK DIAGRAM (x = 2, 4, 6 AND 8)

| HS/HC-0    | ) HS/HC-0                                                                        | HS/HC-0                                                                                                         | R/W-0                         | R/W-0              | R/W-0                | R/W-0                | R/W-0               |  |

|------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------|----------------------|----------------------|---------------------|--|

| FLTSTAT(   | (1) CLSTAT <sup>(1)</sup>                                                        | TRGSTAT                                                                                                         | FLTIEN                        | CLIEN              | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |  |

| bit 15     |                                                                                  |                                                                                                                 |                               |                    |                      | •                    | bit 8               |  |

|            |                                                                                  |                                                                                                                 |                               |                    |                      |                      |                     |  |

| R/W-0      | R/W-0                                                                            | R/W-0                                                                                                           | U-0                           | R/W-0              | R/W-0                | R/W-0                | R/W-0               |  |

| DTC1       | DTC0                                                                             | DTCP <sup>(3)</sup>                                                                                             | <u> </u>                      | MTBS               | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |  |

| bit 7      |                                                                                  |                                                                                                                 |                               |                    |                      |                      | bit                 |  |

|            |                                                                                  |                                                                                                                 |                               |                    |                      |                      |                     |  |

| Legend:    |                                                                                  | HC = Hardware                                                                                                   |                               |                    | are Settable bit     |                      |                     |  |

| R = Reada  |                                                                                  | W = Writable b                                                                                                  | it                            | -                  | mented bit, rea      |                      |                     |  |

| -n = Value | at POR                                                                           | '1' = Bit is set                                                                                                |                               | '0' = Bit is cle   | eared                | x = Bit is unkr      | IOWN                |  |

| bit 15     |                                                                                  | ault Interrupt Sta                                                                                              | tue hit(1)                    |                    |                      |                      |                     |  |

| DIL 15     |                                                                                  | errupt is pending                                                                                               |                               |                    |                      |                      |                     |  |

|            |                                                                                  | interrupt is pending                                                                                            |                               |                    |                      |                      |                     |  |

|            | This bit is cle                                                                  | ared by setting:                                                                                                | FLTIEN = 0.                   |                    |                      |                      |                     |  |

| bit 14     | CLSTAT: Cu                                                                       | rrent-Limit Interi                                                                                              | upt Status bit <sup>(1)</sup> | )                  |                      |                      |                     |  |

|            |                                                                                  | imit interrupt is                                                                                               |                               |                    |                      |                      |                     |  |

|            |                                                                                  | nt-limit interrupt                                                                                              |                               |                    |                      |                      |                     |  |

| bit 13     |                                                                                  | This bit is cleared by setting: CLIEN = 0.                                                                      |                               |                    |                      |                      |                     |  |

| DIC 15     | <b>TRGSTAT:</b> Trigger Interrupt Status bit<br>1 = Trigger interrupt is pending |                                                                                                                 |                               |                    |                      |                      |                     |  |

|            |                                                                                  | r interrupt is pe                                                                                               | •                             |                    |                      |                      |                     |  |

|            | This bit is cle                                                                  | ared by setting:                                                                                                | TRGIEN = 0.                   |                    |                      |                      |                     |  |

| bit 12     |                                                                                  | It Interrupt Enat                                                                                               |                               |                    |                      |                      |                     |  |

|            |                                                                                  | errupt is enabled<br>errupt is disabled                                                                         |                               | TAT bit is clear   | red                  |                      |                     |  |

| bit 11     | CLIEN: Curre                                                                     | ent-Limit Interru                                                                                               | pt Enable bit                 |                    |                      |                      |                     |  |

|            |                                                                                  | imit interrupt is of init interrupt is of init interrupt is of the second second second second second second se |                               | e CLSTAT bit i     | s cleared            |                      |                     |  |

| bit 10     |                                                                                  | gger Interrupt E                                                                                                |                               |                    |                      |                      |                     |  |

|            |                                                                                  | event generate                                                                                                  |                               | equest             |                      |                      |                     |  |

|            |                                                                                  | vent interrupts a                                                                                               |                               | d the TRGSTA       | T bit is cleared     |                      |                     |  |

| bit 9      | ITB: Indepen                                                                     | ident Time Base                                                                                                 | e Mode bit <sup>(2)</sup>     |                    |                      |                      |                     |  |

|            |                                                                                  | register provide<br>egister provides                                                                            |                               |                    |                      | ator                 |                     |  |

| bit 8      | MDCS: Mast                                                                       | er Duty Cycle R                                                                                                 | legister Select I             | oit <sup>(2)</sup> |                      |                      |                     |  |

|            | 1 = MDC reg                                                                      | ister provides d<br>gister provides d                                                                           | uty cycle inform              | nation for this F  | -                    |                      |                     |  |

| Note 1:    | Software must cle                                                                | ear the interrupt                                                                                               | status here and               | d in the corres    | ponding IFSx b       | it in the interru    | pt controller.      |  |

|            | These bits should                                                                | •                                                                                                               |                               | -                  | •                    |                      |                     |  |

|            | DTC<1:0> = 11 fo                                                                 | -                                                                                                               |                               |                    |                      |                      |                     |  |

|            | The Independent<br>CAM bit is ignore                                             |                                                                                                                 | 5 = 1) mode mu                | st be enabled i    | to use Center-A      | Aligned mode. I      | If ITB = 0, the     |  |

|            |                                                                                  |                                                                                                                 |                               |                    |                      |                      |                     |  |

## REGISTER 16-11: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

## REGISTER 17-2: QEIXIOC: QEIX I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control bit

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control and SWPAB Pin Swapping bit

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 0 QEA: Status of QEAx Input Pin After Polarity Control and SWPAB Pin Swapping bit

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

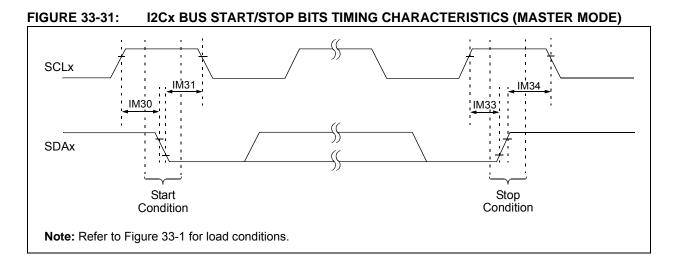

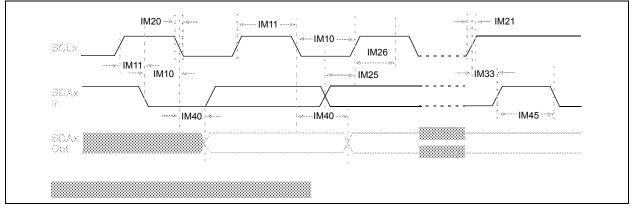

## 19.0 INTER-INTEGRATED CIRCUIT<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70000195), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX family of devices contains two Inter-Integrated Circuit ( $I^2C$ ) modules: I2C1 and I2C2.

The  $I^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface. The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx pin is clock.

- The SDAx pin is data.

The  $I^2C$  module offers the following key features:

- I<sup>2</sup>C Interface Supporting both Master and Slave modes of Operation.

- I<sup>2</sup>C Slave mode Supports 7 and 10-Bit Addressing.

- I<sup>2</sup>C Master mode Supports 7 and 10-Bit Addressing.

- I<sup>2</sup>C Port Allows Bidirectional Transfers Between Master and Slaves.

- Serial Clock Synchronization for I<sup>2</sup>C Port can be used as a Handshake Mechanism to Suspend and Resume Serial Transfer (SCLREL control).

- I<sup>2</sup>C Supports Multi-Master Operation, Detects Bus Collision and Arbitrates Accordingly.

- Intelligent Platform Management Interface (IPMI)

Support

- System Management Bus (SMBus) Support

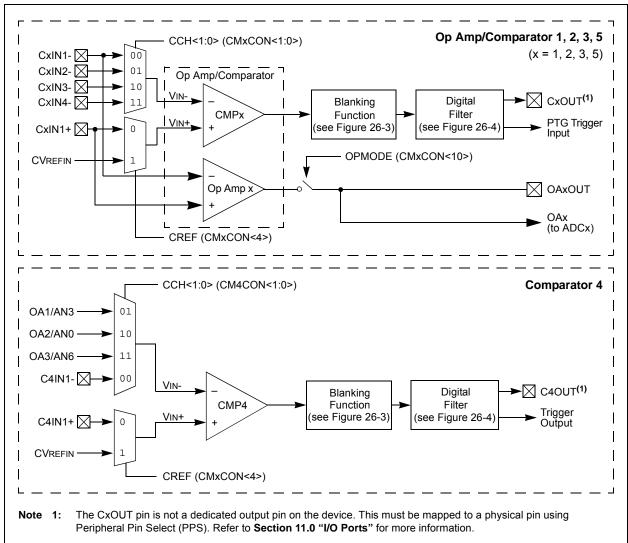

## 26.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGM3XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Op Amp/ Comparator" (DS70000357), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGM3XX/6XX/7XX devices contain up to five comparators that can be configured in various ways. Comparators, CMP1, CMP2, CMP3 and CMP5, also have the option to be configured as op amps, with the output being brought to an external pin for gain/ filtering connections. As shown in Figure 26-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

These options allow users to:

- · Select the edge for trigger and interrupt generation

- · Configure the comparator voltage reference

- · Configure output blanking and masking

- Configure as a comparator or op amp (CMP1, CMP2, CMP3 and CMP5 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

#### FIGURE 26-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM

| R/W-0                 | R/W-0                                                   | R/W-0                                                                   | U-0                 | U-0              | U-0             | R/W-0               | R/W-0               |  |

|-----------------------|---------------------------------------------------------|-------------------------------------------------------------------------|---------------------|------------------|-----------------|---------------------|---------------------|--|

| CON                   | COE                                                     | CPOL                                                                    |                     |                  |                 | CEVT <sup>(2)</sup> | COUT                |  |

| bit 15                |                                                         |                                                                         |                     |                  |                 |                     | bit                 |  |

|                       |                                                         |                                                                         |                     |                  |                 |                     |                     |  |

| R/W-0                 | R/W-0                                                   | U-0                                                                     | R/W-0               | U-0              | U-0             | R/W-0               | R/W-0               |  |

| EVPOL1 <sup>(2)</sup> | EVPOL0 <sup>(2)</sup>                                   | —                                                                       | CREF <sup>(1)</sup> | —                | —               | CCH1 <sup>(1)</sup> | ССН0 <sup>(1)</sup> |  |

| bit 7                 |                                                         |                                                                         |                     |                  |                 |                     | bit                 |  |

| Legend:               |                                                         |                                                                         |                     |                  |                 |                     |                     |  |

| R = Readable          | bit                                                     | W = Writable                                                            | bit                 | U = Unimpler     | nented bit, rea | ıd as '0'           |                     |  |

| -n = Value at F       | POR                                                     | '1' = Bit is set                                                        | t                   | '0' = Bit is cle | ared            | x = Bit is unkn     | iown                |  |

| bit 14<br>bit 13      | 0 = Comparat                                            | or is disabled<br>rator Output E<br>or output is pr<br>or output is int | esent on the C      | ·                |                 |                     |                     |  |

| DIL 13                | 1 = Comparat<br>0 = Comparat                            | or output is in                                                         | verted              | Dit              |                 |                     |                     |  |

| bit 12-10             | Unimplemented: Read as '0'                              |                                                                         |                     |                  |                 |                     |                     |  |

| bit 9                 | CEVT: Compa                                             | arator Event bi                                                         | t <sup>(2)</sup>    |                  |                 |                     |                     |  |

|                       |                                                         | until the bit is                                                        | cleared             | VPOL<1:0> se     | ttings, occurre | ed; disables futur  | e triggers an       |  |

| bit 8                 | COUT: Compa                                             | arator Output                                                           | bit                 |                  |                 |                     |                     |  |

|                       | When CPOL         1 = VIN+ > VIN         0 = VIN+ < VIN | 1-                                                                      | ed polarity):       |                  |                 |                     |                     |  |

|                       | When CPOL =                                             | = 1 (inverted p                                                         | olarity):           |                  |                 |                     |                     |  |

2: After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator Event bit, CEVT (CMxCON<9>), and the Comparator Combined Interrupt Flag, CMPIF (IFS1<2>), **must be cleared** before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

## **REGISTER 28-1: PMCON: PARALLEL MASTER PORT CONTROL REGISTER<sup>(3)</sup> (CONTINUED)**

- bit 3 **CS1P:** Chip Select 0 Polarity bit<sup>(1)</sup> 1 = Active-high (PMCS1/PMCS)<sup>(2)</sup> 0 = Active-low (PMCS1/PMCS)

- bit 2 **BEP:** Byte Enable Polarity bit

- 1 = Byte enable is active-high (PMBE)

- 0 = Byte enable is active-low (PMBE)

- bit 1

WRSP: Write Strobe Polarity bit

For Slave Modes and Master Mode 2 (PMMODE<9:8> = 00, 01, 10):

1 = Write strobe is active-high (PMWR)

0 = Write strobe is active-low (PMWR)

For Master Mode 1 (PMMODE<9:8> = 11):

1 = Enables strobe active-high (PMENB)

0 = Enables strobe active-low (PMENB)

0 = Enables strobe active-low (PMENB)

bit 0

RDSP: Read Strobe Polarity bit

For Slave Modes and Master Mode 2 (PMMODE<9:8> = 00, 01, 10):

1 = Read strobe is active-high (PMRD)

- 0 = Read strobe is active-ligh (PMRD)

- 0 Read Strobe is active-low (FIVIRD)

- For Master Mode 1 (PMMODE<9:8> = 11):

- 1 = Enables strobe active-high (PMRD/PMWR)

- 0 = Enables strobe active-low (PMRD/PMWR)

- **Note 1:** These bits have no effect when their corresponding pins are used as address lines.

- 2: PMCS1 applies to Master mode and PMCS applies to Slave mode.

- 3: This register is not available on 44-pin devices.

## 33.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33EPXXXGM3XX/6XX/7XX electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXXGM3XX/6XX/7XX family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## **Absolute Maximum Ratings**

### (See Note 1)

| Ambient temperature under bias                                                | 40°C to +125°C       |

|-------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                           | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                            | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\geq 3.0V^{(3)}$ | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD < 3.0V^{(3)}$    | -0.3V to +3.6V       |

| Voltage on VCAP with respect to Vss                                           | 1.62V to 1.98V       |

| Maximum current out of Vss pin                                                | 350 mA               |

| Maximum current into Vod pin <sup>(2)</sup>                                   | 350 mA               |

| Maximum current sunk by any I/O pin                                           | 20 mA                |

| Maximum current sourced by I/O pin                                            |                      |

| Maximum current sourced/sunk by all ports <sup>(2,4)</sup>                    | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 33-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

- 4: Exceptions are: RA3, RA4, RA7, RA9, RA10, RB7-RB15, RC3, RC15, RD1-RD4, which are able to sink 30 mA and source 20 mA.

## 33.2 AC Characteristics and Timing Parameters

This section defines the dsPIC33EPXXXGM3XX/6XX/ 7XX AC characteristics and timing parameters.

#### TABLE 33-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)                                                                                                                        |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature -40°C ≤ TA ≤ +85°C for Industrial<br>-40°C ≤ TA ≤ +125°C for Extended<br>Operating voltage VDD range as described in <b>Section 33.1 "DC</b><br><b>Characteristics</b> ". |

|                    |                                                                                                                                                                                                 |

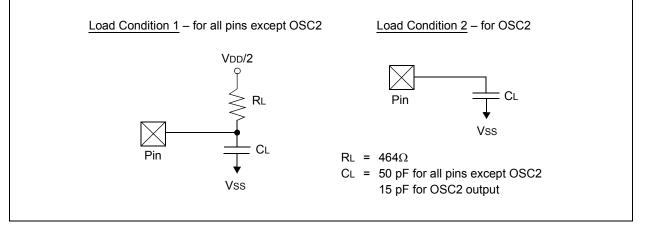

## FIGURE 33-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 33-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   | pF    | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Cio    | All I/O Pins and OSC2 | —    | —    | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            | _    | —    | 400  | pF    | In l <sup>2</sup> C™ mode                                           |

# TABLE 33-36:SPI2 AND SPI3 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                |  |

|--------------------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|--|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                    | Тур. <sup>(2)</sup> | Max. | Units | Conditions                     |  |

| SP70               | FscP                  | Maximum SCKx Input Frequency                 |                                                                                                                                                                                                                                                                                         |                     | 15   | MHz   | (Note 3)                       |  |

| SP72               | TscF                  | SCKx Input Fall Time                         | —                                                                                                                                                                                                                                                                                       | _                   | -    | ns    | See Parameter DO32<br>(Note 4) |  |

| SP73               | TscR                  | SCKx Input Rise Time                         | —                                                                                                                                                                                                                                                                                       | _                   | _    | ns    | See Parameter DO31<br>(Note 4) |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                   | —                                                                                                                                                                                                                                                                                       | _                   | -    | ns    | See Parameter DO32<br>(Note 4) |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                       | _                   | -    | ns    | See Parameter DO31<br>(Note 4) |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    | —                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                                |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge | 30                                                                                                                                                                                                                                                                                      | _                   | _    | ns    |                                |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge   | 30                                                                                                                                                                                                                                                                                      | _                   |      | ns    |                                |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge    | 30                                                                                                                                                                                                                                                                                      | _                   |      | ns    |                                |  |

| SP50               | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↑ or SCKx ↓<br>Input           | 120                                                                                                                                                                                                                                                                                     | _                   | _    | ns    |                                |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance       | 10                                                                                                                                                                                                                                                                                      | —                   | 50   | ns    | (Note 4)                       |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                        | 1.5 Tcy + 40                                                                                                                                                                                                                                                                            | —                   | _    | ns    | (Note 4)                       |  |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge     | —                                                                                                                                                                                                                                                                                       | —                   | 50   | ns    |                                |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

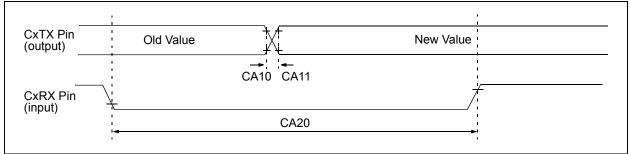

#### TABLE 33-50: CANx MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                    |