Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product StatusActiveCore Processor8052Core Size8-BitSpeed40MHzConnectivityEBI/EMI, UART/USARTPeripheralsPOR, WDTNumber of I/O36Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size-Voltage - Supply (Vcc/Vdd)2.4V ~ 5.5VData Converters-Operating Temperature4.0°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package-Purchase URLhttps://www.e-xfl.com/product-detail/nuvcton-technology-corporation-america/W78e516dlg | Becano                     |                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------|

| Core Size8-BitSpeed40MHzConnectivityEBI/EMI, UART/USARTPeripheralsPOR, WDTNumber of I/O36Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size-RAM SizeS12 x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package-                                                                                                   | Product Status             | Active                                                                                 |

| Speed40MHzConnectivityEB//EMI, UART/USARTPeripheralsPOR, WDTNumber of I/O36Program Memory Size64KB (64K × 8)Program Memory TypeFLASHEEPROM Size-S12 × 8Voltage - Supply (Vcc/Vdd)2.4V ~ 5.5VData Converters-Oscillator Type4.0°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case4.0CPPSupplier Device Package-                                                                                                                                                       | Core Processor             | 8052                                                                                   |

| ConnectivityEBI/EMI, UART/USARTPeripheralsPOR, WDTNumber of I/O36Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package-                                                                                                                           | Core Size                  | 8-Bit                                                                                  |

| PeripheralsPOR, WDTNumber of I/O36Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package-                                                                                                                                                          | Speed                      | 40MHz                                                                                  |

| Number of I/O36Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package-                                                                                                                                                                             | Connectivity               | EBI/EMI, UART/USART                                                                    |

| Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package-                                                                                                                                                                                            | Peripherals                | POR, WDT                                                                               |

| Program Memory TypeFLASHEEPROM Size-RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package-                                                                                                                                                                                                                             | Number of I/O              | 36                                                                                     |

| EEPROM Size-RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package-                                                                                                                                                                                                                                                     | Program Memory Size        | 64KB (64K × 8)                                                                         |

| RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.4V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package-                                                                                                                                                                                                                                                                 | Program Memory Type        | FLASH                                                                                  |

| Voltage - Supply (Vcc/Vdd)2.4V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device Package-https://www.e.vfl.com/product.detail/nuvoton.technology.comparation.amprice/w78e516dln                                                                                                                                                                                          | EEPROM Size                | -                                                                                      |

| Data Converters     -       Oscillator Type     External       Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     Surface Mount       Package / Case     48-LQFP       Supplier Device Package     -                                                                                                                                                                                                                                                    | RAM Size                   | 512 x 8                                                                                |

| Oscillator Type     External       Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     Surface Mount       Package / Case     48-LQFP       Supplier Device Package     -                                                                                                                                                                                                                                                                                | Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                            |

| Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     Surface Mount       Package / Case     48-LQFP       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                   | Data Converters            | -                                                                                      |

| Mounting Type     Surface Mount       Package / Case     48-LQFP       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                                                     | Oscillator Type            | External                                                                               |

| Package / Case 48-LQFP<br>Supplier Device Package -<br>https://www.e.vfl.com/product.detail/nuvoton_technology_corporation_america/w78e516dla                                                                                                                                                                                                                                                                                                                            | Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Supplier Device Package                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Mounting Type              | Surface Mount                                                                          |

| https://www.e.vfl.com/product.detail/puyeten_technology_corporation_america/w78e516dlg                                                                                                                                                                                                                                                                                                                                                                                   | Package / Case             | 48-LQFP                                                                                |

| Purchase URL https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w78e516dlg                                                                                                                                                                                                                                                                                                                                                                      | Supplier Device Package    | -                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w78e516dlg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2 FEATURES

- Fully static design 8-bit CMOS microcontroller

- Optional 12T or 6T mode

- 12T Mode, 12 clocks per machine cycle operation (default), Speed up to 40 MHz/5V

- 6T Mode, 6 clocks per machine cycle operation set by the writer, Speed up to 20 MHz/5V

- Wide supply voltage of 2.4 to 5.5V

- Temperature grade is (-40°C~85°C)

- 64K/32K bytes of in-system programmable FLASH EPROM for Application Program (APROM)

- 4K bytes of auxiliary FLASH EPROM for Loader Program (LDROM)

- Low standby current at full supply voltage

- 512 bytes of on-chip RAM. (include 256 bytes of AUX-RAM, software selectable)

- 64K bytes program memory address space and 64K bytes data memory address space

- One 4-bit multipurpose programmable port, additional INT2 / INT3

- Support Watch Dog Timer

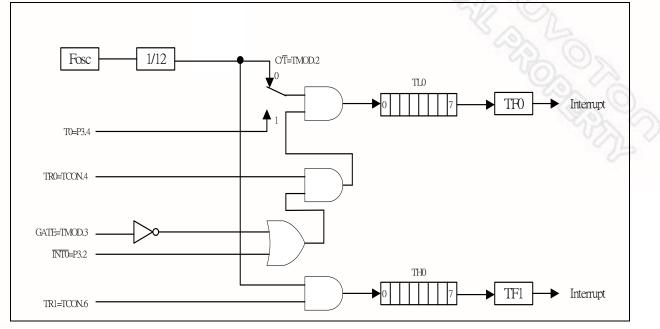

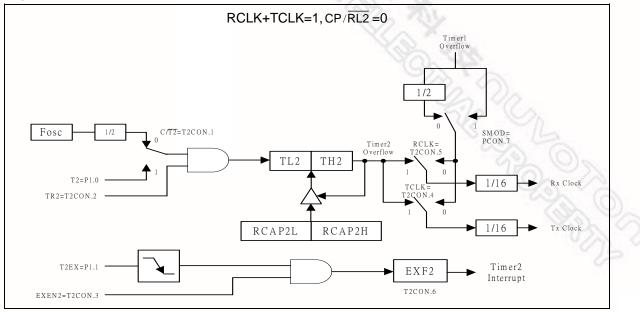

- Three 16-bit timer/counters

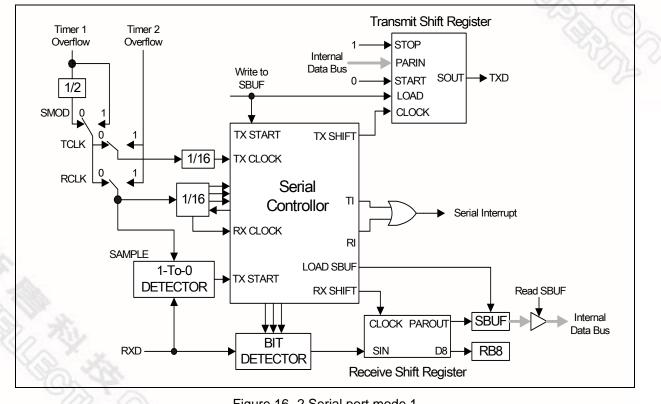

- One full duplex serial port

- 8-sources, 2-level interrupt capability

- Software Reset

- Built-in power management with idle mode and power down mode

- Code protection

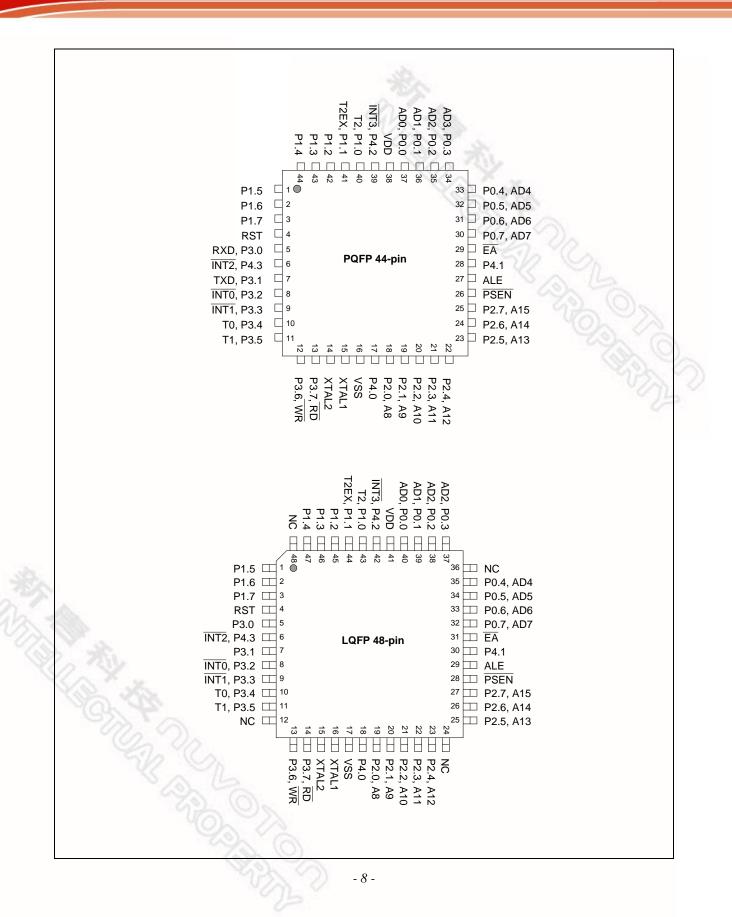

- Packages:

- Lead Free (RoHS) DIP 40: W78E516DDG

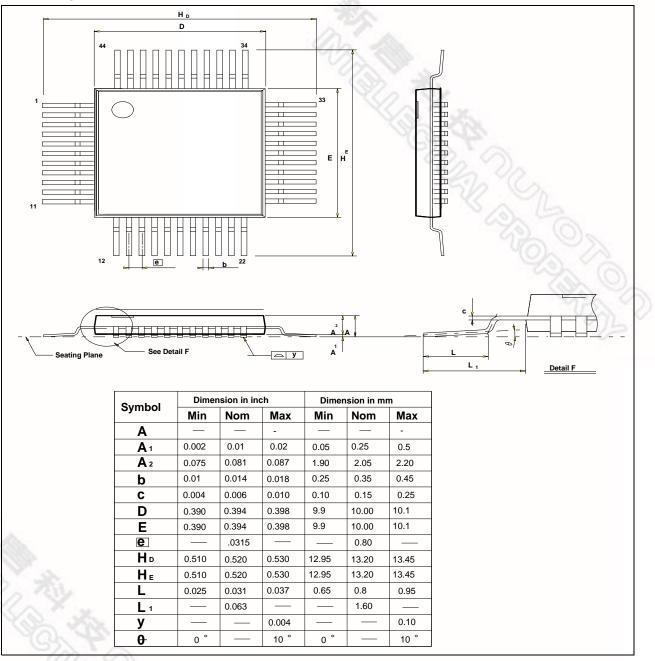

- Lead Free (RoHS) PLCC 44: W78E516DPG

- Lead Free (RoHS) PQFP 44: W78E516DFG

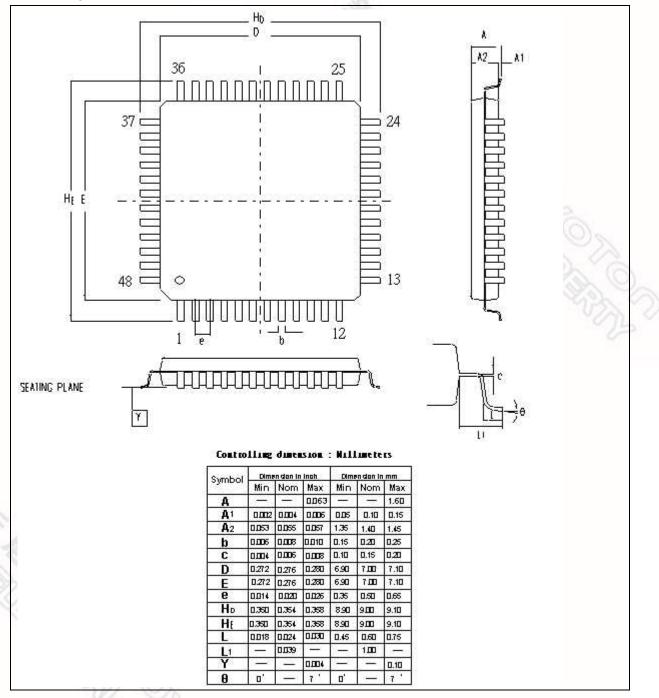

- Lead Free (RoHS) LQFP 48: W78E516DLG

- Lead Free (RoHS) DIP 40: W78E058DDG

- Lead Free (RoHS) PLCC 44: W78E058DPG

- Lead Free (RoHS) PQFP 44: W78E058DFG

- Lead Free (RoHS) LQFP 48: W78E058DLG

W78E516D/W78E058D Data Sheet

### nuvoTon

### **5 PIN DESCRIPTIONS**

| SYMBOL    | TYPE  | DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EA        | I     | <b>EXTERNAL ACCESS ENABLE:</b> This pin forces the processor to execute the external ROM. The ROM address and data will not be present on the bus if the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           |       | $\overline{EA}$ pin is high and the program counter is within the internal ROM area. Oth erwise they will be present on the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PSEN      | ОН    | <b>PROGRAM STORE ENABLE:</b> PSEN enables the external ROM data in the Port 0 address/data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           |       | When internal ROM access is performed, no <b>PSEN</b> strobe signal outputs or ginate from this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ALE       | ОН    | ADDRESS LATCH ENABLE: ALE is used to enable the address latch that separates the address from the data on Port 0. ALE runs at 1/6th of the oscillator frequency. An ALE pulse is omitted during external data memory accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RST       | I L   | <b>RESET:</b> A high on this pin for two machine cycles while the oscillator is run ning resets the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XTAL1     | I     | <b>CRYSTAL 1:</b> This is the crystal oscillator input. This pin may be driven by a external clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| XTAL2     | 0     | <b>CRYSTAL 2:</b> This is the crystal oscillator output. It is the inversion of XTAL1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VSS       | I     | GROUND: ground potential.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VDD       | I     | POWER SUPPLY: Supply voltage for operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P0.0–P0.7 | I/O D | <b>PORT 0:</b> Port 0 is an <b>open-drain bi-directional I/O port</b> . This port also provides a multiplexed low order address/data bus during accesses to externate memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P1.0–P1.7 | I/O H | <b>PORT 1</b> : Port 1 is a bi-directional I/O port with internal pull-ups. The bits hav alternate functions which are described below: T2(P1.0): Timer/Counter 2 external count input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           |       | T2EX(P1.1): Timer/Counter 2 Reload/Capture/Direction control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P2.0–P2.7 | I/O H | <b>PORT 2:</b> Port 2 is a bi-directional I/O port with internal pull-ups. This port als provides the upper address bits for accesses to external memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P3.0–P3.7 | I/O H | <b>PORT 3:</b> Port 3 is a bi-directional I/O port with internal pull-ups. All bits hav alternate functions, which are described below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|           |       | RXD(P3.0): Serial Port 0 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| S-1       |       | TXD(P3.1): Serial Port 0 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           |       | INT0 (P3.2) : External Interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.25      |       | INT1 (P3.3) : External Interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2 24      |       | T0(P3.4) : Timer 0 External Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10 ° J    | 5     | T1(P3.5) : Timer 1 External Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| S.S.      | 12    | WR (P3.6) : External Data Memory Write Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -07,      | 5     | RD (P3.7) : External Data Memory Read Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P4.0-P4.3 | I/O H | <b>PORT 4:</b> Another bit-addressable bidirectional I/O port P4. P4.3 and P4.2 ar alternative function pins. It can be used as general I/O port or external interruption provided and provided as general I/O port or external interruption provided as general I/O port or |

\* Note : TYPE I: input, O: output, I/O: bi-directional, H: pull-high, L: pull-low, D: open drain

#### 7.7.5 Stack Pointer

The W78E516D/W78E058D series has an 8-bit Stack Pointer which points to the top of the Stack. This stack resides in the Scratch Pad RAM in the W78E516D/W78E058D series. Hence the size of the stack is limited by the size of this RAM.

#### 7.7.6 Scratch-pad RAM

The W78E516D/W78E058D series has a 256 bytes on-chip scratch-pad RAM. This can be used by the user for temporary storage during program execution. A certain section of this RAM is bit addressable, and can be directly addressed for this purpose.

#### 7.7.7 AUX-RAM

AUX-RAM 0H~255H is addressed indirectly as the same way to access external data memory with the MOVX instruction. The data memory region is from 0000H to 00FFH. Memory MAP shows the memory map for this product series. W78E516D/W78E058D series can read/write 256 bytes AUX RAM by the MOVX instruction.

| BIT | NAME        | FUNCTION                                                                                            |

|-----|-------------|-----------------------------------------------------------------------------------------------------|

| 7-0 | P42AL.[7:0] | The Base address register for comparator of P4.2. P42AL contains the low-<br>order byte of address. |

#### P4.2 Base Address High Byte Register

order byte of address.

| Bit: | 7                           | 6       | 5          | 4            | 3          | 2            | 1           | 0           |

|------|-----------------------------|---------|------------|--------------|------------|--------------|-------------|-------------|

|      | P42AH.7                     | P42AH.6 | P42AH.5    | P42AH.4      | P42AH.3    | P42AH.2      | P42AH.1     | P42AH.0     |

| Mnem | Mnemonic:P42AH Address: ADh |         |            |              |            |              |             | ddress: ADh |

| BIT  | NAME                        | FUNCT   | ON         |              |            | - Ch         | 500         |             |

| 7-0  | P42AH.[7:0]                 | The Bas | se address | register for | comparator | of P4.2. P42 | 2AH contain | s the High- |

#### **Port 2 Expanded Control**

| Bit: | 7       | 6       | 5       | 4       | 3 | 2 | 1 9 | 0     |

|------|---------|---------|---------|---------|---|---|-----|-------|

|      | P43CSIN | P42CSIN | P41CSIN | P40CSIN | - | - | -   | (D) V |

#### **Mnemonic: P2ECON**

| -   |          |                                                                                                                                                                                                                                                                         |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT | NAME     | FUNCTION                                                                                                                                                                                                                                                                |

| 7   | P43CSINV | The active polarity of P4.3 when pin P4.3 is defined as read and/or write strobe signal.<br>1 : P4.3 is active high when pin P4.3 is defined as read and/or write strobe signal.<br>0 : P4.3 is active low when pin P4.3 is defined as read and/or write strobe signal. |

| 6   | P42CSINV | The similarity definition as P43SINV.                                                                                                                                                                                                                                   |

| 5   | P41CSINV | The similarity definition as P43SINV.                                                                                                                                                                                                                                   |

| 4   | P40CSINV | The similarity definition as P43SINV.                                                                                                                                                                                                                                   |

#### Port 3

| Bit: | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|------|

|      | P3.7 | P3.6 | P3.5 | P3.4 | P3.3 | P3.2 | P3.1 | P3.0 |

#### Mnemonic: P3

Address: B0h

Address:AEh

P3.7-0: General purpose Input/Output port. Most instructions will read the port pins in case of a port read access, however in case of read-modify-write instructions, the port latch is read. These alternate functions are described below:

| BIT | NAME | FUNCTION |

|-----|------|----------|

| 7   | P3.7 | RD       |

| 6   | P3.6 | WR       |

| 5   | P3.5 | T1 b     |

| 4   | P3.4 | ТО       |

- 27 -

### W78E516D/W78E058D Data Sheet

# nuvoTon

| Op-code           | HEX Code | Bytes | W78E516D/W78E058D series Clock cycles |

|-------------------|----------|-------|---------------------------------------|

| XRL A, R4         | 6C       | 1     | 12                                    |

| XRL A, R5         | 6D       | 1 6   | 12                                    |

| XRL A, R6         | 6E       | 1     | 12                                    |

| XRL A, R7         | 6F       | 1     | 12                                    |

| XRL A, @R0        | 66       | 1     | 12                                    |

| XRL A, @R1        | 67       | 1     | 12                                    |

| XRL A, direct     | 65       | 2     | 12                                    |

| XRL A, #data      | 64       | 2     | 12                                    |

| XRL direct, A     | 62       | 2     | 12                                    |

| XRL direct, #data | 63       | 3     | 24                                    |

| CLR A             | E4       | 1     | 12                                    |

| CPL A             | F4       | 1     | 12                                    |

| RL A              | 23       | 1     | 12                                    |

| RLC A             | 33       | 1     | 12                                    |

| RR A              | 03       | 1     | 12                                    |

| RRC A             | 13       | 1     | 12                                    |

| SWAP A            | C4       | 1     | 12                                    |

| MOV A, R0         | E8       | 1     | 12                                    |

| MOV A, R1         | E9       | 1     | 12                                    |

| MOV A, R2         | EA       | 1     | 12                                    |

| MOV A, R3         | EB       | 1     | 12                                    |

| MOV A, R4         | EC       | 1     | 12                                    |

| MOV A, R5         | ED       | 1     | 12                                    |

| MOV A, R6         | EE       | 1     | 12                                    |

| MOV A, R7         | EF       | 1     | 12                                    |

| MOV A, @R0        | E6       | 1     | 12                                    |

| MOV A, @R1        | E7       | 1     | 12                                    |

| MOV A, direct     | E5       | 2     | 12                                    |

| MOV A, #data      | 74       | 2     | 12                                    |

| MOV R0, A         | F8       | 1     | 12                                    |

| MOV R1, A         | F9       | 1     | 12                                    |

| MOV R2, A         | FA       | 1     | 12                                    |

| MOV R3, A         | FB       | 1     | 12                                    |

| MOV R4, A         | FC       | 1     | 12                                    |

- 40 -

### 13 RESET CONDITIONS

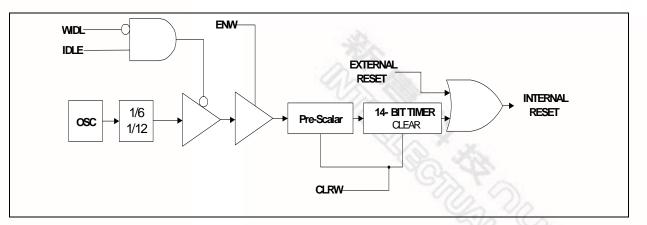

The user has several hardware related options for placing the W78E516D/W78E058D into reset condition. In general, most register bits go to their reset value irrespective of the reset condition, but there are a few flags whose state depends on the source of reset. The user can use these flags to determine the cause of reset using software.

#### 13.1 Sources of reset

#### 13.1.1 External Reset

The device continuously samples the RST pin at state S5P2 of every machine cycle. Therefore the RST pin must be held for at least 2 machine cycles (24 clock cycles) to ensure detection of a valid RST high. The reset circuitry then synchronously applies the internal reset signal. Thus the reset is a synchronous operation and requires the clock to be running to cause an external reset. For more timing descript, please reference the character 21.4.5 (Page 79).

Once the device is in reset condition, it will remain so as long as RST is 1. Even after RST is deactivated, the device will continue to be in reset state for up to two machine cycles, and then begin program execution from 0000h. There is no flag associated with the external reset condition.

#### 13.1.2 Watchdog Timer Reset

The Watchdog timer is a free running timer with programmable time-out intervals. The user can clear the watchdog timer at any time, causing it to restart the count. When the time-out interval is reached an interrupt flag is set. If the Watchdog reset is enabled and the watchdog timer is not cleared, the watchdog timer will generate a reset. This places the device into the reset condition. The reset condition is maintained by hardware for two machine cycles. Once the reset is removed the device will begin execution from 0000h.

#### 13.1.3 Software Reset

The W78E516D/W78E058D offers a software reset to switch back to the AP Flash EPROM. Setting CHPCON bits 0, 1 and 7 to logic-1 creates a software reset to reset the CPU.

#### 13.1.4 RESET STATE

Most of the SFRs and registers on the device will go to the same condition in the reset state. The Program Counter is forced to 0000h and is held there as long as the reset condition is applied. However, the reset state does not affect the on-chip RAM. The data in the RAM will be preserved during the reset. However, the stack pointer is reset to 07h, and therefore the stack contents will be lost. The RAM contents will be lost if the VDD falls below approximately 2V, as this is the minimum voltage level required for the RAM to operate normally. Therefore after a first time power on reset the RAM contents will be indeterminate. During a power fail condition, if the power falls below 2V, the RAM contents are lost.

After a reset most SFRs are cleared. Interrupts and Timers are disabled. The Watchdog timer is disabled if the reset source was a POR. The port SFRs have 0FFh written into them which puts the port No No No pins in a high state.

The interrupt flags are sampled every machine cycle. In the same machine cycle, the sampled interrupts are polled and their priority is resolved. If certain conditions are met then the hardware will execute an internally generated LCALL instruction which will vector the process to the appropriate interrupt vector address. The conditions for generating the LCALL are;

- 1. An interrupt of equal or higher priority is not currently being serviced.

- 2. The current polling cycle is the last machine cycle of the instruction currently being executed.

- 3. The current instruction does not involve a write to IE, IP, XICON registers and is not a RETI.

If any of these conditions are not met, then the LCALL will not be generated. The polling cycle is repeated every machine cycle, with the interrupts sampled in the same machine cycle. If an interrupt flag is active in one cycle but not responded to, and is not active when the above conditions are met, the denied interrupt will not be serviced. This means that active interrupts are not remembered; every polling cycle is new.