Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                 |

| Number of I/O              | 20                                                                            |

| Program Memory Size        | 12KB (4K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 512 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 6x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f2010-20i-mm |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### High-Performance, 16-bit Digital Signal Controller

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

#### High-Performance Modified RISC CPU:

- Modified Harvard architecture

- C compiler optimized instruction set architecture

- 83 base instructions with flexible addressing modes

- 24-bit wide instructions, 16-bit wide data path

- 12 Kbytes on-chip Flash program space

- · 512 bytes on-chip data RAM

- 1 Kbyte nonvolatile data EEPROM

- 16 x 16-bit working register array

- Up to 30 MIPs operation:

- DC to 40 MHz external clock input

- 4 MHz-10 MHz oscillator input with PLL active (4x, 8x, 16x)

- 27 interrupt sources

- Three external interrupt sources

- · Eight user-selectable priority levels for each interrupt

- · Four processor exceptions and software traps

#### **DSP Engine Features:**

- · Modulo and Bit-Reversed modes

- Two 40-bit wide accumulators with optional saturation logic

- 17-bit x 17-bit single-cycle hardware fractional/ integer multiplier

- Single-cycle Multiply-Accumulate (MAC) operation

- 40-stage Barrel Shifter

- Dual data fetch

#### **Peripheral Features:**

- High current sink/source I/O pins: 25 mA/25 mA

- Three 16-bit timers/counters; optionally pair up 16-bit timers into 32-bit timer modules

- Four 16-bit capture input functions

- Two 16-bit compare/PWM output functions

Dual Compare mode available

- 3-wire SPI modules (supports 4 Frame modes)

- I<sup>2</sup>C<sup>™</sup> module supports Multi-Master/Slave mode

- and 7-bit/10-bit addressing

- Addressable UART modules with FIFO buffers

#### Motor Control PWM Module Features:

- Six PWM output channels

- Complementary or Independent Output modes

- Edge and Center-Aligned modes

- Four duty cycle generators

- · Dedicated time base with four modes

- · Programmable output polarity

- · Dead-time control for Complementary mode

- Manual output control

- Trigger for synchronized A/D conversions

### Quadrature Encoder Interface Module Features:

- · Phase A, Phase B and Index Pulse input

- 16-bit up/down position counter

- Count direction status

- Position Measurement (x2 and x4) mode

- · Programmable digital noise filters on inputs

- Alternate 16-bit Timer/Counter mode

- · Interrupt on position counter rollover/underflow

#### **Analog Features:**

- 10-bit Analog-to-Digital Converter (ADC) with:

- 1 Msps (for 10-bit A/D) conversion rate

- Six input channels

- Conversion available during Sleep and Idle

- Programmable Brown-out Reset

#### 2.3 Divide Support

The dsPIC DSC devices feature a 16/16-bit signed fractional divide operation, as well as 32/16-bit and 16/ 16-bit signed and unsigned integer divide operations, in the form of single instruction iterative divides. The following instructions and data sizes are supported:

- DIVF 16/16 signed fractional divide

- DIV.sd 32/16 signed divide

- DIV.ud 32/16 unsigned divide

- DIV. sw 16/16 signed divide

- DIV.uw 16/16 unsigned divide

The 16/16 divides are similar to the 32/16 (same number of iterations), but the dividend is either zero-extended or sign-extended during the first iteration.

The divide instructions must be executed within a REPEAT loop. Any other form of execution (e.g., a series of discrete divide instructions) will not function correctly because the instruction flow depends on RCOUNT. The divide instruction does not automatically set up the RCOUNT value, and it must, therefore, be explicitly and correctly specified in the REPEAT instruction, as shown in Table 2-2 (REPEAT will execute the target instruction {operand value + 1} times). The REPEAT loop count must be set up for 18 iterations of the DIV/DIVF instruction. Thus, a complete divide operation requires 19 cycles.

**Note:** The Divide flow is interruptible; however, the user needs to save the context as appropriate.

#### 2.4 DSP Engine

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a barrel shifter, and a 40-bit adder/sub-tracter (with two target accumulators, round and saturation logic).

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations, which require no additional data. These instructions are ADD, SUB, and NEG.

The DSP engine has various options selected through various bits in the CPU Core Configuration Register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF).

- · Signed or unsigned DSP multiply (US).

- Conventional or convergent rounding (RND).

- Automatic saturation on/off for ACCA (SATA).

- Automatic saturation on/off for ACCB (SATB).

- Automatic saturation on/off for writes to data memory (SATDW).

- Accumulator Saturation mode selection (ACC-SAT).

**Note:** For CORCON layout, see Table 3-3.

A block diagram of the DSP engine is shown in Figure 2-2.

#### TABLE 2-1: DSP INSTRUCTION SUMMARY

| Instruction | Algebraic<br>Operation  | ACC WB? |

|-------------|-------------------------|---------|

| CLR         | A = 0                   | Yes     |

| ED          | $A = (x - y)^2$         | No      |

| EDAC        | $A = A + (x - y)^2$     | No      |

| MAC         | $A = A + (x \bullet y)$ | Yes     |

| MAC         | $A = A + x^2$           | No      |

| MOVSAC      | No change in A          | Yes     |

| MPY         | $A = x \bullet y$       | No      |

| MPY.N       | $A = -x \bullet y$      | No      |

| MSC         | $A = A - x \bullet y$   | Yes     |

#### TABLE 2-2: DIVIDE INSTRUCTIONS

| Instruction               | Function                                                               |  |  |  |  |  |

|---------------------------|------------------------------------------------------------------------|--|--|--|--|--|

| DIVF                      | Signed fractional divide: Wm/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1 |  |  |  |  |  |

| DIV.sd                    | Signed divide: (Wm + 1:Wm)/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1   |  |  |  |  |  |

| DIV.ud                    | Unsigned divide: (Wm + 1:Wm)/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1 |  |  |  |  |  |

| DIV.sw (Or DIV.s)         | Signed divide: Wm/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1            |  |  |  |  |  |

| DIV.uw ( <b>or</b> DIV.u) | Unsigned divide: Wm/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1          |  |  |  |  |  |

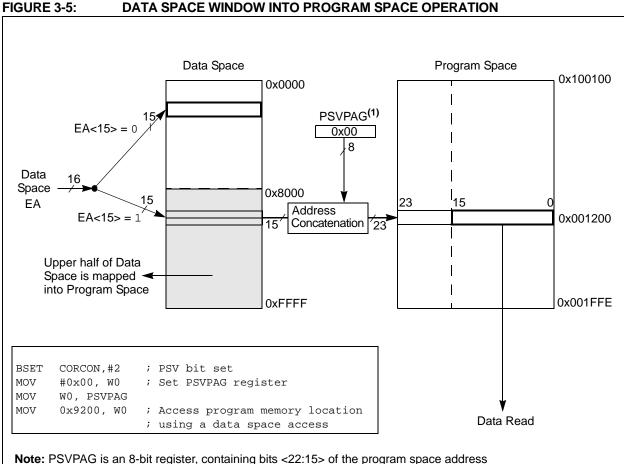

#### 3.1.2 DATA ACCESS FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word program space page. This provides transparent access of stored constant data from X data space, without the need to use special instructions (i.e., TBLRDL/H, TBLWTL/H instructions).

Program space access through the data space occurs if the MSb of the data space EA is set and program space visibility is enabled, by setting the PSV bit in the Core Control register (CORCON). The functions of CORCON are discussed in **Section 2.4** "**DSP Engine**".

Data accesses to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Note that the upper half of addressable data space is always part of the X data space. Therefore, when a DSP operation uses program space mapping to access this memory region, Y data space should typically contain state (variable) data for DSP operations, whereas X data space should typically contain coefficient (constant) data.

Although each data space address, 0x8000 and higher, maps directly into a corresponding program memory address (see Figure 3-5), only the lower 16-bits of the 24-bit program word are used to contain the data. The upper 8 bits should be programmed to force an illegal instruction to maintain machine robustness. Refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157) for details on instruction encoding.

Note that by incrementing the PC by 2 for each program memory word, the Least Significant 15 bits of data space addresses directly map to the Least Significant 15 bits in the corresponding program space addresses. The remaining bits are provided by the Program Space Visibility Page register, PSVPAG<7:0>, as shown in Figure 3-5.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | table reads/writes.                       |

For instructions that use PSV which are executed outside a REPEAT loop:

- The following instructions will require one instruction cycle in addition to the specified execution time:

- MAC class of instructions with data operand prefetch

- MOV instructions

- MOV.D instructions

- All other instructions will require two instruction cycles in addition to the specified execution time of the instruction.

For instructions that use PSV which are executed inside a  $\ensuremath{\mathtt{REPEAT}}$  loop:

- The following instances will require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

- Any other iteration of the REPEAT loop will allow the instruction, accessing data using PSV, to execute in a single cycle.

(i.e., it defines the page in program space to which the upper half of data space is being mapped).

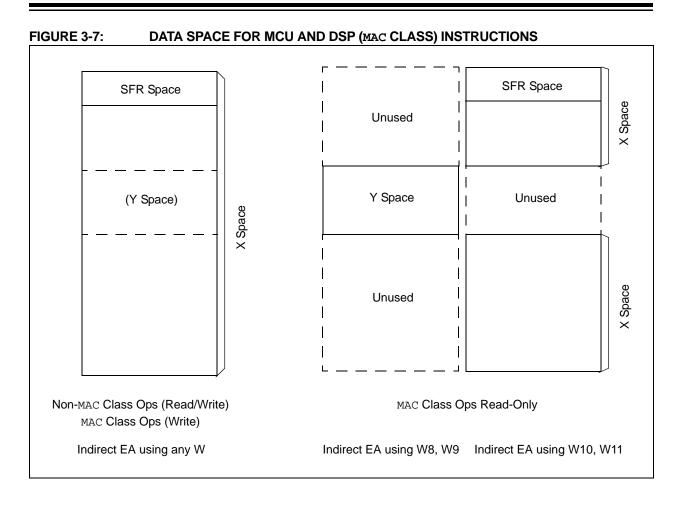

#### 3.2 Data Address Space

The core has two data spaces. The data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths.

#### 3.2.1 DATA SPACE MEMORY MAP

The data space memory is split into two blocks, X and Y data space. A key element of this architecture is that Y space is a subset of X space, and is fully contained within X space. In order to provide an apparent linear addressing space, X and Y spaces have contiguous addresses.

When executing any instruction other than one of the MAC class of instructions, the X block consists of the 256 byte data address space (including all Y addresses). When executing one of the MAC class of instructions, the X block consists of the 256 bytes data address space excluding the Y address block (for data reads only). In other words, all other instructions regard the entire data memory as one composite address space. The MAC class instructions extract the Y address space from data space and address it using EAs sourced from W10 and W11. The remaining X data space is addressed using W8 and W9. Both address spaces are concurrently accessed only with the MAC class instructions.

A data space memory map is shown in Figure 3-6.

#### TABLE 5-2: INTERRUPT CONTROLLER REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7  | Bit 6 | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0         | Reset State        |

|-------------|-------|--------|--------|-----------|--------|--------|--------|------------|--------|--------|-------|-------------|---------|---------|--------|-------------|---------------|--------------------|

| INTCON1     | 0080  | NSTDIS | —      | _         | _      | _      | OVATE  | OVBTE      | COVTE  | —      |       | _           | MATHERR | ADDRERR | STKERR | OSCFAIL     | —             | 0000 0000 0000 000 |

| INTCON2     | 0082  | ALTIVT | DISI   | _         | _      | _      |        | _          | _      | _      | -     |             | _       | _       | INT2EP | INT1EP      | INT0EP        | 0000 0000 0000 000 |

| IFS0        | 0084  | CNIF   | MI2CIF | SI2CIF    | NVMIF  | ADIF   | U1TXIF | U1RXIF     | SPI1IF | T3IF   | T2IF  | OC2IF       | IC2IF   | T1IF    | OC1IF  | IC1IF       | <b>INT0IF</b> | 0000 0000 0000 000 |

| IFS1        | 0086  |        | _      | _         |        |        | _      | _          |        | INT2IF |       | _           | _       | —       | IC8IF  | IC7IF       | INT1IF        | 0000 0000 0000 000 |

| IFS2        | 0088  |        | _      | _         |        | FLTAIF |        |            | QEIIF  | PWMIF  |       | _           | _       | —       | _      | _           |               | 0000 0000 0000 000 |

| IEC0        | 008C  | CNIE   | MI2CIE | SI2CIE    | NVMIE  | ADIE   | U1TXIE | U1RXIE     | SPI1IE | T3IE   | T2IE  | OC2IE       | IC2IE   | T1IE    | OC1IE  | IC1IE       | INT0IE        | 0000 0000 0000 000 |

| IEC1        | 008E  |        |        | _         |        |        | _      |            |        | INT2IE |       | _           | _       | _       | IC8IE  | IC7IE       | INT1IE        | 0000 0000 0000 000 |

| IEC2        | 0090  |        |        | _         |        | FLTAIE |        |            | QEIIE  | PWMIE  |       | —           | _       | _       | _      | _           | _             | 0000 0000 0000 000 |

| IPC0        | 0094  | _      | -      | T1IP<2:0> |        |        | C      | DC1IP<2:0  | >      | _      |       | IC1IP<      | 2:0>    | _       | I      | NT0IP<2:0:  | >             | 0100 0100 0100 010 |

| IPC1        | 0096  | _      | Т      | 31P<2:0   | >      | _      |        | T2IP<2:0>  |        | —      |       | OC2IP<      | :2:0>   | _       |        | IC2IP<2:0>  |               | 0100 0100 0100 010 |

| IPC2        | 0098  | —      | A      | ADIP<2:0> | >      | —      | U      | 1TXIP<2:0  | )>     | _      |       | U1RXIP<2:0> |         | _       | 5      | SPI1IP<2:0: | >             | 0100 0100 0100 010 |

| IPC3        | 009A  | —      | C      | CNIP<2:0> | >      | —      | N      | 112CIP<2:0 | )>     | —      |       | SI2CIP<     | <2:0>   | —       | 1      | VMIP<2:0    | >             | 0100 0100 0100 010 |

| IPC4        | 009C  |        |        | _         |        |        | l      | C8IP<2:0;  | >      | _      |       | IC7IP<      | 2:0>    | _       | I      | NT1IP<2:0:  | >             | 0100 0100 0100 010 |

| IPC5        | 009E  | _      | IN     | T2IP<2:0  | >      | _      |        |            | _      | —      |       | —           | _       | _       | _      | _           | _             | 0100 0000 0000 000 |

| IPC6        | 00A0  | _      | —      | _         | _      | —      | _      | _          | _      | —      | -     | —           | _       | _       | _      | _           | _             | 0000 0000 0000 000 |

| IPC7        | 00A2  | _      | _      | _         | _      | _      | _      | _          | _      | _      | _     | —           | _       | _       | _      | _           | _             | 0000 0000 0000 000 |

| IPC8        | 00A4  |        | _      | _         | _      |        | _      | _          |        | _      |       | _           | _       | _       | _      | _           |               | 0000 0000 0000 000 |

| IPC9        | 00A6  |        | P\     | WMIP<2:0  | )>     |        | _      |            |        | _      |       | _           | _       | _       | _      | _           |               | 0000 0000 0000 000 |

| IPC10       | 00A8  | _      | Fl     | _TAIP<2:0 | )>     | _      | _      | _          | _      | _      | _     | -           | _       | —       |        | QEIIP<2:0>  |               | 0100 0000 0000 010 |

| IPC11       | 00AA  | _      | _      | _         | _      | _      | Ι      | _          | _      | _      | _     |             | _       | _       | _      | _           | _             | 0000 0000 0000 000 |

Legend: — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

#### 6.4 RTSP Operation

The dsPIC30F Flash program memory is organized into rows and panels. Each row consists of 32 instructions, or 96 bytes. Each panel consists of 128 rows, or 4K x 24 instructions. RTSP allows the user to erase one row (32 instructions) at a time and to program 32 instructions at one time. RTSP may be used to program multiple program memory panels, but the table pointer must be changed at each panel boundary.

Each panel of program memory contains write latches that hold 32 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the panel write latches. The data to be programmed into the panel is loaded in sequential order into the write latches; instruction 0, instruction 1, etc. The instruction words loaded must always be from a 32 address boundary.

The basic sequence for RTSP programming is to set up a table pointer, then do a series of TBLWT instructions to load the write latches. Programming is performed by setting the special bits in the NVMCON register. 32 TBLWTL and four TBLWTH instructions are required to load the 32 instructions. If multiple panel programming is required, the table pointer needs to be changed and the next set of multiple write latches written.

All of the table write operations are single word writes (2 instruction cycles), because only the table latches are written. A programming cycle is required for programming each row.

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

#### 6.5 Control Registers

The four SFRs used to read and write the program Flash memory are:

- NVMCON

- NVMADR

- NVMADRU

- NVMKEY

#### 6.5.1 NVMCON REGISTER

The NVMCON register controls which blocks are to be erased, which memory type is to be programmed, and the start of the programming cycle.

#### 6.5.2 NVMADR REGISTER

The NVMADR register is used to hold the lower two bytes of the effective address. The NVMADR register captures the EA<15:0> of the last table instruction that has been executed and selects the row to write.

#### 6.5.3 NVMADRU REGISTER

The NVMADRU register is used to hold the upper byte of the effective address. The NVMADRU register captures the EA<23:16> of the last table instruction that has been executed.

#### 6.5.4 NVMKEY REGISTER

NVMKEY is a write-only register that is used for write protection. To start a programming or an erase sequence, the user must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 6.6 "Programming Operations"** for further details.

Note: The user can also directly write to the NVMADR and NVMADRU registers to specify a program memory address for erasing or programming.

#### 13.7 QEI Module Operation During CPU Idle Mode

Since the QEI module can function as a quadrature encoder interface, or as a 16-bit timer, the following section describes operation of the module in both modes.

#### 13.7.1 QEI OPERATION DURING CPU IDLE MODE

When the CPU is placed in the Idle mode, the QEI module will operate if the QEISIDL bit (QEICON<13>) = 0. This bit defaults to a logic '0' upon executing POR and BOR. For halting the QEI module during the CPU Idle mode, QEISIDL should be set to '1'.

#### 13.7.2 TIMER OPERATION DURING CPU IDLE MODE

When the CPU is placed in the Idle mode and the QEI module is configured in the 16-bit Timer mode, the 16-bit timer will operate if the QEISIDL bit (QEI-CON<13>) = 0. This bit defaults to a logic '0' upon executing POR and BOR. For halting the timer module during the CPU Idle mode, QEISIDL should be set to '1'.

If the QEISIDL bit is cleared, the timer will function normally, as if the CPU Idle mode had not been entered.

#### 13.8 Quadrature Encoder Interface Interrupts

The quadrature encoder interface has the ability to generate an interrupt on occurrence of the following events:

- Interrupt on 16-bit up/down position counter rollover/underflow

- Detection of qualified index pulse, or if CNTERR bit is set

- Timer period match event (overflow/underflow)

- · Gate accumulation event

The QEI interrupt flag bit, QEIIF, is asserted upon occurrence of any of the above events. The QEIIF bit must be cleared in software. QEIIF is located in the IFS2 status register.

Enabling an interrupt is accomplished via the respective enable bit, QEIIE. The QEIIE bit is located in the IEC2 Control register.

#### 14.5.1 DUTY CYCLE REGISTER BUFFERS

The four PWM duty cycle registers are double-buffered to allow glitchless updates of the PWM outputs. For each duty cycle, there is a duty cycle register that is accessible by the user and a second duty cycle register that holds the actual compare value used in the present PWM period.

For edge-aligned PWM output, a new duty cycle value will be updated whenever a match with the PTPER register occurs and PTMR is reset. The contents of the duty cycle buffers are automatically loaded into the duty cycle registers when the PWM time base is disabled (PTEN = 0) and the UDIS bit is cleared in PWMCON2.

When the PWM time base is in the Up/Down Counting mode, new duty cycle values are updated when the value of the PTMR register is zero and the PWM time base begins to count upwards. The contents of the duty cycle buffers are automatically loaded into the duty cycle registers when the PWM time base is disabled (PTEN = 0).

When the PWM time base is in the Up/Down Counting mode with double updates, new duty cycle values are updated when the value of the PTMR register is zero, and when the value of the PTMR register matches the value in the PTPER register. The contents of the duty cycle buffers are automatically loaded into the duty cycle registers when the PWM time base is disabled (PTEN = 0).

#### 14.6 Complementary PWM Operation

In the Complementary mode of operation, each pair of PWM outputs is obtained by a complementary PWM signal. A dead time may be optionally inserted during device switching, when both outputs are inactive for a short period (Refer to **Section 14.7** "**Dead-Time Generators**").

In Complementary mode, the duty cycle comparison units are assigned to the PWM outputs as follows:

- PDC1 register controls PWM1H/PWM1L outputs

- PDC2 register controls PWM2H/PWM2L outputs

- PDC3 register controls PWM3H/PWM3L outputs

The Complementary mode is selected for each PWM I/O pin pair by clearing the appropriate PMODx bit in the PWMCON1 SFR. The PWM I/O pins are set to Complementary mode by default upon a device Reset.

#### 14.7 Dead-Time Generators

Dead-time generation may be provided when any of the PWM I/O pin pairs are operating in the Complementary Output mode. The PWM outputs use Push-Pull drive circuits. Due to the inability of the power output devices to switch instantaneously, some amount of time must be provided between the turn off event of one PWM output in a complementary pair and the turn on event of the other transistor.

#### 14.7.1 DEAD-TIME GENERATORS

Each complementary output pair for the PWM module has a 6-bit down counter that is used to produce the dead-time insertion. As shown in Figure 14-4, the dead-time unit has a rising and falling edge detector connected to the duty cycle comparison output.

#### 14.7.2 DEAD-TIME RANGES

The amount of dead time provided by the dead-time unit is selected by specifying the input clock prescaler value and a 6-bit unsigned value.

Four input clock prescaler selections have been provided to allow a suitable range of dead times, based on the device operating frequency. The dead-time clock prescaler value is selected using the DTAPS<1:0> and DTBPS<1:0> control bits in the DTCON1 SFR. One of four clock prescaler options (TCY, 2 TCY, 4 TCY or 8 TCY) is selected for the dead-time value.

After the prescaler value is selected, the dead time is adjusted by loading a 6-bit unsigned value into the DTCON1 SFR.

The dead-time unit prescaler is cleared on the following events:

- On a load of the down timer due to a duty cycle comparison edge event.

- On a write to the DTCON1 register.

- On any device Reset.

**Note:** The user should not modify the DTCON1 values while the PWM module is operating (PTEN = 1). Unexpected results may occur.

#### TABLE 14-1: PWM REGISTER MAP

| SFR Name | Addr. | Bit 15                      | Bit 14                    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8       | Bit 7     | Bit 6    | Bit 5   | Bit 4   | Bit 3    | Bit 2     | Bit 1  | Bit 0  | R      | eset Sta | ite     |

|----------|-------|-----------------------------|---------------------------|--------|--------|--------|--------|---------|-------------|-----------|----------|---------|---------|----------|-----------|--------|--------|--------|----------|---------|

| PTCON    | 01C0  | PTEN                        | _                         | PTSIDL |        | —      | —      |         |             |           | PTO      | PS<3:0> |         | PTCKP    | S<1:0>    | PTMO   | D<1:0> | 0000 0 | 00 000   | 00 0000 |

| PTMR     | 01C2  | PTDIR PWM Timer Count Value |                           |        |        |        |        |         |             | 0000 0    | 00 00    | 00 0000 |         |          |           |        |        |        |          |         |

| PTPER    | 01C4  |                             |                           |        |        |        |        | P١      | NM Time E   | Base Peri | od Regis | ter     |         |          |           |        |        | 0011 1 | 111 11   | 11 1111 |

| SEVTCMP  | 01C6  | SEVTDIR                     |                           |        |        |        |        | PWM     | 1 Special E | vent Con  | npare Re | gister  |         |          | _         | -      |        | 0000 0 | 00 00    | 00 0000 |

| PWMCON1  | 01C8  | _                           | _                         | _      |        | _      | PTMOD3 | PTMOD2  | PTMOD1      |           | PEN3H    | PEN2H   | PEN1H   |          | PEN3L     | PEN2L  | PEN1L  | 0000 0 | 000 01   | 11 0111 |

| PWMCON2  | 01CA  | _                           | —                         | _      |        |        | SEVOP  | °S<3:0> |             |           | _        | _       |         |          | IUE       | OSYNC  | UDIS   | 0000 0 | 00 00    | 00 0000 |

| DTCON1   | 01CC  | DTBPS<                      | :1:0>                     |        |        | DTB<   | <5:0>  |         |             | DTAPS     | S<1:0>   |         |         | Dead Tim | e A Value |        |        | 0000 0 | 00 00    | 00 0000 |

| FLTACON  | 01D0  |                             | -                         | FAOV3H | FAOV3L | FAOV2H | FAOV2L | FAOV1H  | FAOV1L      | FLTAM     | _        | _       |         |          | FAEN3     | FAEN2  | FAEN1  | 0000 0 | 00 00    | 00 0000 |

| OVDCON   | 01D4  | _                           | _                         | POVD3H | POVD3L | POVD2H | POVD2L | POVD1H  | POVD1L      | _         | _        | POUT3H  | POUT3L  | POUT2H   | POUT2L    | POUT1H | POUT1L | 0011 1 | 111 00   | 00 0000 |

| PDC1     | 01D6  |                             |                           |        |        |        |        | PWN     | I Duty Cycl | e 1 Regi  | ster     |         |         |          |           |        |        | 0000 0 | 00 00    | 00 0000 |

| PDC2     | 01D8  |                             | PWM Duty Cycle 2 Register |        |        |        |        |         |             |           | 0000 0   | 00 000  | 00 0000 |          |           |        |        |        |          |         |

| PDC3     | 01DA  | PWM Duty Cycle 3 Register   |                           |        |        |        |        |         |             | 0000 0    | 00 00    | 00 0000 |         |          |           |        |        |        |          |         |

Legend: — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

#### 18.7.1 1 Msps CONFIGURATION GUIDELINE

The configuration for 1 Msps operation is dependent on whether a single input pin is to be sampled or whether multiple pins will be sampled.

#### 18.7.1.1 Single Analog Input

For conversions at 1 Msps for a single analog input, at least two sample and hold channels must be enabled. The analog input multiplexer must be configured so that the same input pin is connected to both sample and hold channels. The A/D converts the value held on one S/H channel, while the second S/H channel acquires a new input sample.

#### 18.7.1.2 Multiple Analog Inputs

The A/D converter can also be used to sample multiple analog inputs using multiple sample and hold channels. In this case, the total 1 Msps conversion rate is divided among the different input signals. For example, four inputs can be sampled at a rate of 250 ksps for each signal or two inputs could be sampled at a rate of 500 ksps for each signal. Sequential sampling must be used in this configuration to allow adequate sampling time on each input.

#### 18.7.1.3 1 Msps Configuration Items

The following configuration items are required to achieve a 1 Msps conversion rate.

- Comply with conditions provided in Table 19-2

- Connect external VREF+ and VREF- pins following the recommended circuit shown in Figure 18-2

- Set SSRC<2:0> = 111 in the ADCON1 register to enable the auto-convert option

- Enable automatic sampling by setting the ASAM control bit in the ADCON1 register

- Enable sequential sampling by clearing the SIMSAM bit in the ADCON1 register

- Enable at least two sample and hold channels by writing the CHPS<1:0> control bits in the ADCON2 register

- Write the SMPI<3:0> control bits in the ADCON2 register for the desired number of conversions between interrupts. At a minimum, set SMPI<3:0> = 0001 since at least two sample and hold channels should be enabled

- Configure the A/D clock period to be:

1 12 x 1,000,000 = 83.33 ns

by writing to the ADCS<5:0> control bits in the ADCON3 register

- Configure the sampling time to be 2 TAD by writing: SAMC<4:0> = 00010

- Select at least two channels per analog input pin by writing to the ADCHS register

#### 18.7.2 750 ksps CONFIGURATION GUIDELINE

The following configuration items are required to achieve a 750 ksps conversion rate. This configuration assumes that a single analog input is to be sampled.

- Comply with conditions provided in Table 18-2

- Connect external VREF+ and VREF- pins following the recommended circuit shown in Figure 18-2

- Set SSRC<2:0> = 111 in the ADCON1 register to enable the auto-convert option

- Enable automatic sampling by setting the ASAM control bit in the ADCON1 register

- Enable one sample and hold channel by setting CHPS<1:0> = 00 in the ADCON2 register

- Write the SMPI<3:0> control bits in the ADCON2 register for the desired number of conversions between interrupts

- Configure the A/D clock period to be:

$$\frac{1}{(12+2) \times 750,000} = 95.24 \text{ ns}$$

by writing to the ADCS<5:0> control bits in the ADCON3 register

• Configure the sampling time to be 2 TAD by writing: SAMC<4:0> = 00010

#### 18.7.3 600 ksps CONFIGURATION GUIDELINE

The configuration for 600 ksps operation is dependent on whether a single input pin is to be sampled or whether multiple pins will be sampled.

#### 18.7.3.1 Single Analog Input

When performing conversions at 600 ksps for a single analog input, at least two sample and hold channels must be enabled. The analog input multiplexer must be configured so that the same input pin is connected to both sample and hold channels. The A/D converts the value held on one S/H channel, while the second S/H channel acquires a new input sample.

#### 18.7.3.2 Multiple Analog Input

The ADC can also be used to sample multiple analog inputs using multiple sample and hold channels. In this case, the total 600 ksps conversion rate is divided among the different input signals. For example, four inputs can be sampled at a rate of 150 ksps for each signal or two inputs can be sampled at a rate of 300 ksps for each signal. Sequential sampling must be used in this configuration to allow adequate sampling time on each input.

#### 19.2.7 FAIL-SAFE CLOCK MONITOR

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by appropriately programming the FCKSM Configuration bits (Clock Switch and Monitor Selection bits) in the Fosc device Configuration register. If the FSCM function is enabled, the LPRC Internal oscillator will run at all times (except during Sleep mode) and will not be subject to control by the SWDTEN bit.

In the event of an oscillator failure, the FSCM will generate a clock failure trap event and will switch the system clock over to the FRC oscillator. The user will then have the option to either attempt to restart the oscillator or execute a controlled shutdown. The user may decide to treat the trap as a warm Reset by simply loading the Reset address into the oscillator fail trap vector. In this event, the CF (Clock Fail) status bit (OSCCON<3>) is also set whenever a clock failure is recognized.

In the event of a clock failure, the WDT is unaffected and continues to run on the LPRC clock.

If the oscillator has a very slow start-up time coming out of POR, BOR or Sleep, it is possible that the PWRT timer will expire before the oscillator has started. In such cases, the FSCM will be activated and the FSCM will initiate a clock failure trap, and the COSC<1:0> bits are loaded with FRC oscillator selection. This will effectively shut-off the original oscillator that was trying to start.

The user may detect this situation and restart the oscillator in the clock fail trap ISR.

Upon a clock failure detection, the FSCM module will initiate a clock switch to the FRC Oscillator as follows:

- 1. The COSC bits (OSCCON<13:12>) are loaded with the FRC Oscillator selection value.

- 2. CF bit is set (OSCCON<3>).

- 3. OSWEN control bit (OSCCON<0>) is cleared.

For the purpose of clock switching, the clock sources are sectioned into four groups:

- Primary

- Secondary

- Internal FRC

- Internal LPRC

The user can switch between these functional groups, but cannot switch between options within a group. If the primary group is selected, then the choice within the group is always determined by the FPR<3:0> Configuration bits.

The OSCCON register holds the control and Status bits related to clock switching.

- COSC<1:0>: Read-only status bits always reflect the current oscillator group in effect.

- NOSC<1:0>: Control bits which are written to indicate the new oscillator group of choice.

- On POR and BOR, COSC<1:0> and NOSC<1:0> are both loaded with the Configuration bit values FOS<1:0>.

- LOCK: The LOCK status bit indicates a PLL lock.

- CF: Read-only status bit indicating if a clock fail detect has occurred.

- OSWEN: Control bit changes from a '0' to a '1' when a clock transition sequence is initiated. Clearing the OSWEN control bit will abort a clock transition in progress (used for hang-up situations).

If Configuration bits FCKSM<1:0> = 1x, then the clock switching and fail-safe clock monitor functions are disabled. This is the default Configuration bit setting.

If clock switching is disabled, then the FOS<1:0> and FPR<3:0> bits directly control the oscillator selection and the COSC<1:0> bits do not control the clock selection. However, these bits will reflect the clock source selection.

**Note:** The application should not attempt to switch to a clock of frequency lower than 100 kHz when the fail-safe clock monitor is enabled. If such clock switching is performed, the device may generate an oscillator fail trap and switch to the Fast RC oscillator.

#### 19.2.8 PROTECTION AGAINST ACCIDENTAL WRITES TO OSCCON

A write to the OSCCON register is intentionally made difficult because it controls clock switching and clock scaling.

To write to the OSCCON low byte, the following code sequence must be executed without any other instructions in between:

Byte Write 0x46 to OSCCON low Byte Write 0x57 to OSCCON low

Byte Write is allowed for one instruction cycle. Write the desired value or use bit manipulation instruction.

To write to the OSCCON high byte, the following instructions must be executed without any other instructions in between:

Byte Write 0x78 to OSCCON high Byte Write 0x9A to OSCCON high

*Byte Write is allowed for one instruction cycle.* Write the desired value or use bit manipulation instruction.

### 19.3.1.1 POR with Long Crystal Start-up Time (with FSCM Enabled)

The oscillator start-up circuitry is not linked to the POR circuitry. Some crystal circuits (especially low frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after the POR timer and the PWRT have expired:

- The oscillator circuit has not begun to oscillate.

- The oscillator start-up timer has NOT expired (if a crystal oscillator is used).

- The PLL has not achieved a LOCK (if PLL is used).

If the FSCM is enabled and one of the above conditions is true, then a clock failure trap will occur. The device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the trap ISR.

#### 19.3.1.2 Operating without FSCM and PWRT

If the FSCM is disabled and the Power-up Timer (PWRT) is also disabled, then the device will exit rapidly from Reset on power-up. If the clock source is FRC, LPRC, EXTRC, or EC, it will be active immediately.

If the FSCM is disabled and the system clock has not started, the device will be in a frozen state at the Reset vector until the system clock starts. From the user's perspective, the device will appear to be in Reset until a system clock is available.

#### 19.3.2 BOR: PROGRAMMABLE BROWN-OUT RESET

The BOR module is based on an internal voltage reference circuit. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (i.e., missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

The BOR module allows selection of one of the following voltage trip points:

- 2.6V-2.71V

- 4.1V-4.4V

- 4.58V-4.73V

**Note:** The BOR voltage trip points indicated here are nominal values provided for design guidance only.

A BOR will generate a Reset pulse which will reset the device. The BOR will select the clock source, based on the device Configuration bit values (FOS<1:0> and FPR<3:0>). Furthermore, if an Oscillator mode is selected, the BOR will activate the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, then the clock will be held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the POR time-out (TPOR) and the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100  $\mu$ s is applied. The total delay in this case is (TPOR + TFSCM).

The BOR status bit (RCON<1>) will be set to indicate that a BOR has occurred. The BOR circuit, if enabled, will continue to operate while in Sleep or Idle modes and will reset the device should VDD fall below the BOR threshold voltage.

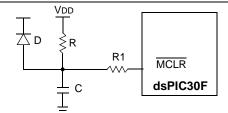

FIGURE 19-6:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2: R should be suitably chosen so as to make sure that the voltage drop across R does not violate the device's electrical specification.

- 3: R1 should be suitably chosen so as to limit any current flowing into MCLR from external capacitor C, in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

Note: Dedicated supervisory devices, such as the MCP1XX and MCP8XX, may also be used as an external Power-on Reset circuit. Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes and RETURN/RETFIE instructions, which are single-word instructions, but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction, require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double word moves require two cycles. The double word instructions execute in two instruction cycles.

| Note: | For more deta   |               |            |

|-------|-----------------|---------------|------------|

|       | refer to the "1 | 6-bit MCU and | I DSC Pro- |

|       | grammer's       | Reference     | Manual"    |

|       | (DS70157).      |               |            |

| Field           | Description                                                                      |  |  |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------|--|--|--|--|--|--|

| #text           | Means literal defined by "text"                                                  |  |  |  |  |  |  |

| (text)          | Means "content of text"                                                          |  |  |  |  |  |  |

| [text]          | Means "the location addressed by text"                                           |  |  |  |  |  |  |

| { }             | Optional field or operation                                                      |  |  |  |  |  |  |

| <n:m></n:m>     | Register bit field                                                               |  |  |  |  |  |  |

| .b              | Byte mode selection                                                              |  |  |  |  |  |  |

| .d              | Double word mode selection                                                       |  |  |  |  |  |  |

| .s              | Shadow register select                                                           |  |  |  |  |  |  |

| .w              | Word mode selection (default)                                                    |  |  |  |  |  |  |

| Acc             | One of two accumulators {A, B}                                                   |  |  |  |  |  |  |

| AWB             | Accumulator write-back destination address register $\in$ {W13, [W13] + = 2}     |  |  |  |  |  |  |

| bit4            | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$    |  |  |  |  |  |  |

| C, DC, N, OV, Z | MCU status bits: Carry, Digit Carry, Negative, Overflow, Zero                    |  |  |  |  |  |  |

| Expr            | Absolute address, label or expression (resolved by the linker)                   |  |  |  |  |  |  |

| f               | File register address ∈ {0x00000x1FFF}                                           |  |  |  |  |  |  |

| lit1            | 1-bit unsigned literal $\in \{0,1\}$                                             |  |  |  |  |  |  |

| lit4            | 4-bit unsigned literal ∈ {015}                                                   |  |  |  |  |  |  |

| lit5            | 5-bit unsigned literal ∈ {031}                                                   |  |  |  |  |  |  |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                  |  |  |  |  |  |  |

| lit10           | 10-bit unsigned literal $\in \{0255\}$ for Byte mode, $\{0:1023\}$ for Word mode |  |  |  |  |  |  |

| lit14           | 14-bit unsigned literal ∈ {016384}                                               |  |  |  |  |  |  |

| lit16           | 16-bit unsigned literal ∈ {065535}                                               |  |  |  |  |  |  |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSB must be 0                              |  |  |  |  |  |  |

| None            | Field does not require an entry, may be blank                                    |  |  |  |  |  |  |

| OA, OB, SA, SB  | DSP status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate      |  |  |  |  |  |  |

| PC              | Program Counter                                                                  |  |  |  |  |  |  |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                |  |  |  |  |  |  |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                            |  |  |  |  |  |  |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                   |  |  |  |  |  |  |

#### TABLE 20-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

#### 22.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC30F AC characteristics and timing parameters.

#### TABLE 22-12: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 2.5V to 5.5V             |  |  |  |  |  |

|--------------------|---------------------------------------------------------|--|--|--|--|--|

|                    | (unless otherwise stated)                               |  |  |  |  |  |

| AC CHARACTERISTICS | Operating temperature -40°C ≤TA ≤+85°C for Industrial   |  |  |  |  |  |

|                    | -40°C ≤TA ≤+125°C for Extended                          |  |  |  |  |  |

|                    | Operating voltage VDD range as described in Table 22-1. |  |  |  |  |  |

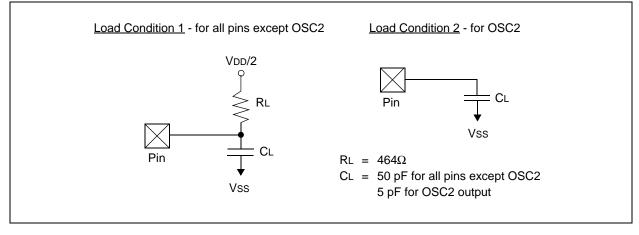

#### FIGURE 22-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

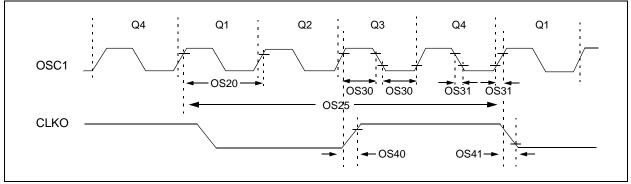

#### FIGURE 22-3: EXTERNAL CLOCK TIMING

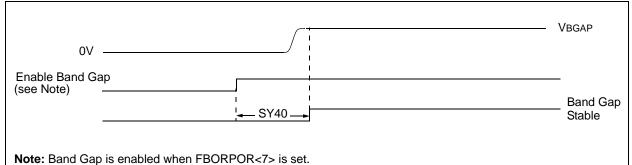

#### FIGURE 22-6: BAND GAP START-UP TIME CHARACTERISTICS

#### TABLE 22-21: BAND GAP START-UP TIME REQUIREMENTS

| AC CHARACTERISTICS |        |                               | (unles                                      | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |    |    |                                                                                                                                                                   |  |  |

|--------------------|--------|-------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min Typ <sup>(2)</sup> Max Units Conditions |                                                                                                                                                                                          |    |    |                                                                                                                                                                   |  |  |

| SY40               | TBGAP  | Band Gap Start-up Time        |                                             | 40                                                                                                                                                                                       | 65 | μs | Defined as the time between the<br>instant that the band gap is enabled<br>and the moment that the band gap<br>reference voltage is stable.<br>RCON<13>Status bit |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated.

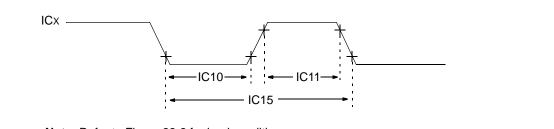

#### FIGURE 22-9: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

**Note:** Refer to Figure 22-2 for load conditions.

#### TABLE 22-26: INPUT CAPTURE TIMING REQUIREMENTS

| АС СНА                       | RACTERI | STICS               | (unless otherwis      | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |     |       |                                  |  |  |  |

|------------------------------|---------|---------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|----------------------------------|--|--|--|

| Param<br>No. Symbol Characte |         |                     | ristic <sup>(1)</sup> | Min                                                                                                                                                                                      | Мах | Units | Conditions                       |  |  |  |

| IC10                         | TccL    | ICx Input Low Time  | No Prescaler          | 0.5 TCY + 20                                                                                                                                                                             | _   | ns    | —                                |  |  |  |

|                              |         |                     | With Prescaler        | 10                                                                                                                                                                                       | _   | ns    |                                  |  |  |  |

| IC11                         | TccH    | ICx Input High Time | No Prescaler          | 0.5 TCY + 20                                                                                                                                                                             | _   | ns    | —                                |  |  |  |

|                              |         |                     | With Prescaler        | 10                                                                                                                                                                                       | _   | ns    |                                  |  |  |  |

| IC15                         | TccP    | ICx Input Period    |                       | (2 TCY + 40)/N                                                                                                                                                                           |     | ns    | N = prescale<br>value (1, 4, 16) |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

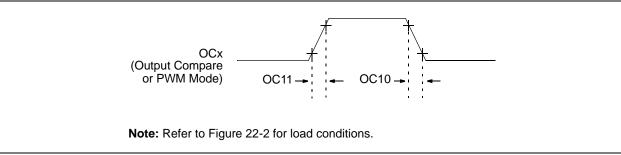

#### FIGURE 22-10: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 22-27: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHA       | ISTICS | (unless                       | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                                       |  |    |                    |  |  |  |

|--------------|--------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|----|--------------------|--|--|--|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup> | Min                                                                                                                                                                                      | Min Typ <sup>(2)</sup> Max Units Cond |  |    |                    |  |  |  |

| OC10         | TccF   | OCx Output Fall Time          | —                                                                                                                                                                                        | —                                     |  | ns | See parameter DO32 |  |  |  |

| OC11         | TccR   | OCx Output Rise Time          | — — — ns See parameter DO31                                                                                                                                                              |                                       |  |    |                    |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

### TABLE 22-36: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHARACTERISTICS |         |                                                      | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |                 |       |                        |  |

|--------------------|---------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|-------|------------------------|--|

| Param<br>No.       | Symbol  | Characteristic                                       |                                                                                                                                                                                          | Min <sup>(1)</sup> | Max             | Units | Conditions             |  |

| IM10               | TLO:SCL | Clock Low Time                                       | 100 kHz mode                                                                                                                                                                             | Tcy/2 (BRG + 1)    | _               | μs    | —                      |  |

|                    |         |                                                      | 400 kHz mode                                                                                                                                                                             | Tcy/2 (BRG + 1)    |                 | μs    | —                      |  |

|                    |         |                                                      | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                | Tcy/2 (BRG + 1)    | _               | μs    | —                      |  |

| IM11               | THI:SCL | Clock High Time                                      | 100 kHz mode                                                                                                                                                                             | Tcy/2 (BRG + 1)    |                 | μs    | —                      |  |

|                    |         |                                                      | 400 kHz mode                                                                                                                                                                             | Tcy/2 (BRG + 1)    |                 | μs    | —                      |  |

|                    |         |                                                      | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                | Tcy/2 (BRG + 1)    |                 | μs    | —                      |  |

| IM20               | TF:SCL  | SDA and SCL                                          | 100 kHz mode                                                                                                                                                                             | —                  | 300             | ns    | CB is specified to be  |  |

|                    |         | Fall Time                                            | 400 kHz mode                                                                                                                                                                             | 20 + 0.1 Св        | 300             | ns    | from 10 to 400 pF      |  |

|                    |         |                                                      | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                |                    | 100             | ns    |                        |  |

| IM21               | TR:SCL  | SDA and SCL                                          | 100 kHz mode                                                                                                                                                                             |                    | 1000            | ns    | CB is specified to be  |  |

|                    |         | Rise Time                                            | 400 kHz mode                                                                                                                                                                             | 20 + 0.1 Св        | 300             | ns    | from 10 to 400 pF      |  |

|                    |         |                                                      | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                |                    | 300             | ns    |                        |  |

| IM25               | TSU:DAT | Data Input<br>Setup Time                             | 100 kHz mode                                                                                                                                                                             | 250                |                 | ns    |                        |  |

|                    |         |                                                      | 400 kHz mode                                                                                                                                                                             | 100                | _               | ns    |                        |  |

|                    |         |                                                      | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                | _                  |                 | ns    | -                      |  |

| IM26               | Thd:dat | Data Input<br>Hold Time                              | 100 kHz mode                                                                                                                                                                             | 0                  |                 | ns    |                        |  |

|                    |         |                                                      | 400 kHz mode                                                                                                                                                                             | 0                  | 0.9             | μs    | —                      |  |

|                    |         |                                                      | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                |                    |                 | ns    |                        |  |

| IM30               | TSU:STA | SU:STA Start Condition<br>Setup Time                 | 100 kHz mode                                                                                                                                                                             | Tcy/2 (BRG + 1)    |                 | μs    | Only relevant for      |  |

|                    |         |                                                      | 400 kHz mode                                                                                                                                                                             | Tcy/2 (BRG + 1)    |                 | μs    | repeated Start         |  |

|                    |         |                                                      | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                | TCY/2 (BRG + 1)    | —               | μs    | condition              |  |

| IM31               | Thd:sta | D:STA Start Condition<br>Hold Time                   | 100 kHz mode                                                                                                                                                                             | Tcy/2 (BRG + 1)    |                 | μs    | After this period the  |  |

|                    |         |                                                      | 400 kHz mode                                                                                                                                                                             | Tcy/2 (BRG + 1)    |                 | μs    | first clock pulse is   |  |

|                    |         |                                                      | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                | Tcy/2 (BRG + 1)    |                 | μs    | generated              |  |

| IM33 1             | Tsu:sto | Tsu:sto                                              | Stop Condition                                                                                                                                                                           | 100 kHz mode       | Tcy/2 (BRG + 1) |       | μs                     |  |

|                    |         | Setup Time                                           | 400 kHz mode                                                                                                                                                                             | TCY/2 (BRG + 1)    | _               | μs    | · -                    |  |

|                    |         |                                                      | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                | Tcy/2 (BRG + 1)    |                 | μs    |                        |  |

| IM34               | THD:STO | Stop Condition                                       | 100 kHz mode                                                                                                                                                                             | Tcy/2 (BRG + 1)    |                 | ns    |                        |  |

|                    |         | Hold Time                                            | 400 kHz mode                                                                                                                                                                             | Tcy/2 (BRG + 1)    |                 | ns    | —                      |  |

|                    |         |                                                      | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                | Tcy/2 (BRG + 1)    |                 | ns    | -                      |  |

| IM40               | TAA:SCL | <ul> <li>Output Valid</li> <li>From Clock</li> </ul> | 100 kHz mode                                                                                                                                                                             | —                  | 3500            | ns    | —                      |  |

|                    |         |                                                      | 400 kHz mode                                                                                                                                                                             | _                  | 1000            | ns    | —                      |  |

|                    |         |                                                      | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                | _                  | —               | ns    | _                      |  |

| IM45               | Tbf:sda | F:SDA Bus Free Time                                  | 100 kHz mode                                                                                                                                                                             | 4.7                | _               | μs    | Time the bus must be   |  |

| -                  |         |                                                      | 400 kHz mode                                                                                                                                                                             | 1.3                | —               | μs    | free before a new      |  |

|                    |         |                                                      | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                | —                  | _               | μs    | transmission can start |  |

| IM50               | Св      | Bus Capacitive Lo                                    |                                                                                                                                                                                          | _                  | 400             | pF    |                        |  |

Note 1: BRG is the value of the I<sup>2</sup>C<sup>™</sup> Baud Rate Generator. Refer to Section 21. "Inter-Integrated Circuit<sup>™</sup> (I<sup>2</sup>C)" (DS70068) in the "*dsPIC30F Family Reference Manual*" (DS70046).

**2:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins (for 1 MHz mode only).

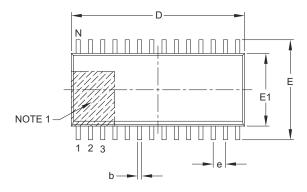

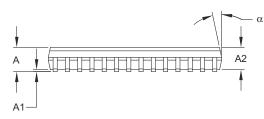

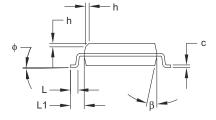

#### 28-Lead Plastic Small Outline (SO) – Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |     |      |

|--------------------------|------------------|-------------|-----|------|

|                          | Dimension Limits |             | NOM | MAX  |

| Number of Pins           | N                | 28          |     |      |

| Pitch                    | e                | 1.27 BSC    |     |      |

| Overall Height           | A                | -           | -   | 2.65 |

| Molded Package Thickness | A2               | 2.05        | -   | _    |

| Standoff §               | A1               | 0.10        | -   | 0.30 |

| Overall Width            | E                | 10.30 BSC   |     |      |

| Molded Package Width     | E1               | 7.50 BSC    |     |      |

| Overall Length           | D                | 17.90 BSC   |     |      |

| Chamfer (optional)       | h                | 0.25        | -   | 0.75 |

| Foot Length              | L                | 0.40        | -   | 1.27 |

| Footprint                | L1               | 1.40 REF    |     |      |

| Foot Angle Top           | φ                | 0°          | -   | 8°   |

| Lead Thickness           | С                | 0.18        | -   | 0.33 |

| Lead Width               | b                | 0.31        | -   | 0.51 |

| Mold Draft Angle Top     | α                | 5°          | -   | 15°  |

| Mold Draft Angle Bottom  | β                | 5° – 15°    |     |      |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-052B

| Enable Bits88                          |

|----------------------------------------|

| Fault States88                         |

| Modes                                  |

| Cycle-by-Cycle88                       |

| Latched88                              |

| PWM Operation During CPU Idle Mode89   |

| PWM Operation During CPU Sleep Mode 89 |

| PWM Output and Polarity Control 88     |

| Output Pin Control88                   |

| PWM Output Override87                  |

| Complementary Output Mode87            |

| Synchronization87                      |

| PWM Period                             |

| PWM Special Event Trigger 89           |

| Postscaler 89                          |

| PWM Time Base                          |

| Continuous Up/Down Counting Modes      |

| Double Update Mode 84                  |

| Free Running Mode 83                   |

| Postscaler84                           |

| Prescaler                              |

| Single-Shot Mode83                     |

| PWM Update Lockout                     |

#### Q

| QEA/QEB Input Characteristics             | 169 |

|-------------------------------------------|-----|

| QEI Module                                |     |

| External Clock Timing Requirements        | 165 |

| Index Pulse Timing Characteristics        | 170 |

| Index Pulse Timing Requirements           | 170 |

| Operation During CPU Idle Mode            | 78  |

| Operation During CPU Sleep Mode           | 77  |

| Register Map                              | 79  |

| Timer Operation During CPU Idle Mode      | 78  |

| Timer Operation During CPU Sleep Mode     | 77  |

| Quadrature Decoder Timing Requirements    | 169 |

| Quadrature Encoder Interface (QEI) Module | 75  |

| Quadrature Encoder Interface Interrupts   | 78  |

| Quadrature Encoder Interface Logic        | 76  |

#### R

| Reader Response                     |          |

|-------------------------------------|----------|

| Reset                               | 121, 127 |

| Reset Sequence                      |          |

| Reset Sources                       |          |

| Reset Timing Characteristics        | 161      |

| Reset Timing Requirements           | 161      |

| Resets                              |          |

| BOR, Programmable                   | 129      |

| POR                                 | 127      |

| Operating without FSCM and PWRT     | 129      |

| POR with Long Crystal Start-up Time | 129      |

| RTSP Operation                      | 44       |

|                                     |          |

### S

| Serial Peripheral | Interface. | See SPI |

|-------------------|------------|---------|

|-------------------|------------|---------|

| Simple Capture Event Mode              |    |

|----------------------------------------|----|

| Capture Buffer Operation               | 68 |

| Capture Prescaler                      | 68 |

| Hall Sensor Mode                       | 68 |

| Input Capture in CPU Idle Mode         | 69 |

| Timer2 and Timer3 Selection Mode       |    |

| Simple OC/PWM Mode Timing Requirements |    |

| Simple Output Compare Match Mode       | 72 |

| Simple Output Compare Match Mode       | 72 |

| Simple PWM Mode                       | 72    |

|---------------------------------------|-------|

| Input Pin Fault Protection            | 72    |

| Period                                |       |

| Single Pulse PWM Operation            | 87    |

| Software Simulator (MPLAB SIM)        | 145   |

| Software Stack Pointer, Frame Pointer | 12    |

| CALL Stack Frame                      | 27    |

| SPI                                   | 91    |

| SPI Mode                              |       |

| Slave Select Synchronization          | 93    |

| SPI1 Register Map                     | 94    |

| SPI Module                            |       |

| Framed SPI Support                    | 92    |

| Operating Function Description        |       |

| SDOx Disable                          | 91    |

| Timing Characteristics                |       |

| Master Mode (CKE = 0)                 |       |

| Master Mode (CKE = 1)                 |       |

| Slave Mode (CKE = 1) 173              | , 174 |