Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Betails                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 30 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                 |

| Number of I/O              | 20                                                                            |

| Program Memory Size        | 12KB (4K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 512 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 6x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f2010-30i-mm |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC30F2010

### High-Performance, 16-bit Digital Signal Controller

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

#### High-Performance Modified RISC CPU:

- Modified Harvard architecture

- C compiler optimized instruction set architecture

- 83 base instructions with flexible addressing modes

- 24-bit wide instructions, 16-bit wide data path

- 12 Kbytes on-chip Flash program space

- · 512 bytes on-chip data RAM

- 1 Kbyte nonvolatile data EEPROM

- 16 x 16-bit working register array

- Up to 30 MIPs operation:

- DC to 40 MHz external clock input

- 4 MHz-10 MHz oscillator input with PLL active (4x, 8x, 16x)

- 27 interrupt sources

- Three external interrupt sources

- · Eight user-selectable priority levels for each interrupt

- · Four processor exceptions and software traps

#### **DSP Engine Features:**

- · Modulo and Bit-Reversed modes

- Two 40-bit wide accumulators with optional saturation logic

- 17-bit x 17-bit single-cycle hardware fractional/ integer multiplier

- Single-cycle Multiply-Accumulate (MAC) operation

- 40-stage Barrel Shifter

- Dual data fetch

#### **Peripheral Features:**

- High current sink/source I/O pins: 25 mA/25 mA

- Three 16-bit timers/counters; optionally pair up 16-bit timers into 32-bit timer modules

- Four 16-bit capture input functions

- Two 16-bit compare/PWM output functions

Dual Compare mode available

- 3-wire SPI modules (supports 4 Frame modes)

- I<sup>2</sup>C<sup>™</sup> module supports Multi-Master/Slave mode

- and 7-bit/10-bit addressing

- Addressable UART modules with FIFO buffers

#### Motor Control PWM Module Features:

- Six PWM output channels

- Complementary or Independent Output modes

- Edge and Center-Aligned modes

- Four duty cycle generators

- · Dedicated time base with four modes

- · Programmable output polarity

- · Dead-time control for Complementary mode

- Manual output control

- Trigger for synchronized A/D conversions

### Quadrature Encoder Interface Module Features:

- · Phase A, Phase B and Index Pulse input

- 16-bit up/down position counter

- Count direction status

- Position Measurement (x2 and x4) mode

- · Programmable digital noise filters on inputs

- Alternate 16-bit Timer/Counter mode

- · Interrupt on position counter rollover/underflow

#### **Analog Features:**

- 10-bit Analog-to-Digital Converter (ADC) with:

- 1 Msps (for 10-bit A/D) conversion rate

- Six input channels

- Conversion available during Sleep and Idle

- Programmable Brown-out Reset

# Special Digital Signal Controller Features:

- Enhanced Flash program memory:

- 10,000 erase/write cycle (min.) for industrial temperature range, 100K (typical)

- Data EEPROM memory:

- 100,000 erase/write cycle (min.) for industrial temperature range, 1M (typical)

- Self-reprogrammable under software control

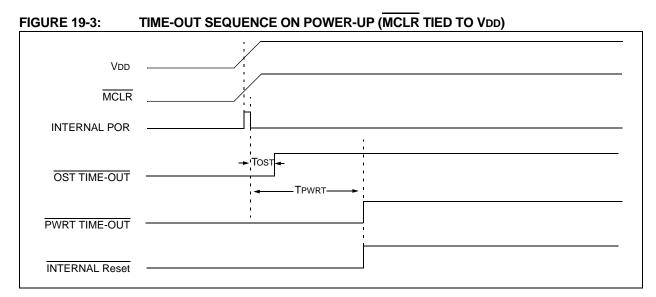

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Flexible Watchdog Timer (WDT) with on-chip low-power RC oscillator for reliable operation

- Fail-Safe Clock Monitor (FSCM) operation

- Detects clock failure and switches to on-chip Low-Power RC (LPRC) oscillator

- Programmable code protection

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- Selectable Power Management modes - Sleep, Idle and Alternate Clock modes

#### **CMOS Technology:**

- · Low-power, high-speed Flash technology

- Wide operating voltage range (2.5V to 5.5V)

- Industrial and Extended temperature ranges

- Low power consumption

#### dsPIC30F Motor Control and Power Conversion Family

| Device       | Pins | Program<br>Mem. Bytes/<br>Instructions | SRAM<br>Bytes | EEPROM<br>Bytes | Timer<br>16-bit | Input<br>Cap | Output<br>Comp/Std<br>PWM | Motor<br>Control<br>PWM | A/D 10-bit<br>1 Msps | QEI | UART | IdS | I <sup>2</sup> C <sup>TM</sup> |

|--------------|------|----------------------------------------|---------------|-----------------|-----------------|--------------|---------------------------|-------------------------|----------------------|-----|------|-----|--------------------------------|

| dsPIC30F2010 | 28   | 12K/4K                                 | 512           | 1024            | 3               | 4            | 2                         | 6 ch                    | 6 ch                 | Yes | 1    | 1   | 1                              |

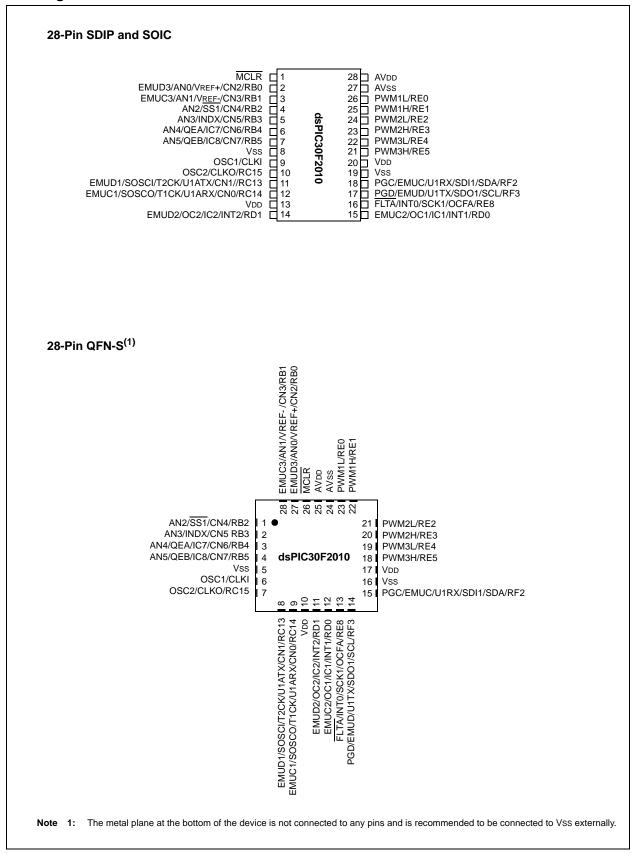

#### **Pin Diagrams**

Table 1-1 provides a brief description of device I/O pinouts and the functions that may be multiplexed to a port pin. Multiple functions may exist on one port pin. When multiplexing occurs, the peripheral module's functional requirements may force an override of the data direction of the port pin.

| Pin Name              | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                              |

|-----------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN5               | I           | Analog         | Analog input channels.                                                                                                                                                                   |

| AVdd                  | Р           | Р              | Positive supply for analog module. This pin must be connected at all times.                                                                                                              |

| AVss                  | Р           | Р              | Ground reference for analog module. This pin must be connected at all times                                                                                                              |

| CLKI                  |             | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                   |

| CLKO                  | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always<br>associated with OSC2 pin function. |

| CN0-CN7               | I           | ST             | Input change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                                |

| EMUD                  | I/O         | ST             | ICD Primary Communication Channel data input/output pin.                                                                                                                                 |

| EMUC                  | I/O         | ST             | ICD Primary Communication Channel clock input/output pin.                                                                                                                                |

| EMUD1                 | I/O         | ST             | ICD Secondary Communication Channel data input/output pin.                                                                                                                               |

| EMUC1                 | I/O         | ST             | ICD Secondary Communication Channel clock input/output pin.                                                                                                                              |

| EMUD2                 | I/O         | ST             | ICD Tertiary Communication Channel data input/output pin.                                                                                                                                |

| EMUC2                 | I/O         | ST             | ICD Tertiary Communication Channel clock input/output pin.                                                                                                                               |

| EMUD3                 | I/O         | ST             | ICD Quaternary Communication Channel data input/output pin.                                                                                                                              |

| EMUC3                 | I/O         | ST             | ICD Quaternary Communication Channel clock input/output pin.                                                                                                                             |

| IC1, IC2, IC7,<br>IC8 | 1           | ST             | Capture inputs. The dsPIC30F2010 has four capture inputs. The inputs are numbered for consistency with the inputs on larger device variants.                                             |

| INDX                  | 1           | ST             | Quadrature Encoder Index Pulse input.                                                                                                                                                    |

| QEA                   | i           | ST             | Quadrature Encoder Phase A input in QEI mode.                                                                                                                                            |

| QLA                   |             | 01             | Auxiliary Timer External Clock/Gate input in Timer mode.                                                                                                                                 |

| QEB                   | 1           | ST             | Quadrature Encoder Phase B input in QEI mode.                                                                                                                                            |

| QLD                   |             | 01             | Auxiliary Timer External Clock/Gate input in Timer mode.                                                                                                                                 |

| INT0                  | I           | ST             | External interrupt 0                                                                                                                                                                     |

| INT1                  | I           | ST             | External interrupt 1                                                                                                                                                                     |

| INT2                  | I           | ST             | External interrupt 2                                                                                                                                                                     |

| FLTA                  | 1           | ST             | PWM Fault A input                                                                                                                                                                        |

| PWM1L                 | Ó           | _              | PWM 1 Low output                                                                                                                                                                         |

| PWM1H                 | õ           |                | PWM 1 High output                                                                                                                                                                        |

| PWM2L                 | õ           |                | PWM 2 Low output                                                                                                                                                                         |

| PWM2H                 | ŏ           |                | PWM 2 High output                                                                                                                                                                        |

| PWM3L                 | õ           |                | PWM 3 Low output                                                                                                                                                                         |

| PWM3H                 | ŏ           | _              | PWM 3 High output                                                                                                                                                                        |

| MCLR                  | I/P         | ST             | Master Clear (Reset) input or programming voltage input. This pin is an active-low Reset to the device.                                                                                  |

| OCFA                  |             | ST             | Compare Fault A input (for Compare channels 1, 2, 3 and 4).                                                                                                                              |

| 0C1-0C2               | Ö           | _              | Compare outputs.                                                                                                                                                                         |

| OSC1                  | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                          |

| OSC2                  | I/O         | —              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                 |

| Legend: CMC           | DS = CN     | IOS compati    | ble input or output Analog = Analog input                                                                                                                                                |

| ST                    |             |                | input with CMOS levels O = Output                                                                                                                                                        |

| 1                     | = Inp       |                | P = Power                                                                                                                                                                                |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS

The SA and SB bits are modified each time data passes through the adder/subtracter, but can only be cleared by the user. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation, or bit 39 for 40-bit saturation) and will be saturated (if saturation is enabled). When saturation is not enabled, SA and SB default to bit 39 overflow and thus indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits will generate an arithmetic warning trap when saturation is disabled.

The overflow and saturation status bits can optionally be viewed in the Status Register (SR) as the logical OR of OA and OB (in bit OAB), and the logical OR of SA and SB (in bit SAB). This allows programmers to check one bit in the STATUS register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated. This would be useful for complex number arithmetic which typically uses both the accumulators.

The device supports three Saturation and Overflow modes.

- 1. Bit 39 Overflow and Saturation:

- When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFF) or maximally negative 9.31 value (0x800000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. This is referred to as 'super saturation' and provides protection against erroneous data or unexpected algorithm problems (e.g., gain calculations).

- Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFF) or maximally negative 1.31 value (0x0080000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. When this Saturation mode is in effect, the guard bits are not used (so the OA, OB or OAB bits are never set).

- 3. Bit 39 Catastrophic Overflow The bit 39 overflow status bit from the adder is used to set the SA or SB bit, which remain set until cleared by the user. No saturation operation is performed and the accumulator is allowed to overflow (destroying its sign). If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

#### 2.4.2.2 Accumulator 'Write-Back'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

- 1. W13, Register Direct: The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

- [W13]+=2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

#### 2.4.2.3 Round Logic

The round logic is a combinational block, which performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value which is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word (lsw) is simply discarded.

Conventional rounding takes bit 15 of the accumulator, zero-extends it and adds it to the ACCxH word (bits 16 through 31 of the accumulator). If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented. If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged. A consequence of this algorithm is that over a succession of random rounding operations, the value will tend to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. If this is the case, the Least Significant bit (bit 16 of the accumulator) of ACCxH is examined. If it is '1', ACCxH is incremented. If it is '0', ACCxH is not modified. Assuming that bit 16 is effectively random in nature, this scheme will remove any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC) or rounded (SAC.R) version of the contents of the target accumulator to data memory, via the X bus (subject to data saturation, see **Section 2.4.2.4 "Data Space Write Saturation"**). Note that for the MAC class of instructions, the accumulator write-back operation will function in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

#### 4.2.3 MODULO ADDRESSING APPLICABILITY

Modulo addressing can be applied to the effective address calculation associated with any W register. It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes may, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected effective address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the effective address. When an address offset (e.g., [W7 + W2]) is used, modulo address correction is performed, but the contents of the register remains unchanged.

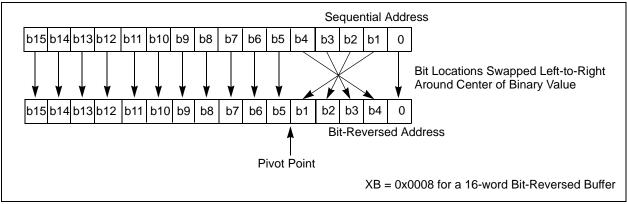

#### 4.3 Bit-Reversed Addressing

Bit-Reversed Addressing is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which may be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

### 4.3.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing is enabled when:

- 1. BWM (W register selection) in the MODCON register is any value other than 15 (the stack can not be accessed using Bit-Reversed Addressing) **and**

- 2. the BREN bit is set in the XBREV register **and**

- 3. the Addressing mode used is Register Indirect with Pre-Increment or Post-Increment.

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, then the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the bit-reversed address modifier or 'pivot point' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All Bit-Reversed EA calculations assume   |  |  |  |

|-------|-------------------------------------------|--|--|--|

|       | word-sized data (LSb of every EA is       |  |  |  |

|       | always clear). The XB value is scaled     |  |  |  |

|       | accordingly to generate compatible (byte) |  |  |  |

|       | addresses.                                |  |  |  |

When enabled, Bit-Reversed Addressing will only be executed for register indirect with pre-increment or post-increment addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data, and normal addresses will be generated instead. When Bit-Reversed Addressing is active, the W Address Pointer will always be added to the address modifier (XB) and the offset associated with the register Indirect Addressing mode will be ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo addressing and Bit-Reversed Addressing should not be enabled together. In the event that the user attempts to do this, bit reversed addressing will assume priority when active for the X WAGU, and X WAGU Modulo Addressing will be disabled. However, Modulo Addressing will continue to function in the X RAGU.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, then a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the bit-reversed pointer.

#### FIGURE 4-2: BIT-REVERSED ADDRESS EXAMPLE

#### 7.0 DATA EEPROM MEMORY

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

The Data EEPROM Memory is readable and writable during normal operation over the entire VDD range. The data EEPROM memory is directly mapped in the program memory address space.

The four SFRs used to read and write the program Flash memory are used to access data EEPROM memory as well. As described in **Section 6.0 "Flash Program Memory"**, these registers are:

- NVMCON

- NVMADR

- NVMADRU

- NVMKEY

The EEPROM data memory allows read and write of single words and 16-word blocks. When interfacing to data memory, NVMADR, in conjunction with the NVMADRU register, is used to address the EEPROM location being accessed. TBLRDL and TBLWTL instructions are used to read and write data EEPROM. The dsPIC30F devices have up to 1 Kbyte of data EEPROM, with an address range from 0x7FFC00 to 0x7FFFFE.

A word write operation should be preceded by an erase of the corresponding memory location(s). The write typically requires 2 ms to complete, but the write time will vary with voltage and temperature. A program or erase operation on the data EEPROM does not stop the instruction flow. The user is responsible for waiting for the appropriate duration of time before initiating another data EEPROM write/erase operation. Attempting to read the data EEPROM while a programming or erase operation is in progress results in unspecified data.

Control bit WR initiates write operations, similar to program Flash writes. This bit cannot be cleared, only set, in software. This bit is cleared in hardware at the completion of the write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a  $\overline{\text{MCLR}}$  Reset, or a WDT Time-out Reset, during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The address register NVMADR remains unchanged.

Note: Interrupt flag bit NVMIF in the IFS0 register is set when write is complete. It must be cleared in software.

#### 7.1 Reading the Data EEPROM

A TBLRD instruction reads a word at the current program word address. This example uses W0 as a pointer to data EEPROM. The result is placed in register W4, as shown in Example 7-1.

#### EXAMPLE 7-1: DATA EEPROM READ

| MOV    | #LOW_ADDR_WORD,W0  | ; Init Pointer     |

|--------|--------------------|--------------------|

| MOV    | #HIGH_ADDR_WORD,W1 |                    |

| MOV    | W1 TBLPAG          |                    |

| TBLRDL | [ WO ], W4         | ; read data EEPROM |

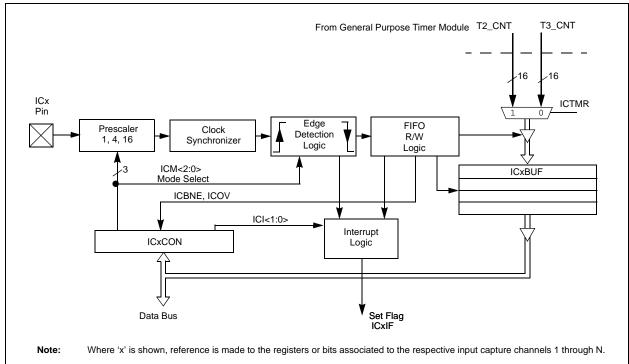

#### 11.0 INPUT CAPTURE MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the Input Capture module and associated operational modes. The features provided by this module are useful in applications requiring Frequency (Period) and Pulse measurement. Figure 11-1 depicts a block diagram of the Input Capture module. Input capture is useful for such modes as:

- Frequency/Period/Pulse Measurements

- Additional sources of External Interrupts

The key operational features of the Input Capture module are:

- Simple Capture Event mode

- Timer2 and Timer3 mode selection

- Interrupt on input capture event

These operating modes are determined by setting the appropriate bits in the ICxCON register (where x = 1,2,...,N). The dsPIC DSC devices contain up to eight capture channels, (i.e., the maximum value of N is 8).

Note: The dsPIC30F2010 device has four capture inputs – IC1, IC2, IC7 and IC8. The naming of these four capture channels is intentional and preserves software compatibility with other dsPIC DSC devices.

#### FIGURE 11-1: INPUT CAPTURE MODE BLOCK DIAGRAM

#### 13.7 QEI Module Operation During CPU Idle Mode

Since the QEI module can function as a quadrature encoder interface, or as a 16-bit timer, the following section describes operation of the module in both modes.

#### 13.7.1 QEI OPERATION DURING CPU IDLE MODE

When the CPU is placed in the Idle mode, the QEI module will operate if the QEISIDL bit (QEICON<13>) = 0. This bit defaults to a logic '0' upon executing POR and BOR. For halting the QEI module during the CPU Idle mode, QEISIDL should be set to '1'.

#### 13.7.2 TIMER OPERATION DURING CPU IDLE MODE

When the CPU is placed in the Idle mode and the QEI module is configured in the 16-bit Timer mode, the 16-bit timer will operate if the QEISIDL bit (QEI-CON<13>) = 0. This bit defaults to a logic '0' upon executing POR and BOR. For halting the timer module during the CPU Idle mode, QEISIDL should be set to '1'.

If the QEISIDL bit is cleared, the timer will function normally, as if the CPU Idle mode had not been entered.

#### 13.8 Quadrature Encoder Interface Interrupts

The quadrature encoder interface has the ability to generate an interrupt on occurrence of the following events:

- Interrupt on 16-bit up/down position counter rollover/underflow

- Detection of qualified index pulse, or if CNTERR bit is set

- Timer period match event (overflow/underflow)

- · Gate accumulation event

The QEI interrupt flag bit, QEIIF, is asserted upon occurrence of any of the above events. The QEIIF bit must be cleared in software. QEIIF is located in the IFS2 status register.

Enabling an interrupt is accomplished via the respective enable bit, QEIIE. The QEIIE bit is located in the IEC2 Control register.

#### 16.12.4 CLOCK ARBITRATION

Clock arbitration occurs when the master de-asserts the SCL pin (SCL allowed to float high) during any receive, transmit or Restart/Stop condition. When the SCL pin is allowed to float high, the Baud Rate Generator is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of I2CBRG and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device.

#### 16.12.5 MULTI-MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master operation support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high while another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the MI2CIF pulse and reset the master portion of the I<sup>2</sup>C port to its Idle state.

If a transmit was in progress when the bus collision occurred, the transmission is halted, the TBF flag is cleared, the SDA and SCL lines are de-asserted, and a value can now be written to I2CTRN. When the user services the  $I^2C$  master event Interrupt Service Routine, if the  $I^2C$  bus is free (i.e., the P bit is set) the user can resume communication by asserting a Start condition.

If a Start, Restart, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the I2CCON register are cleared to '0'. When the user services the bus collision Interrupt Service Routine, and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The Master will continue to monitor the SDA and SCL pins, and if a Stop condition occurs, the MI2CIF bit will be set.

A write to the I2CTRN will start the transmission of data at the first data bit, regardless of where the transmitter left off when bus collision occurred.

In a Multi-Master environment, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$ bus can be taken when the P bit is set in the I2CSTAT register, or the bus is Idle and the S and P bits are cleared.

#### 16.13 I<sup>2</sup>C Module Operation During CPU Sleep and Idle Modes

#### 16.13.1 I<sup>2</sup>C OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shutdown and stay at logic '0'. If Sleep occurs in the middle of a transmission, and the state machine is partially into a transmission as the clocks stop, then the transmission is aborted. Similarly, if Sleep occurs in the middle of a reception, then the reception is aborted.

### 16.13.2 I<sup>2</sup>C OPERATION DURING CPU IDLE MODE

For the  $I^2C$ , the I2CSIDL bit selects if the module will stop on Idle or continue on Idle. If I2CSIDL = 0, the module will continue operation on assertion of the Idle mode. If I2CSIDL = 1, the module will stop on Idle.

#### 19.2.7 FAIL-SAFE CLOCK MONITOR

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by appropriately programming the FCKSM Configuration bits (Clock Switch and Monitor Selection bits) in the Fosc device Configuration register. If the FSCM function is enabled, the LPRC Internal oscillator will run at all times (except during Sleep mode) and will not be subject to control by the SWDTEN bit.

In the event of an oscillator failure, the FSCM will generate a clock failure trap event and will switch the system clock over to the FRC oscillator. The user will then have the option to either attempt to restart the oscillator or execute a controlled shutdown. The user may decide to treat the trap as a warm Reset by simply loading the Reset address into the oscillator fail trap vector. In this event, the CF (Clock Fail) status bit (OSCCON<3>) is also set whenever a clock failure is recognized.

In the event of a clock failure, the WDT is unaffected and continues to run on the LPRC clock.

If the oscillator has a very slow start-up time coming out of POR, BOR or Sleep, it is possible that the PWRT timer will expire before the oscillator has started. In such cases, the FSCM will be activated and the FSCM will initiate a clock failure trap, and the COSC<1:0> bits are loaded with FRC oscillator selection. This will effectively shut-off the original oscillator that was trying to start.

The user may detect this situation and restart the oscillator in the clock fail trap ISR.

Upon a clock failure detection, the FSCM module will initiate a clock switch to the FRC Oscillator as follows:

- 1. The COSC bits (OSCCON<13:12>) are loaded with the FRC Oscillator selection value.

- 2. CF bit is set (OSCCON<3>).

- 3. OSWEN control bit (OSCCON<0>) is cleared.

For the purpose of clock switching, the clock sources are sectioned into four groups:

- Primary

- Secondary

- Internal FRC

- Internal LPRC

The user can switch between these functional groups, but cannot switch between options within a group. If the primary group is selected, then the choice within the group is always determined by the FPR<3:0> Configuration bits.

The OSCCON register holds the control and Status bits related to clock switching.

- COSC<1:0>: Read-only status bits always reflect the current oscillator group in effect.

- NOSC<1:0>: Control bits which are written to indicate the new oscillator group of choice.

- On POR and BOR, COSC<1:0> and NOSC<1:0> are both loaded with the Configuration bit values FOS<1:0>.

- LOCK: The LOCK status bit indicates a PLL lock.

- CF: Read-only status bit indicating if a clock fail detect has occurred.

- OSWEN: Control bit changes from a '0' to a '1' when a clock transition sequence is initiated. Clearing the OSWEN control bit will abort a clock transition in progress (used for hang-up situations).

If Configuration bits FCKSM<1:0> = 1x, then the clock switching and fail-safe clock monitor functions are disabled. This is the default Configuration bit setting.

If clock switching is disabled, then the FOS<1:0> and FPR<3:0> bits directly control the oscillator selection and the COSC<1:0> bits do not control the clock selection. However, these bits will reflect the clock source selection.

**Note:** The application should not attempt to switch to a clock of frequency lower than 100 kHz when the fail-safe clock monitor is enabled. If such clock switching is performed, the device may generate an oscillator fail trap and switch to the Fast RC oscillator.

#### 19.2.8 PROTECTION AGAINST ACCIDENTAL WRITES TO OSCCON

A write to the OSCCON register is intentionally made difficult because it controls clock switching and clock scaling.

To write to the OSCCON low byte, the following code sequence must be executed without any other instructions in between:

Byte Write 0x46 to OSCCON low Byte Write 0x57 to OSCCON low

Byte Write is allowed for one instruction cycle. Write the desired value or use bit manipulation instruction.

To write to the OSCCON high byte, the following instructions must be executed without any other instructions in between:

Byte Write 0x78 to OSCCON high Byte Write 0x9A to OSCCON high

*Byte Write is allowed for one instruction cycle.* Write the desired value or use bit manipulation instruction.

# dsPIC30F2010

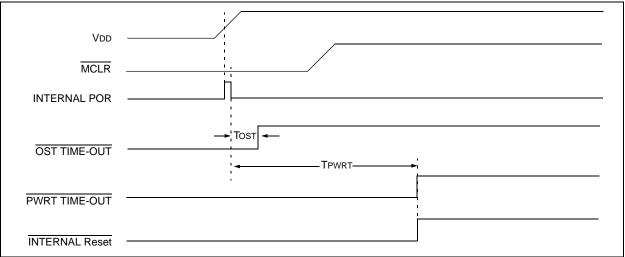

#### FIGURE 19-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

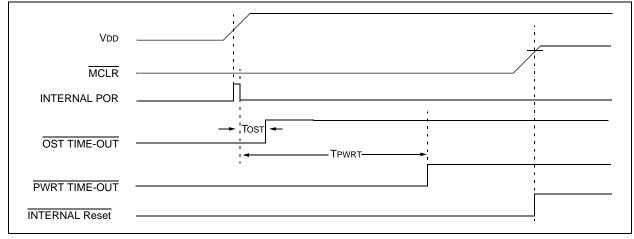

#### FIGURE 19-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

### dsPIC30F2010

NOTES:

#### 21.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 21.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

#### 21.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### dsPIC30F2010

#### TABLE 22-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACTERISTICS |                            |     | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated) |                                             |      |                                                 |  |  |

|--------------------|----------------------------|-----|-----------------------------------------------------------------------|---------------------------------------------|------|-------------------------------------------------|--|--|

|                    |                            |     | Operating to                                                          | ≆85°C for Industrial<br>≆125°C for Extended |      |                                                 |  |  |

| Parameter<br>No.   | Typical                    | Max | Units                                                                 |                                             |      | Conditions                                      |  |  |

| Power Down         | Current (IPD) <sup>(</sup> | 1)  |                                                                       |                                             |      |                                                 |  |  |

| DC60a              | 0.05                       | _   | μA                                                                    | 25°C                                        |      |                                                 |  |  |

| DC60b              | 3                          | 25  | μA                                                                    | 85°C                                        | 3.3V |                                                 |  |  |

| DC60c              | 20                         | 50  | μΑ                                                                    | 125°C                                       |      | Base Power Down Current <sup>(2)</sup>          |  |  |

| DC60e              | 0.1                        | _   | μΑ                                                                    | 25°C                                        |      | Base Power Down Current                         |  |  |

| DC60f              | 6                          | 35  | μΑ                                                                    | 85°C                                        | 5V   |                                                 |  |  |

| DC60g              | 40                         | 200 | μΑ                                                                    | 125°C                                       |      |                                                 |  |  |

| DC61a              | 30                         | 45  | μΑ                                                                    | 25°C                                        |      |                                                 |  |  |

| DC61b              | 34                         | 51  | μΑ                                                                    | 85°C                                        | 3.3V |                                                 |  |  |

| DC61c              | 46                         | 69  | μΑ                                                                    | 125°C                                       |      | Watchdog Timer Current: ∆IwDT <sup>(2)</sup>    |  |  |

| DC61e              | 35                         | 53  | μΑ                                                                    | 25°C                                        |      |                                                 |  |  |

| DC61f              | 39                         | 59  | μA                                                                    | 85°C                                        | 5V   |                                                 |  |  |

| DC61g              | 40                         | 60  | μΑ                                                                    | 125°C                                       |      |                                                 |  |  |

| DC62a              | 4                          | 10  | μΑ                                                                    | 25°C                                        |      |                                                 |  |  |

| DC62b              | 5                          | 10  | μA                                                                    | 85°C                                        | 3.3V |                                                 |  |  |

| DC62c              | 4                          | 10  | μA                                                                    | 125°C                                       |      | Timer 1 w/32 kHz Crystal: ∆ITi32 <sup>(2)</sup> |  |  |

| DC62e              | 4                          | 15  | μΑ                                                                    | 25°C                                        |      |                                                 |  |  |

| DC62f              | 6                          | 15  | μA                                                                    | 85°C                                        | 5V   |                                                 |  |  |

| DC62g              | 5                          | 15  | μA                                                                    | 125°C                                       |      |                                                 |  |  |

| DC63a              | 4                          | 6   | μΑ                                                                    | 25°C                                        |      |                                                 |  |  |

| DC63b              | 4                          | 6   | μΑ                                                                    | 85°C                                        | 3.3V |                                                 |  |  |

| DC63c              | 5                          | 7.5 | μA                                                                    | 125°C                                       | ]    | – BOR On: ∆IBOR <sup>(2)</sup>                  |  |  |

| DC63e              | 10                         | 15  | μΑ                                                                    | 25°C                                        |      |                                                 |  |  |

| DC63f              | 9                          | 15  | μΑ                                                                    | 85°C                                        | 5V   |                                                 |  |  |

| DC63g              | 10                         | 15  | μA                                                                    | 125°C                                       |      |                                                 |  |  |

**Note 1:** Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled high. LVD, BOR, WDT, etc. are all switched off.

2: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

#### TABLE 22-23: TIMER2 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |                              |                                           |                                                                | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                                         |     |         |       |                                  |

|--------------------|------------------------------|-------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|---------|-------|----------------------------------|

| Param<br>No.       | Symbol                       | Characte                                  | Characteristic                                                 |                                                                                                                                                                                          | Min                                     | Тур | Max     | Units | Conditions                       |

| TB10               | TtxH                         | TxCK High Time                            | Synchronous,<br>no prescaler<br>Synchronous,<br>with prescaler |                                                                                                                                                                                          | 0.5 Tcy + 20                            |     | _       | ns    | Must also meet<br>parameter TB15 |

|                    |                              |                                           |                                                                |                                                                                                                                                                                          | 10                                      |     | _       | ns    |                                  |

| TB11               | TtxL                         | TxCK Low Time                             | Synchronous,<br>no prescaler                                   |                                                                                                                                                                                          | 0.5 TCY + 20                            |     | _       | ns    | Must also meet<br>parameter TB15 |

|                    | Synchronous<br>with prescale |                                           |                                                                | 10                                                                                                                                                                                       |                                         | —   | ns      |       |                                  |

| TB15               | TtxP                         | TxCK Input Period                         | Synchro<br>no presc                                            |                                                                                                                                                                                          | Tcy + 10                                |     | —       | ns    | N = prescale<br>value            |

|                    |                              |                                           | Synchronous, with prescaler                                    |                                                                                                                                                                                          | Greater of:<br>20 ns or<br>(TCY + 40)/N |     |         |       | (1, 8, 64, 256)                  |

| TB20               | TCKEXTMRL                    | Delay from Externa<br>Edge to Timer Incre |                                                                | lock                                                                                                                                                                                     | 0.5 TCY                                 | _   | 1.5 TCY | —     | —                                |

#### TABLE 22-24: TIMER3 EXTERNAL CLOCK TIMING REQUIREMENTS

#### AC CHARACTERISTICS

Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature-40°C ≤TA ≤+85°C for Industrial

|              |           |                                           |                              | allig temperatur                        |         | C ≤TA ≤+1 | 25°C fc    | or Extended                   |

|--------------|-----------|-------------------------------------------|------------------------------|-----------------------------------------|---------|-----------|------------|-------------------------------|

| Param<br>No. | Symbol    | Charact                                   | Min                          | Тур                                     | Max     | Units     | Conditions |                               |

| TC10         | TtxH      | TxCK High Time                            | Synchronous                  | 0.5 Tcy + 20                            |         |           | ns         | Must also meet parameter TC15 |

| TC11         | TtxL      | TxCK Low Time                             | Synchronous                  | 0.5 Tcy + 20                            | —       | —         | ns         | Must also meet parameter TC15 |

| TC15         | TtxP      | TxCK Input Period                         | Synchronous,<br>no prescaler | Tcy + 10                                | —       | —         | ns         | N = prescale<br>value         |

|              |           |                                           | Synchronous, with prescaler  | Greater of:<br>20 ns or<br>(Tcy + 40)/N |         |           |            | (1, 8, 64, 256)               |

| TC20         | TCKEXTMRL | Delay from Externa<br>Edge to Timer Incre | 0.5 TCY                      | _                                       | 1.5 TCY | _         | —          |                               |

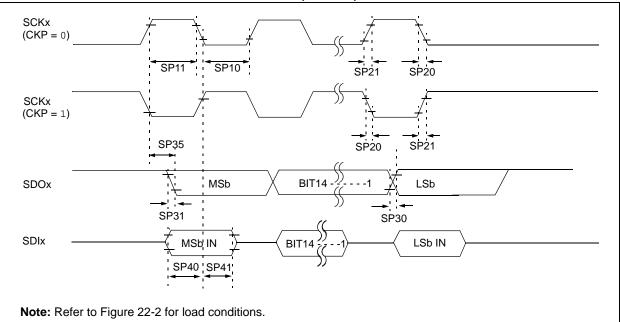

| АС СНА       | RACTERIST             | TICS                                       | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |     |       |                       |

|--------------|-----------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-----------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>              | Min                                                                                                                                                                                      | Тур <sup>(2)</sup> | Max | Units | Conditions            |

| SP10         | TscL                  | SCKx Output Low Time <sup>(3)</sup>        | Tcy/2                                                                                                                                                                                    | _                  | _   | ns    | See Note 3            |

| SP11         | TscH                  | SCKx Output High Time <sup>(3)</sup>       | Tcy/2                                                                                                                                                                                    | —                  |     | ns    | See Note 3            |

| SP20         | TscF                  | SCKx Output Fall Time <sup>(4</sup>        | —                                                                                                                                                                                        | —                  |     | ns    | See parameter<br>DO32 |

| SP21         | TscR                  | SCKx Output Rise Time <sup>(4)</sup>       | —                                                                                                                                                                                        | —                  | —   | ns    | See parameter<br>DO31 |

| SP30         | TdoF                  | SDOx Data Output Fall Time <sup>(4)</sup>  | —                                                                                                                                                                                        | —                  | _   | ns    | See parameter<br>DO32 |

| SP31         | TdoR                  | SDOx Data Output Rise Time <sup>(4)</sup>  | —                                                                                                                                                                                        | —                  |     | ns    | See parameter<br>DO31 |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge  | —                                                                                                                                                                                        | —                  | 30  | ns    | _                     |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge | 20                                                                                                                                                                                       | —                  | —   | ns    | -                     |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge  | 20                                                                                                                                                                                       | —                  |     | ns    | -                     |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCK is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI pins.

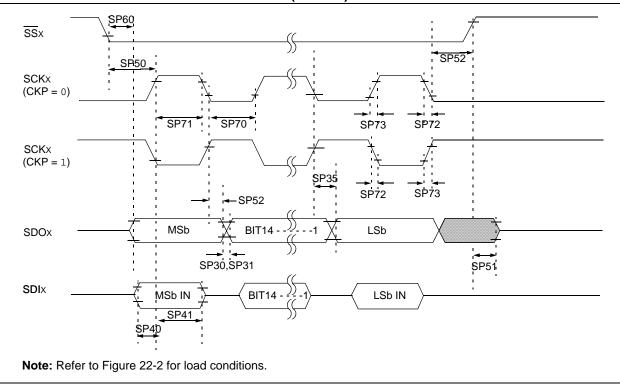

#### FIGURE 22-19: SPI MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

### TABLE 22-36: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA       |                       | ISTICS            |                           | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Indus         -40°C ≤TA ≤+125°C for External |       |            |                        |  |  |

|--------------|-----------------------|-------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|------------------------|--|--|

| Param<br>No. | Symbol Characteristic |                   | Min <sup>(1)</sup>        | Max                                                                                                                                                                                 | Units | Conditions |                        |  |  |

| IM10         | TLO:SCL               | Clock Low Time    | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                     | _     | μs         | _                      |  |  |

|              |                       |                   | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                     |       | μs         | _                      |  |  |

|              |                       |                   | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                     | _     | μs         | _                      |  |  |

| IM11         | THI:SCL               | Clock High Time   | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                     |       | μs         | _                      |  |  |

|              |                       |                   | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                     |       | μs         | _                      |  |  |

|              |                       |                   | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                     |       | μs         | _                      |  |  |

| IM20         | TF:SCL                | SDA and SCL       | 100 kHz mode              | —                                                                                                                                                                                   | 300   | ns         | CB is specified to be  |  |  |

|              |                       | Fall Time         | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                         | 300   | ns         | from 10 to 400 pF      |  |  |

|              |                       |                   | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                                                     | 100   | ns         |                        |  |  |

| IM21         | TR:SCL                | SDA and SCL       | 100 kHz mode              |                                                                                                                                                                                     | 1000  | ns         | CB is specified to be  |  |  |

|              |                       | Rise Time         | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                         | 300   | ns         | from 10 to 400 pF      |  |  |

|              |                       |                   | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                                                     | 300   | ns         |                        |  |  |

| IM25         | TSU:DAT               | Data Input        | 100 kHz mode              | 250                                                                                                                                                                                 |       | ns         |                        |  |  |

|              |                       | Setup Time        | 400 kHz mode              | 100                                                                                                                                                                                 | _     | ns         | -                      |  |  |

|              |                       |                   | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                                   |       | ns         |                        |  |  |

| IM26         | THD:DAT               | Data Input        | 100 kHz mode              | 0                                                                                                                                                                                   |       | ns         |                        |  |  |

|              |                       | Hold Time         | 400 kHz mode              | 0                                                                                                                                                                                   | 0.9   | μs         | -                      |  |  |

|              |                       |                   | 1 MHz mode <sup>(2)</sup> |                                                                                                                                                                                     |       | ns         |                        |  |  |

| IM30         | TSU:STA               | Start Condition   | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                     |       | μs         | Only relevant for      |  |  |

|              |                       | Setup Time        | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                     |       | μs         | repeated Start         |  |  |

|              |                       |                   | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 1)                                                                                                                                                                     | —     | μs         | condition              |  |  |

| IM31         | THD:STA               | Start Condition   | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                     |       | μs         | After this period the  |  |  |

|              |                       | Hold Time         | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                     |       | μs         | first clock pulse is   |  |  |

|              |                       |                   | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                     |       | μs         | generated              |  |  |

| IM33         | TSU:STO               | Stop Condition    | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                     |       | μs         |                        |  |  |

|              |                       | Setup Time        | 400 kHz mode              | TCY/2 (BRG + 1)                                                                                                                                                                     | _     | μs         |                        |  |  |

|              |                       |                   | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                     |       | μs         |                        |  |  |

| IM34         | THD:STO               | Stop Condition    | 100 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                     |       | ns         |                        |  |  |

|              |                       | Hold Time         | 400 kHz mode              | Tcy/2 (BRG + 1)                                                                                                                                                                     |       | ns         | -                      |  |  |

|              |                       |                   | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 1)                                                                                                                                                                     |       | ns         |                        |  |  |

| IM40         | TAA:SCL               | Output Valid      | 100 kHz mode              | —                                                                                                                                                                                   | 3500  | ns         | _                      |  |  |

|              |                       | From Clock        | 400 kHz mode              | _                                                                                                                                                                                   | 1000  | ns         | _                      |  |  |

|              |                       |                   | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                                   | —     | ns         | _                      |  |  |

| IM45         | TBF:SDA               | Bus Free Time     | 100 kHz mode              | 4.7                                                                                                                                                                                 | _     | μs         | Time the bus must be   |  |  |

|              |                       |                   | 400 kHz mode              | 1.3                                                                                                                                                                                 | —     | μs         | free before a new      |  |  |

|              |                       |                   | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                   | _     | μs         | transmission can start |  |  |

| IM50         | Св                    | Bus Capacitive Lo |                           | _                                                                                                                                                                                   | 400   | pF         | _                      |  |  |

Note 1: BRG is the value of the I<sup>2</sup>C<sup>™</sup> Baud Rate Generator. Refer to Section 21. "Inter-Integrated Circuit<sup>™</sup> (I<sup>2</sup>C)" (DS70068) in the "*dsPIC30F Family Reference Manual*" (DS70046).

**2:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins (for 1 MHz mode only).

#### READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: |                                                     | Total Pages Sent                          |

|------------|-----------------------------------------------------|-------------------------------------------|

|            | m: Name                                             |                                           |

| 110        |                                                     |                                           |

|            | Company                                             |                                           |

|            | City / State / ZIP / Country                        |                                           |

|            | Telephone: ()                                       |                                           |

| Арр        | lication (optional):                                |                                           |

|            | uld you like a reply? Y N                           |                                           |

|            | vice: dsPIC30F2010                                  | Literature Number: DS70118J               |

| Que        | estions:                                            |                                           |

| 1.         | What are the best features of this document?        |                                           |

|            |                                                     |                                           |

| 2.         | How does this document meet your hardware and       | software development needs?               |