Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20 MIPS                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                  |

| Number of I/O              | 20                                                                             |

| Program Memory Size        | 12KB (4K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 1K x 8                                                                         |

| RAM Size                   | 512 x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 6x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f2010t-20e-mm |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 CPU ARCHITECTURE OVERVIEW

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

#### 2.1 Core Overview

The core has a 24-bit instruction word. The Program Counter (PC) is 23 bits wide with the Least Significant bit (LSb) always clear (see **Section 3.1 "Program Address Space**"), and the Most Significant bit (MSb) is ignored during normal program execution, except for certain specialized instructions. Thus, the PC can address up to 4M instruction words of user program space. An instruction prefetch mechanism is used to help maintain throughput. Program loop constructs, free from loop count management overhead, are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The working register array consists of 16x16-bit registers, each of which can act as data, address or offset registers. One working register (W15) operates as a software Stack Pointer for interrupts and calls.

The data space is 64 Kbytes (32K words) and is split into two blocks, referred to as X and Y data memory. Each block has its own independent Address Generation Unit (AGU). Most instructions operate solely through the X memory AGU, which provides the appearance of a single unified data space. The Multiply-Accumulate (MAC) class of dual source DSP instructions operate through both the X and Y AGUs, splitting the data address space into two parts (see **Section 3.2 "Data Address Space"**). The X and Y data space boundary is device specific and cannot be altered by the user. Each data word consists of 2 bytes, and most instructions can address data either as words or bytes.

There are two methods of accessing data stored in program memory:

• The upper 32 Kbytes of data space memory can be mapped into the lower half (user space) of program space at any 16K program word boundary, defined by the 8-bit Program Space Visibility Page (PSVPAG) register. This lets any instruction access program space as if it were data space, with a limitation that the access requires an additional cycle. Moreover, only the lower 16 bits of each instruction word can be accessed using this method.  Linear indirect access of 32K word pages within program space is also possible using any working register, via table read and write instructions. Table read and write instructions can be used to access all 24 bits of an instruction word.

Overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. This is primarily intended to remove the loop overhead for DSP algorithms.

The X AGU also supports Bit-Reversed Addressing on destination effective addresses, to greatly simplify input or output data reordering for radix-2 FFT algorithms. Refer to **Section 4.0 "Address Generator Units"** for details on Modulo and Bit-Reversed Addressing.

The core supports Inherent (no operand), Relative, Literal, Memory Direct, Register Direct, Register Indirect, Register Offset and Literal Offset Addressing modes. Instructions are associated with predefined Addressing modes, depending upon their functional requirements.

For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, 3-operand instructions are supported, allowing C = A + B operations to be executed in a single cycle.

A DSP engine has been included to significantly enhance the core arithmetic capability and throughput. It features a high-speed 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. Data in the accumulator or any working register can be shifted up to 15 bits right or 16 bits left in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC class of instructions can concurrently fetch two data operands from memory, while multiplying two W registers. To enable this concurrent fetching of data operands, the data space has been split for these instructions and linear for all others. This has been achieved in a transparent and flexible manner, by dedicating certain working registers to each address space for the MAC class of instructions.

The core does not support a multi-stage instruction pipeline. However, a single stage instruction prefetch mechanism is used, which accesses and partially decodes instructions a cycle ahead of execution, in order to maximize available execution time. Most instructions execute in a single cycle, with certain exceptions.

The core features a vectored exception processing structure for traps and interrupts, with 62 independent vectors. The exceptions consist of up to 8 traps (of which 4 are reserved) and 54 interrupts. Each interrupt is prioritized based on a user-assigned priority between 1 and 7 (1 being the lowest priority and 7 being the highest) in conjunction with a predetermined 'natural order'. Traps have fixed priorities, ranging from 8 to 15.

# 3.0 MEMORY ORGANIZATION

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

# 3.1 Program Address Space

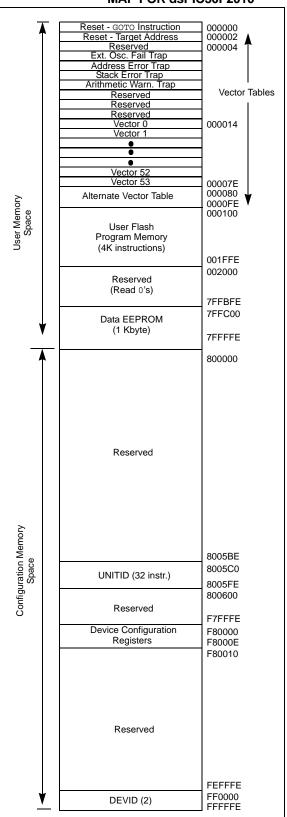

The program address space is 4M instruction words. It is addressable by a 24-bit value from either the 23-bit PC, table instruction Effective Address (EA), or data space EA, when program space is mapped into data space, as defined by Table 3-1. Note that the program space address is incremented by two between successive program words, in order to provide compatibility with data space addressing.

User program space access is restricted to the lower 4M instruction word address range (0x000000 to 0x7FFFFE), for all accesses other than TBLRD/TBLWT, which use TBLPAG<7> to determine user or configuration space access. In Table 3-1, Read/Write instructions, bit 23 allows access to the Device ID, the User ID and the Configuration bits. Otherwise, bit 23 is always clear.

| Note: | The address map shown in Figure 3-1 is |  |  |  |  |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | conceptual, and the actual memory con- |  |  |  |  |  |  |  |  |  |  |

|       | figuration may vary across individual  |  |  |  |  |  |  |  |  |  |  |

|       | devices depending on available memory. |  |  |  |  |  |  |  |  |  |  |

#### FIGURE 3-1: PR

#### PROGRAM SPACE MEMORY MAP FOR dsPIC30F2010

#### 6.6.3 LOADING WRITE LATCHES

Example 6-2 shows a sequence of instructions that can be used to load the 96 bytes of write latches. 32 TBLWTL and 32 TBLWTH instructions are needed to load the write latches selected by the table pointer.

#### EXAMPLE 6-2: LOADING WRITE LATCHES

```

; Set up a pointer to the first program memory location to be written

; program memory selected, and writes enabled

MOV

#0x0000,W0

MOV

W0 TBLPAG

; Initialize PM Page Boundary SFR

MOV

#0x6000,W0

; An example program memory address

; Perform the TBLWT instructions to write the latches

; 0th_program_word

MOV

#LOW_WORD_0,W2

;

MOV

#HIGH_BYTE_0,W3

;

TBLWTL W2 [W0]

; Write PM low word into program latch

TBLWTH W3 [W0++]

; Write PM high byte into program latch

; 1st_program_word

MOV

#LOW_WORD_1,W2

;

MOV

#HIGH_BYTE_1,W3

;

TBLWTL W2 [W0]

; Write PM low word into program latch

TBLWTH W3 [W0++]

; Write PM high byte into program latch

2nd_program_word

#LOW_WORD_2,W2

MOV

;

MOV

#HIGH_BYTE_2,W3

;

TBLWTL W2, [W0]

; Write PM low word into program latch

TBLWTH W3 [W0++]

; Write PM high byte into program latch

; 31st_program_word

MOV

#LOW WORD 31,W2

;

#HIGH_BYTE_31,W3

MOV

;

TBLWTL W2 [W0]

; Write PM low word into program latch

TBLWTH W3 [W0++]

; Write PM high byte into program latch

```

Note: In Example 6-2, the contents of the upper byte of W3 has no effect.

#### 6.6.4 INITIATING THE PROGRAMMING SEQUENCE

For protection, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

#### EXAMPLE 6-3: INITIATING A PROGRAMMING SEQUENCE

| DI | SI    |             |   | Block all interrupts with priority <7<br>for next 5 instructions |

|----|-------|-------------|---|------------------------------------------------------------------|

| MC | V     | #0x55,W0    |   |                                                                  |

| MC | V     | W0,NVMKEY   | ; | Write the 0x55 key                                               |

| MC | V     | #0xAA,W1    | ; |                                                                  |

| MC | V     | W1,NVMKEY   | ; | Write the OxAA key                                               |

| BS | SET 1 | NVMCON, #WR | ; | Start the erase sequence                                         |

| NC | P     |             | ; | Insert two NOPs after the erase                                  |

| NC | P     |             | ; | command is asserted                                              |

|    |       |             |   |                                                                  |

# 9.0 TIMER1 MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the 16-bit general purpose Timer1 module and associated operational modes. Figure 9-1 depicts the simplified block diagram of the 16-bit Timer1 Module.

| Note: | Timer1 is a 'Type A' timer. Refer to the  |

|-------|-------------------------------------------|

|       | specifications for the Type A timer in    |

|       | Section 22.0 "Electrical Characteristics" |

|       | for details.                              |

The following sections provide a detailed description of the operational modes of the timers, including setup and control registers along with associated block diagrams.

The Timer1 module is a 16-bit timer which can serve as the time counter for the real-time clock, or operate as a free running interval timer/counter. The 16-bit timer has the following modes:

- 16-bit Timer

- 16-bit Synchronous Counter

- 16-bit Asynchronous Counter

Further, the following operational characteristics are supported:

- Timer gate operation

- Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit period register match or falling edge of external gate signal

These operating modes are determined by setting the appropriate bit(s) in the 16-bit SFR, T1CON. Figure 9-1 presents a block diagram of the 16-bit timer module.

**16-bit Timer Mode:** In the 16-bit Timer mode, the timer increments on every instruction cycle up to a match value, preloaded into the period register PR1, then resets to '0' and continues to count.

When the CPU goes into the Idle mode, the timer will stop incrementing unless the TSIDL (T1CON<13>) bit = 0. If TSIDL = 1, the timer module logic will resume the incrementing sequence upon termination of the CPU Idle mode.

**16-bit Synchronous Counter Mode:** In the 16-bit Synchronous Counter mode, the timer increments on the rising edge of the applied external clock signal, which is synchronized with the internal phase clocks. The timer counts up to a match value preloaded in PR1, then resets to '0' and continues.

When the CPU goes into the Idle mode, the timer will stop incrementing, unless the respective TSIDL bit = 0. If TSIDL = 1, the timer module logic will resume the incrementing sequence upon termination of the CPU Idle mode.

**16-bit Asynchronous Counter Mode:** In the 16-bit Asynchronous Counter mode, the timer increments on every rising edge of the applied external clock signal. The timer counts up to a match value preloaded in PR1, then resets to '0' and continues.

When the timer is configured for the Asynchronous mode of operation and the CPU goes into the Idle mode, the timer will stop incrementing if TSIDL = 1.

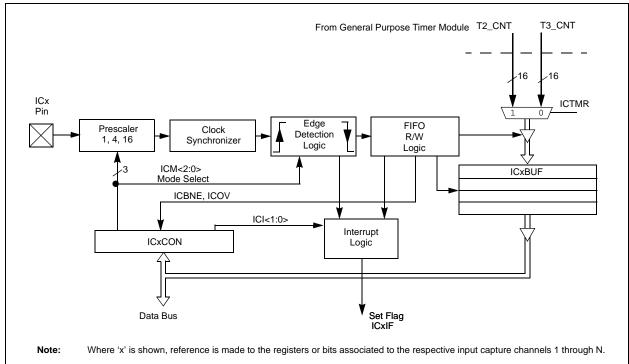

# 11.0 INPUT CAPTURE MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the Input Capture module and associated operational modes. The features provided by this module are useful in applications requiring Frequency (Period) and Pulse measurement. Figure 11-1 depicts a block diagram of the Input Capture module. Input capture is useful for such modes as:

- Frequency/Period/Pulse Measurements

- Additional sources of External Interrupts

The key operational features of the Input Capture module are:

- Simple Capture Event mode

- Timer2 and Timer3 mode selection

- Interrupt on input capture event

These operating modes are determined by setting the appropriate bits in the ICxCON register (where x = 1,2,...,N). The dsPIC DSC devices contain up to eight capture channels, (i.e., the maximum value of N is 8).

Note: The dsPIC30F2010 device has four capture inputs – IC1, IC2, IC7 and IC8. The naming of these four capture channels is intentional and preserves software compatibility with other dsPIC DSC devices.

### FIGURE 11-1: INPUT CAPTURE MODE BLOCK DIAGRAM

# 11.1 Simple Capture Event Mode

The simple capture events in the dsPIC30F product family are:

- Capture every falling edge

- · Capture every rising edge

- Capture every 4th rising edge

- Capture every 16th rising edge

- · Capture every rising and falling edge

These simple Input Capture modes are configured by setting the appropriate bits ICM<2:0> (ICxCON<2:0>).

#### 11.1.1 CAPTURE PRESCALER

There are four input capture prescaler settings, specified by bits ICM<2:0> (ICxCON<2:0>). Whenever the capture channel is turned off, the prescaler counter will be cleared. In addition, any Reset will clear the prescaler counter.

#### 11.1.2 CAPTURE BUFFER OPERATION

Each capture channel has an associated FIFO buffer, which is four 16-bit words deep. There are two status flags, which provide status on the FIFO buffer:

- ICBNE Input Capture Buffer Not Empty

- ICOV Input Capture Overflow

The ICBFNE will be set on the first input capture event and remain set until all capture events have been read from the FIFO. As each word is read from the FIFO, the remaining words are advanced by one position within the buffer.

In the event that the FIFO is full with four capture events and a fifth capture event occurs prior to a read of the FIFO, an overflow condition will occur and the ICOV bit will be set to a logic '1'. The fifth capture event is lost and is not stored in the FIFO. No additional events will be captured until all four events have been read from the buffer.

If a FIFO read is performed after the last read and no new capture event has been received, the read will yield indeterminate results.

# 11.1.3 TIMER2 AND TIMER3 SELECTION MODE

The input capture module consists of up to eight input capture channels. Each channel can select between one of two timers for the time base, Timer2 or Timer3.

Selection of the timer resource is accomplished through SFR bit ICTMR (ICxCON<7>). Timer3 is the default timer resource available for the input capture module.

#### 11.1.4 HALL SENSOR MODE

When the input capture module is set for capture on every edge, rising and falling, ICM<2:0> = 0.01, the following operations are performed by the input capture logic:

- The input capture interrupt flag is set on every edge, rising and falling.

- The interrupt on Capture mode setting bits, ICI<1:0>, is ignored, since every capture generates an interrupt.

- A capture overflow condition is not generated in this mode.

# TABLE 12-1: OUTPUT COMPARE REGISTER MAP

| SFR Name | Addr. | Bit 15 | Bit 14                           | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7     | Bit 6       | Bit 5 | Bit 4               | Bit 3   | Bit 2 | Bit 1    | Bit 0 | Reset State         |

|----------|-------|--------|----------------------------------|--------|--------|--------|--------|-------|----------|-----------|-------------|-------|---------------------|---------|-------|----------|-------|---------------------|

| OC1RS    | 0180  |        |                                  |        |        |        |        | Out   | put Comp | are 1 Mas | ter Registe | er    |                     |         |       |          |       | 0000 0000 0000 0000 |

| OC1R     | 0182  |        | Output Compare 1 Slave Register  |        |        |        |        |       |          |           |             |       | 0000 0000 0000 0000 |         |       |          |       |                     |

| OC1CON   | 0184  | _      | OCFRZ                            | OCSIDL | _      | _      | —      | _     | _        | _         | _           | _     | OCFLT1              | OCTSEL1 |       | OCM<2:0> | >     | 0000 0000 0000 0000 |

| OC2RS    | 0186  |        | Output Compare 2 Master Register |        |        |        |        |       |          |           |             |       | 0000 0000 0000 0000 |         |       |          |       |                     |

| OC2R     | 0188  |        | Output Compare 2 Slave Register  |        |        |        |        |       |          |           |             |       | 0000 0000 0000 0000 |         |       |          |       |                     |

| OC2CON   | 018A  | _      | OCFRZ                            | OCSIDL | _      |        | _      | _     | Ι        | -         | Ι           | _     | OCFLT2              | OCTSEL2 |       | OCM<2:0> | >     | 0000 0000 0000 0000 |

**Legend:** — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

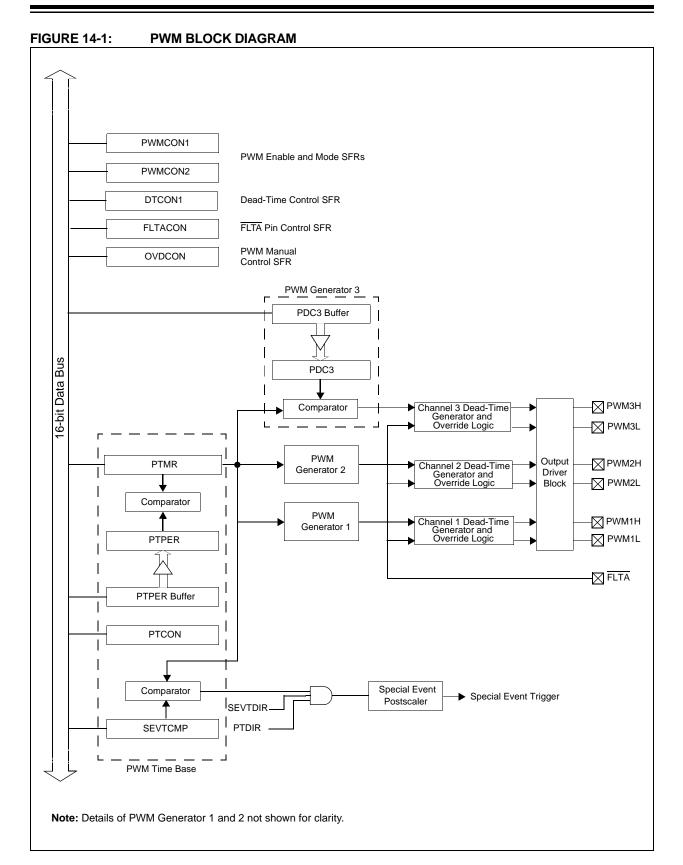

# 14.1 PWM Time Base

The PWM time base is provided by a 15-bit timer with a prescaler and postscaler. The time base is accessible via the PTMR SFR. PTMR<15> is a read-only status bit, PTDIR, that indicates the present count direction of the PWM time base. If PTDIR is cleared, PTMR is counting upwards. If PTDIR is set, PTMR is counting downwards. The PWM time base is configured via the PTCON SFR. The time base is enabled/disabled by setting/clearing the PTEN bit in the PTCON SFR. PTMR is not cleared when the PTEN bit is cleared in software.

The PTPER SFR sets the counting period for PTMR. The user must write a 15-bit value to PTPER<14:0>. When the value in PTMR<14:0> matches the value in PTPER<14:0>, the time base will either Reset to '0', or reverse the count direction on the next occurring clock cycle. The action taken depends on the Operating mode of the time base.

**Note:** If the period register is set to 0x0000, the timer will stop counting, and the interrupt and the special event trigger will not be generated, even if the special event value is also 0x0000. The module will not update the period register if it is already at 0x0000; therefore, the user must disable the module in order to update the period register.

The PWM time base can be configured for four different modes of operation:

- Free Running mode

- Single Shot mode

- Continuous Up/Down Count mode

- Continuous Up/Down Count mode with interrupts for double updates

These four modes are selected by the PTMOD<1:0> bits in the PTCON SFR. The Up/Down Counting modes support center-aligned PWM generation. The Single Shot mode allows the PWM module to support pulse control of certain Electronically Commutative Motors (ECMs).

The interrupt signals generated by the PWM time base depend on the mode selection bits (PTMOD<1:0>) and the postscaler bits (PTOPS<3:0>) in the PTCON SFR.

#### 14.1.1 FREE RUNNING MODE

In the Free Running mode, the PWM time base counts upwards until the value in the Time Base Period register (PTPER) is matched. The PTMR register is reset on the following input clock edge and the time base will continue to count upwards as long as the PTEN bit remains set.

When the PWM time base is in the Free Running mode (PTMOD<1:0> = 00), an interrupt event is generated each time a match with the PTPER register occurs and the PTMR register is Reset to zero. The postscaler selection bits may be used in this mode of the timer to reduce the frequency of the interrupt events.

#### 14.1.2 SINGLE-SHOT MODE

In the Single-Shot Counting mode, the PWM time base begins counting upwards when the PTEN bit is set. When the value in the PTMR register matches the PTPER register, the PTMR register will be reset on the following input clock edge and the PTEN bit will be cleared by the hardware to halt the time base.

When the PWM time base is in the Single-Shot mode (PTMOD<1:0> = 01), an interrupt event is generated when a match with the PTPER register occurs, the PTMR register is reset to zero on the following input clock edge, and the PTEN bit is cleared. The postscaler selection bits have no effect in this mode of the timer.

#### 14.1.3 CONTINUOUS UP/DOWN COUNTING MODES

In the Continuous Up/Down Counting modes, the PWM time base counts upwards until the value in the PTPER register is matched. The timer will begin counting downwards on the following input clock edge. The PTDIR bit in the PTCON SFR is read-only and indicates the counting direction The PTDIR bit is set when the timer counts downwards.

In the Up/Down Counting mode (PTMOD<1:0> = 10), an interrupt event is generated each time the value of the PTMR register becomes zero and the PWM time base begins to count upwards. The postscaler selection bits may be used in this mode of the timer to reduce the frequency of the interrupt events.

# 14.5.1 DUTY CYCLE REGISTER BUFFERS

The four PWM duty cycle registers are double-buffered to allow glitchless updates of the PWM outputs. For each duty cycle, there is a duty cycle register that is accessible by the user and a second duty cycle register that holds the actual compare value used in the present PWM period.

For edge-aligned PWM output, a new duty cycle value will be updated whenever a match with the PTPER register occurs and PTMR is reset. The contents of the duty cycle buffers are automatically loaded into the duty cycle registers when the PWM time base is disabled (PTEN = 0) and the UDIS bit is cleared in PWMCON2.

When the PWM time base is in the Up/Down Counting mode, new duty cycle values are updated when the value of the PTMR register is zero and the PWM time base begins to count upwards. The contents of the duty cycle buffers are automatically loaded into the duty cycle registers when the PWM time base is disabled (PTEN = 0).

When the PWM time base is in the Up/Down Counting mode with double updates, new duty cycle values are updated when the value of the PTMR register is zero, and when the value of the PTMR register matches the value in the PTPER register. The contents of the duty cycle buffers are automatically loaded into the duty cycle registers when the PWM time base is disabled (PTEN = 0).

# 14.6 Complementary PWM Operation

In the Complementary mode of operation, each pair of PWM outputs is obtained by a complementary PWM signal. A dead time may be optionally inserted during device switching, when both outputs are inactive for a short period (Refer to **Section 14.7** "**Dead-Time Generators**").

In Complementary mode, the duty cycle comparison units are assigned to the PWM outputs as follows:

- PDC1 register controls PWM1H/PWM1L outputs

- PDC2 register controls PWM2H/PWM2L outputs

- PDC3 register controls PWM3H/PWM3L outputs

The Complementary mode is selected for each PWM I/O pin pair by clearing the appropriate PMODx bit in the PWMCON1 SFR. The PWM I/O pins are set to Complementary mode by default upon a device Reset.

### 14.7 Dead-Time Generators

Dead-time generation may be provided when any of the PWM I/O pin pairs are operating in the Complementary Output mode. The PWM outputs use Push-Pull drive circuits. Due to the inability of the power output devices to switch instantaneously, some amount of time must be provided between the turn off event of one PWM output in a complementary pair and the turn on event of the other transistor.

#### 14.7.1 DEAD-TIME GENERATORS

Each complementary output pair for the PWM module has a 6-bit down counter that is used to produce the dead-time insertion. As shown in Figure 14-4, the dead-time unit has a rising and falling edge detector connected to the duty cycle comparison output.

#### 14.7.2 DEAD-TIME RANGES

The amount of dead time provided by the dead-time unit is selected by specifying the input clock prescaler value and a 6-bit unsigned value.

Four input clock prescaler selections have been provided to allow a suitable range of dead times, based on the device operating frequency. The dead-time clock prescaler value is selected using the DTAPS<1:0> and DTBPS<1:0> control bits in the DTCON1 SFR. One of four clock prescaler options (TCY, 2 TCY, 4 TCY or 8 TCY) is selected for the dead-time value.

After the prescaler value is selected, the dead time is adjusted by loading a 6-bit unsigned value into the DTCON1 SFR.

The dead-time unit prescaler is cleared on the following events:

- On a load of the down timer due to a duty cycle comparison edge event.

- On a write to the DTCON1 register.

- On any device Reset.

**Note:** The user should not modify the DTCON1 values while the PWM module is operating (PTEN = 1). Unexpected results may occur.

### 15.3 Slave Select Synchronization

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be configured in SPI Slave mode, with  $\overline{SSx}$  pin control enabled (SSEN = 1). When the  $\overline{SSx}$  pin is low, transmission and reception are enabled, and the SDOx pin is driven. When  $\overline{SSx}$  pin goes high, the SDOx pin is no longer driven. Also, the SPI module is resynchronized, and all counters/control circuitry are reset. Therefore, when the  $\overline{SSx}$  pin is asserted low again, transmission/reception will begin at the MSb, even if  $\overline{SSx}$  had been de-asserted in the middle of a transmit/receive.

#### 15.4 SPI Operation During CPU Sleep Mode

During Sleep mode, the SPI module is shut down. If the CPU enters Sleep mode while an SPI transaction is in progress, then the transmission and reception is aborted.

The transmitter and receiver will stop in Sleep mode. However, register contents are not affected by entering or exiting Sleep mode.

# 15.5 SPI Operation During CPU Idle Mode

When the device enters Idle mode, all clock sources remain functional. The SPISIDL bit (SPIxSTAT<13>) selects if the SPI module will stop or continue on Idle. If SPISIDL = 0, the module will continue to operate when the CPU enters Idle mode. If SPISIDL = 1, the module will stop when the CPU enters Idle mode.

NOTES:

# 17.2 Enabling and Setting Up UART

#### 17.2.1 ENABLING THE UART

The UART module is enabled by setting the UARTEN bit in the UxMODE register (where x = 1 only). Once enabled, the UxTX and UxRX pins are configured as an output and an input respectively, overriding the TRIS and LATCH register bit settings for the corresponding I/O port pins. The UxTX pin is at logic '1' when no transmission is taking place.

#### 17.2.2 DISABLING THE UART

The UART module is disabled by clearing the UARTEN bit in the UxMODE register. This is the default state after any Reset. If the UART is disabled, all I/O pins operate as port pins under the control of the latch and TRIS bits of the corresponding port pins.

Disabling the UART module resets the buffers to empty states. Any data characters in the buffers are lost, and the baud rate counter is reset.

All error and status flags associated with the UART module are reset when the module is disabled. The URXDA, OERR, FERR, PERR, UTXEN, UTXBRK and UTXBF bits are cleared, whereas RIDLE and TRMT are set. Other control bits, including ADDEN, URXISEL<1:0>, UTXISEL, as well as the UxMODE and UxBRG registers, are not affected.

Clearing the UARTEN bit while the UART is active will abort all pending transmissions and receptions and reset the module as defined above. Re-enabling the UART will restart the UART in the same configuration.

#### 17.2.3 ALTERNATE I/O

The alternate I/O function is enabled by setting the ALTIO bit (UxMODE<10>). If ALTIO = 1, the UxATX and UxARX pins (alternate transmit and alternate receive pins, respectively) are used by the UART module instead of the UxTX and UxRX pins. If ALTIO = 0, the UxTX and UxRX pins are used by the UART module.

# 17.2.4 SETTING UP DATA, PARITY AND STOP BIT SELECTIONS

Control bits PDSEL<1:0> in the UxMODE register are used to select the data length and parity used in the transmission. The data length may either be 8 bits with even, odd, or no parity, or 9 bits with no parity.

The STSEL bit determines whether one or two Stop bits will be used during data transmission.

The default (Power-on) setting of the UART is 8 bits, no parity, 1 Stop bit (typically represented as 8, N, 1).

# 17.3 Transmitting Data

#### 17.3.1 TRANSMITTING IN 8-BIT DATA MODE

The following steps must be performed in order to transmit 8-bit data:

1. Set up the UART:

First, the data length, parity and number of Stop bits must be selected. Then, the Transmit and Receive Interrupt enable and priority bits are setup in the UxMODE and UxSTA registers. Also, the appropriate baud rate value must be written to the UxBRG register.

- Enable the UART by setting the UARTEN bit (UxMODE<15>).

- 3. Set the UTXEN bit (UxSTA<10>), thereby enabling a transmission.

**Note:** The UTXEN bit must be set after the UARTEN bit is set to enable UART transmissions.

- 4. Write the byte to be transmitted to the lower byte of UxTXREG. The value will be transferred to the Transmit Shift register (UxTSR) immediately and the serial bit stream will start shifting out during the next rising edge of the baud clock. Alternatively, the data byte may be written while UTXEN = 0, following which the user may set UTXEN. This will cause the serial bit stream to begin immediately because the baud clock will start from a cleared state.

- 5. A Transmit interrupt will be generated depending on the value of the interrupt control bit UTXISEL (UxSTA<15>).

#### 17.3.2 TRANSMITTING IN 9-BIT DATA MODE

The sequence of steps involved in the transmission of 9-bit data is similar to 8-bit transmission, except that a 16-bit data word (of which the upper 7 bits are always clear) must be written to the UxTXREG register.

# 17.3.3 TRANSMIT BUFFER (UXTXB)

The transmit buffer is 9 bits wide and four characters deep. Including the Transmit Shift Register (UxTSR), the user effectively has a 5-deep FIFO (First In First Out) buffer. The UTXBF status bit (UxSTA<9>) indicates whether the transmit buffer is full.

If a user attempts to write to a full buffer, the new data will not be accepted into the FIFO, and no data shift will occur within the buffer. This enables recovery from a buffer overrun condition.

The FIFO is reset during any device Reset, but is not affected when the device enters or wakes up from a Power-Saving mode.

# **19.0 SYSTEM INTEGRATION**

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

There are several features intended to maximize system reliability, minimize cost through elimination of external components, provide Power-Saving Operating modes and offer code protection:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

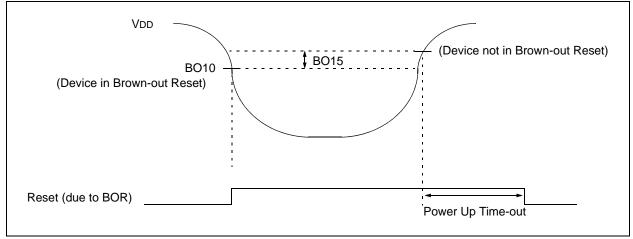

- Programmable Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- Power-Saving modes (Sleep and Idle)

- Code Protection

- Unit ID Locations

- In-Circuit Serial Programming (ICSP) programming capability

dsPIC30F devices have a Watchdog Timer, which is permanently enabled via the Configuration bits, or can be software controlled. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Startup Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Powerup Timer (PWRT), which provides a delay on power-up only, designed to keep the part in Reset while the power supply stabilizes. With these two timers on-chip, most applications need no external Reset circuitry.

Sleep mode is designed to offer a very low current Power-down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer Wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit a wide variety of applications. In the Idle mode, the clock sources are still active, but the CPU is shut off. The RC oscillator option saves system cost, while the LP crystal option saves power.

# 19.1 Oscillator System Overview

The dsPIC30F oscillator system has the following modules and features:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to boost internal operating frequency

- A clock switching mechanism between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- Clock Control Register OSCCON

- · Configuration bits for main oscillator selection

Table 19-1 provides a summary of the dsPIC30F Oscillator Operating modes. A simplified diagram of the oscillator system is shown in Figure 19-1.

Configuration bits determine the clock source upon Power-on Reset (POR) and Brown-out Reset (BOR). Thereafter, the clock source can be changed between permissible clock sources. The OSCCON register controls the clock switching and reflects system clock related status bits.

# TABLE 19-1: OSCILLATOR OPERATING MODES

| Oscillator Mode | Description                                                                        |

|-----------------|------------------------------------------------------------------------------------|

| XTL             | 200 kHz-4 MHz crystal on OSC1:OSC2.                                                |

| XT              | 4 MHz-10 MHz crystal on OSC1:OSC2.                                                 |

| XT w/ PLL 4x    | 4 MHz-10 MHz crystal on OSC1:OSC2. 4x PLL enabled.                                 |

| XT w/ PLL 8x    | 4 MHz-10 MHz crystal on OSC1:OSC2. 8x PLL enabled.                                 |

| XT w/ PLL 16x   | 4 MHz-10 MHz crystal on OSC1:OSC2. 16x PLL enabled <sup>(1)</sup> .                |

| LP              | 32 kHz crystal on SOSCO:SOSCI <sup>(2)</sup> .                                     |

| HS              | 10 MHz-25 MHz crystal.                                                             |

| EC              | External clock input (0-40 MHz).                                                   |

| ECIO            | External clock input (0-40 MHz). OSC2 pin is I/O.                                  |

| EC w/ PLL 4x    | External clock input (0-40 MHz). OSC2 pin is I/O. 4x PLL enabled <sup>(1)</sup> .  |

| EC w/ PLL 8x    | External clock input (0-40 MHz). OSC2 pin is I/O. 8x PLL enabled <sup>(1)</sup> .  |

| EC w/ PLL 16x   | External clock input (0-40 MHz). OSC2 pin is I/O. 16x PLL enabled <sup>(1)</sup> . |

| ERC             | External RC oscillator. OSC2 pin is Fosc/4 output <sup>(3)</sup> .                 |

| ERCIO           | External RC oscillator. OSC2 pin is I/O <sup>(3)</sup> .                           |

| FRC             | 7.37 MHz internal RC Oscillator.                                                   |

| LPRC            | 512 kHz internal RC Oscillator.                                                    |

**Note 1:** dsPIC30F maximum operating frequency of 120 MHz must be met.

2: LP oscillator can be conveniently shared as system clock, as well as real-time clock for Timer1.

**3:** Requires external R and C. Frequency operation up to 4 MHz.

# 21.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

# 21.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

# 21.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

|              |        |                                                           | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |   |      |    |                                                                        |  |  |  |  |  |  |

|--------------|--------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|----|------------------------------------------------------------------------|--|--|--|--|--|--|

| Param<br>No. | Symbol | Characteristic                                            | Min Typ <sup>(1)</sup> Max Units Conditions                                                                                                                                              |   |      |    |                                                                        |  |  |  |  |  |  |

|              | Vol    | Output Low Voltage <sup>(2)</sup>                         |                                                                                                                                                                                          |   |      |    |                                                                        |  |  |  |  |  |  |

| DO10         |        | I/O ports                                                 | —                                                                                                                                                                                        | — | 0.6  | V  | Iol = 8.5 mA, Vdd = 5V                                                 |  |  |  |  |  |  |

|              |        |                                                           | —                                                                                                                                                                                        | — | 0.15 | V  | IOL = 2.0 mA, VDD = 3V                                                 |  |  |  |  |  |  |

| DO16         |        | OSC2/CLKO                                                 | —                                                                                                                                                                                        | — | 0.6  | V  | IOL = 1.6 mA, VDD = 5V                                                 |  |  |  |  |  |  |

|              |        | (RC or EC Osc mode)                                       | —                                                                                                                                                                                        | — | 0.72 | V  | IOL = 2.0 mA, VDD = 3V                                                 |  |  |  |  |  |  |

|              | Voh    | Output High Voltage <sup>(2)</sup>                        |                                                                                                                                                                                          |   |      |    |                                                                        |  |  |  |  |  |  |

| DO20         |        | I/O ports                                                 | Vdd - 0.7                                                                                                                                                                                | — | _    | V  | IOH = -3.0 mA, VDD = 5V                                                |  |  |  |  |  |  |

|              |        |                                                           | Vdd - 0.2                                                                                                                                                                                | — | —    | V  | IOH = -2.0 mA, VDD = 3V                                                |  |  |  |  |  |  |

| DO26         |        | OSC2/CLKO                                                 | Vdd - 0.7                                                                                                                                                                                | — | _    | V  | IOH = -1.3 mA, VDD = 5V                                                |  |  |  |  |  |  |

|              |        | (RC or EC Osc mode)                                       | Vdd - 0.1                                                                                                                                                                                | — | _    | V  | Iон = -2.0 mA, Vdd = 3V                                                |  |  |  |  |  |  |

|              |        | Capacitive Loading Specs<br>on Output Pins <sup>(2)</sup> |                                                                                                                                                                                          |   |      |    |                                                                        |  |  |  |  |  |  |

| DO50         | Cosc2  | OSC2/SOSC2 pin                                            |                                                                                                                                                                                          | — | 15   | pF | In XTL, XT, HS and LP modes when external clock is used to drive OSC1. |  |  |  |  |  |  |

| DO56         | Cio    | All I/O pins and OSC2                                     | —                                                                                                                                                                                        | — | 50   | pF | RC or EC Osc mode                                                      |  |  |  |  |  |  |

| DO58         | Св     | SCL, SDA                                                  | —                                                                                                                                                                                        | — | 400  | pF | In l <sup>2</sup> C™ mode                                              |  |  |  |  |  |  |

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized but not tested in manufacturing.

#### FIGURE 22-1: BROWN-OUT RESET CHARACTERISTICS

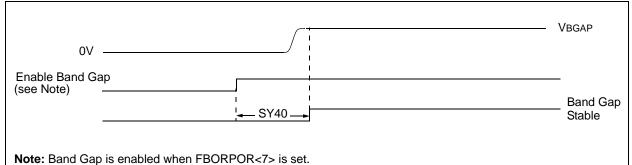

# FIGURE 22-6: BAND GAP START-UP TIME CHARACTERISTICS

# TABLE 22-21: BAND GAP START-UP TIME REQUIREMENTS

| AC CHARACTERISTICS |        |                               | (unles | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |     |       |                                                                                                                                                                   |  |  |

|--------------------|--------|-------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min    | Typ <sup>(2)</sup>                                                                                                                                                                       | Max | Units | Conditions                                                                                                                                                        |  |  |

| SY40               | TBGAP  | Band Gap Start-up Time        |        | 40                                                                                                                                                                                       | 65  | μs    | Defined as the time between the<br>instant that the band gap is enabled<br>and the moment that the band gap<br>reference voltage is stable.<br>RCON<13>Status bit |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated.

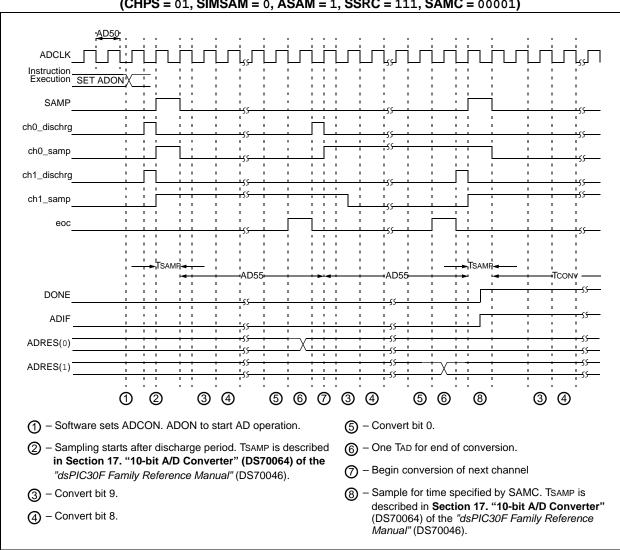

FIGURE 22-25: 10-BIT HIGH-SPEED A/D CONVERSION TIMING CHARACTERISTICS (CHPS = 01, SIMSAM = 0, ASAM = 1, SSRC = 111, SAMC = 00001)

| Instruction Addressing Modes                   |

|------------------------------------------------|

| File Register Instructions                     |

| Fundamental Modes Supported                    |

| MAC Instructions                               |

| MCU Instructions                               |

| Move and Accumulator Instructions              |

| Other Instructions                             |

| Instruction Set                                |

| Inter-Integrated Circuit. See I <sup>2</sup> C |

| Internal Clock Timing Examples 159             |

| Internet Address                               |

| Interrupt Controller                           |

| Register Map 42                                |

| Interrupt Priority                             |

| Traps                                          |

| Interrupt Sequence                             |

| Interrupt Stack Frame 41                       |

| Interrupts                                     |

|                                                |

#### L

| Load Conditions | 15 | 6 | j |

|-----------------|----|---|---|

|                 |    |   |   |

# Μ

| Memory Organization                                  | 19 |

|------------------------------------------------------|----|

| Microchip Internet Web Site                          | 99 |

| Modulo Addressing                                    | 33 |

| Applicability                                        | 35 |

| Operation Example                                    | 34 |

| Start and End Address                                | 33 |

| W Address Register Selection                         | 33 |

| Motor Control PWM Module                             | 81 |

| Fault Timing Characteristics16                       | 68 |

| Timing Characteristics16                             | 68 |

| Timing Requirements16                                | 68 |

| MPLAB ASM30 Assembler, Linker, Librarian14           | 44 |

| MPLAB Integrated Development Environment Software 14 | 43 |

| MPLAB PM3 Device Programmer14                        | 46 |

| MPLAB REAL ICE In-Circuit Emulator System            | 45 |

| MPLINK Object Linker/MPLIB Object Librarian14        | 44 |

# 0

| OC/PWM Module Timing Characteristics |      |

|--------------------------------------|------|

| Operating Current (IDD)              | 150  |

| Operating MIPS vs Voltage            |      |

| dsPIC30F2010                         | 148  |

| Oscillator                           |      |

| Configurations                       |      |

| Fast RC (FRC)                        |      |

| Low Power RC (LPRC)                  | 125  |

| Phase Locked Loop (PLL)              | 125  |

| Oscillator Configurations            |      |

| Fail-Safe Clock Monitor              | 126  |

| Initial Clock Source Selection       | 124  |

| LP Oscillator Control                | 125  |

| Start-up Timer (OST)                 | 124  |

| Oscillator Operating Modes Table     | 122  |

| Oscillator Selection                 |      |

| Oscillator Start-up Timer            |      |

| Timing Characteristics               | 161  |

| Timing Requirements                  | 161  |

| Output Compare Interrupts            | . 73 |

| Output Compare Mode                  |      |

| Register Map                         | . 74 |

| Output Compare Module                | . 71 |

| Timing Characteristics               |      |

| Timing Requirements                  | 166  |

|                                      |      |

| Output Compare Operation During CPU Idle Mode<br>Output Compare Sleep Mode Operation |      |

|--------------------------------------------------------------------------------------|------|

| P                                                                                    |      |

| Packaging Information                                                                |      |

| Marking                                                                              |      |

| Pinout Descriptions                                                                  | 9    |

| PLL Clock Timing Specifications                                                      | 158  |

| POR. See Power-on Reset                                                              |      |

| Port Register Map                                                                    | . 55 |

| Port Write/Read Example                                                              |      |

| PORTB                                                                                |      |

| Register Map                                                                         | . 55 |

| PORTC                                                                                |      |

| Register Map                                                                         | . 55 |

| PORTD                                                                                |      |

| Register Map                                                                         | 55   |

| PORTE                                                                                | . 00 |

| Register Map                                                                         | 55   |

| PORTF                                                                                | . 55 |

|                                                                                      |      |

| Register Map                                                                         | . 55 |

| Position Measurement Mode                                                            |      |

| Power-Down Current (IPD)                                                             |      |

| Power-on Reset (POR)                                                                 |      |

| Oscillator Start-up Timer (OST)                                                      |      |

| Power-up Timer (PWRT)                                                                |      |

| Power-Saving Modes                                                                   |      |

| Idle                                                                                 | 132  |

| Sleep                                                                                | 131  |

| Power-Saving Modes (Sleep and Idle)                                                  | 121  |

| Power-up Timer                                                                       |      |

| Timing Characteristics                                                               | 161  |

| Timing Requirements                                                                  |      |

| Product Identification System                                                        |      |

| Program Address Space                                                                |      |

| Construction                                                                         |      |

| Data Access from Program Memory Using                                                | . 20 |

| Table Instructions                                                                   | 21   |

| Data Access From, Address Generation                                                 |      |

| Memory Map                                                                           |      |

| Table Instructions                                                                   | . 19 |

|                                                                                      | ~    |

| TBLRDH                                                                               |      |

| TBLRDL                                                                               |      |

| TBLWTH                                                                               |      |

| TBLWTL                                                                               |      |

| Program and EEPROM Characteristics                                                   |      |

| Program Counter                                                                      |      |

| Program Data Table Access                                                            | . 22 |

| Program Space Visibility                                                             |      |

| Window into Program Space Operation                                                  | . 23 |

| Programmable                                                                         |      |

| Programmable Digital Noise Filters                                                   | . 77 |

| Programmer's Model                                                                   | . 12 |

| Diagram                                                                              | . 13 |

| Programming Operations                                                               | . 45 |

| Algorithm for Program Flash                                                          | . 45 |

| Erasing a Row of Program Memory                                                      |      |

| Initiating the Programming Sequence                                                  |      |

| Loading Write Latches                                                                |      |

| Programming, Device Instructions                                                     |      |

| Protection Against Accidental Writes to OSCCON                                       |      |

| PWM                                                                                  | 0    |

| Register Map                                                                         | ۵۸   |

| PWM Duty Cycle Comparison Units                                                      |      |

|                                                                                      |      |

| Duty Cycle Register Buffers                                                          |      |

| PWM FLTA Pins                                                                        | . 88 |