Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Decalis                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

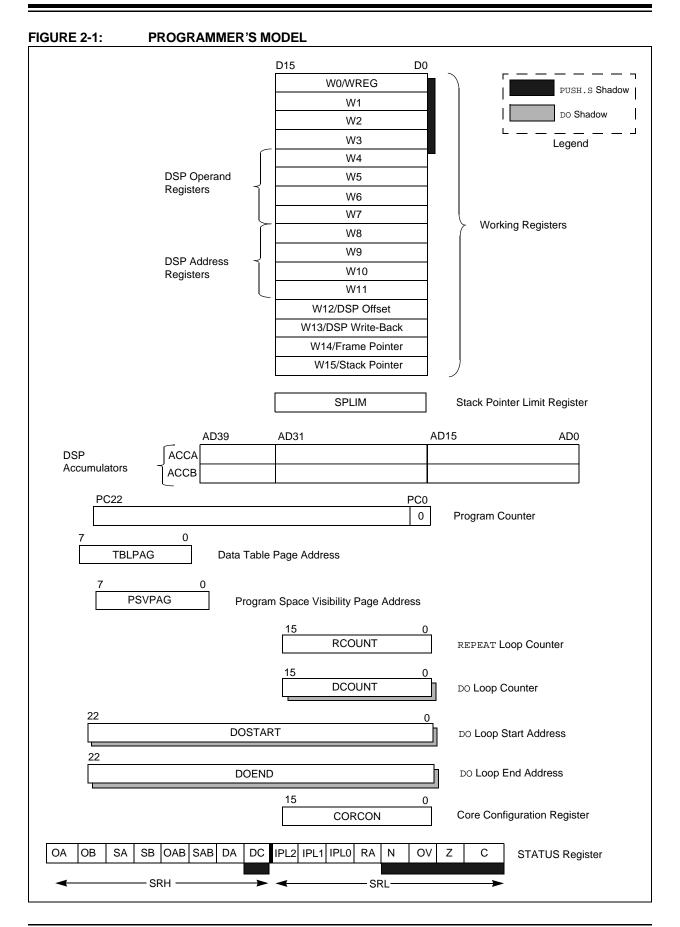

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20 MIPS                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                  |

| Number of I/O              | 20                                                                             |

| Program Memory Size        | 12KB (4K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 1K x 8                                                                         |

| RAM Size                   | 512 x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 6x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f2010t-20e-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.1.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 < function> Operand 2

where Operand 1 is always a working register (i.e., the Addressing mode can only be register direct), which is referred to as Wb. Operand 2 can be a W register, fetched from data memory, or 5-bit literal. The result location can be either a W register or an address location. The following Addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- 5-bit or 10-bit Literal

| Note: | Not  | all    | instruc  | tions  | support  | all   | the    |

|-------|------|--------|----------|--------|----------|-------|--------|

|       | Addı | ressii | ng mod   | es giv | en above | . Ind | livid- |

|       | ual  | instr  | uctions  | may    | support  | diffe | erent  |

|       | subs | sets o | of these | Addre  | ssing mo | des.  |        |

## 4.1.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP Accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the Addressing modes supported by most MCU instructions, Move and Accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the Addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared between both source and destination (but typically only used by one).

In summary, the following Addressing modes are supported by Move and Accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

Note: Not all instructions support all the Addressing modes given above. Individual instructions may support different subsets of these Addressing modes.

#### 4.1.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, utilize a simplified set of Addressing modes to allow the user to effectively manipulate the data pointers through register indirect tables.

The two source operand prefetch registers must be a member of the set {W8, W9, W10, W11}. For data reads, W8 and W9 will always be directed to the X RAGU and W10 and W11 will always be directed to the Y AGU. The effective addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

Note: Register Indirect with Register Offset Addressing is only available for W9 (in X space) and W11 (in Y space).

In summary, the following Addressing modes are supported by the MAC class of instructions:

- Register Indirect

- Register Indirect Post-modified by 2

- Register Indirect Post-modified by 4

- Register Indirect Post-modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.1.5 OTHER INSTRUCTIONS

Besides the various Addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

## 5.1 Interrupt Priority

The user-assignable Interrupt Priority (IP<2:0>) bits for each individual interrupt source are located in the Least Significant 3 bits of each nibble, within the IPCx register(s). Bit 3 of each nibble is not used and is read as a '0'. These bits define the priority level assigned to a particular interrupt by the user.

| Note: | The user-assigned priority levels are from    |

|-------|-----------------------------------------------|

|       | 0, as the lowest priority, to level 7, as the |

|       | highest priority.                             |

Since more than one interrupt request source may be assigned to a specific user-assigned priority level, a means is provided to assign priority within a given level. This method is called "Natural Order Priority" and is final.

Natural Order Priority is determined by the position of an interrupt in the vector table, and only affects interrupt operation when multiple interrupts with the same user-assigned priority become pending at the same time.

Table 5-1 lists the interrupt numbers and interrupt sources for the dsPIC DSC devices and their associated vector numbers.

- **Note 1:** The natural order priority scheme has 0 as the highest priority and 53 as the lowest priority.

- **2:** The natural order priority number is the same as the INT number.

The ability for the user to assign every interrupt to one of seven priority levels means that the user can assign a very high overall priority level to an interrupt with a low natural order priority. For example, the PLVD (Low-Voltage Detect) can be given a priority of 7. The INTO (external interrupt 0) may be assigned to priority level 1, thus giving it a very low effective priority.

#### TABLE 5-1: dsPIC30F2010 INTERRUPT VECTOR TABLE

| VECTOR TABLE  |                  |                                                      |  |  |  |  |  |  |  |

|---------------|------------------|------------------------------------------------------|--|--|--|--|--|--|--|

| INT<br>Number | Vector<br>Number | Interrupt Source                                     |  |  |  |  |  |  |  |

|               | Highest          | Natural Order Priority                               |  |  |  |  |  |  |  |

| 0             | 8                | INT0 – External Interrupt 0                          |  |  |  |  |  |  |  |

| 1             | 9                | IC1 – Input Capture 1                                |  |  |  |  |  |  |  |

| 2             | 10               | OC1 – Output Compare 1                               |  |  |  |  |  |  |  |

| 3             | 11               | T1 – Timer1                                          |  |  |  |  |  |  |  |

| 4             | 12               | IC2 – Input Capture 2                                |  |  |  |  |  |  |  |

| 5             | 13               | OC2 – Output Compare 2                               |  |  |  |  |  |  |  |

| 6             | 14               | T2 – Timer2                                          |  |  |  |  |  |  |  |

| 7             | 15               | T3 – Timer3                                          |  |  |  |  |  |  |  |

| 8             | 16               | SPI1                                                 |  |  |  |  |  |  |  |

| 9             | 17               | U1RX – UART1 Receiver                                |  |  |  |  |  |  |  |

| 10            | 18               | U1TX – UART1 Transmitter                             |  |  |  |  |  |  |  |

| 11            | 19               | ADC – ADC Convert Done                               |  |  |  |  |  |  |  |

| 12            | 20               | NVM – NVM Write Complete                             |  |  |  |  |  |  |  |

| 13            | 21               | SI2C – I <sup>2</sup> C <sup>™</sup> Slave Interrupt |  |  |  |  |  |  |  |

| 14            | 22               | MI2C – I <sup>2</sup> C Master Interrupt             |  |  |  |  |  |  |  |

| 15            | 23               | Input Change Interrupt                               |  |  |  |  |  |  |  |

| 16            | 24               | INT1 – External Interrupt 1                          |  |  |  |  |  |  |  |

| 17            | 25               | IC7 – Input Capture 7                                |  |  |  |  |  |  |  |

| 18            | 26               | IC8 – Input Capture 8                                |  |  |  |  |  |  |  |

| 19            | 27               | Reserved                                             |  |  |  |  |  |  |  |

| 20            | 28               | Reserved                                             |  |  |  |  |  |  |  |

| 20            | 29               | Reserved                                             |  |  |  |  |  |  |  |

| 22            | 30               | Reserved                                             |  |  |  |  |  |  |  |

| 23            | 31               | INT2 - External Interrupt 2                          |  |  |  |  |  |  |  |

| 23            | 32               | Reserved                                             |  |  |  |  |  |  |  |

| 24            | 33               | Reserved                                             |  |  |  |  |  |  |  |

| 25            | 34               | Reserved                                             |  |  |  |  |  |  |  |

| 20            | 35               | Reserved                                             |  |  |  |  |  |  |  |

| 28            | 36               | Reserved                                             |  |  |  |  |  |  |  |

| 20            | 37               |                                                      |  |  |  |  |  |  |  |

|               |                  | Reserved<br>Reserved                                 |  |  |  |  |  |  |  |

| 30<br>31      | 38<br>39         | Reserved                                             |  |  |  |  |  |  |  |

|               |                  |                                                      |  |  |  |  |  |  |  |

| 32            | 40               | Reserved                                             |  |  |  |  |  |  |  |

| 33            | 41               | Reserved                                             |  |  |  |  |  |  |  |

| 34            | 42               | Reserved                                             |  |  |  |  |  |  |  |

| 35            | 43               | Reserved                                             |  |  |  |  |  |  |  |

| 36            | 44               | INT3 – External Interrupt 3                          |  |  |  |  |  |  |  |

| 37            | 45               | Reserved                                             |  |  |  |  |  |  |  |

| 38            | 46               | Reserved                                             |  |  |  |  |  |  |  |

| 39            | 47               | PWM – PWM Period Match                               |  |  |  |  |  |  |  |

| 40            | 48               | QEI – QEI Interrupt                                  |  |  |  |  |  |  |  |

| 41            | 49               | Reserved                                             |  |  |  |  |  |  |  |

| 42            | 50               | Reserved                                             |  |  |  |  |  |  |  |

| 43            | 51               | FLTA – PWM Fault A                                   |  |  |  |  |  |  |  |

| 44            | 52               | Reserved                                             |  |  |  |  |  |  |  |

| 45-53         | 53-61            | Reserved                                             |  |  |  |  |  |  |  |

|               | Lowest           | Natural Order Priority                               |  |  |  |  |  |  |  |

#### 7.3 Writing to the Data EEPROM

To write an EEPROM data location, the following sequence must be followed:

- 1. Erase data EEPROM word.

- a) Select word, data EEPROM, erase and set WREN bit in NVMCON register.

- b) Write address of word to be erased into NVMADRU/NVMADR.

- c) Enable NVM interrupt (optional).

- d) Write 0x55 to NVMKEY.

- e) Write 0xAA to NVMKEY.

- f) Set the WR bit. This will begin erase cycle.

- g) Either poll NVMIF bit or wait for NVMIF interrupt.

- h) The WR bit is cleared when the erase cycle ends.

- 2. Write data word into data EEPROM write latches.

- 3. Program 1 data word into data EEPROM.

- a) Select word, data EEPROM, program and set WREN bit in NVMCON register.

- b) Enable NVM write done interrupt (optional).

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set The WR bit. This will begin program cycle.

- f) Either poll NVMIF bit or wait for NVM interrupt.

- g) The WR bit is cleared when the write cycle ends.

#### EXAMPLE 7-4: DATA EEPROM WORD WRITE

| : р | oint to data me | moriz                          |                                 |

|-----|-----------------|--------------------------------|---------------------------------|

| , P | MOV             | #LOW ADDR WORD,W0              | ; Init pointer                  |

|     | MOV             |                                | , mit pomter                    |

|     |                 | #HIGH_ADDR_WORD,W1             |                                 |

|     | MOV             | W1,TBLPAG                      |                                 |

|     | MOV             | #LOW(WORD),W2                  | ; Get data                      |

|     | TBLWTL          | W2,[ W0]                       | ; Write data                    |

| ; T | he NVMADR captu | res last table access address  |                                 |

| ; S | elect data EEPR | OM for 1 word op               |                                 |

|     | MOV             | #0x4004,W0                     |                                 |

|     | MOV             | W0 NVMCON                      |                                 |

|     |                 | 1                              |                                 |

| ; 0 | perate key to a | llow write operation           |                                 |

|     | DISI #5         | _                              | all interrupts with priority <7 |

|     |                 |                                | ext 5 instructions              |

|     | MOV             | #0x55,W0                       |                                 |

|     | MOV             | W0 NVMKEY                      | ; Write the 0x55 key            |

|     | MOV             | #0xAA,W1                       |                                 |

|     | MOV             | W1 NVMKEY                      | ; Write the OxAA key            |

|     | BSET            |                                | -                               |

|     | -               | NVMCON, #WR                    | ; Initiate program sequence     |

|     | NOP             |                                |                                 |

|     | NOP             |                                |                                 |

| ; W | rite cycle will | complete in 2mS. CPU is not st | alled for the Data Write Cycle  |

| ; U | ser can poll WR | bit, use NVMIF or Timer IRQ to | determine write complete        |

|     |                 |                                |                                 |

The write will not initiate if the above sequence is not exactly followed (write 0x55 to NVMKEY, write 0xAA to NVMCON, then set WR bit) for each word. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in NVMCON must be set to enable writes. This mechanism prevents accidental writes to data EEPROM, due to unexpected code execution. The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect the current write cycle. The WR bit will be inhibited from being set unless the WREN bit is set. The WREN bit must be set on a previous instruction. Both WR and WREN cannot be set with the same instruction.

At the completion of the write cycle, the WR bit is cleared in hardware and the Nonvolatile Memory Write Complete Interrupt Flag bit (NVMIF) is set. The user may either enable this interrupt, or poll this bit. NVMIF must be cleared by software.

#### 7.3.1 WRITING A WORD OF DATA EEPROM

Once the user has erased the word to be programmed, then a table write instruction is used to write one write latch, as shown in Example 7-4.

### 8.0 I/O PORTS

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

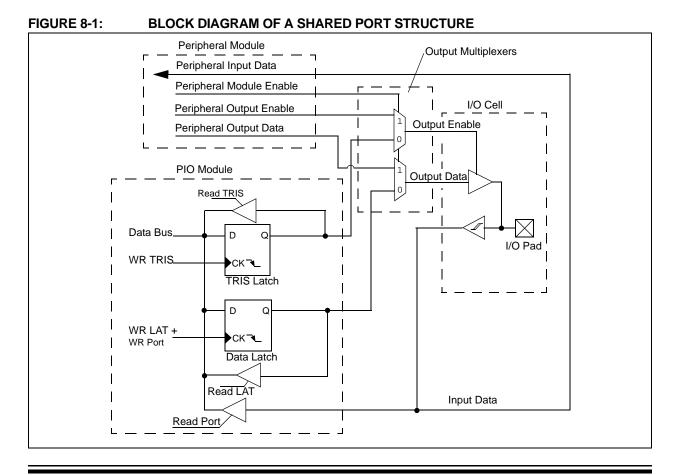

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared between the peripherals and the parallel I/O ports.

All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

### 8.1 Parallel I/O (PIO) Ports

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with the operation of the port pin. The data direction register (TRISx) determines whether the pin is an input

or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch (LATx). Reads from the port (PORTx), read the port pins, and writes to the port pins, write the latch (LATx).

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs. An example is the INT4 pin.

A parallel I/O (PIO) port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pad cell. Figure 8-1 shows how ports are shared with other peripherals, and the associated I/O cell (pad) to which they are connected. Table 8-1 shows the formats of the registers for the shared ports, PORTB through PORTF.

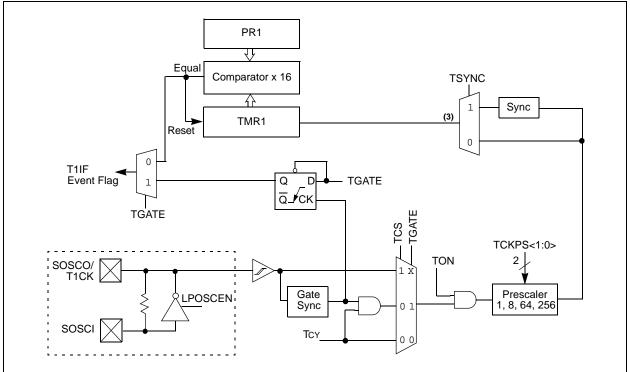

### 9.1 Timer Gate Operation

The 16-bit timer can be placed in the Gated Time Accumulation mode. This mode allows the internal TCY to increment the respective timer when the gate input signal (T1CK pin) is asserted high. Control bit TGATE (T1CON<6>) must be set to enable this mode. The timer must be enabled (TON = 1) and the timer clock source set to internal (TCS = 0).

When the CPU goes into the Idle mode, the timer will stop incrementing, unless TSIDL = 0. If TSIDL = 1, the timer will resume the incrementing sequence upon termination of the CPU Idle mode.

## 9.2 Timer Prescaler

The input clock (Fosc/4 or external clock) to the 16-bit Timer, has a prescale option of 1:1, 1:8, 1:64, and 1:256 selected by control bits TCKPS<1:0> (T1CON<5:4>). The prescaler counter is cleared when any of the following occurs:

- A write to the TMR1 register

- Clearing of the TON bit (T1CON<15>)

- Device Reset such as POR and BOR

However, if the timer is disabled (TON = 0), then the timer prescaler cannot be reset since the prescaler clock is halted.

TMR1 is not cleared when T1CON is written. It is cleared by writing to the TMR1 register.

### 9.3 Timer Operation During Sleep Mode

During CPU Sleep mode, the timer will operate if:

- The timer module is enabled (TON = 1) and

- The timer clock source is selected as external (TCS = 1) and

- The TSYNC bit (T1CON<2>) is asserted to a logic '0', which defines the external clock source as asynchronous

When all three conditions are true, the timer will continue to count up to the period register and be Reset to 0x0000.

When a match between the timer and the period register occurs, an interrupt can be generated, if the respective timer interrupt enable bit is asserted.

#### TABLE 9-1: TIMER1 REGISTER MAP

| -        |                                                                |        | -                 |        |        |        |        |       |       |       |       |        |                     |       |                     |       |       |                     |  |  |  |

|----------|----------------------------------------------------------------|--------|-------------------|--------|--------|--------|--------|-------|-------|-------|-------|--------|---------------------|-------|---------------------|-------|-------|---------------------|--|--|--|

| SFR Name | Addr.                                                          | Bit 15 | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5  | Bit 4               | Bit 3 | Bit 2               | Bit 1 | Bit 0 | Reset State         |  |  |  |

| TMR1     | 0100                                                           |        | Timer 1 Register  |        |        |        |        |       |       |       |       |        | uuuu uuuu uuuu uuuu |       |                     |       |       |                     |  |  |  |

| PR1      | 0102                                                           |        | Period Register 1 |        |        |        |        |       |       |       |       |        |                     |       | 1111 1111 1111 1111 |       |       |                     |  |  |  |

| T1CON    | 0104                                                           | TON    | _                 | TSIDL  | _      | —      | _      | _     | _     | _     | TGATE | TCKPS1 | TCKPS0              | _     | TSYNC               | TCS   | _     | 0000 0000 0000 0000 |  |  |  |

| Legend.  | erend: y - uninitialized bit — - unimplemented bit read as '0' |        |                   |        |        |        |        |       |       |       |       |        |                     |       |                     |       |       |                     |  |  |  |

**Legend:** u = uninitialized bit; — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

**Output Compare Operation During**

When the CPU enters the Sleep mode, all internal

clocks are stopped. Therefore, when the CPU enters the Sleep state, the output compare channel will drive

the pin to the active state that was observed prior to

For example, if the pin was high when the CPU entered the Sleep state, the pin will remain high. Likewise, if the pin was low when the CPU entered the

Sleep state, the pin will remain low. In either case, the

output compare module will resume operation when

When the CPU enters the Idle mode, the output

The output compare channel will operate during the

CPU Idle mode if the OCSIDL bit (OCxCON<13>) is at

logic '0' and the selected time base (Timer2 or Timer3)

is enabled and the TSIDL bit of the selected timer is

compare module can operate with full functionality.

**Output Compare Operation During**

**CPU Sleep Mode**

entering the CPU Sleep state.

**CPU Idle Mode**

the device wakes up.

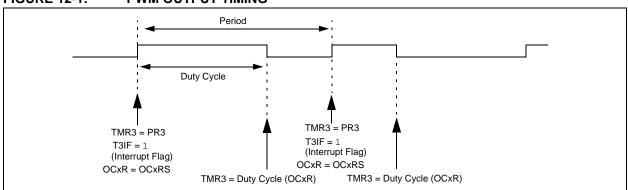

#### 12.4.2 PWM PERIOD

The PWM period is specified by writing to the PRx register. The PWM period can be calculated using Equation 12-1.

#### EQUATION 12-1: PWM PERIOD

$PWM period = [(PRx) + 1] \bullet 4 \bullet TOSC \bullet$ (TMRx prescale value)

PWM frequency is defined as 1/[PWM period].

When the selected TMRx is equal to its respective period register, PRx, the following four events occur on the next increment cycle:

- TMRx is cleared.

- The OCx pin is set.

- Exception 1: If PWM duty cycle is 0x0000, the OCx pin will remain low.

- Exception 2: If duty cycle is greater than PRx, the pin will remain high.

- The PWM duty cycle is latched from OCxRS into OCxR.

- The corresponding timer interrupt flag is set.

See Figure 12-1 for key PWM period comparisons. Timer3 is referred to in the figure for clarity.

12.5

12.6

set to logic '0'.

#### FIGURE 12-1: PWM OUTPUT TIMING

## 12.7 Output Compare Interrupts

The output compare channels have the ability to generate an interrupt on a compare match, for whichever Match mode has been selected.

For all modes except the PWM mode, when a compare event occurs, the respective interrupt flag (OCxIF) is asserted and an interrupt will be generated, if enabled. The OCxIF bit is located in the corresponding IFS status register, and must be cleared in software. The interrupt is enabled via the respective compare interrupt enable (OCxIE) bit, located in the corresponding IEC Control register. For the PWM mode, when an event occurs, the respective timer interrupt flag (T2IF or T3IF) is asserted and an interrupt will be generated, if enabled. The IF bit is located in the IFS0 status register, and must be cleared in software. The interrupt is enabled via the respective timer interrupt enable bit (T2IE or T3IE), located in the IEC0 Control register. The output compare interrupt flag is never set during the PWM mode of operation.

#### TABLE 12-1: OUTPUT COMPARE REGISTER MAP

| SFR Name | Addr. | Bit 15 | Bit 14                           | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7       | Bit 6       | Bit 5 | Bit 4  | Bit 3   | Bit 2               | Bit 1    | Bit 0 | Reset State         |

|----------|-------|--------|----------------------------------|--------|--------|--------|--------|-------|-----------|-------------|-------------|-------|--------|---------|---------------------|----------|-------|---------------------|

| OC1RS    | 0180  |        | Output Compare 1 Master Register |        |        |        |        |       |           |             |             |       |        |         | 0000 0000 0000 0000 |          |       |                     |

| OC1R     | 0182  |        | Output Compare 1 Slave Register  |        |        |        |        |       |           |             |             |       |        |         | 0000 0000 0000 0000 |          |       |                     |

| OC1CON   | 0184  | _      | OCFRZ                            | OCSIDL | _      | _      | —      | _     | _         | _           | _           | _     | OCFLT1 | OCTSEL1 | OCM<2:0>            |          |       | 0000 0000 0000 0000 |

| OC2RS    | 0186  |        |                                  |        |        |        |        | Out   | put Comp  | are 2 Mas   | ter Registe | er    | -      |         |                     |          |       | 0000 0000 0000 0000 |

| OC2R     | 0188  |        |                                  |        |        |        |        | Ou    | tput Comp | oare 2 Slav | /e Registe  | r     | _      |         |                     |          |       | 0000 0000 0000 0000 |

| OC2CON   | 018A  | _      | OCFRZ                            | OCSIDL | _      |        | —      | _     | Ι         | -           | Ι           | _     | OCFLT2 | OCTSEL2 |                     | OCM<2:0> | >     | 0000 0000 0000 0000 |

**Legend:** — = unimplemented bit, read as '0'

Note: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

#### 14.1.4 DOUBLE UPDATE MODE

In the Double Update mode (PTMOD<1:0> = 11), an interrupt event is generated each time the PTMR register is equal to zero, as well as each time a period match occurs. The postscaler selection bits have no effect in this mode of the timer.

The Double Update mode provides two additional functions to the user. First, the control loop bandwidth is doubled because the PWM duty cycles can be updated, twice per period. Second, asymmetrical center-aligned PWM waveforms can be generated, which are useful for minimizing output waveform distortion in certain motor control applications.

Programming a value of 0x0001 in the Note: period register could generate a continuous interrupt pulse, and hence, must be avoided.

#### 14.1.5 PWM TIME BASE PRESCALER

The input clock to PTMR (Fosc/4), has prescaler options of 1:1, 1:4, 1:16 or 1:64, selected by control bits PTCKPS<1:0> in the PTCON SFR. The prescaler counter is cleared when any of the following occurs:

- · a write to the PTMR register

- · a write to the PTCON register

- · any device Reset

The PTMR register is not cleared when PTCON is written.

#### 14.1.6 PWM TIME BASE POSTSCALER

The match output of PTMR can optionally be postscaled through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling).

The postscaler counter is cleared when any of the following occurs:

- · a write to the PTMR register

- · a write to the PTCON register

- · any device Reset

The PTMR register is not cleared when PTCON is written.

#### **PWM Period** 14.2

PTPER is a 15-bit register and is used to set the counting period for the PWM time base. PTPER is a doublebuffered register. The PTPER buffer contents are loaded into the PTPER register at the following instances:

- · Free Running and Single Shot modes: When the PTMR register is reset to zero after a match with the PTPER register.

- Up/Down Counting modes: When the PTMR register is zero.

The value held in the PTPER buffer is automatically loaded into the PTPER register when the PWM time base is disabled (PTEN = 0).

The PWM period can be determined using Equation 14-1:

#### EQUATION 14-1: **PWM PERIOD**

TPWM = TCY • (PTPER + 1) • PTMR Prescale Value

If the PWM time base is configured for one of the Up/ Down Count modes, the PWM period is found using Equation 14-2.

#### EQUATION 14-2: **PWM PERIOD (UP/DOWN** COUNT MODE)

TPWM = TCY • 2 • (PTPER + 1) • PTMR Prescale Value

The maximum resolution (in bits) for a given device oscillator and PWM frequency can be determined using Equation 14-3:

#### EQUATION 14-3: PWM RESOLUTION

log (2 • TPWM/TCY) Resolution =  $\log(2)$

#### 16.8 Slope Control

The I<sup>2</sup>C standard requires slope control on the SDA and SCL signals for Fast Mode (400 kHz). The control bit, DISSLW, enables the user to disable slew rate control, if desired. It is necessary to disable the slew rate control for 1 MHz mode.

#### 16.9 IPMI Support

The control bit IPMIEN enables the module to support Intelligent Peripheral Management Interface (IPMI). When this bit is set, the module accepts and acts upon all addresses.

#### 16.10 General Call Address Support

The general call address can address all devices. When this address is used, all devices should, in theory, respond with an acknowledgement.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all 0s with  $R_W = 0$ .

The general call address is recognized when the General Call Enable (GCEN) bit is set (I2CCON<15> = 1). Following a Start bit detection, 8 bits are shifted into I2CRSR and the address is compared with I2CADD, and is also compared with the general call address which is fixed in hardware.

If a general call address match occurs, the I2CRSR is transferred to the I2CRCV after the eighth clock, the RBF flag is set, and on the falling edge of the ninth bit (ACK bit), the master event interrupt flag (MI2CIF) is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the I2CRCV to determine if the address was device specific, or a general call address.

## 16.11 I<sup>2</sup>C Master Support

As a Master device, six operations are supported.

- Assert a Start condition on SDA and SCL.

- · Assert a Restart condition on SDA and SCL.

- Write to the I2CTRN register initiating transmission of data/address.

- · Generate a Stop condition on SDA and SCL.

- Configure the I<sup>2</sup>C port to receive data.

- Generate an ACK condition at the end of a received byte of data.

## 16.12 I<sup>2</sup>C Master Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the data direction bit. In this case, the data direction bit ( $R_W$ ) is logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an ACK bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the data direction bit. In this case, the data direction bit (R\_W) is logic '1'. Thus, the first byte transmitted is a 7-bit slave address, followed by a '1' to indicate receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an ACK bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

### 16.12.1 I<sup>2</sup>C MASTER TRANSMISSION

Transmission of a data byte, a 7-bit address or the second half of a 10-bit address is accomplished by simply writing a value to I2CTRN register. The user should only write to I2CTRN when the module is in a Wait state. This action will set the buffer full flag (TBF) and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. The Transmit Status Flag, TRSTAT (I2CSTAT<14>), indicates that a master transmit is in progress.

## 16.12.2 I<sup>2</sup>C MASTER RECEPTION

Master mode reception is enabled by programming the receive enable (RCEN) bit (I2CCON<11>). The  $I^2C$  module must be Idle before the RCEN bit is set, otherwise the RCEN bit will be disregarded. The Baud Rate Generator begins counting, and on each rollover, the state of the SCL pin toggles, and data is shifted in to the I2CRSR on the rising edge of each clock.

#### 16.12.3 BAUD RATE GENERATOR

In I<sup>2</sup>C Master mode, the reload value for the BRG is located in the I2CBRG register. When the BRG is loaded with this value, the BRG counts down to '0' and stops until another reload has taken place. If clock arbitration is taking place, for instance, the BRG is reloaded when the SCL pin is sampled high.

As per the I<sup>2</sup>C standard, FSCK may be 100 kHz or 400 kHz. However, the user can specify any baud rate up to 1 MHz. I2CBRG values of '0' or '1' are illegal.

#### EQUATION 16-1: I2CBRG VALUE

$I2CBRG = \left(\frac{FCY}{FSCL} - \frac{FCY}{1, 111, 111}\right) - 1$

#### 17.5.2 FRAMING ERROR (FERR)

The FERR bit (UxSTA<2>) is set if a '0' is detected instead of a Stop bit. If two Stop bits are selected, both Stop bits must be '1', otherwise FERR will be set. The read-only FERR bit is buffered along with the received data. It is cleared on any Reset.

#### 17.5.3 PARITY ERROR (PERR)

The PERR bit (UxSTA<3>) is set if the parity of the received word is incorrect. This error bit is applicable only if a Parity mode (odd or even) is selected. The read-only PERR bit is buffered along with the received data bytes. It is cleared on any Reset.

#### 17.5.4 IDLE STATUS

When the receiver is active (i.e., between the initial detection of the Start bit and the completion of the Stop bit), the RIDLE bit (UxSTA<4>) is '0'. Between the completion of the Stop bit and detection of the next Start bit, the RIDLE bit is '1', indicating that the UART is Idle.

#### 17.5.5 RECEIVE BREAK

The receiver will count and expect a certain number of bit times based on the values programmed in the PDSEL (UxMODE<2:1>) and STSEL (UxMODE<0>) bits.

If the break is longer than 13 bit times, the reception is considered complete after the number of bit times specified by PDSEL and STSEL. The URXDA bit is set, FERR is set, zeros are loaded into the receive FIFO, interrupts are generated, if appropriate, and the RIDLE bit is set.

When the module receives a long break signal and the receiver has detected the Start bit, the data bits and the invalid Stop bit (which sets the FERR), the receiver must wait for a valid Stop bit before looking for the next Start bit. It cannot assume that the break condition on the line is the next Start bit.

Break is regarded as a character containing all '0's, with the FERR bit set. The break character is loaded into the buffer. No further reception can occur until a Stop bit is received. Note that RIDLE goes high when the Stop bit has not been received yet.

#### 17.6 Address Detect Mode

Setting the ADDEN bit (UxSTA<5>) enables this special mode, in which a 9th bit (URX8) value of '1' identifies the received word as an address rather than data. This mode is only applicable for 9-bit data communication. The URXISEL control bit does not have any impact on interrupt generation in this mode, since an interrupt (if enabled) will be generated every time the received word has the 9th bit set.

#### 17.7 Loopback Mode

Setting the LPBACK bit enables this special mode in which the UxTX pin is internally connected to the UxRX pin. When configured for the Loopback mode, the UxRX pin is disconnected from the internal UART receive logic. However, the UxTX pin still functions as in a normal operation.

To select this mode:

- a) Configure UART for desired mode of operation.

- b) Set LPBACK = 1 to enable Loopback mode.

- c) Enable transmission as defined in **Section 17.3** "**Transmitting Data**".

#### 17.8 Baud Rate Generator

The UART has a 16-bit Baud Rate Generator to allow maximum flexibility in baud rate generation. The Baud Rate Generator register (UxBRG) is readable and writable. The baud rate is computed as follows:

- BRG = 16-bit value held in UxBRG register (0 through 65535)

- FCY = Instruction Clock Rate (1/TCY)

The Baud Rate is given by Equation 17-1.

#### EQUATION 17-1: BAUD RATE

Baud Rate = FCY/(16 \* (BRG + 1))

Therefore, maximum baud rate possible is

FCY/16 (if BRG = 0),

and the minimum baud rate possible is

FCY/(16 \* 65536).

With a full 16-bit Baud Rate Generator, at 30 MIPs operation, the minimum baud rate achievable is 28.5 bps.

#### 17.9 Auto Baud Support

To allow the system to determine baud rates of received characters, the input can be optionally linked to a selected capture input. To enable this mode, the user must program the input capture module to detect the falling and rising edges of the Start bit.

#### 18.1 A/D Result Buffer

The module contains a 16-word dual port read-only buffer, called ADCBUF0 through ADCBUFF, to buffer the ADC results. The RAM is 10 bits wide, but is read into different format 16-bit words. The contents of the sixteen ADC conversion result buffer registers, ADCBUF0 through ADCBUFF, cannot be written by user software.

### 18.2 Conversion Operation

After the ADC module has been configured, the sample acquisition is started by setting the SAMP bit. Various sources, such as a programmable bit, timer time-outs and external events, will terminate acquisition and start a conversion. When the A/D conversion is complete, the result is loaded into ADCBUF0...ADCBUFF, and the A/D interrupt flag ADIF and the DONE bit are set after the number of samples specified by the SMPI bit.

The following steps should be followed for doing an A/D conversion:

- 1. Configure the ADC module:

- Configure analog pins, voltage reference and digital I/O

- Select A/D input channels

- Select A/D conversion clock

- Select A/D conversion trigger

- Turn on A/D module

- 2. Configure A/D interrupt (if required):

- Clear ADIF bit

- Select A/D interrupt priority

- 3. Start sampling.

- 4. Wait the required acquisition time.

- 5. Trigger acquisition end, start conversion

- 6. Wait for A/D conversion to complete, by either:

- Waiting for the A/D interrupt

- Waiting for the DONE bit to get set

- 7. Read A/D result buffer, clear ADIF if required.

# 18.3 Selecting the Conversion Sequence

Several groups of control bits select the sequence in which the A/D connects inputs to the sample/hold channels, converts channels, writes the buffer memory, and generates interrupts. The sequence is controlled by the sampling clocks.

The SIMSAM bit controls the acquire/convert sequence for multiple channels. If the SIMSAM bit is '0', the two or four selected channels are acquired and converted sequentially, with two or four sample clocks. If the SIMSAM bit is '1', two or four selected channels are acquired simultaneously, with one sample clock. The channels are then converted sequentially. Obviously, if there is only one channel selected, the SIMSAM bit is not applicable.

The CHPS bits selects how many channels are sampled. This can vary from 1, 2 or 4 channels. If CHPS selects 1 channel, the CH0 channel will be sampled at the sample clock and converted. The result is stored in the buffer. If CHPS selects 2 channels, the CH0 and CH1 channels will be sampled and converted. If CHPS selects 4 channels, the CH0, CH1, CH2 and CH3 channels will be sampled and converted.

The SMPI bits select the number of acquisition/conversion sequences that would be performed before an interrupt occurs. This can vary from 1 sample per interrupt to 16 samples per interrupt.

The user cannot program a combination of CHPS and SMPI bits that specifies more than 16 conversions per interrupt, or 8 conversions per interrupt, depending on the BUFM bit. The BUFM bit, when set, will split the 16-word results buffer (ADCBUF0...ADCBUFF) into two 8-word groups. Writing to the 8-word buffers will be alternated on each interrupt event. Use of the BUFM bit will depend on how much time is available for moving data out of the buffers after the interrupt, as determined by the application.

If the processor can quickly unload a full buffer within the time it takes to acquire and convert one channel, the BUFM bit can be '0' and up to 16 conversions may be done per interrupt. The processor will have one sample and conversion time to move the sixteen conversions.

If the processor cannot unload the buffer within the acquisition and conversion time, the BUFM bit should be '1'. For example, if SMPI<3:0> (ADCON2<5:2>) = 0111, then eight conversions will be loaded into 1/2 of the buffer, following which an interrupt occurs. The next eight conversions will be loaded into the other 1/2 of the buffer. The processor will have the entire time between interrupts to move the eight conversions.

The ALTS bit can be used to alternate the inputs selected during the sampling sequence. The input multiplexer has two sets of sample inputs: MUX A and MUX B. If the ALTS bit is '0', only the MUX A inputs are selected for sampling. If the ALTS bit is '1' and SMPI<3:0> = 0000, on the first sample/convert sequence, the MUX A inputs are selected, and on the next acquire/convert sequence, the MUX B inputs are selected.

The CSCNA bit (ADCON2<10>) will allow the CH0 channel inputs to be alternately scanned across a selected number of analog inputs for the MUX A group. The inputs are selected by the ADCSSL register. If a particular bit in the ADCSSL register is '1', the corresponding input is selected. The inputs are always scanned from lower to higher numbered inputs, starting after each interrupt. If the number of inputs selected is greater than the number of samples taken per interrupt, the higher numbered inputs are unused.

#### 18.4 Programming the Start of Conversion Trigger

The conversion trigger will terminate acquisition and start the requested conversions.

The SSRC<2:0> bits select the source of the conversion trigger.

The SSRC bits provide for up to five alternate sources of conversion trigger.

When SSRC<2:0> = 000, the conversion trigger is under software control. Clearing the SAMP bit will cause the conversion trigger.

When SSRC<2:0> = 111 (Auto-Start mode), the conversion trigger is under A/D clock control. The SAMC bits select the number of A/D clocks between the start of acquisition and the start of conversion. This provides the fastest conversion rates on multiple channels. SAMC must always be at least one clock cycle.

Other trigger sources can come from timer modules, Motor Control PWM module or external interrupts.

Note: To operate the A/D at the maximum specified conversion speed, the Auto Convert Trigger option should be selected (SSRC = 111) and the Auto Sample Time bits should be set to 1 TAD (SAMC = 00001). This configuration will give a total conversion period (sample + convert) of 13 TAD.

The use of any other conversion trigger will result in additional TAD cycles to synchronize the external event to the A/D.

## 18.5 Aborting a Conversion

Clearing the ADON bit during a conversion will abort the current conversion and stop the sampling sequencing. The ADCBUF will not be updated with the partially completed A/D conversion sample. That is, the ADCBUF will continue to contain the value of the last completed conversion (or the last value written to the ADCBUF register).

If the clearing of the ADON bit coincides with an auto start, the clearing has a higher priority.

After the A/D conversion is aborted, a 2 TAD wait is required before the next sampling may be started by setting the SAMP bit.

If sequential sampling is specified, the A/D will continue at the next sample pulse which corresponds with the next channel converted. If simultaneous sampling is specified, the A/D will continue with the next multichannel group conversion sequence.

#### 18.6 Selecting the A/D Conversion Clock

The A/D conversion requires 12 TAD. The source of the A/D conversion clock is software selected using a 6-bit counter. There are 64 possible options for TAD.

#### EQUATION 18-1: A/D CONVERSION CLOCK

TAD = TCY \*

$$(0.5 * (ADCS < 5:0 > + 1))$$

ADCS < 5:0 > = 2  $\frac{TAD}{TCY} - 1$

The internal RC oscillator is selected by setting the ADRC bit.

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 83.33 ns (for VDD = 5V). Refer to **Section 22.0 "Electrical Characteristics"** for minimum TAD under other operating conditions.

Example 18-1 shows a sample calculation for the ADCS<5:0> bits, assuming a device operating speed of 30 MIPS.

## EXAMPLE 18-1: A/D CONVERSION CLOCK CALCULATION

TAD = 84 ns

TCY = 33 ns (30 MIPS)

ADCS<5:0> =

$$2 \cdot \frac{TAD}{TCY} - 1$$

=  $2 \cdot \frac{84 \text{ ns}}{33 \text{ ns}} - 1$

= 4.09

Therefore,

Set ADCS<5:0> = 5

Actual TAD =  $\frac{TCY}{2} \cdot (ADCS<5:0> + 1)$

=  $\frac{33 \text{ ns}}{2} \cdot (5 + 1)$

= 99 ns

#### 18.9 Module Power-Down Modes

The module has three internal power modes. When the ADON bit is '1', the module is in Active mode; it is fully powered and functional. When ADON is '0', the module is in Off mode. The digital and analog portions of the circuit are disabled for maximum current savings. In order to return to the Active mode from Off mode, the user must wait for the ADC circuitry to stabilize.

#### 18.10 A/D Operation During CPU Sleep and Idle Modes

#### 18.10.1 A/D OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shutdown and stay at logic '0'.

If Sleep occurs in the middle of a conversion, the conversion is aborted. The converter will not continue with a partially completed conversion on exit from Sleep mode.

Register contents are not affected by the device entering or leaving Sleep mode.

The A/D module can operate during Sleep mode if the A/D clock source is set to RC (ADRC = 1). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is complete, the DONE bit will be set and the result loaded into the ADCBUF register.

If the A/D interrupt is enabled, the device will wake-up from Sleep. If the A/D interrupt is not enabled, the A/D module will then be turned off, although the ADON bit will remain set.

## 18.10.2 A/D OPERATION DURING CPU IDLE MODE

The ADSIDL bit selects if the module will stop on Idle or continue on Idle. If ADSIDL = 0, the module will continue operation on assertion of Idle mode. If ADSIDL = 1, the module will stop on Idle.

#### 18.11 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off, and any conversion and acquisition sequence is aborted. The values that are in the ADCBUF registers are not modified. The A/D result register will contain unknown data after a Power-on Reset.

#### 18.12 Output Formats

The A/D result is 10 bits wide. The data buffer RAM is also 10 bits wide. The 10-bit data can be read in one of four different formats. The FORM<1:0> bits select the format. Each of the output formats translates to a 16-bit result on the data bus.

Write data will always be in right justified (integer) format.

| RAM Contents:            |         |     |     |     |     | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|--------------------------|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|                          |         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Read to Bus:             |         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Fractional (1.15) | d09 d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   | 0   | 0   |

|                          |         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Fractional (1.15)        | d09 d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   | 0   | 0   |

|                          |         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Integer           | d09 d09 | d09 | d09 | d09 | d09 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                          |         |     |     | -   |     |     |     |     |     |     | -   |     |     | -   |     |

| Integer                  | 0 0     | 0   | 0   | 0   | 0   | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                          |         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

#### FIGURE 18-4: A/D OUTPUT DATA FORMATS

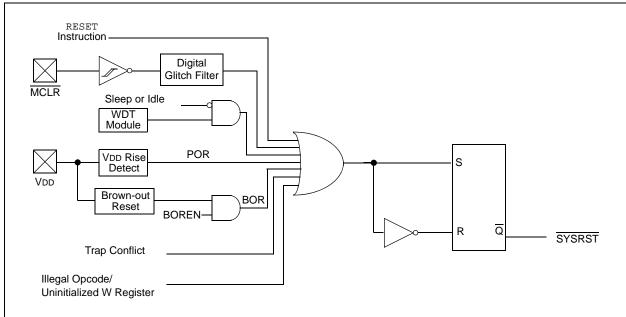

#### 19.3 Reset

The dsPIC30F2010 differentiates between various kinds of Reset:

- Power-on Reset (POR) a)

- MCLR Reset during normal operation b)

- MCLR Reset during Sleep C)

- Watchdog Timer (WDT) Reset (during normal d) operation)

- e) Programmable Brown-out Reset (BOR)

- f) **RESET** Instruction

**FIGURE 19-2:**

- Reset cause by trap lockup (TRAPR) g)

- Reset caused by illegal opcode, or by using an h) uninitialized W register as an Address Pointer (IOPUWR)

Different registers are affected in different ways by various Reset conditions. Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register are set or cleared differently in different Reset situations, as indicated in Table 19-5. These bits are used in software to determine the nature of the Reset.

A block diagram of the on-chip Reset circuit is shown in Figure 19-2.

A MCLR noise filter is provided in the MCLR Reset path. The filter detects and ignores small pulses.

Internally generated Resets do not drive MCLR pin low.

RESET SYSTEM BLOCK DIAGRAM

#### POR: POWER-ON RESET 19.3.1

A power-on event will generate an internal POR pulse when a VDD rise is detected. The Reset pulse will occur at the POR circuit threshold voltage (VPOR), which is nominally 1.85V. The device supply voltage characteristics must meet specified starting voltage and rise rate requirements. The POR pulse will Reset a POR timer and place the device in the Reset state. The POR also selects the device clock source identified by the oscillator configuration fuses.

The POR circuit inserts a small delay, TPOR, which is nominally 10 us and ensures that the device bias circuits are stable. Furthermore, a user selected powerup time-out (TPWRT) is applied. The TPWRT parameter is based on device Configuration bits and can be 0 ms (no delay), 4 ms, 16 ms, or 64 ms. The total delay is at device power-up TPOR + TPWRT. When these delays have expired, SYSRST will be negated on the next leading edge of the Q1 clock, and the PC will jump to the Reset vector.

The timing for the SYSRST signal is shown in Figure 19-3 through Figure 19-5.

### 20.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

The dsPIC30F instruction set adds many enhancements to the previous  $\text{PIC}^{\textcircled{R}}$  MCU instruction sets, while maintaining an easy migration from PIC MCU instruction sets.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode which specifies the instruction type, and one or more operands which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- Control operations

Table 20-1 shows the general symbols used in describing the instructions.

The dsPIC30F instruction set summary in Table 20-2 lists all the instructions along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- The file register specified by the value 'f'

- The destination, which could either be the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value, or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions may use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write-back destination

The other DSP instructions do not involve any multiplication, and may include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift, specified by a W register 'Wn' or a literal value

The control instructions may use some of the following operands:

- A program memory address

- The mode of the table read and table write instructions

All instructions are a single word, except for certain double word instructions, which were made double word instructions so that all the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

#### TABLE 20-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax                 | Description                                       | # of<br>word<br>s | # of<br>cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------|---------------------------------|---------------------------------------------------|-------------------|----------------|--------------------------|

| 34                 | EXCH                 | EXCH   | Wns,Wnd                         | Swap Wns with Wnd                                 | 1                 | 1              | None                     |

| 35                 | FBCL                 | FBCL   | Ws,Wnd                          | Find Bit Change from Left (MSb) Side              | 1                 | 1              | С                        |

| 36                 | FF1L                 | FF1L   | Ws,Wnd                          | Find First One from Left (MSb) Side               | 1                 | 1              | С                        |

| 37                 | FF1R                 | FF1R   | Ws,Wnd                          | Find First One from Right (LSb) Side              | 1                 | 1              | С                        |

| 38                 | GOTO                 | GOTO   | Expr                            | Go to address                                     | 2                 | 2              | None                     |

|                    |                      | GOTO   | Wn                              | Go to indirect                                    | 1                 | 2              | None                     |

| 39                 | INC                  | INC    | f                               | f = f + 1                                         | 1                 | 1              | C,DC,N,OV,Z              |

|                    |                      | INC    | f,WREG                          | WREG = f + 1                                      | 1                 | 1              | C,DC,N,OV,Z              |

|                    |                      | INC    | Ws,Wd                           | Wd = Ws + 1                                       | 1                 | 1              | C,DC,N,OV,Z              |

| 40                 | INC2                 | INC2   | f                               | f = f + 2                                         | 1                 | 1              | C,DC,N,OV,Z              |

|                    |                      | INC2   | f,WREG                          | WREG = f + 2                                      | 1                 | 1              | C,DC,N,OV,Z              |

|                    |                      | INC2   | Ws,Wd                           | Wd = Ws + 2                                       | 1                 | 1              | C,DC,N,OV,Z              |

| 41                 | IOR                  | IOR    | f                               | f = f .IOR. WREG                                  | 1                 | 1              | N,Z                      |

|                    |                      | IOR    | f,WREG                          | WREG = f .IOR. WREG                               | 1                 | 1              | N,Z                      |

|                    |                      | IOR    | #lit10,Wn                       | Wd = lit10 .IOR. Wd                               | 1                 | 1              | N,Z                      |

|                    |                      | IOR    | Wb,Ws,Wd                        | Wd = Wb .IOR. Ws                                  | 1                 | 1              | N,Z                      |

|                    |                      | IOR    | Wb,#lit5,Wd                     | Wd = Wb .IOR. lit5                                | 1                 | 1              | N,Z                      |

| 42                 | LAC                  | LAC    | Wso,#Slit4,Acc                  | Load Accumulator                                  | 1                 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 43                 | LNK                  | LNK    | #lit14                          | Link frame pointer                                | 1                 | 1              | None                     |

| 44                 | LSR                  | LSR    | f                               | f = Logical Right Shift f                         | 1                 | 1              | C,N,OV,Z                 |

|                    |                      | LSR    | f,WREG                          | WREG = Logical Right Shift f                      | 1                 | 1              | C,N,OV,Z                 |

|                    |                      | LSR    | Ws,Wd                           | Wd = Logical Right Shift Ws                       | 1                 | 1              | C,N,OV,Z                 |

|                    |                      | LSR    | Wb,Wns,Wnd                      | Wnd = Logical Right Shift Wb by Wns               | 1                 | 1              | N,Z                      |

|                    |                      | LSR    | Wb,#lit5,Wnd                    | Wnd = Logical Right Shift Wb by lit5              | 1                 | 1              | N,Z                      |

| 45                 | MAC                  | MAC    | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd,<br>AWB | Multiply and Accumulate                           | 1                 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MAC    | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd         | Square and Accumulate                             | 1                 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 46                 | MOV                  | MOV    | f,Wn                            | Move f to Wn                                      | 1                 | 1              | None                     |

|                    |                      | MOV    | f                               | Move f to f                                       | 1                 | 1              | N,Z                      |

|                    |                      | MOV    | f,WREG                          | Move f to WREG                                    | 1                 | 1              | N,Z                      |

|                    |                      | MOV    | #lit16,Wn                       | Move 16-bit literal to Wn                         | 1                 | 1              | None                     |

|                    |                      | MOV.b  | #lit8,Wn                        | Move 8-bit literal to Wn                          | 1                 | 1              | None                     |

|                    |                      | MOV    | Wn,f                            | Move Wn to f                                      | 1                 | 1              | None                     |

|                    |                      | MOV    | Wso,Wdo                         | Move Ws to Wd                                     | 1                 | 1              | None                     |

|                    |                      | MOV    | WREG, f                         | Move WREG to f                                    | 1                 | 1              | N,Z                      |

|                    |                      | MOV.D  | Wns,Wd                          | Move Double from W(ns):W(ns+1) to Wd              | 1                 | 2              | None                     |

|                    |                      | MOV.D  | Ws,Wnd                          | Move Double from Ws to W(nd+1):W(nd)              | 1                 | 2              | None                     |

| 47                 | MOVSAC               | MOVSAC | Acc,Wx,Wxd,Wy,Wyd,AWB           | Prefetch and store accumulator                    | 1                 | 1              | None                     |

| 48                 | MPY                  | MPY    | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd         | Multiply Wm by Wn to Accumulator                  | 1                 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY    | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd         | Square Wm to Accumulator                          | 1                 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 49                 | MPY.N                | MPY.N  | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd         | -(Multiply Wm by Wn) to Accumulator               | 1                 | 1              | None                     |

| 50                 | MSC                  | MSC    | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd,<br>AWB | Multiply and Subtract from Accumulator            | 1                 | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 51                 | MUL                  | MUL.SS | Wb,Ws,Wnd                       | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)          | 1                 | 1              | None                     |

|                    |                      | MUL.SU | Wb,Ws,Wnd                       | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(Ws)     | 1                 | 1              | None                     |

|                    |                      | MUL.US | Wb,Ws,Wnd                       | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)        | 1                 | 1              | None                     |

|                    |                      | MUL.UU | Wb,Ws,Wnd                       | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1                 | 1              | None                     |

|                    |                      | MUL.SU | Wb,#lit5,Wnd                    | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(lit5)   | 1                 | 1              | None                     |

|                    |                      | MUL.UU | Wb,#lit5,Wnd                    | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5) | 1                 | 1              | None                     |

|                    |                      | MUL    | f                               | W3:W2 = f * WREG                                  | 1                 | 1              | None                     |

| Instruction Addressing Modes                   |

|------------------------------------------------|

| File Register Instructions                     |

| Fundamental Modes Supported                    |

| MAC Instructions                               |

| MCU Instructions                               |

| Move and Accumulator Instructions              |

| Other Instructions                             |

| Instruction Set                                |

| Inter-Integrated Circuit. See I <sup>2</sup> C |

| Internal Clock Timing Examples 159             |

| Internet Address                               |

| Interrupt Controller                           |

| Register Map 42                                |

| Interrupt Priority                             |

| Traps                                          |

| Interrupt Sequence                             |

| Interrupt Stack Frame 41                       |

| Interrupts                                     |

|                                                |

#### L

| Load Conditions | 15 | 6 | j |

|-----------------|----|---|---|

|                 |    |   |   |

## Μ

| Memory Organization                                  | 19 |

|------------------------------------------------------|----|

| Microchip Internet Web Site                          | 99 |

| Modulo Addressing                                    | 33 |

| Applicability                                        | 35 |

| Operation Example                                    | 34 |

| Start and End Address                                | 33 |

| W Address Register Selection                         | 33 |

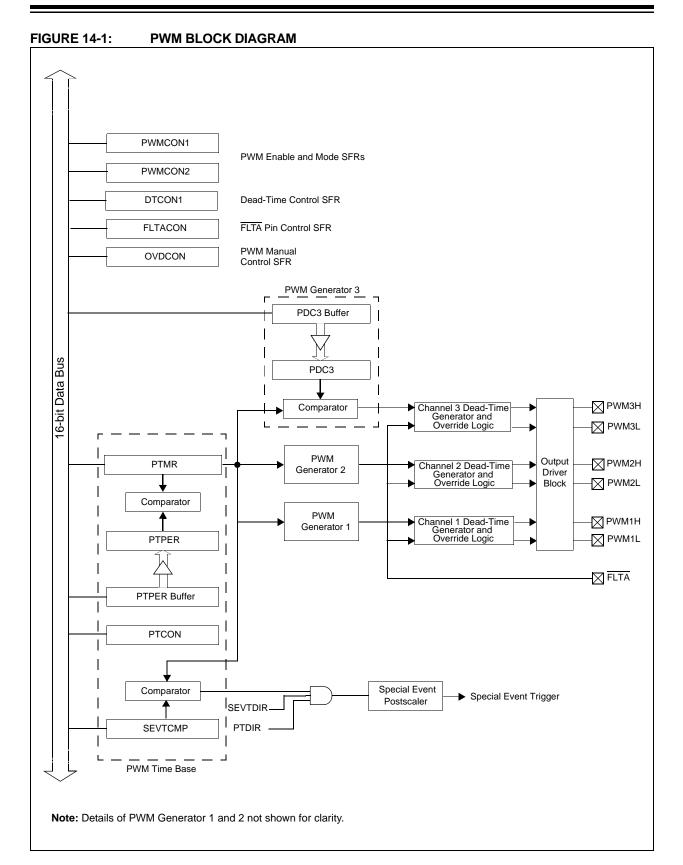

| Motor Control PWM Module                             | 81 |

| Fault Timing Characteristics16                       | 68 |

| Timing Characteristics16                             | 68 |

| Timing Requirements16                                | 68 |

| MPLAB ASM30 Assembler, Linker, Librarian14           | 44 |

| MPLAB Integrated Development Environment Software 14 | 43 |

| MPLAB PM3 Device Programmer14                        | 46 |

| MPLAB REAL ICE In-Circuit Emulator System            | 45 |

| MPLINK Object Linker/MPLIB Object Librarian14        | 44 |

### 0

| OC/PWM Module Timing Characteristics |      |

|--------------------------------------|------|

| Operating Current (IDD)              | 150  |

| Operating MIPS vs Voltage            |      |

| dsPIC30F2010                         | 148  |

| Oscillator                           |      |

| Configurations                       |      |

| Fast RC (FRC)                        |      |

| Low Power RC (LPRC)                  | 125  |

| Phase Locked Loop (PLL)              | 125  |

| Oscillator Configurations            |      |

| Fail-Safe Clock Monitor              | 126  |

| Initial Clock Source Selection       | 124  |

| LP Oscillator Control                | 125  |

| Start-up Timer (OST)                 | 124  |

| Oscillator Operating Modes Table     | 122  |

| Oscillator Selection                 |      |

| Oscillator Start-up Timer            |      |

| Timing Characteristics               | 161  |

| Timing Requirements                  | 161  |

| Output Compare Interrupts            | . 73 |

| Output Compare Mode                  |      |

| Register Map                         | . 74 |

| Output Compare Module                | . 71 |

| Timing Characteristics               |      |

| Timing Requirements                  | 166  |

|                                      |      |

| Output Compare Operation During CPU Idle Mode<br>Output Compare Sleep Mode Operation |      |

|--------------------------------------------------------------------------------------|------|

| P                                                                                    |      |

| Packaging Information                                                                |      |

| Marking                                                                              |      |

| Pinout Descriptions                                                                  | 9    |

| PLL Clock Timing Specifications                                                      | 158  |

| POR. See Power-on Reset                                                              |      |

| Port Register Map                                                                    | . 55 |

| Port Write/Read Example                                                              |      |

| PORTB                                                                                |      |

| Register Map                                                                         | . 55 |

| PORTC                                                                                |      |

| Register Map                                                                         | . 55 |

| PORTD                                                                                |      |

| Register Map                                                                         | 55   |

| PORTE                                                                                | . 00 |

| Register Map                                                                         | 55   |

| PORTF                                                                                | . 55 |

|                                                                                      |      |

| Register Map                                                                         | . 55 |

| Position Measurement Mode                                                            |      |