Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | HC08                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | LINbus, SCI, SPI                                                         |

| Peripherals                | LVD, POR, PWM                                                            |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-LQFP                                                                  |

| Supplier Device Package    | 48-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908gr16cfa |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **General Description**

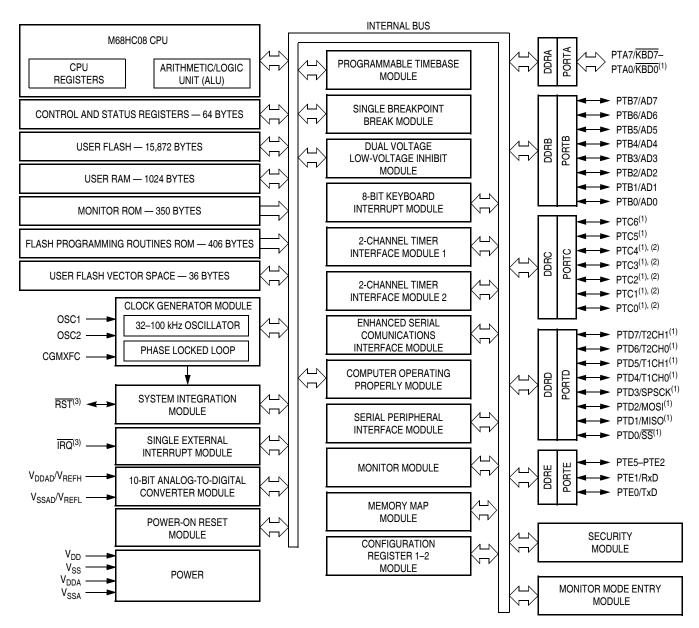

- 1. Ports are software configurable with pullup device if input port.

- 2. Higher current drive port pins

- 3. Pin contains integrated pullup device

Figure 1-1. MCU Block Diagram

#### Memory

| Addr.  | Register Name                                     |                 | Bit 7 | 6       | 5       | 4       | 3                   | 2       | 1                | Bit 0   |

|--------|---------------------------------------------------|-----------------|-------|---------|---------|---------|---------------------|---------|------------------|---------|

|        | Configuration Register 2                          | Read:           | 0     | 0       | 0       | 0       | R                   | TMBCLK- | OSCENIN-<br>STOP | ESCIBD- |

| \$001E | (CONFIG2) <sup>(1)</sup><br>See page 80.          | Write:          |       |         |         |         | ••                  | SEL     |                  | SRC     |

|        | oos page co.                                      | Reset:          | 0     | 0       | 0       | 0       | 0                   | 0       | 0                | 1       |

| \$001F | Configuration Register 1 (CONFIG1) <sup>(1)</sup> | Read:<br>Write: | COPRS | LVISTOP | LVIRSTD | LVIPWRD | LVI5OR3<br>(Note 1) | SSREC   | STOP             | COPD    |

|        | See page 80.                                      | Reset:          | 0     | 0       | 0       | 0       | 0                   | 0       | 0                | 0       |

<sup>1.</sup> One-time writable register after each reset, except LVI5OR3 bit. LVI5OR3 bit is only reset via POR (power-on reset).

|                    | Timer 1 Status and Control   | Read:  | TOF     | TOIE       | TSTOP | 0           | 0              | PS2     | PS1     | PS0        |

|--------------------|------------------------------|--------|---------|------------|-------|-------------|----------------|---------|---------|------------|

| \$0020             | Register (T1SC)              | Write: | 0       | TOIL       | 10101 | TRST        |                | 1 02    | 5       | 1 00       |

|                    | See page 231.                | Reset: | 0       | 0          | 1     | 0           | 0              | 0       | 0       | 0          |

|                    | Timer 1 Counter              | Read:  | Bit 15  | 14         | 13    | 12          | 11             | 10      | 9       | Bit 8      |

| \$0021             | Register High (T1CNTH)       | Write: |         |            |       |             |                |         |         |            |

| See page 232.      |                              | Reset: | 0       | 0          | 0     | 0           | 0              | 0       | 0       | 0          |

|                    | Timer 1 Counter              | Read:  | Bit 7   | 6          | 5     | 4           | 3              | 2       | 1       | Bit 0      |

| \$0022             | Register Low (T1CNTL)        | Write: |         |            |       |             |                |         |         |            |

|                    | See page 232.                | Reset: | 0       | 0          | 0     | 0           | 0              | 0       | 0       | 0          |

| Timer 1 Counter Mo | Timer 1 Counter Modulo       | Read:  | Bit 15  | 14         | 13    | 12          | 11             | 10      | 9       | Bit 8      |

| \$0023             | Register High (T1MODH)       | Write: | מני זום | 17         | 10    | 12          | 11             | 10      | ,       | Dit o      |

| See page 233.      |                              | Reset: | 1       | 1          | 1     | 1           | 1              | 1       | 1       | 1          |

|                    | Timer 1 Counter Modulo       | Read:  | Bit 7   | 6          | 5     | 4           | 3              | 2       | 1       | Bit 0      |

| \$0024             | Register Low (T1MODL)        | Write: | Dit 7   | Ů          | Ŭ     | -           | ŭ              | _       | '       | Dit 0      |

|                    | See page 233.                | Reset: | 1       | 1          | 1     | 1           | 1              | 1       | 1       | 11         |

|                    | Timer 1 Channel 0 Status and | Read:  | CH0F    | CH0IE      | MS0B  | MS0A        | ELS0B          | ELS0A   | TOV0    | CH0MAX     |

| \$0025             | Control Register (T1SC0)     | Write: | 0       | OHOLE      | MICOD | MOOA        | LLOOD          | LLOOM   | 1010    | OT TOWN DX |

|                    | See page 233.                | Reset: | 0       | 0          | 0     | 0           | 0              | 0       | 0       | 0          |

|                    | Timer 1 Channel 0            | Read:  | Bit 15  | 14         | 13    | 12          | 11             | 10      | 9       | Bit 8      |

| \$0026             | Register High (T1CH0H)       | Write: | Dit 10  |            |       |             |                | .0      | Ū       | Dit 0      |

|                    | See page 236.                | Reset: |         |            |       | Indetermina | te after reset |         |         |            |

|                    | Timer 1 Channel 0            | Read:  | Bit 7   | 6          | 5     | 4           | 3              | 2       | 1       | Bit 0      |

| \$0027             | Register Low (T1CH0L)        | Write: | Dit 7   | Ů          | Ŭ     | 7           | Ü              | _       | '       | Dit 0      |

|                    | See page 236.                | Reset: |         |            |       | Indetermina | te after reset |         |         |            |

|                    | Timer 1 Channel 1 Status and | Read:  | CH1F    | CH1IE      | 0     | MS1A        | ELS1B          | ELS1A   | TOV1    | CH1MAX     |

| \$0028             | Control Register (T1SC1)     | Write: | 0       | OITTIL     |       | IVIOTA      | LLSID          | LLOTA   | 1011    | OTTIWIAX   |

|                    | See page 234.                | Reset: | 0       | 0          | 0     | 0           | 0              | 0       | 0       | 0          |

|                    |                              |        |         | -          |       |             | ·              |         |         |            |

|                    |                              |        |         | = Unimplem | ented | R           | = Reserved     | U = Una | ffected |            |

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 8)

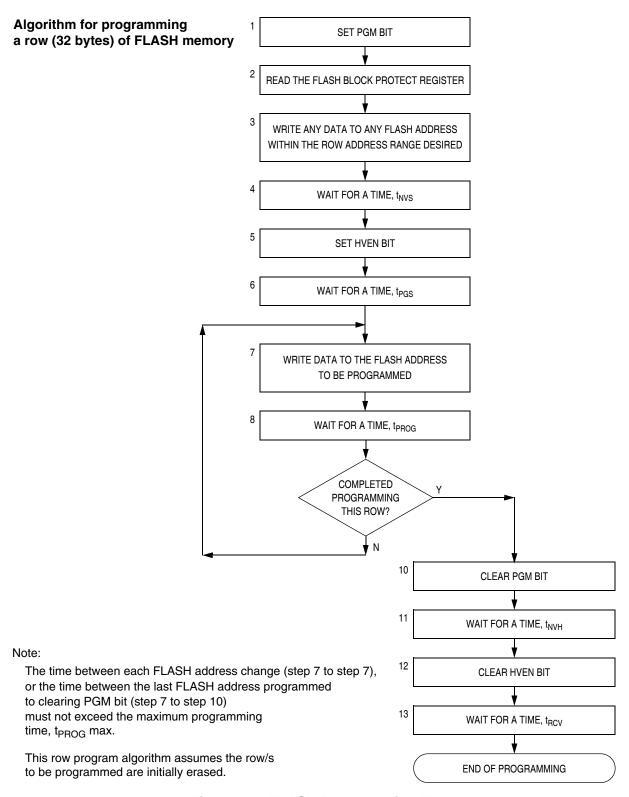

Figure 2-4. FLASH Programming Flowchart

MC68HC908GR16 Data Sheet, Rev. 5.0

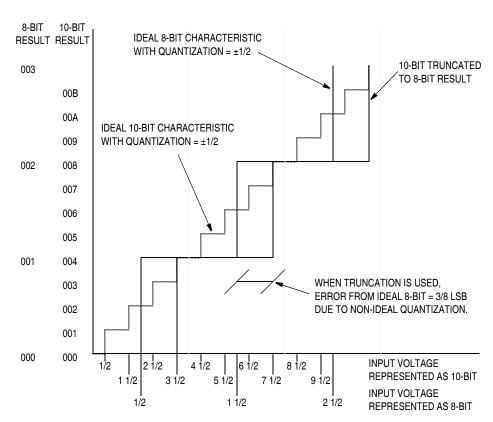

is used when compatibility with 8-bit ADC designs are required. No interlocking between ADRH and ADRL is present.

#### NOTE

Quantization error is affected when only the most significant eight bits are used as a result. See Figure 3-3.

Figure 3-3. Bit Truncation Mode Error

# 3.4 Monotonicity

The conversion process is monotonic and has no missing codes.

# 3.5 Interrupts

When the AIEN bit is set, the ADC module is capable of generating CPU interrupts after each ADC conversion. A CPU interrupt is generated if the COCO bit is a 0. The COCO bit is not used as a conversion complete flag when interrupts are enabled.

## 3.6 Low-Power Modes

The WAIT and STOP instruction can put the MCU in low power-consumption standby modes.

**Analog-to-Digital Converter (ADC)**

## **Central Processor Unit (CPU)**

Table 7-1. Instruction Set Summary (Sheet 3 of 6)

| Source                                                                                         | Operation                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |   | Effect on CCR |          |          |   | Address<br>Mode                                     | Opcode                                           | Operand                                         | es                                   |

|------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---------------|----------|----------|---|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                           | Operation                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ٧ | Н | I             | N        | Z        | С | Add                                                 | obc                                              | Ope                                             | Cycles                               |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR,X<br>CLR opr,SP                            | Clear                            | M ← \$00<br>A ← \$00<br>X ← \$00<br>H ← \$00<br>M ← \$00<br>M ← \$00<br>M ← \$00                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 | _ | _             | 0        | 1        | _ | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1        | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F         | dd<br>ff                                        | 3 1 1 1 3 2 4                        |

| CMP #opr<br>CMP opr<br>CMP opr<br>CMP opr,X<br>CMP opr,X<br>CMP,X<br>CMP opr,SP<br>CMP opr,SP  | Compare A with M                 | (A) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Î | _ | _             | ţ        | ‡        | t | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A1<br>B1<br>C1<br>D1<br>E1<br>F1<br>9EE1<br>9ED1 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2 3 4 4 3 2 4 5                      |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                   | Complement (One's Complement)    | $\begin{array}{l} M \leftarrow (\overline{M}) = \$FF - (M) \\ A \leftarrow (\overline{A}) = \$FF - (M) \\ X \leftarrow (\overline{X}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \end{array}$                                                                                                                                                                                      | 0 | _ | ı             | 1        | ‡        | 1 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33<br>43<br>53<br>63<br>73<br>9E63               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| CPHX #opr<br>CPHX opr                                                                          | Compare H:X with M               | (H:X) – (M:M + 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 | - | 1             | ‡        | 1        | ‡ | IMM<br>DIR                                          | 65<br>75                                         | ii ii+1<br>dd                                   | 3                                    |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP  | Compare X with M                 | (X) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | î | _ |               | 1        | 1        | ‡ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff          | 23443245                             |

| DAA                                                                                            | Decimal Adjust A                 | (A) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U | - | _             | 1        | 1        | 1 | INH                                                 | 72                                               |                                                 | 2                                    |

| DBNZ opr,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ opr,X,rel<br>DBNZ X,rel<br>DBNZ opr,SP,rel      | Decrement and Branch if Not Zero | $\begin{array}{l} A \leftarrow (A) - 1 \text{ or } M \leftarrow (M) - 1 \text{ or } X \leftarrow (X) - 1 \\ PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0 \\ PC \leftarrow (PC) + 4 + rel? \text{ (result)} \neq 0 \end{array}$ | _ | _ | -             | _        | -        | _ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B               | dd rr<br>rr<br>rr<br>ff rr<br>rr<br>ff rr       | 533546                               |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                   | Decrement                        | $\begin{array}{c} M \leftarrow (M) - 1 \\ A \leftarrow (A) - 1 \\ X \leftarrow (X) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                          | 1 | - | -             | <b>‡</b> | <b>‡</b> | - | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| DIV                                                                                            | Divide                           | $A \leftarrow (H:A)/(X)$<br>$H \leftarrow Remainder$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - | - | _             | -        | ‡        | ‡ | INH                                                 | 52                                               |                                                 | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr,<br>EOR opr,X<br>EOR opr,X<br>EOR,X<br>EOR opr,SP<br>EOR opr,SP | Exclusive OR M with A            | $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0 | _ | -             | ‡        | <b>‡</b> | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                   | Increment                        | $\begin{array}{c} M \leftarrow (M) + 1 \\ A \leftarrow (A) + 1 \\ X \leftarrow (X) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                          | 1 | _ | - 1           | 1        | <b>‡</b> | _ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

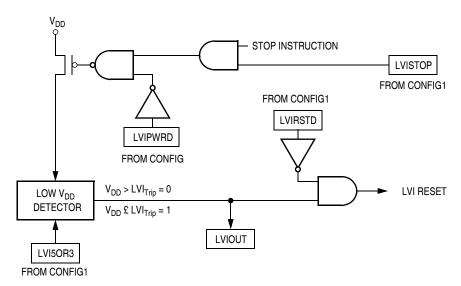

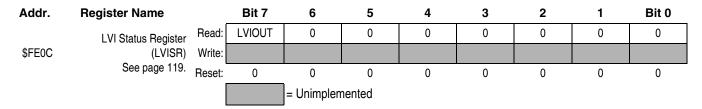

#### Low-Voltage Inhibit (LVI)

LVISTOP, LVIPWRD, LVI5OR3, and LVIRSTD are in the configuration register (CONFIG1). See Figure 5-2. Configuration Register 1 (CONFIG1) for details of the LVI's configuration bits. Once an LVI reset occurs, the MCU remains in reset until V<sub>DD</sub> rises above a voltage, V<sub>TRIPR</sub>, which causes the MCU to exit reset. See 15.3.2.5 Low-Voltage Inhibit (LVI) Reset for details of the interaction between the SIM and the LVI. The output of the comparator controls the state of the LVIOUT flag in the LVI status register (LVISR).

An LVI reset also drives the RST pin low to provide low-voltage protection to external peripheral devices.

Figure 11-1. LVI Module Block Diagram

Figure 11-2. LVI I/O Register Summary

## 11.3.1 Polled LVI Operation

In applications that can operate at  $V_{DD}$  levels below the  $V_{TRIPF}$  level, software can monitor  $V_{DD}$  by polling the LVIOUT bit. In the configuration register, the LVIPWRD bit must be at 0 to enable the LVI module, and the LVIRSTD bit must be at 1 to disable LVI resets.

## 11.3.2 Forced Reset Operation

In applications that require  $V_{DD}$  to remain above the  $V_{TRIPF}$  level, enabling LVI resets allows the LVI module to reset the MCU when  $V_{DD}$  falls below the  $V_{TRIPF}$  level. In the configuration register, the LVIPWRD and LVIRSTD bits must be at 0 to enable the LVI module and to enable LVI resets.

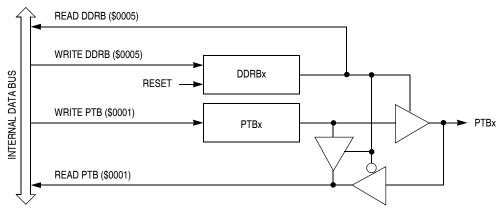

## DDRB7-DDRB0 — Data Direction Register B Bits

These read/write bits control port B data direction. Reset clears DDRB7–DDRB0, configuring all port B pins as inputs.

- 1 = Corresponding port B pin configured as output

- 0 = Corresponding port B pin configured as input

#### NOTE

Avoid glitches on port B pins by writing to the port B data register before changing data direction register B bits from 0 to 1.

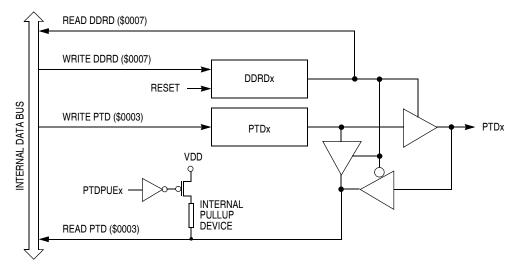

Figure 12-8 shows the port B I/O logic.

Figure 12-8. Port B I/O Circuit

When bit DDRBx is a 1, reading address \$0001 reads the PTBx data latch. When bit DDRBx is a 0, reading address \$0001 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 12-3 summarizes the operation of the port B pins.

| DDRB | PTB                                         | I/O Pin | Accesses to DDRB Accesses to P |           | ses to PTB               |  |

|------|---------------------------------------------|---------|--------------------------------|-----------|--------------------------|--|

| Bit  | Bit                                         | Mode    | Read/Write                     | Read      | Write                    |  |

| 0    | X <sup>(1)</sup> Input, Hi-Z <sup>(2)</sup> |         | DDRB7-DDRB0                    | Pin       | PTB7-PTB0 <sup>(3)</sup> |  |

| 1    | Χ                                           | Output  | DDRB7-DDRB0                    | PTB7-PTB0 | PTB7-PTB0                |  |

**Table 12-3. Port B Pin Functions**

- 1. X = Don't care

- 2. Hi-Z = High impedance

- 3. Writing affects data register, but does not affect input.

Data direction register D (DDRD) does not affect the data direction of port D pins that are being used by the SPI module. However, the DDRD bits always determine whether reading port D returns the states of the latches or the states of the pins. See Table 12-5.

#### SS — Slave Select

The PTD0/SS pin is the slave select input of the SPI module. When the SPE bit is clear, or when the SPI master bit, SPMSTR, is set, the PTD0/SS pin is available for general-purpose I/O. When the SPI is enabled, the DDRB0 bit in data direction register B (DDRB) has no effect on the PTD0/SS pin.

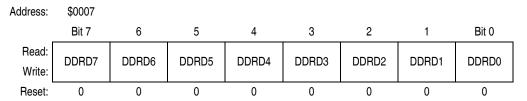

## 12.5.2 Data Direction Register D

Data direction register D (DDRD) determines whether each port D pin is an input or an output. Writing a 1 to a DDRD bit enables the output buffer for the corresponding port D pin; a 0 disables the output buffer.

Figure 12-14. Data Direction Register D (DDRD)

## DDRD7-DDRD0 — Data Direction Register D Bits

These read/write bits control port D data direction. Reset clears DDRD7–DDRD0, configuring all port D pins as inputs.

- 1 = Corresponding port D pin configured as output

- 0 = Corresponding port D pin configured as input

#### NOTE

Avoid glitches on port D pins by writing to the port D data register before changing data direction register D bits from 0 to 1.

Figure 12-15 shows the port D I/O logic.

Figure 12-15. Port D I/O Circuit

MC68HC908GR16 Data Sheet, Rev. 5.0

# **Chapter 13 Resets and Interrupts**

## 13.1 Introduction

Resets and interrupts are responses to exceptional events during program execution. A reset re-initializes the microcontroller (MCU) to its startup condition. An interrupt vectors the program counter to a service routine.

#### 13.2 Resets

A reset immediately returns the MCU to a known startup condition and begins program execution from a user-defined memory location.

#### 13.2.1 Effects

#### A reset:

- Immediately stops the operation of the instruction being executed

- · Initializes certain control and status bits

- Loads the program counter with a user-defined reset vector address from locations \$FFFE and \$FFFF, \$FEFE and \$FEFF in monitor mode

- Selects CGMXCLK divided by four as the bus clock

#### 13.2.2 External Reset

A 0 applied to the  $\overline{\text{RST}}$  pin for a time,  $t_{\text{RL}}$ , generates an external reset. An external reset sets the PIN bit in the system integration module (SIM) reset status register.

#### 13.2.3 Internal Reset

#### Sources:

- Power-on reset (POR)

- Computer operating properly (COP)

- Low-power reset circuits

- Illegal opcode

- Illegal address

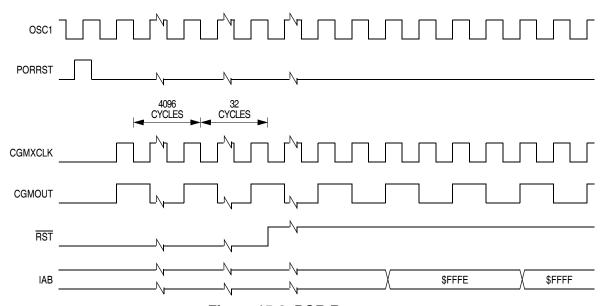

All internal reset sources pull the  $\overline{RST}$  pin low for 32 CGMXCLK cycles to allow resetting of external devices. The MCU is held in reset for an additional 32 CGMXCLK cycles after releasing the  $\overline{RST}$  pin.

#### 13.2.3.1 Power-On Reset (POR)

A power-on reset (POR) is an internal reset caused by a positive transition on the  $V_{DD}$  pin.  $V_{DD}$  at the POR must go below  $V_{POR}$  to reset the MCU. This distinguishes between a reset and a POR. The POR is not a brown-out detector, low-voltage detector, or glitch detector.

MC68HC908GR16 Data Sheet, Rev. 5.0

## **Enhanced Serial Communications Interface (ESCI) Module**

The baud rate clock source for the ESCI can be selected via the configuration bit, ESCIBDSRC, of the CONFIG2 register (\$001E).

For reference, a summary of the ESCI module input/output registers is provided in Figure 14-3.

| Addr.  | Register Name                                      |                 | Bit 7 | 6               | 5     | 4         | 3          | 2     | 1      | Bit 0 |

|--------|----------------------------------------------------|-----------------|-------|-----------------|-------|-----------|------------|-------|--------|-------|

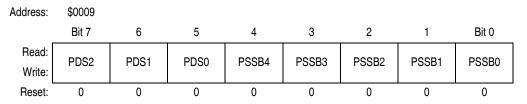

| \$0009 | ESCI Prescaler Register (SCPSC)                    | Read:<br>Write: | PDS2  | PDS1            | PDS0  | PSSB4     | PSSB3      | PSSB2 | PSSB1  | PSSB0 |

|        | See page 170.                                      |                 | 0     | 0               | 0     | 0         | 0          | 0     | 0      | 0     |

| \$000A | ESCI Arbiter Control<br>Register (SCIACTL)         | Read:<br>Write: | AM1   | ALOST           | - AMO | ACLK      | AFIN       | ARUN  | AROVFL | ARD8  |

|        | See page 174.                                      | Reset:          | 0     | 0               | 0     | 0         | 0          | 0     | 0      | 0     |

|        | ESCI Arbiter Data                                  | Read:           | ARD7  | ARD6            | ARD5  | ARD4      | ARD3       | ARD2  | ARD1   | ARD0  |

| \$000B | Register (SCIADAT)                                 | Write:          |       |                 |       |           |            |       |        |       |

|        | See page 175.                                      | Reset:          | 0     | 0               | 0     | 0         | 0          | 0     | 0      | 0     |

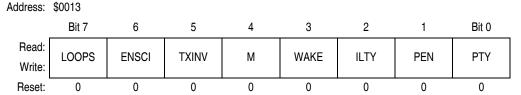

| \$0013 | ESCI Control Register 1<br>(SCC1)                  | Read:<br>Write: | LOOPS | ENSCI           | TXINV | М         | WAKE       | ILTY  | PEN    | PTY   |

|        | See page 161.                                      | Reset:          | 0     | 0               | 0     | 0         | 0          | 0     | 0      | 0     |

| \$0014 | ESCI Control Register 2<br>(SCC2)                  | Read:<br>Write: | SCTIE | TCIE            | SCRIE | ILIE      | TE         | RE    | RWU    | SBK   |

|        | See page 163.                                      | Reset:          | 0     | 0               | 0     | 0         | 0          | 0     | 0      | 0     |

| \$0015 | ESCI Control Register 3<br>(SCC3)<br>See page 164. | Read:<br>Write: | R8    | Т8              | R     | R         | ORIE       | NEIE  | FEIE   | PEIE  |

|        |                                                    | Reset:          | U     | 0               | 0     | 0         | 0          | 0     | 0      | 0     |

|        | ESCI Status Register 1                             | Read:           | SCTE  | TC              | SCRF  | IDLE      | OR         | NF    | FE     | PE    |

| \$0016 | (SCS1)                                             | Write:          |       |                 |       |           |            |       |        |       |

|        | See page 165.                                      | Reset:          | 1     | 1               | 0     | 0         | 0          | 0     | 0      | 0     |

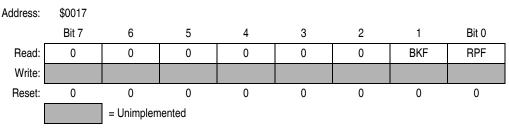

|        | ESCI Status Register 2                             | Read:           | 0     | 0               | 0     | 0         | 0          | 0     | BKF    | RPF   |

| \$0017 | (SCS2)                                             | Write:          |       |                 |       |           |            |       |        |       |

|        | See page 168.                                      | Reset:          | 0     | 0               | 0     | 0         | 0          | 0     | 0      | 0     |

|        | ESCI Data Register                                 | Read:           | R7    | R6              | R5    | R4        | R3         | R2    | R1     | R0    |

| \$0018 | (SCDR)                                             | Write:          | T7    | T6              | T5    | T4        | T3         | T2    | T1     | T0    |

|        | See page 168.                                      | Reset:          |       |                 |       | Unaffecte | d by reset |       |        |       |

| \$0019 | ESCI Baud Rate Register<br>(SCBR)                  | Read:<br>Write: | LINT  | LINR            | SCP1  | SCP0      | R          | SCR2  | SCR1   | SCR0  |

|        | See page 169.                                      | Reset:          | 0     | 0               | 0     | 0<br>R    | 0          | 0     | 0      | 0     |

|        |                                                    |                 |       | = Unimplemented |       |           | = Reserved |       |        |       |

Figure 14-3. ESCI I/O Register Summary

## 14.4.1 Data Format

The SCI uses the standard non-return-to-zero mark/space data format illustrated in Figure 14-4.

MC68HC908GR16 Data Sheet, Rev. 5.0

- ESCI prescaler register, SCPSC

- ESCI arbiter control register, SCIACTL

- ESCI arbiter data register, SCIADAT

## 14.8.1 ESCI Control Register 1

ESCI control register 1 (SCC1):

- Enables loop mode operation

- Enables the ESCI

- Controls output polarity

- · Controls character length

- · Controls ESCI wakeup method

- Controls idle character detection

- Enables parity function

- Controls parity type

Figure 14-10. ESCI Control Register 1 (SCC1)

#### LOOPS — Loop Mode Select Bit

This read/write bit enables loop mode operation. In loop mode the RxD pin is disconnected from the ESCI, and the transmitter output goes into the receiver input. Both the transmitter and the receiver must be enabled to use loop mode. Reset clears the LOOPS bit.

- 1 = Loop mode enabled

- 0 = Normal operation enabled

#### **ENSCI** — Enable ESCI Bit

This read/write bit enables the ESCI and the ESCI baud rate generator. Clearing ENSCI sets the SCTE and TC bits in ESCI status register 1 and disables transmitter interrupts. Reset clears the ENSCI bit.

- 1 = ESCI enabled

- 0 = ESCI disabled

#### TXINV — Transmit Inversion Bit

This read/write bit reverses the polarity of transmitted data. Reset clears the TXINV bit.

- 1 = Transmitter output inverted

- 0 = Transmitter output not inverted

#### NOTE

Setting the TXINV bit inverts all transmitted values including idle, break, start, and stop bits.

## M — Mode (Character Length) Bit

This read/write bit determines whether ESCI characters are eight or nine bits long (See Table 14-5). The ninth bit can serve as a receiver wakeup signal or as a parity bit. Reset clears the M bit.

- 1 = 9-bit ESCI characters

- 0 = 8-bit ESCI characters

MC68HC908GR16 Data Sheet, Rev. 5.0

**Enhanced Serial Communications Interface (ESCI) Module**

## 14.8.5 ESCI Status Register 2

ESCI status register 2 (SCS2) contains flags to signal these conditions:

- · Break character detected

- Incoming data

Figure 14-15. ESCI Status Register 2 (SCS2)

## **BKF** — Break Flag Bit

This clearable, read-only bit is set when the ESCI detects a break character on the RxD pin. In SCS1, the FE and SCRF bits are also set. In 9-bit character transmissions, the R8 bit in SCC3 is cleared. BKF does not generate a CPU interrupt request. Clear BKF by reading SCS2 with BKF set and then reading the SCDR. Once cleared, BKF can become set again only after 1s again appear on the RxD pin followed by another break character. Reset clears the BKF bit.

- 1 = Break character detected

- 0 = No break character detected

## RPF — Reception in Progress Flag Bit

This read-only bit is set when the receiver detects a 0 during the RT1 time period of the start bit search. RPF does not generate an interrupt request. RPF is reset after the receiver detects false start bits (usually from noise or a baud rate mismatch), or when the receiver detects an idle character. Polling RPF before disabling the ESCI module or entering stop mode can show whether a reception is in progress.

- 1 = Reception in progress

- 0 = No reception in progress

## 14.8.6 ESCI Data Register

The ESCI data register (SCDR) is the buffer between the internal data bus and the receive and transmit shift registers. Reset has no effect on data in the ESCI data register.

| Address: | \$0018 |    |    |           |            |    |    |       |

|----------|--------|----|----|-----------|------------|----|----|-------|

|          | Bit 7  | 6  | 5  | 4         | 3          | 2  | 1  | Bit 0 |

| Read:    | R7     | R6 | R5 | R4        | R3         | R2 | R1 | R0    |

| Write:   | T7     | T6 | T5 | T4        | T3         | T2 | T1 | T0    |

| Reset:   |        |    |    | Unaffecte | d by reset |    |    |       |

Figure 14-16. ESCI Data Register (SCDR)

#### R7/T7:R0/T0 — Receive/Transmit Data Bits

Reading address \$0018 accesses the read-only received data bits, R7:R0. Writing to address \$0018 writes the data to be transmitted, T7:T0. Reset has no effect on the ESCI data register.

#### NOTE

Do not use read-modify-write instructions on the ESCI data register.

MC68HC908GR16 Data Sheet, Rev. 5.0

**Enhanced Serial Communications Interface (ESCI) Module**

## SCP1 and SCP0 — ESCI Baud Rate Register Prescaler Bits

These read/write bits select the baud rate register prescaler divisor as shown in Table 14-7. Reset clears SCP1 and SCP0.

**Table 14-7. ESCI Baud Rate Prescaling**

| SCP[1:0] | Baud Rate Register<br>Prescaler Divisor (BPD) |

|----------|-----------------------------------------------|

| 0 0      | 1                                             |

| 0 1      | 3                                             |

| 1 0      | 4                                             |

| 1 1      | 13                                            |

#### SCR2-SCR0 — ESCI Baud Rate Select Bits

These read/write bits select the ESCI baud rate divisor as shown in Table 14-8. Reset clears SCR2–SCR0.

**Table 14-8. ESCI Baud Rate Selection**

| SCR[2:1:0] | Baud Rate Divisor (BD) |

|------------|------------------------|

| 0 0 0      | 1                      |

| 0 0 1      | 2                      |

| 0 1 0      | 4                      |

| 0 1 1      | 8                      |

| 1 0 0      | 16                     |

| 1 0 1      | 32                     |

| 1 1 0      | 64                     |

| 1 1 1      | 128                    |

## 14.8.8 ESCI Prescaler Register

The ESCI prescaler register (SCPSC) together with the ESCI baud rate register selects the baud rate for both the receiver and the transmitter.

#### NOTE

There are two prescalers available to adjust the baud rate. One in the ESCI baud rate register and one in the ESCI prescaler register.

Figure 14-18. ESCI Prescaler Register (SCPSC)

MC68HC908GR16 Data Sheet, Rev. 5.0

Figure 15-8. POR Recovery

### 15.3.2.2 Computer Operating Properly (COP) Reset

An input to the SIM is reserved for the COP reset signal. The overflow of the COP counter causes an internal reset and sets the COP bit in the SIM reset status register (SRSR). The SIM actively pulls down the RST pin for all internal reset sources.

The COP module is disabled if the  $\overline{RST}$  pin or the  $\overline{IRQ}$  pin is held at  $V_{TST}$  while the MCU is in monitor mode. The COP module can be disabled only through combinational logic conditioned with the high voltage signal on the  $\overline{RST}$  or the  $\overline{IRQ}$  pin. This prevents the COP from becoming disabled as a result of external noise. During a break state,  $V_{TST}$  on the  $\overline{RST}$  pin disables the COP module.

#### 15.3.2.3 Illegal Opcode Reset

The SIM decodes signals from the CPU to detect illegal instructions. An illegal instruction sets the ILOP bit in the SIM reset status register (SRSR) and causes a reset.

If the stop enable bit, STOP, in the mask option register is 0, the SIM treats the STOP instruction as an illegal opcode and causes an illegal opcode reset. The SIM actively pulls down the RST pin for all internal reset sources.

#### 15.3.2.4 Illegal Address Reset

An opcode fetch from an unmapped address generates an illegal address reset. The SIM verifies that the CPU is fetching an opcode prior to asserting the ILAD bit in the SIM reset status register (SRSR) and resetting the MCU. A data fetch from an unmapped address does not generate a reset. The SIM actively pulls down the  $\overline{RST}$  pin for all internal reset sources.

#### 15.3.2.5 Low-Voltage Inhibit (LVI) Reset

The low-voltage inhibit module (LVI) asserts its output to the SIM when the  $V_{DD}$  voltage falls to the LVI<sub>TRIPF</sub> voltage. The LVI bit in the SIM reset status register (SRSR) is set, and the external reset pin (RST) is held low while the SIM counter counts out 4096 + 32 CGMXCLK cycles.

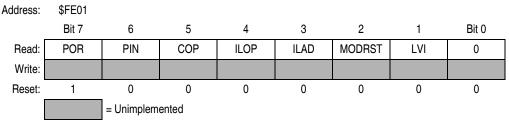

## 15.7.2 SIM Reset Status Register

This register contains seven flags that show the source of the last reset provided all previous reset status bits have been cleared. Clear the SIM reset status register by reading it. A power-on reset sets the POR bit and clears all other bits in the register.

Figure 15-22. SIM Reset Status Register (SRSR)

#### POR — Power-On Reset Bit

- 1 = Last reset caused by POR circuit

- 0 = Read of SRSR

#### PIN — External Reset Bit

- $1 = \text{Last reset caused by external reset pin } (\overline{RST})$

- 0 = POR or read of SRSR

## **COP** — Computer Operating Properly Reset Bit

- 1 = Last reset caused by COP counter

- 0 = POR or read of SRSR

## ILOP — Illegal Opcode Reset Bit

- 1 = Last reset caused by an illegal opcode

- 0 = POR or read of SRSR

## ILAD — Illegal Address Reset Bit (opcode fetches only)

- 1 = Last reset caused by an opcode fetch from an illegal address

- 0 = POR or read of SRSR

## **MODRST** — Monitor Mode Entry Module Reset Bit

- 1 = Last reset caused by monitor mode entry when vector locations \$FFFE and \$FFFF are \$FF after POR while  $\overline{IRQ} = V_{DD}$

- 0 = POR or read of SRSR

#### LVI — Low-Voltage Inhibit Reset Bit

- 1 = Last reset caused by the LVI circuit

- 0 = POR or read of SRSR

#### **Development Support**

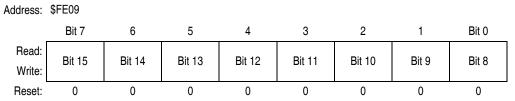

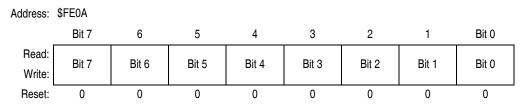

## 19.2.2.2 Break Address Registers

The break address registers (BRKH and BRKL) contain the high and low bytes of the desired breakpoint address. Reset clears the break address registers.

Figure 19-4. Break Address Register High (BRKH)

Figure 19-5. Break Address Register Low (BRKL)

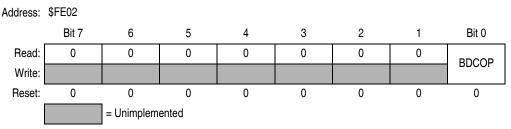

## 19.2.2.3 Break Auxiliary Register

The break auxiliary register (BRKAR) contains a bit that enables software to disable the COP while the MCU is in a state of break interrupt with monitor mode.

Figure 19-6. Break Auxiliary Register (BRKAR)

#### **BDCOP** — Break Disable COP Bit

This read/write bit disables the COP during a break interrupt. Reset clears the BDCOP bit.

- 1 = COP disabled during break interrupt

- 0 = COP enabled during break interrupt.

#### **Development Support**

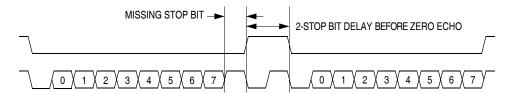

## 19.3.1.5 Break Signal

A start bit (0) followed by nine 0 bits is a break signal. When the monitor receives a break signal, it drives the PTA0 pin high for the duration of two bits and then echoes back the break signal.

Figure 19-14. Break Transaction

#### 19.3.1.6 Baud Rate

The communication baud rate is controlled by the crystal frequency or external clock and the state of the PTB4 pin (when  $\overline{IRQ}$  is set to  $V_{TST}$ ) upon entry into monitor mode. If monitor mode was entered with  $V_{DD}$  on  $\overline{IRQ}$  and the reset vector blank, then the baud rate is independent of PTB4.

Table 19-1 also lists external frequencies required to achieve a standard baud rate of 9600 bps. The effective baud rate is the bus frequency divided by 256. If using a crystal as the clock source, be aware of the upper frequency limit that the internal clock module can handle. See 20.7 5.0-Volt Control Timing or 20.8 3.3-Volt Control Timing for this limit.

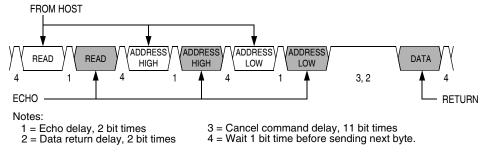

#### 19.3.1.7 Commands

The monitor ROM firmware uses these commands:

- READ (read memory)

- WRITE (write memory)

- IREAD (indexed read)

- IWRITE (indexed write)

- READSP (read stack pointer)

- RUN (run user program)

The monitor ROM firmware echoes each received byte back to the PTA0 pin for error checking. An 11-bit delay at the end of each command allows the host to send a break character to cancel the command. A delay of two bit times occurs before each echo and before READ, IREAD, or READSP data is returned. The data returned by a read command appears after the echo of the last byte of the command.

#### NOTE

Wait one bit time after each echo before sending the next byte.

Figure 19-15. Read Transaction

MC68HC908GR16 Data Sheet, Rev. 5.0

# 20.6 3.3-Vdc Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                                                                                                                                  | Symbol                                                | Min                                                                     | Typ <sup>(2)</sup>          | Max                   | Unit                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------|-----------------------|----------------------|

| Output high voltage  (I <sub>Load</sub> = -0.6 mA) all I/O pins  (I <sub>Load</sub> = -4.0 mA) all I/O pins  (I <sub>Load</sub> = -10.0 mA) pins PTC0-PTC4 only                                                | V <sub>OH</sub><br>V <sub>OH</sub><br>V <sub>OH</sub> | V <sub>DD</sub> - 0.3<br>V <sub>DD</sub> - 1.0<br>V <sub>DD</sub> - 1.0 | _<br>_<br>_                 | _<br>_<br>_           | V<br>V<br>V          |

| Maximum combined I <sub>OH</sub> for port PTA7–PTA3, port PTC0–PTC1, port E, port PTD0–PTD3                                                                                                                    | I <sub>OH1</sub>                                      |                                                                         | _                           | 30                    | mA                   |

| Maximum combined I <sub>OH</sub> for port PTA2–PTA0, port B, port PTC2–PTC6, port PTD4–PTD7                                                                                                                    | I <sub>OH2</sub>                                      | _                                                                       | _                           | 30                    | mA                   |

| Maximum total I <sub>OH</sub> for all port pins                                                                                                                                                                | I <sub>OHT</sub>                                      | _                                                                       | _                           | 60                    | mA                   |

| Output low voltage  (I <sub>Load</sub> = 1.6 mA) all I/O pins  (I <sub>Load</sub> = 10 mA) all I/O pins  (I <sub>Load</sub> = 20 mA) pins PTC0–PTC4 only  Maximum combined I <sub>OH</sub> for port PTA7–PTA3, | V <sub>OL</sub><br>V <sub>OL</sub><br>V <sub>OL</sub> | _<br>_<br>_                                                             | _<br>_<br>_                 | 0.3<br>1.0<br>0.8     | V<br>V<br>V          |

| port PTC0–PTC1, port E, port PTD0–PTD3  Maximum combined I <sub>OH</sub> for port PTA2–PTA0, port B, port PTC2–PTC6, port PTD4–PTD7                                                                            | I <sub>OL2</sub>                                      |                                                                         | _                           | 30<br>30              | mA<br>mA             |

| Maximum total I <sub>OL</sub> for all port pins                                                                                                                                                                | I <sub>OLT</sub>                                      | _                                                                       | _                           | 60                    | mA                   |

| Input high voltage All ports, IRQ, RST, OSC1                                                                                                                                                                   | V <sub>IH</sub>                                       | $0.7 \times V_{DD}$                                                     | _                           | V <sub>DD</sub>       | V                    |

| Input low voltage All ports, IRQ, RST, OSC1                                                                                                                                                                    | V <sub>IL</sub>                                       | V <sub>SS</sub>                                                         | _                           | $0.3 \times V_{DD}$   | V                    |

| V <sub>DD</sub> supply current Run <sup>(3)</sup> Wait <sup>(4)</sup> Stop <sup>(5)</sup>                                                                                                                      |                                                       | =                                                                       | 8<br>3                      | 12<br>6               | mA<br>mA             |

| 25°C 25°C with TBM enabled <sup>(6)</sup> 25°C with LVI and TBM enabled <sup>(6)</sup> -40°C to 125°C with TBM enabled <sup>(6)</sup> -40°C to 125°C with LVI and TBM enabled <sup>(6)</sup>                   | I <sub>DD</sub>                                       | _<br>_<br>_<br>_<br>_                                                   | 2<br>12<br>200<br>30<br>300 | _<br>_<br>_<br>_<br>_ | μΑ<br>μΑ<br>μΑ<br>μΑ |

| DC injection current, all ports                                                                                                                                                                                | I <sub>INJ</sub>                                      | -2                                                                      | _                           | +2                    | mA                   |

| Total dc current injection (sum of all I/O)                                                                                                                                                                    | I <sub>INJTOT</sub>                                   | -25                                                                     |                             | +25                   | mA                   |

| I/O ports Hi-Z leakage current <sup>(7)</sup>                                                                                                                                                                  | I <sub>IL</sub>                                       | -10                                                                     | _                           | +10                   | μΑ                   |

| Input current                                                                                                                                                                                                  | I <sub>In</sub>                                       | -1                                                                      | _                           | +1                    | μΑ                   |

| Pullup resistors (as input only) Ports PTA7/KBD7-PTA0/KBD0, PTC6-PTC0, PTD7/T2CH1-PTD0/SS                                                                                                                      | R <sub>PU</sub>                                       | 20                                                                      | 45                          | 65                    | kΩ                   |

| Capacitance Ports (as input or output)                                                                                                                                                                         | C <sub>Out</sub><br>C <sub>In</sub>                   |                                                                         | _                           | 12<br>8               | pF                   |

Continued on next page

# 20.10 5.0-Volt ADC Characteristics

| Characteristic <sup>(1)</sup>                | Symbol            | Min               | Max          | Unit                    | Comments                                                                                             |

|----------------------------------------------|-------------------|-------------------|--------------|-------------------------|------------------------------------------------------------------------------------------------------|

| Supply voltage                               | $V_{DDAD}$        | 4.5               | 5.5          | V                       | V <sub>DDAD</sub> should be tied to<br>the same potential as V <sub>DD</sub><br>via separate traces. |

| Input voltages                               | V <sub>ADIN</sub> | 0                 | $V_{DDAD}$   | V                       | V <sub>ADIN</sub> <= V <sub>DDAD</sub>                                                               |

| Resolution                                   | B <sub>AD</sub>   | 10                | 10           | Bits                    |                                                                                                      |

| Absolute accuracy                            | A <sub>AD</sub>   | -4                | +4           | Counts                  | Includes quantization                                                                                |

| ADC internal clock                           | f <sub>ADIC</sub> | 500 k             | 1.048 M      | Hz                      | $t_{AIC} = 1/f_{ADIC}$                                                                               |

| Conversion range                             | R <sub>AD</sub>   | V <sub>SSAD</sub> | $V_{DDAD}$   | V                       |                                                                                                      |

| Power-up time                                | t <sub>ADPU</sub> | 16                | _            | t <sub>AIC</sub> cycles |                                                                                                      |

| Conversion time                              | t <sub>ADC</sub>  | 16                | 17           | t <sub>AIC</sub> cycles |                                                                                                      |

| Sample time                                  | t <sub>ADS</sub>  | 5                 | _            | t <sub>AIC</sub> cycles |                                                                                                      |

| Monotonicity                                 | M <sub>AD</sub>   |                   |              | Guaranteed              |                                                                                                      |

| Zero input reading                           | Z <sub>ADI</sub>  | 000               | 003          | Hex                     | V <sub>ADIN</sub> = V <sub>SSA</sub>                                                                 |

| Full-scale reading                           | F <sub>ADI</sub>  | 3FC               | 3FF          | Hex                     | $V_{ADIN} = V_{DDA}$                                                                                 |

| Input capacitance                            | C <sub>ADI</sub>  | _                 | 30           | pF                      | Not tested                                                                                           |

| V <sub>DDAD</sub> /V <sub>REFH</sub> current | I <sub>VREF</sub> | _                 | 1.6          | mA                      |                                                                                                      |

| Absolute accuracy (8-bit truncation mode)    | A <sub>AD</sub>   | -1                | +1           | LSB                     | Includes quantization                                                                                |

| Quantization error (8-bit truncation mode)   | _                 | _                 | +7/8<br>-1/8 | LSB                     |                                                                                                      |

<sup>1.</sup>  $V_{DD}$  = 5.0 Vdc  $\pm$  10%,  $V_{SS}$  = 0 Vdc,  $V_{DDAD/VREFH}$  = 5.0 Vdc  $\pm$  10%,  $V_{SSAD/}V_{REFL}$  = 0 Vdc