#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | HC08                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | LINbus, SCI, SPI                                                         |

| Peripherals                | LVD, POR, PWM                                                            |

| Number of I/O              | 21                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-LQFP                                                                  |

| Supplier Device Package    | 32-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908gr16cfj |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table of Contents

| 10.13 Timebase Module (TBM) | 115 |

|-----------------------------|-----|

| 10.13.1 Wait Mode           | 115 |

| 10.13.2 Stop Mode           | 115 |

| 10.14 Exiting Wait Mode     | 115 |

| 10.15 Exiting Stop Mode     | 116 |

## Chapter 11 Low-Voltage Inhibit (LVI)

| 11.1   | Introduction                      |

|--------|-----------------------------------|

| 11.2   | Features                          |

| 11.3   | Functional Description            |

| 11.3.1 | Polled LVI Operation              |

| 11.3.2 | Forced Reset Operation            |

| 11.3.3 | Voltage Hysteresis Protection 119 |

| 11.3.4 | LVI Trip Selection                |

| 11.4   | LVI Status Register               |

| 11.5   | LVI Interrupts                    |

| 11.6   | Low-Power Modes                   |

| 11.6.1 |                                   |

| 11.6.2 | Stop Mode                         |

## Chapter 12 Input/Output Ports (PORTS)

| 12.1   | Introduction                            |

|--------|-----------------------------------------|

| 12.2   | Port A                                  |

| 12.2.1 | Port A Data Register                    |

| 12.2.2 | Data Direction Register A 124           |

| 12.2.3 | Port A Input Pullup Enable Register     |

| 12.3   | Port B                                  |

| 12.3.1 | Port B Data Register                    |

| 12.3.2 | Data Direction Register B 126           |

| 12.4   | Port C                                  |

| 12.4.1 | Port C Data Register                    |

| 12.4.2 | Data Direction Register C 128           |

| 12.4.3 | Port C Input Pullup Enable Register 129 |

| 12.5   | Port D                                  |

| 12.5.1 | Port D Data Register                    |

| 12.5.2 | Data Direction Register D 131           |

| 12.5.3 | Port D Input Pullup Enable Register 132 |

| 12.6   | Port E                                  |

| 12.6.1 | Port E Data Register                    |

| 12.6.2 | Data Direction Register E               |

General Description

## **1.5 Pin Functions**

Descriptions of the pin functions are provided here.

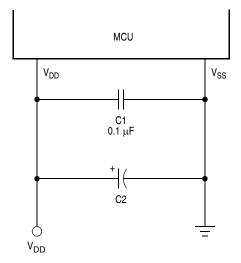

### 1.5.1 Power Supply Pins ( $V_{DD}$ and $V_{SS}$ )

V<sub>DD</sub> and V<sub>SS</sub> are the power supply and ground pins. The MCU operates from a single power supply.

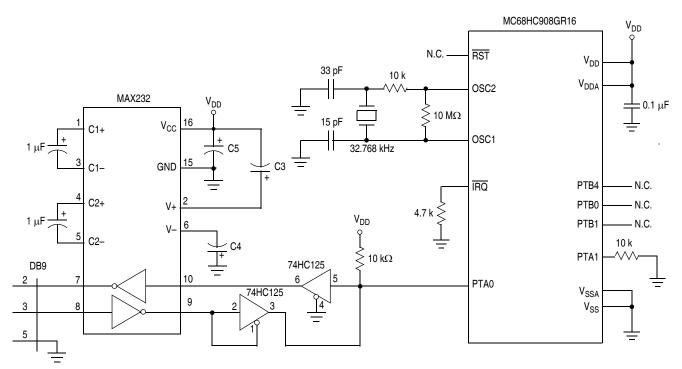

Fast signal transitions on MCU pins place high, short-duration current demands on the power supply. To prevent noise problems, take special care to provide power supply bypassing at the MCU as Figure 1-4 shows. Place the C1 bypass capacitor as close to the MCU as possible. Use a high-frequency-response ceramic capacitor for C1. C2 is an optional bulk current bypass capacitor for use in applications that require the port pins to source high current levels.

Note: Component values shown represent typical applications.

Figure 1-4. Power Supply Bypassing

### 1.5.2 Oscillator Pins (OSC1 and OSC2)

OSC1 and OSC2 are the connections for an external crystal, resonator, or clock circuit. See Chapter 4 Clock Generator Module (CGM).

### 1.5.3 External Reset Pin (RST)

A 0 on the RST pin forces the MCU to a known startup state. RST is bidirectional, allowing a reset of the entire system. It is driven low when any internal reset source is asserted. This pin contains an internal pullup resistor. See Chapter 15 System Integration Module (SIM).

### 1.5.4 External Interrupt Pin (IRQ)

IRQ is an asynchronous external interrupt pin. This pin contains an internal pullup resistor. See Chapter 8 External Interrupt (IRQ).

Memory

| Addr.                       | Register Name                                          |                 | Bit 7                                  | 6                   | 5     | 4           | 3            | 2       | 1       | Bit 0 |

|-----------------------------|--------------------------------------------------------|-----------------|----------------------------------------|---------------------|-------|-------------|--------------|---------|---------|-------|

| \$FF7E                      | FLASH Block Protect<br>Register (FLBPR) <sup>(3)</sup> | Read:<br>Write: | BPR7                                   | BPR6                | BPR5  | BPR4        | BPR3         | BPR2    | BPR1    | BPR0  |

|                             | See page 44.                                           | Reset:          |                                        | Unaffected by reset |       |             |              |         |         |       |

| <ol><li>Non-volat</li></ol> | ile FLASH register                                     |                 |                                        |                     |       |             |              |         |         |       |

|                             | COP Control Register                                   | Read:           |                                        |                     |       | Low byte of | reset vector |         |         |       |

| \$FFFF                      | (COPCTL)                                               | Write:          | Writing clears COP counter (any value) |                     |       |             |              |         |         |       |

|                             | See page 85.                                           | Reset:          | Unaffected by reset                    |                     |       |             |              |         |         |       |

|                             |                                                        |                 |                                        |                     |       |             |              |         |         |       |

|                             |                                                        |                 |                                        | = Unimplem          | ented | R           | = Reserved   | U = Una | ffected |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 8 of 8)

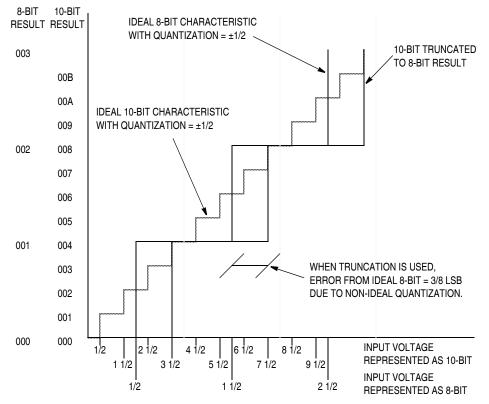

is used when compatibility with 8-bit ADC designs are required. No interlocking between ADRH and ADRL is present.

#### NOTE

Quantization error is affected when only the most significant eight bits are used as a result. See Figure 3-3.

Figure 3-3. Bit Truncation Mode Error

### 3.4 Monotonicity

The conversion process is monotonic and has no missing codes.

### 3.5 Interrupts

When the AIEN bit is set, the ADC module is capable of generating CPU interrupts after each ADC conversion. A CPU interrupt is generated if the COCO bit is a 0. The COCO bit is not used as a conversion complete flag when interrupts are enabled.

### 3.6 Low-Power Modes

The WAIT and STOP instruction can put the MCU in low power-consumption standby modes.

**Clock Generator Module (CGM)**

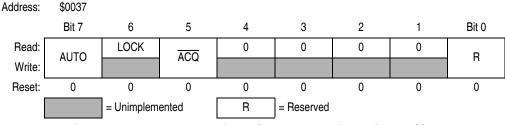

### 4.5.2 PLL Bandwidth Control Register

The PLL bandwidth control register (PBWC):

- Selects automatic or manual (software-controlled) bandwidth control mode

- Indicates when the PLL is locked

- In automatic bandwidth control mode, indicates when the PLL is in acquisition or tracking mode

- In manual operation, forces the PLL into acquisition or tracking mode

Figure 4-5. PLL Bandwidth Control Register (PBWC)

#### AUTO — Automatic Bandwidth Control Bit

This read/write bit selects automatic or manual bandwidth control. When initializing the PLL for manual operation (AUTO = 0), clear the  $\overline{ACQ}$  bit before turning on the PLL. Reset clears the AUTO bit.

1 = Automatic bandwidth control

0 = Manual bandwidth control

#### LOCK — Lock Indicator Bit

When the AUTO bit is set, LOCK is a read-only bit that becomes set when the VCO clock, CGMVCLK, is locked (running at the programmed frequency). When the AUTO bit is clear, LOCK reads as a 0 and has no meaning. The write one function of this bit is reserved for test, so this bit must **always** be written a 0. Reset clears the LOCK bit.

1 = VCO frequency correct or locked

0 = VCO frequency incorrect or unlocked

#### ACQ — Acquisition Mode Bit

When the AUTO bit is set,  $\overline{ACQ}$  is a read-only bit that indicates whether the PLL is in acquisition mode or tracking mode. When the AUTO bit is clear,  $\overline{ACQ}$  is a read/write bit that controls whether the PLL is in acquisition or tracking mode.

In automatic bandwidth control mode (AUTO = 1), the last-written value from manual operation is stored in a temporary location and is recovered when manual operation resumes. Reset clears this bit, enabling acquisition mode.

1 = Tracking mode

0 = Acquisition mode

# Chapter 6 Computer Operating Properly (COP) Module

## 6.1 Introduction

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the CONFIG register.

## 6.2 Functional Description

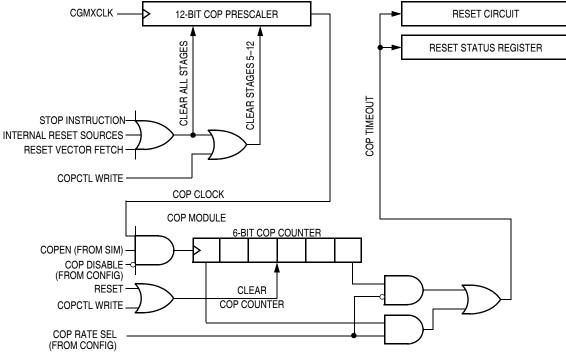

Figure 6-1 shows the structure of the COP module.

Figure 6-1. COP Block Diagram

**Central Processor Unit (CPU)**

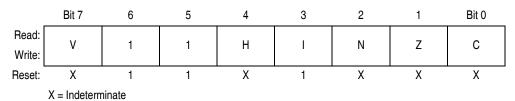

### 7.3.5 Condition Code Register

The 8-bit condition code register contains the interrupt mask and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code register.

Figure 7-6. Condition Code Register (CCR)

### V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

- 1 = Overflow

- 0 = No overflow

#### H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C flags to determine the appropriate correction factor.

1 = Carry between bits 3 and 4

0 = No carry between bits 3 and 4

### I — Interrupt Mask

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the interrupt vector is fetched.

- 1 = Interrupts disabled

- 0 = Interrupts enabled

#### NOTE

To maintain M6805 Family compatibility, the upper byte of the index register (H) is not stacked automatically. If the interrupt service routine modifies H, then the user must stack and unstack H using the PSHH and PULH instructions.

After the I bit is cleared, the highest-priority interrupt request is serviced first. A return-from-interrupt (RTI) instruction pulls the CPU registers from the stack and restores the interrupt mask from the stack. After any reset, the interrupt mask is set and can be cleared only by the clear interrupt mask software instruction (CLI).

#### N — Negative Flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result.

1 = Negative result

0 = Non-negative result

### 10.9.2 Stop Mode

If enabled, the LVI module remains active in stop mode. If enabled to generate resets, the LVI module can generate a reset and bring the MCU out of stop mode.

## **10.10 Enhanced Serial Communications Interface Module (ESCI)**

### 10.10.1 Wait Mode

The enhanced serial communications interface (ESCI), or SCI module for short, module remains active in wait mode. Any enabled CPU interrupt request from the SCI module can bring the MCU out of wait mode.

If SCI module functions are not required during wait mode, reduce power consumption by disabling the module before executing the WAIT instruction.

### 10.10.2 Stop Mode

The SCI module is inactive in stop mode. The STOP instruction does not affect SCI register states. SCI module operation resumes after the MCU exits stop mode.

Because the internal clock is inactive during stop mode, entering stop mode during an SCI transmission or reception results in invalid data.

## **10.11 Serial Peripheral Interface Module (SPI)**

### 10.11.1 Wait Mode

The serial peripheral interface (SPI) module remains active in wait mode. Any enabled CPU interrupt request from the SPI module can bring the MCU out of wait mode.

If SPI module functions are not required during wait mode, reduce power consumption by disabling the SPI module before executing the WAIT instruction.

### 10.11.2 Stop Mode

The SPI module is inactive in stop mode. The STOP instruction does not affect SPI register states. SPI operation resumes after an external interrupt. If stop mode is exited by reset, any transfer in progress is aborted, and the SPI is reset.

### **10.12** Timer Interface Module (TIM1 and TIM2)

### 10.12.1 Wait Mode

The timer interface modules (TIM) remain active in wait mode. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

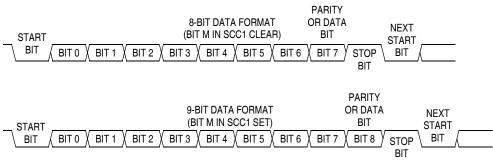

#### **Functional Description**

Figure 14-4. SCI Data Formats

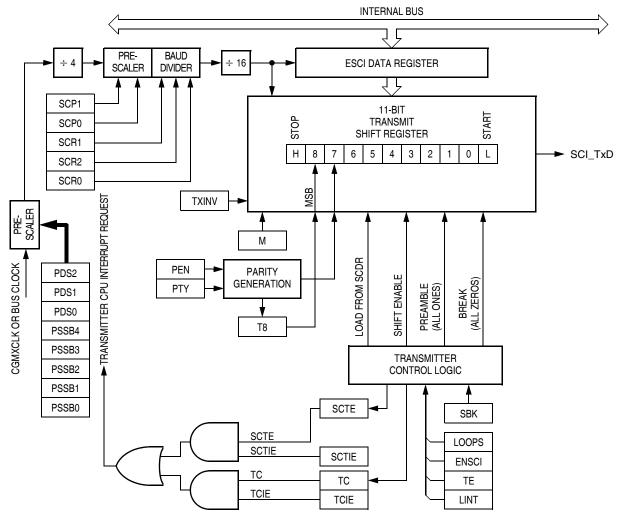

#### 14.4.2 Transmitter

Figure 14-5 shows the structure of the SCI transmitter and the registers are summarized in Figure 14-3. The baud rate clock source for the ESCI can be selected via the configuration bit, ESCIBDSRC.

Figure 14-5. ESCI Transmitter

#### Enhanced Serial Communications Interface (ESCI) Module

#### 14.4.2.1 Character Length

The transmitter can accommodate either 8-bit or 9-bit data. The state of the M bit in ESCI control register 1 (SCC1) determines character length. When transmitting 9-bit data, bit T8 in ESCI control register 3 (SCC3) is the ninth bit (bit 8).

#### 14.4.2.2 Character Transmission

During an ESCI transmission, the transmit shift register shifts a character out to the TxD pin. The ESCI data register (SCDR) is the write-only buffer between the internal data bus and the transmit shift register.

To initiate an ESCI transmission:

- 1. Enable the ESCI by writing a 1 to the enable ESCI bit (ENSCI) in ESCI control register 1 (SCC1).

- 2. Enable the transmitter by writing a 1 to the transmitter enable bit (TE) in ESCI control register 2 (SCC2).

- 3. Clear the ESCI transmitter empty bit (SCTE) by first reading ESCI status register 1 (SCS1) and then writing to the SCDR. For 9-bit data, also write the T8 bit in SCC3.

- 4. Repeat step 3 for each subsequent transmission.

At the start of a transmission, transmitter control logic automatically loads the transmit shift register with a preamble of 1s. After the preamble shifts out, control logic transfers the SCDR data into the transmit shift register. A 0 start bit automatically goes into the least significant bit (LSB) position of the transmit shift register. A 1 stop bit goes into the most significant bit (MSB) position.

The ESCI transmitter empty bit, SCTE, in SCS1 becomes set when the SCDR transfers a byte to the transmit shift register. The SCTE bit indicates that the SCDR can accept new data from the internal data bus. If the ESCI transmit interrupt enable bit, SCTIE, in SCC2 is also set, the SCTE bit generates a transmitter CPU interrupt request.

When the transmit shift register is not transmitting a character, the TxD pin goes to the idle condition, 1. If at any time software clears the ENSCI bit in ESCI control register 1 (SCC1), the transmitter and receiver relinquish control of the port E pins.

#### 14.4.2.3 Break Characters

Writing a 1 to the send break bit, SBK, in SCC2 loads the transmit shift register with a break character. For TXINV = 0 (output not inverted), a transmitted break character contains all 0s and has no start, stop, or parity bit. Break character length depends on the M bit in SCC1 and the LINR bits in SCBR. As long as SBK is at 1, transmitter logic continuously loads break characters into the transmit shift register. After software clears the SBK bit, the shift register finishes transmitting the last break character and then transmits at least one 1. The automatic 1 at the end of a break character guarantees the recognition of the start bit of the next character.

When LINR is cleared in SCBR, the ESCI recognizes a break character when a start bit is followed by eight or nine 0 data bits and a 0 where the stop bit should be, resulting in a total of 10 or 11 consecutive 0 data bits. When LINR is set in SCBR, the ESCI recognizes a break character when a start bit is followed by 9 or 10 0 data bits and a 0 where the stop bit should be, resulting in a total of 11 or 12 consecutive 0 data bits.

Receiving a break character has these effects on ESCI registers:

- Sets the framing error bit (FE) in SCS1

- Sets the ESCI receiver full bit (SCRF) in SCS1

- Clears the ESCI data register (SCDR)

#### Enhanced Serial Communications Interface (ESCI) Module

#### SCTE — ESCI Transmitter Empty Bit

This clearable, read-only bit is set when the SCDR transfers a character to the transmit shift register. SCTE can generate an ESCI transmitter CPU interrupt request. When the SCTIE bit in SCC2 is set, SCTE generates an ESCI transmitter CPU interrupt request. In normal operation, clear the SCTE bit by reading SCS1 with SCTE set and then writing to SCDR. Reset sets the SCTE bit.

- 1 = SCDR data transferred to transmit shift register

- 0 = SCDR data not transferred to transmit shift register

#### TC — Transmission Complete Bit

This read-only bit is set when the SCTE bit is set, and no data, preamble, or break character is being transmitted. TC generates an ESCI transmitter CPU interrupt request if the TCIE bit in SCC2 is also set. TC is cleared automatically when data, preamble, or break is queued and ready to be sent. There may be up to 1.5 transmitter clocks of latency between queueing data, preamble, and break and the transmission actually starting. Reset sets the TC bit.

- 1 = No transmission in progress

- 0 = Transmission in progress

#### SCRF — ESCI Receiver Full Bit

This clearable, read-only bit is set when the data in the receive shift register transfers to the ESCI data register. SCRF can generate an ESCI receiver CPU interrupt request. When the SCRIE bit in SCC2 is set the SCRF generates a CPU interrupt request. In normal operation, clear the SCRF bit by reading SCS1 with SCRF set and then reading the SCDR. Reset clears SCRF.

- 1 = Received data available in SCDR

- 0 = Data not available in SCDR

#### IDLE — Receiver Idle Bit

This clearable, read-only bit is set when 10 or 11 consecutive 1s appear on the receiver input. IDLE generates an ESCI receiver CPU interrupt request if the ILIE bit in SCC2 is also set. Clear the IDLE bit by reading SCS1 with IDLE set and then reading the SCDR. After the receiver is enabled, it must receive a valid character that sets the SCRF bit before an idle condition can set the IDLE bit. Also, after the IDLE bit has been cleared, a valid character must again set the SCRF bit before an idle condition can set the IDLE bit. Reset clears the IDLE bit.

- 1 = Receiver input idle

- 0 = Receiver input active (or idle since the IDLE bit was cleared)

#### **OR** — Receiver Overrun Bit

This clearable, read-only bit is set when software fails to read the SCDR before the receive shift register receives the next character. The OR bit generates an ESCI error CPU interrupt request if the ORIE bit in SCC3 is also set. The data in the shift register is lost, but the data already in the SCDR is not affected. Clear the OR bit by reading SCS1 with OR set and then reading the SCDR. Reset clears the OR bit.

- 1 = Receive shift register full and SCRF = 1

- 0 = No receiver overrun

Software latency may allow an overrun to occur between reads of SCS1 and SCDR in the flag-clearing sequence. Figure 14-14 shows the normal flag-clearing sequence and an example of an overrun caused by a delayed flag-clearing sequence. The delayed read of SCDR does not clear the OR bit because OR was not set when SCS1 was read. Byte 2 caused the overrun and is lost. The next flag-clearing sequence reads byte 3 in the SCDR instead of byte 2.

#### Enhanced Serial Communications Interface (ESCI) Module

### 14.8.5 ESCI Status Register 2

ESCI status register 2 (SCS2) contains flags to signal these conditions:

- Break character detected

- Incoming data

Figure 14-15. ESCI Status Register 2 (SCS2)

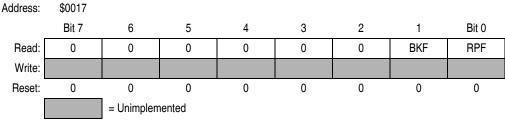

#### **BKF** — Break Flag Bit

This clearable, read-only bit is set when the ESCI detects a break character on the RxD pin. In SCS1, the FE and SCRF bits are also set. In 9-bit character transmissions, the R8 bit in SCC3 is cleared. BKF does not generate a CPU interrupt request. Clear BKF by reading SCS2 with BKF set and then reading the SCDR. Once cleared, BKF can become set again only after 1s again appear on the RxD pin followed by another break character. Reset clears the BKF bit.

1 = Break character detected

0 = No break character detected

#### **RPF** — Reception in Progress Flag Bit

This read-only bit is set when the receiver detects a 0 during the RT1 time period of the start bit search. RPF does not generate an interrupt request. RPF is reset after the receiver detects false start bits (usually from noise or a baud rate mismatch), or when the receiver detects an idle character. Polling RPF before disabling the ESCI module or entering stop mode can show whether a reception is in progress.

1 = Reception in progress

0 = No reception in progress

### 14.8.6 ESCI Data Register

The ESCI data register (SCDR) is the buffer between the internal data bus and the receive and transmit shift registers. Reset has no effect on data in the ESCI data register.

| Address: | \$0018 |                     |    |    |    |    |    |       |  |  |

|----------|--------|---------------------|----|----|----|----|----|-------|--|--|

|          | Bit 7  | 6                   | 5  | 4  | 3  | 2  | 1  | Bit 0 |  |  |

| Read:    | R7     | R6                  | R5 | R4 | R3 | R2 | R1 | R0    |  |  |

| Write:   | T7     | T6                  | T5 | T4 | T3 | T2 | T1 | Т0    |  |  |

| Reset:   |        | Unaffected by reset |    |    |    |    |    |       |  |  |

Figure 14-16. ESCI Data Register (SCDR)

#### R7/T7:R0/T0 — Receive/Transmit Data Bits

Reading address \$0018 accesses the read-only received data bits, R7:R0. Writing to address \$0018 writes the data to be transmitted, T7:T0. Reset has no effect on the ESCI data register.

#### NOTE

Do not use read-modify-write instructions on the ESCI data register.

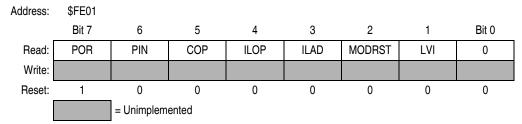

### 15.7.2 SIM Reset Status Register

This register contains seven flags that show the source of the last reset provided all previous reset status bits have been cleared. Clear the SIM reset status register by reading it. A power-on reset sets the POR bit and clears all other bits in the register.

#### Figure 15-22. SIM Reset Status Register (SRSR)

#### POR — Power-On Reset Bit

1 = Last reset caused by POR circuit

0 = Read of SRSR

#### PIN — External Reset Bit

- 1 = Last reset caused by external reset pin ( $\overline{RST}$ )

- 0 = POR or read of SRSR

#### COP — Computer Operating Properly Reset Bit

- 1 = Last reset caused by COP counter

- 0 = POR or read of SRSR

#### ILOP — Illegal Opcode Reset Bit

- 1 = Last reset caused by an illegal opcode

- 0 = POR or read of SRSR

#### ILAD — Illegal Address Reset Bit (opcode fetches only)

- 1 = Last reset caused by an opcode fetch from an illegal address

- 0 = POR or read of SRSR

#### MODRST — Monitor Mode Entry Module Reset Bit

- 1 = Last reset caused by monitor mode entry when vector locations \$FFFE and \$FFFF are \$FF after POR while  $\overline{IRQ} = V_{DD}$

- 0 = POR or read of SRSR

#### LVI — Low-Voltage Inhibit Reset Bit

- 1 = Last reset caused by the LVI circuit

- 0 = POR or read of SRSR

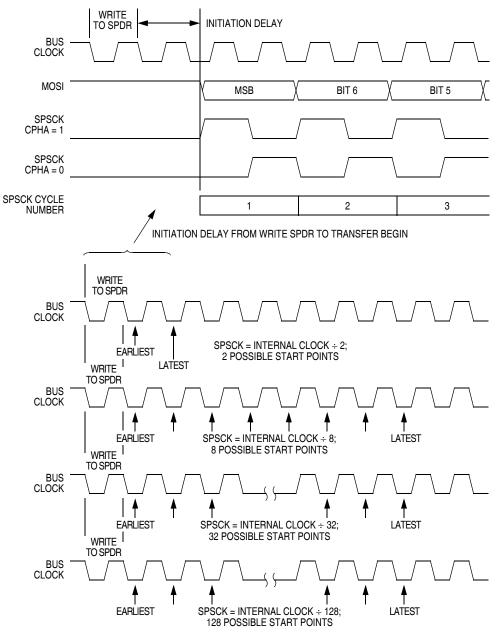

#### Serial Peripheral Interface (SPI) Module

signal. When CPHA = 0, the SPSCK signal remains inactive for the first half of the first SPSCK cycle. When CPHA = 1, the first SPSCK cycle begins with an edge on the SPSCK line from its inactive to its active level. The SPI clock rate (selected by SPR1:SPR0) affects the delay from the write to SPDR and the start of the SPI transmission. (See Figure 16-8.) The internal SPI clock in the master is a free-running derivative of the internal MCU clock. To conserve power, it is enabled only when both the SPE and SPMSTR bits are set. SPSCK edges occur halfway through the low time of the internal MCU clock. Since the SPI clock is free-running, it is uncertain where the write to the SPDR occurs relative to the slower SPSCK. This uncertainty causes the variation in the initiation delay shown in Figure 16-8. This delay is no longer than a single SPI bit time. That is, the maximum delay is two MCU bus cycles for DIV2, eight MCU bus cycles for DIV8, 32 MCU bus cycles for DIV32, and 128 MCU bus cycles for DIV128.

Figure 16-8. Transmission Start Delay (Master)

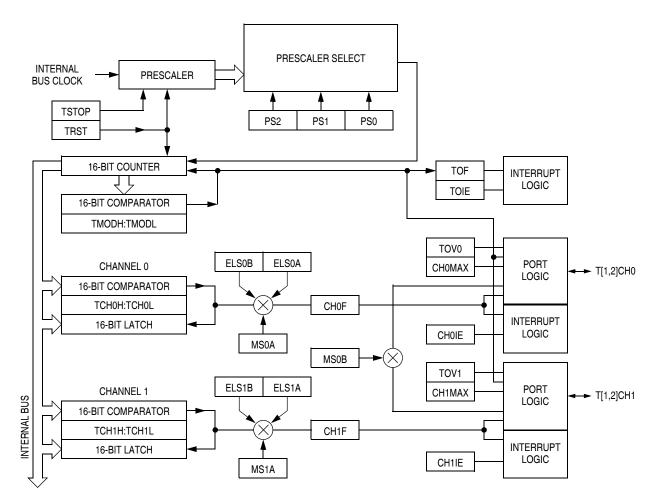

# Chapter 18 Timer Interface Module (TIM)

## **18.1 Introduction**

This section describes the timer interface (TIM) module. The TIM is a two-channel timer that provides a timing reference with input capture, output compare, and pulse-width-modulation functions. Figure 18-1 is a block diagram of the TIM.

This particular MCU has two timer interface modules which are denoted as TIM1 and TIM2.

Figure 18-1. TIM Block Diagram

#### **Timer Interface Module (TIM)**

### 18.6.2 Stop Mode

The TIM is inactive after the execution of a STOP instruction. The STOP instruction does not affect register conditions or the state of the TIM counter. TIM operation resumes when the MCU exits stop mode after an external interrupt.

### 18.7 TIM During Break Interrupts

A break interrupt stops the TIM counter.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear status bits during the break state. See 15.7.3 Break Flag Control Register.

To allow software to clear status bits during a break interrupt, write a 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a 2-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at 0. After the break, doing the second step clears the status bit.

### 18.8 I/O Signals

Port D shares four of its pins with the TIM. The four TIM channel I/O pins are T1CH0, T1CH1, T2CH0, and T2CH1 as described in 18.3 Pin Name Conventions.

Each channel I/O pin is programmable independently as an input capture pin or an output compare pin. T1CH0 and T2CH0 can be configured as buffered output compare or buffered PWM pins.

### 18.9 I/O Registers

#### NOTE

References to either timer 1 or timer 2 may be made in the following text by omitting the timer number. For example, TSC may generically refer to both T1SC AND T2SC.

These I/O registers control and monitor operation of the TIM:

- TIM status and control register (TSC)

- TIM counter registers (TCNTH:TCNTL)

- TIM counter modulo registers (TMODH:TMODL)

- TIM channel status and control registers (TSC0 and TSC1)

- TIM channel registers (TCH0H:TCH0L, TCH1H:TCH1L)

#### ELSxB and ELSxA — Edge/Level Select Bits

When channel x is an input capture channel, these read/write bits control the active edge-sensing logic on channel x.

When channel x is an output compare channel, ELSxB and ELSxA control the channel x output behavior when an output compare occurs.

When ELSxB and ELSxA are both clear, channel x is not connected to port D, and pin PTDx/TCHx is available as a general-purpose I/O pin. Table 18-3 shows how ELSxB and ELSxA work. Reset clears the ELSxB and ELSxA bits.

| MSxB:MSxA | ELSxB:ELSxA | Mode                                                     | Configuration                                    |  |

|-----------|-------------|----------------------------------------------------------|--------------------------------------------------|--|

| X0        | 00          | Output Pin under port control; initial output level high |                                                  |  |

| X1        | 00          | preset                                                   | Pin under port control; initial output level low |  |

| 00        | 01          |                                                          | Capture on rising edge only                      |  |

| 00        | 10          | Input<br>capture                                         | Capture on falling edge only                     |  |

| 00        | 11          | oupturo                                                  | Capture on rising or falling edge                |  |

| 01        | 01          |                                                          | Toggle output on compare                         |  |

| 01        | 10          | Output compare<br>or PWM                                 | Clear output on compare                          |  |

| 01        | 11          |                                                          | Set output on compare                            |  |

| 1X        | 01          | Buffered output                                          | Toggle output on compare                         |  |

| 1X        | 10          | compare<br>or buffered                                   | Clear output on compare                          |  |

| 1X        | 11          | PWM                                                      | Set output on compare                            |  |

Table 18-3. Mode, Edge, and Level Selection

#### NOTE

Before enabling a TIM channel register for input capture operation, make sure that the PTD/TCHx pin is stable for at least two bus clocks.

#### TOVx — Toggle On Overflow Bit

When channel x is an output compare channel, this read/write bit controls the behavior of the channel x output when the TIM counter overflows. When channel x is an input capture channel, TOVx has no effect. Reset clears the TOVx bit.

1 = Channel x pin toggles on TIM counter overflow.

0 = Channel x pin does not toggle on TIM counter overflow.

#### NOTE

When TOVx is set, a TIM counter overflow takes precedence over a channel x output compare if both occur at the same time.

#### CHxMAX — Channel x Maximum Duty Cycle Bit

When the TOVx bit is at 1, setting the CHxMAX bit forces the duty cycle of buffered and unbuffered PWM signals to 100%. As Figure 18-12 shows, the CHxMAX bit takes effect in the cycle after it is set or cleared. The output stays at the 100% duty cycle level until the cycle after CHxMAX is cleared.

Monitor ROM (MON)

Figure 19-12. Forced Monitor Mode Circuit ( $\overline{IRQ} = GND$ )

Enter monitor mode with pin configuration shown in Table 19-1 by pulling  $\overline{RST}$  low and then high. The rising edge of  $\overline{RST}$  latches monitor mode. Once monitor mode is latched, the values on the specified pins can change.

Once out of reset, the MCU waits for the host to send eight security bytes (see

19.3.2 Security). After the security bytes, the MCU sends a break signal (10 consecutive 0s) to the host, indicating that it is ready to receive a command.

#### 19.3.1.1 Normal Monitor Mode

Table 19-1 shows the pin conditions for entering monitor mode.

If  $V_{TST}$  is applied to  $\overline{IRQ}$  and PTB4 is low upon monitor mode entry, the bus frequency is a divide-by-two of the input clock. If PTB4 is high with  $V_{TST}$  applied to  $\overline{IRQ}$  upon monitor mode entry, the bus frequency will be a divide-by-four of the input clock. Holding the PTB4 pin low when entering monitor mode causes a bypass of a divide-by-two stage at the oscillator *only if*  $V_{TST}$  *is applied to*  $\overline{IRQ}$ . In this event, the CGMOUT frequency is equal to the CGMXCLK frequency, and the OSC1 input directly generates internal bus clocks. In this case, the OSC1 signal must have a 50% duty cycle at maximum bus frequency.

When monitor mode was entered with  $V_{TST}$  on  $\overline{IRQ}$ , the computer operating properly (COP) is disabled as long as  $V_{TST}$  is applied to either  $\overline{IRQ}$  or RST.

## 20.13 5.0-Volt SPI Characteristics

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                        | Symbol                                       | Min                                              | Max                                   | Unit                                 |

|----------------------------------|----------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------|---------------------------------------|--------------------------------------|

|                                  | Operating frequency<br>Master<br>Slave                               | f <sub>OP(M)</sub><br>f <sub>OP(S)</sub>     | f <sub>OP</sub> /128<br>dc                       | f <sub>OP</sub> /2<br>f <sub>OP</sub> | MHz<br>MHz                           |

| 1                                | Cycle time<br>Master<br>Slave                                        | t <sub>CYC(M)</sub><br>t <sub>CYC(S)</sub>   | 2<br>1                                           | 128<br>—                              | t <sub>CYC</sub><br>t <sub>CYC</sub> |

| 2                                | Enable lead time                                                     | t <sub>Lead(S)</sub>                         | 1                                                | _                                     | t <sub>CYC</sub>                     |

| 3                                | Enable lag time                                                      | t <sub>Lag(S)</sub>                          | 1                                                |                                       | t <sub>CYC</sub>                     |

| 4                                | Clock (SPSCK) high time<br>Master<br>Slave                           | t <sub>SCKH(M)</sub><br>t <sub>SCKH(S)</sub> | t <sub>CYC</sub> –25<br>1/2 t <sub>CYC</sub> –25 | 64 t <sub>CYC</sub>                   | ns<br>ns                             |

| 5                                | Clock (SPSCK) low time<br>Master<br>Slave                            | t <sub>SCKL(M)</sub><br>t <sub>SCKL(S)</sub> | t <sub>CYC</sub> –25<br>1/2 t <sub>CYC</sub> –25 | 64 t <sub>CYC</sub>                   | ns<br>ns                             |

| 6                                | Data setup time (inputs)<br>Master<br>Slave                          | t <sub>SU(M)</sub><br>t <sub>SU(S)</sub>     | 30<br>30                                         |                                       | ns<br>ns                             |

| 7                                | Data hold time (inputs)<br>Master<br>Slave                           | t <sub>H(M)</sub><br>t <sub>H(S)</sub>       | 30<br>30                                         |                                       | ns<br>ns                             |

| 8                                | Access time, slave <sup>(3)</sup><br>CPHA = 0<br>CPHA = 1            | t <sub>A(CP0)</sub><br>t <sub>A(CP1)</sub>   | 0<br>0                                           | 40<br>40                              | ns<br>ns                             |

| 9                                | Disable time, slave <sup>(4)</sup>                                   | t <sub>DIS(S)</sub>                          | _                                                | 40                                    | ns                                   |

| 10                               | Data valid time, after enable edge<br>Master<br>Slave <sup>(5)</sup> | t <sub>V(M)</sub><br>t <sub>V(S)</sub>       |                                                  | 50<br>50                              | ns<br>ns                             |

| 11                               | Data hold time, outputs, after enable edge<br>Master<br>Slave        | t <sub>HO(M)</sub><br>t <sub>HO(S)</sub>     | 0<br>0                                           |                                       | ns<br>ns                             |

Numbers refer to dimensions in Figure 20-3 and Figure 20-4.

All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins.

Time to data active from high-impedance state

Hold time to high-impedance state

With 100 pF on all SPI pins

**Electrical Specifications**

## 20.14 3.3-Volt SPI Characteristics

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                        | Symbol                                       | Min                                              | Max                                   | Unit                                 |

|----------------------------------|----------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------|---------------------------------------|--------------------------------------|

|                                  | Operating frequency<br>Master<br>Slave                               | f <sub>OP(M)</sub><br>f <sub>OP(S)</sub>     | f <sub>OP</sub> /128<br>DC                       | f <sub>OP</sub> /2<br>f <sub>OP</sub> | MHz<br>MHz                           |

| 1                                | Cycle time<br>Master<br>Slave                                        | t <sub>CYC(M)</sub><br>t <sub>CYC(S)</sub>   | 2<br>1                                           | 128<br>—                              | t <sub>cyc</sub><br>t <sub>cyc</sub> |

| 2                                | Enable lead time                                                     | t <sub>Lead(S)</sub>                         | 1                                                | _                                     | t <sub>cyc</sub>                     |

| 3                                | Enable lag time                                                      | t <sub>Lag(S)</sub>                          | 1                                                | _                                     | t <sub>cyc</sub>                     |

| 4                                | Clock (SPSCK) high time<br>Master<br>Slave                           | t <sub>SCKH(M)</sub><br>t <sub>SCKH(S)</sub> | t <sub>cyc</sub> –35<br>1/2 t <sub>cyc</sub> –35 | 64 t <sub>cyc</sub>                   | ns<br>ns                             |

| 5                                | Clock (SPSCK) low time<br>Master<br>Slave                            | t <sub>SCKL(M)</sub><br>t <sub>SCKL(S)</sub> | t <sub>cyc</sub> –35<br>1/2 t <sub>cyc</sub> –35 | ±<br>64 t <sub>cyc</sub><br>—         | ns<br>ns                             |

| 6                                | Data setup time (inputs)<br>Master<br>Slave                          | t <sub>SU(M)</sub><br>t <sub>SU(S)</sub>     | 40<br>40                                         | _                                     | ns<br>ns                             |

| 7                                | Data hold time (inputs)<br>Master<br>Slave                           | t <sub>H(M)</sub><br>t <sub>H(S)</sub>       | 40<br>40                                         |                                       | ns<br>ns                             |

| 8                                | Access time, slave <sup>(3)</sup><br>CPHA = 0<br>CPHA = 1            | t <sub>A(CP0)</sub><br>t <sub>A(CP1)</sub>   | 0<br>0                                           | 50<br>50                              | ns<br>ns                             |

| 9                                | Disable time, slave <sup>(4)</sup>                                   | t <sub>DIS(S)</sub>                          | —                                                | 50                                    | ns                                   |

| 10                               | Data valid time, after enable edge<br>Master<br>Slave <sup>(5)</sup> | t∨(M)<br>t <sub>V(S)</sub>                   |                                                  | 60<br>60                              | ns<br>ns                             |

| 11                               | Data hold time, outputs, after enable edge<br>Master<br>Slave        | t <sub>HO(M)</sub><br>t <sub>HO(S)</sub>     | 0<br>0                                           |                                       | ns<br>ns                             |

Numbers refer to dimensions in Figure 20-3 and Figure 20-4.

All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins.

Time to data active from high-impedance state

Hold time to high-impedance state

With 100 pF on all SPI pins