Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | HC08                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | LINbus, SCI, SPI                                                         |

| Peripherals                | LVD, POR, PWM                                                            |

| Number of I/O              | 21                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-LQFP                                                                  |

| Supplier Device Package    | 32-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908gr16mfj |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## MC68HC908GR16

## **Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

## **Revision History**

| Date              | Revision<br>Level | Description                                                                               | Page<br>Number(s) |

|-------------------|-------------------|-------------------------------------------------------------------------------------------|-------------------|

| February,<br>2003 | N/A               | Initial release                                                                           | N/A               |

| May,<br>2003      | 1.0               | Reorganized to meet latest publication standards for M68HC08 Family documentation         | N/A               |

|                   |                   | Chapter 16 Serial Peripheral Interface (SPI) Module — Removed all references to DMAS      | 193               |

|                   |                   | Figure 4-2. CGM External Connections — Figure updated for consistency                     | 65                |

|                   |                   | Table 4-4. Example Filter Component Values — Table updated to reflect new resistor values | 76                |

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2004, 2007. All rights reserved.

MC68HC908GR16 Data Sheet, Rev. 5.0

## **List of Chapters**

| Chapter 1 General Description                                     | 19  |

|-------------------------------------------------------------------|-----|

| Chapter 2 Memory                                                  | 27  |

| Chapter 3 Analog-to-Digital Converter (ADC)                       | 47  |

| Chapter 4 Clock Generator Module (CGM)                            | 59  |

| Chapter 5 Configuration Register (CONFIG)                         | 79  |

| Chapter 6 Computer Operating Properly (COP) Module                | 83  |

| Chapter 7 Central Processor Unit (CPU)                            | 87  |

| Chapter 8 External Interrupt (IRQ)                                | 99  |

| Chapter 9 Keyboard Interrupt Module (KBI)                         | 105 |

| Chapter 10 Low-Power Modes                                        | 111 |

| Chapter 11 Low-Voltage Inhibit (LVI)                              | 117 |

| Chapter 12 Input/Output Ports (PORTS)                             | 121 |

| Chapter 13 Resets and Interrupts                                  | 135 |

| Chapter 14 Enhanced Serial Communications Interface (ESCI) Module | 147 |

| Chapter 15 System Integration Module (SIM)                        | 177 |

| Chapter 16 Serial Peripheral Interface (SPI) Module               | 195 |

| Chapter 17 Timebase Module (TBM)                                  | 217 |

| Chapter 18 Timer Interface Module (TIM)                           | 221 |

| Chapter 19 Development Support                                    | 237 |

| Chapter 20 Electrical Specifications                              | 253 |

| Chanter 21 Ordering Information and Mechanical Specifications     | 269 |

| Ta | h | ما | Ωf  | $C_{0}$ | nto | nts  |

|----|---|----|-----|---------|-----|------|

| ıa | u |    | OI. | Cu      |     | 1115 |

| 6.3.8 | COPRS (COP Rate Select)            | 85 |

|-------|------------------------------------|----|

| 6.4   | COP Control Register               | 85 |

| 6.5   | Interrupts                         | 85 |

| 6.6   | Monitor Mode                       | 85 |

| 6.7   | Low-Power Modes                    | 85 |

| 6.7.1 | Wait Mode                          | 85 |

| 6.7.2 | Stop Mode                          | 85 |

| 6.8   | COP Module During Break Mode       | 86 |

|       | Chapter 7                          |    |

|       | Central Processor Unit (CPU)       |    |

| 7.1   | Introduction                       |    |

| 7.2   | Features                           | 87 |

| 7.3   | CPU Registers                      |    |

| 7.3.1 | Accumulator                        |    |

| 7.3.2 | Index Register                     |    |

| 7.3.3 | Stack Pointer                      |    |

| 7.3.4 | Program Counter                    |    |

| 7.3.5 | Condition Code Register            |    |

| 7.4   | Arithmetic/Logic Unit (ALU)        |    |

| 7.5   | Low-Power Modes                    |    |

| 7.5.1 | Wait Mode                          |    |

| 7.5.2 | Stop Mode                          |    |

| 7.6   | CPU During Break Interrupts        |    |

| 7.7   | Instruction Set Summary            |    |

| 7.8   | Opcode Map                         | 97 |

|       | Chapter 8                          |    |

| 0.4   | External Interrupt (IRQ)           |    |

| 8.1   | Introduction                       |    |

| 8.2   | Features                           |    |

| 8.3   | Functional Description             |    |

| 8.4   | IRQ Pin                            |    |

| 8.5   | IRQ Module During Break Interrupts |    |

| 8.6   | IRQ Status and Control Register    | 03 |

|       | Chapter 9                          |    |

| 0.1   | Keyboard Interrupt Module (KBI)    | ΛE |

| 9.1   | Introduction                       |    |

| 9.2   | Features1                          |    |

| 9.3   | Functional Description             |    |

| 9.4   | Keyboard Initialization            |    |

| 9.5   | Low-Power Modes                    |    |

| 9.5.1 | Wait Mode                          | 08 |

MC68HC908GR16 Data Sheet, Rev. 5.0

## Chapter 13 Resets and Interrupts

| 13.1               | Introduction                                           | 135 |

|--------------------|--------------------------------------------------------|-----|

| 13.2               | Resets                                                 | 135 |

| 13.2.1             | Effects                                                | 135 |

| 13.2.2             | External Reset                                         | 135 |

| 13.2.3             | Internal Reset                                         | 135 |

| 13.2.3.            |                                                        |     |

| 13.2.3.            | ·                                                      |     |

| 13.2.3.            |                                                        |     |

| 13.2.3.            |                                                        |     |

| 13.2.3.            | 5 Illegal Address Reset                                | 137 |

| 13.2.4             | System Integration Module (SIM) Reset Status Register  | 137 |

| 13.3               | Interrupts                                             | 138 |

| 13.3.1             | Effects                                                |     |

| 13.3.2             | Sources                                                |     |

| 13.3.2.            |                                                        |     |

| 13.3.2.            | • • •                                                  |     |

| 13.3.2.            | ·                                                      |     |

| 13.3.2.            | 4 Clock Generator (CGM)                                | 142 |

| 13.3.2.            | Timer Interface Module 1 (TIM1)                        | 142 |

| 13.3.2.            | 6 Timer Interface Module 2 (TIM2)                      | 142 |

| 13.3.2.            | 7 Serial Peripheral Interface (SPI)                    | 142 |

| 13.3.2.            |                                                        |     |

| 13.3.2.            |                                                        |     |

| 13.3.2.            | 3 3 ( - )                                              |     |

| 13.3.2.            |                                                        |     |

| 13.3.3             | Interrupt Status Registers                             |     |

| 13.3.3.            | 1 3                                                    |     |

| 13.3.3.            | 1 3                                                    |     |

| 13.3.3.            | Interrupt Status Register 3                            | 145 |

|                    | Chapter 14                                             |     |

|                    | Enhanced Serial Communications Interface (ESCI) Module |     |

| 14.1               | Introduction                                           | 147 |

|                    | Features                                               |     |

|                    | Pin Name Conventions                                   |     |

|                    | Functional Description                                 |     |

| 14.4<br>14.4.1     | ·                                                      |     |

|                    | Data Format                                            |     |

| 14.4.2<br>14.4.2.  | Transmitter                                            |     |

| 14.4.2.<br>14.4.2. |                                                        |     |

| 14.4.2.            |                                                        |     |

| 14.4.2.            |                                                        |     |

| 14.4.2.            |                                                        |     |

| 14.4.2.            | ·                                                      |     |

| 14.4.3             | Receiver                                               |     |

| ı <del>-</del> 0   | 110001701                                              | 104 |

#### Memory

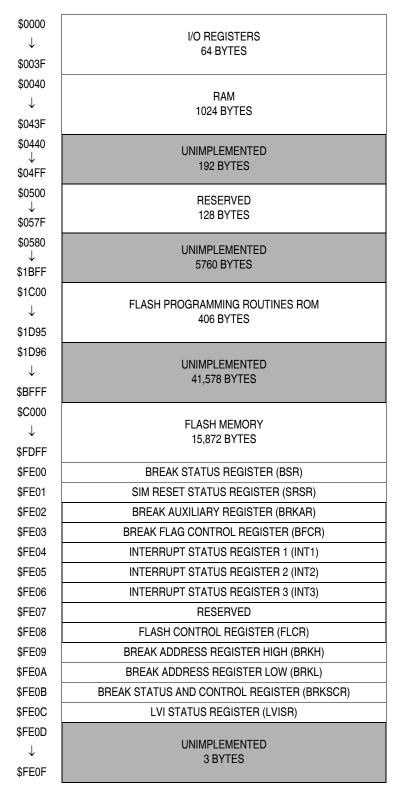

Data registers are shown in Figure 2-2. Table 2-1 is a list of vector locations.

Figure 2-1. Memory Map

MC68HC908GR16 Data Sheet, Rev. 5.0

|          | Timer 1 Channel 1 Register High (T1CH1H) See page 236. Timer 1 Channel 1         | Read:<br>Write: | Bit 15    |            |        |             |                |         |         |        |

|----------|----------------------------------------------------------------------------------|-----------------|-----------|------------|--------|-------------|----------------|---------|---------|--------|

|          | See page 236.                                                                    |                 |           | 14         | 13     | 12          | 11             | 10      | 9       | Bit 8  |

| \$002A   | Timor 1 Channal 1                                                                | Reset:          |           |            |        | Indetermina | te after reset |         |         |        |

|          | Register Low (T1CH1L)                                                            | Read:<br>Write: | Bit 7     | 6          | 5      | 4           | 3              | 2       | 1       | Bit 0  |

|          | See page 236.                                                                    | Reset:          |           |            |        | Indetermina | te after reset |         |         |        |

| Tim      | er 2 Status and Control                                                          | Read:           | TOF       | TOIL       | TOTOR  | 0           | 0              | D00     | D04     | D00    |

| \$002B   | Register (T2SC)                                                                  | Write:          | 0         | TOIE       | TSTOP  | TRST        |                | PS2     | PS1     | PS0    |

|          | See page 231.                                                                    | Reset:          | 0         | 0          | 1      | 0           | 0              | 0       | 0       | 0      |

|          | Timer 2 Counter                                                                  | Read:           | Bit 15    | 14         | 13     | 12          | 11             | 10      | 9       | Bit 8  |

| \$002C F | Register High (T2CNTH)                                                           | Write:          |           |            |        |             |                |         |         |        |

|          | See page 232.                                                                    | Reset:          | 0         | 0          | 0      | 0           | 0              | 0       | 0       | 0      |

|          | Timer 2 Counter                                                                  | Read:           | Bit 7     | 6          | 5      | 4           | 3              | 2       | 1       | Bit 0  |

| \$002D   | Register Low (T2CNTL)                                                            | Write:          |           |            |        |             |                |         |         |        |

|          | See page 232.                                                                    | Reset:          | 0         | 0          | 0      | 0           | 0              | 0       | 0       | 0      |

|          | Timer 2 Counter Modulo egister High (T2MODH)                                     | Read:<br>Write: | Bit 15    | 14         | 13     | 12          | 11             | 10      | 9       | Bit 8  |

|          | See page 233.                                                                    | Reset:          | 1         | 1          | 1      | 1           | 1              | 1       | 1       | 1      |

|          | imer 2 Counter Modulo<br>Register Low (T2MODL)                                   | Read:<br>Write: | Bit 7     | 6          | 5      | 4           | 3              | 2       | 1       | Bit 0  |

|          | See page 233.                                                                    | Reset:          | 1         | 1          | 1      | 1           | 1              | 1       | 1       | 1      |

|          | Timer 2 Channel 0 Status and<br>\$0030 Control Register (T2SC0)                  | Read:<br>Write: | CH0F<br>0 | - CH0IE    | MS0B   | MS0A        | ELS0B          | ELS0A   | TOV0    | CH0MAX |

|          | See page 233.                                                                    | Reset:          | 0         | 0          | 0      | 0           | 0              | 0       | 0       | 0      |

| \$0031 F | Timer 2 Channel 0<br>Register High (T2CH0H)                                      | Read:<br>Write: | Bit 15    | 14         | 13     | 12          | 11             | 10      | 9       | Bit 8  |

|          | See page 236.                                                                    | Reset:          |           |            |        | Indetermina | te after reset |         |         |        |

| \$0032   | Timer 2 Channel 0<br>Register Low (T2CH0L)                                       | Read:<br>Write: | Bit 7     | 6          | 5      | 4           | 3              | 2       | 1       | Bit 0  |

|          | See page 236.                                                                    |                 |           | I.         | I.     | Indetermina | te after reset |         | I       | I I    |

|          | Timer 2 Channel 1 Status and<br>\$0033 Control Register (T2SC1)<br>See page 234. | Read:<br>Write: | CH1F<br>0 | CH1IE      | 0      | MS1A        | ELS1B          | ELS1A   | TOV1    | CH1MAX |

| 7        |                                                                                  | Reset:          | 0         | 0          | 0      | 0           | 0              | 0       | 0       | 0      |

| \$0034 F | Timer 2 Channel 1<br>Register High (T2CH1H)                                      | Read:<br>Write: | Bit 15    | 14         | 13     | 12          | 11             | 10      | 9       | Bit 8  |

|          | See page 236.                                                                    |                 |           | L          | L      | Indetermina | te after reset |         | L       | 1      |

|          |                                                                                  | [               |           | = Unimplem | nented | R           | = Reserved     | U = Una | ffected |        |

Figure 2-2. Control, Status, and Data Registers (Sheet 5 of 8)

Programming tools are available from Freescale Semiconductor. Contact your local representative for more information.

#### NOTE

A security feature prevents viewing of the FLASH contents. (1)

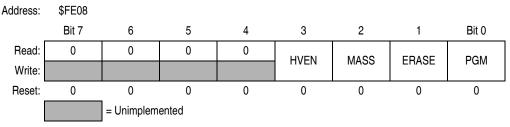

## 2.6.1.1 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

Figure 2-3. FLASH Control Register (FLCR)

## **HVEN** — High-Voltage Enable Bit

This read/write bit enables the charge pump to drive high voltages for program and erase operations in the array. HVEN can only be set if either PGM = 1 or ERASE = 1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

#### MASS — Mass Erase Control Bit

Setting this read/write bit configures the 16-Kbyte FLASH array for mass erase operation.

- 1 = MASS erase operation selected

- 0 = PAGE erase operation selected

## **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

#### **PGM** — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

MC68HC908GR16 Data Sheet, Rev. 5.0

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

#### Memory

#### 2.6.1.5 FLASH Block Protection

Due to the ability of the on-board charge pump to erase and program the FLASH memory in the target application, provision is made for protecting a block of memory from unintentional erase or program operations due to system malfunction. This protection is done by using of a FLASH block protect register (FLBPR). The FLBPR determines the range of the FLASH memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends at the bottom of the FLASH memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either ERASE or PROGRAM operations.

#### NOTE

In performing a program or erase operation, the FLASH block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit

When the FLBPR is program with all 0's, the entire memory is protected from being programmed and erased. When all the bits are erased (all 1's), the entire memory is accessible for program and erase.

When bits within the FLBPR are programmed, they lock a block of memory, address ranges as shown in 2.6.1.6 FLASH Block Protect Register. Once the FLBPR is programmed with a value other than \$FF or \$FE, any erase or program of the FLBPR or the protected block of FLASH memory is prohibited. Mass erase is disabled whenever any block is protected (FLBPR does not equal \$FF). The presence of a  $V_{TST}$  on the  $\overline{IRQ}$  pin will bypass the block protection so that all of the memory included in the block protect register is open for program and erase operations.

## NOTE

The FLASH block protect register is not protected with special hardware or software. Therefore, if this page is not protected by FLBPR the register is erased by either a page or mass erase operation.

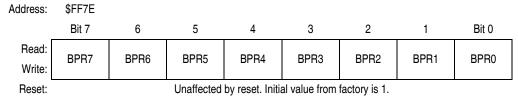

#### 2.6.1.6 FLASH Block Protect Register

The FLASH block protect register (FLBPR) is implemented as a byte within the FLASH memory, and therefore can only be written during a programming sequence of the FLASH memory. The value in this register determines the starting location of the protected range within the FLASH memory.

Write to this register is by a programming sequence to the FLASH memory.

Figure 2-5. FLASH Block Protect Register (FLBPR)

## BPR[7:0] — FLASH Block Protect Bits

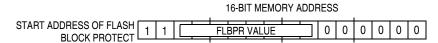

These eight bits represent bits [13:6] of a 16-bit memory address. Bit 15 and Bit 14 are 1s and bits [5:0] are 0s.

The resultant 16-bit address is used for specifying the start address of the FLASH memory for block protection. The FLASH is protected from this start address to the end of FLASH memory, at \$FFFF. With this mechanism, the protect start address can be \$XX00, \$XX40, \$XX80, and \$XXC0 (64 bytes page boundaries) within the FLASH memory.

MC68HC908GR16 Data Sheet, Rev. 5.0

Figure 2-6. FLASH Block Protect Start Address

Table 2-2. Examples of Protect Address Ranges

| BPR[7:0]                  | Addresses of Protect Range                                                        |  |

|---------------------------|-----------------------------------------------------------------------------------|--|

| \$00                      | The entire FLASH memory is protected.                                             |  |

| \$01 ( <b>0000 0001</b> ) | \$C040 (11 <b>00 0000 01</b> 00 0000) — \$FFFF                                    |  |

| \$02 ( <b>0000 0010</b> ) | \$C080 (11 <b>00 0000 10</b> 00 0000) — \$FFFF                                    |  |

| \$03 (0000 0011)          | \$C0C0 (11 <b>00 0000 11</b> 00 0000) — \$FFFF                                    |  |

| \$04 ( <b>0000 0100</b> ) | \$C100 (11 <b>00 0001 00</b> 00 0000) — \$FFFF                                    |  |

| and so on                 |                                                                                   |  |

| \$FC (1111 1100)          | \$FF00 (11 <b>11 1111 00</b> 00 0000) — FFFF                                      |  |

| \$FD ( <b>1111 1101</b> ) | \$FF40 (11 <b>11 1111 01</b> 00 0000) — \$FFFF<br>FLBPR and vectors are protected |  |

| \$FE (1111 1110)          | \$FF80 (11 <b>11 1111 10</b> 00 0000) — FFFF<br>Vectors are protected             |  |

| \$FF                      | The entire FLASH memory is not protected.                                         |  |

## 2.6.2 Wait Mode

Putting the MCU into wait mode while the FLASH is in read mode does not affect the operation of the FLASH memory directly, but there will not be any memory activity since the CPU is inactive.

The WAIT instruction should not be executed while performing a program or erase operation on the FLASH, otherwise the operation will discontinue, and the FLASH will be on standby mode.

## 2.6.3 Stop Mode

Putting the MCU into stop mode while the FLASH is in read mode does not affect the operation of the FLASH memory directly, but there will not be any memory activity since the CPU is inactive.

The STOP instruction should not be executed while performing a program or erase operation on the FLASH, otherwise the operation will discontinue, and the FLASH will be on standby mode

#### NOTE

Standby mode is the power saving mode of the FLASH module in which all internal control signals to the FLASH are inactive and the current consumption of the FLASH is at a minimum.

#### Analog-to-Digital Converter (ADC)

## AIEN — ADC Interrupt Enable Bit

When this bit is set, an interrupt is generated at the end of an ADC conversion. The interrupt signal is cleared when the data register is read or the status/control register is written. Reset clears the AIEN bit.

- 1 = ADC interrupt enabled

- 0 = ADC interrupt disabled

## ADCO — ADC Continuous Conversion Bit

When set, the ADC will convert samples continuously and update the ADR register at the end of each conversion. Only one conversion is completed between writes to the ADSCR when this bit is cleared. Reset clears the ADCO bit.

- 1 = Continuous ADC conversion

- 0 = One ADC conversion

## ADCH4-ADCH0 — ADC Channel Select Bits

ADCH4–ADCH0 form a 5-bit field which is used to select one of 16 ADC channels. Only eight channels, AD7–AD0, are available on this MCU. The channels are detailed in Table 3-1. Care should be taken when using a port pin as both an analog and digital input simultaneously to prevent switching noise from corrupting the analog signal. See Table 3-1.

The ADC subsystem is turned off when the channel select bits are all set to 1. This feature allows for reduced power consumption for the MCU when the ADC is not being used.

#### NOTE

Recovery from the disabled state requires one conversion cycle to stabilize.

The voltage levels supplied from internal reference nodes, as specified in Table 3-1, are used to verify the operation of the ADC converter both in production test and for user applications.

| ADCH4    | ADCH3        | ADCH2        | ADCH1        | ADCH0        | Input Select      |

|----------|--------------|--------------|--------------|--------------|-------------------|

| 0        | 0            | 0            | 0            | 0            | PTB0/AD0          |

| 0        | 0            | 0            | 0            | 1            | PTB1/AD1          |

| 0        | 0            | 0            | 1            | 0            | PTB2/AD2          |

| 0        | 0            | 0            | 1            | 1            | PTB3/AD3          |

| 0        | 0            | 1            | 0            | 0            | PTB4/AD4          |

| 0        | 0            | 1            | 0            | 1            | PTB5/AD5          |

| 0        | 0            | 1            | 1            | 0            | PTB6/AD6          |

| 0        | 0            | 1            | 1            | 1            | PTB7/AD7          |

| 0        | 1            | 0            | 0            | 0            |                   |

| <b>↓</b> | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ | Unused            |

| 1        | 1            | 1            | 0            | 0            |                   |

| 1        | 1            | 1            | 0            | 1            | V <sub>REFH</sub> |

| 1        | 1            | 1            | 1            | 0            | V <sub>REFL</sub> |

| 1        | 1            | 1            | 1            | 1            | ADC power off     |

Table 3-1. Mux Channel Select<sup>(1)</sup>

<sup>1.</sup> If any unused channels are selected, the resulting ADC conversion will be unknown or reserved.

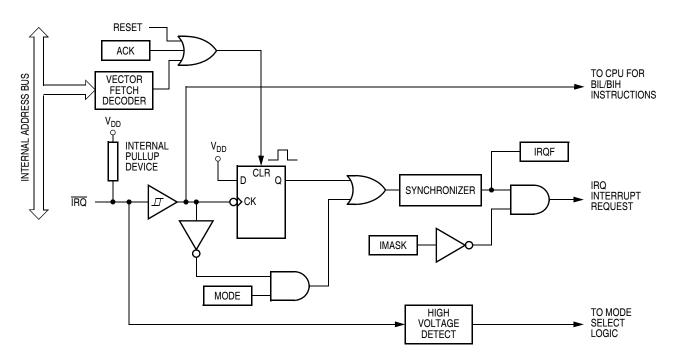

Figure 8-2. IRQ Module Block Diagram

When an interrupt pin is both falling-edge and low-level triggered (MODE = 1), the interrupt remains set until both of these events occur:

- · Vector fetch or software clear

- Return of the interrupt pin to 1

The vector fetch or software clear may occur before or after the interrupt pin returns to 1. As long as the pin is low, the interrupt request remains pending. A reset will clear the latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

When set, the IMASK bit in the INTSCR mask all external interrupt requests. A latched interrupt request is not presented to the interrupt priority logic unless the IMASK bit is clear.

## **NOTE**

The interrupt mask (I) in the condition code register (CCR) masks all interrupt requests, including external interrupt requests.

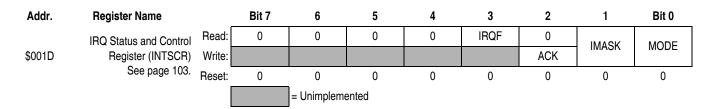

Figure 8-3. IRQ I/O Register Summary

Freescale Semiconductor 101

MC68HC908GR16 Data Sheet, Rev. 5.0

#### **Keyboard Interrupt Module (KBI)**

## ACKK — Keyboard Acknowledge Bit

Writing a 1 to this write-only bit clears the keyboard interrupt request. ACKK always reads as 0. Reset clears ACKK.

## **IMASKK** — Keyboard Interrupt Mask Bit

Writing a 1 to this read/write bit prevents the output of the keyboard interrupt mask from generating interrupt requests. Reset clears the IMASKK bit.

- 1 = Keyboard interrupt requests masked

- 0 = Keyboard interrupt requests not masked

## **MODEK** — Keyboard Triggering Sensitivity Bit

This read/write bit controls the triggering sensitivity of the keyboard interrupt pins. Reset clears MODEK.

- 1 = Keyboard interrupt requests on falling edges and low levels

- 0 = Keyboard interrupt requests on falling edges only

## 9.7.2 Keyboard Interrupt Enable Register

The keyboard interrupt enable register enables or disables each port A pin to operate as a keyboard interrupt pin.

Figure 9-5. Keyboard Interrupt Enable Register (INTKBIER)

## KBIE7-KBIE0 — Keyboard Interrupt Enable Bits

Each of these read/write bits enables the corresponding keyboard interrupt pin to latch interrupt requests. Reset clears the keyboard interrupt enable register.

- 1 = PTAx pin enabled as keyboard interrupt pin

- 0 = PTAx pin not enabled as keyboard interrupt pin

#### **Resets and Interrupts**

## 13.3.2.9 KBD0-KBD7 Pins

A 0 on a keyboard interrupt pin latches an external interrupt request.

## 13.3.2.10 Analog-to-Digital Converter (ADC)

When the AIEN bit is set, the ADC module is capable of generating a CPU interrupt after each ADC conversion. The COCO bit is not used as a conversion complete flag when interrupts are enabled.

## 13.3.2.11 Timebase Module (TBM)

The timebase module can interrupt the CPU on a regular basis with a rate defined by TBR2–TBR0. When the timebase counter chain rolls over, the TBIF flag is set. If the TBIE bit is set, enabling the timebase interrupt, the counter chain overflow will generate a CPU interrupt request.

Interrupts must be acknowledged by writing a 1 to the TACK bit.

## 13.3.3 Interrupt Status Registers

The flags in the interrupt status registers identify maskable interrupt sources. Table 13-2 summarizes the interrupt sources and the interrupt status register flags that they set. The interrupt status registers can be useful for debugging.

**Table 13-2. Interrupt Source Flags**

| Interrupt<br>Source     | Interrupt Status<br>Register Flag |  |  |

|-------------------------|-----------------------------------|--|--|

| Reset                   | _                                 |  |  |

| SWI instruction         | _                                 |  |  |

| ĪRQ pin                 | IF1                               |  |  |

| CGM change of lock      | IF2                               |  |  |

| TIM1 channel 0          | IF3                               |  |  |

| TIM1 channel 1          | IF4                               |  |  |

| TIM1 overflow           | IF5                               |  |  |

| TIM2 channel 0          | IF6                               |  |  |

| TIM2 channel 1          | IF7                               |  |  |

| TIM2 overflow           | IF8                               |  |  |

| SPI receive             | IF9                               |  |  |

| SPI transmit            | IF10                              |  |  |

| SCI error               | IF11                              |  |  |

| SCI receive             | IF12                              |  |  |

| SCI transmit            | IF13                              |  |  |

| Keyboard                | IF14                              |  |  |

| ADC conversion complete | IF15                              |  |  |

| Timebase                | IF16                              |  |  |

MC68HC908GR16 Data Sheet, Rev. 5.0

#### **Enhanced Serial Communications Interface (ESCI) Module**

## SCTE — ESCI Transmitter Empty Bit

This clearable, read-only bit is set when the SCDR transfers a character to the transmit shift register. SCTE can generate an ESCI transmitter CPU interrupt request. When the SCTIE bit in SCC2 is set, SCTE generates an ESCI transmitter CPU interrupt request. In normal operation, clear the SCTE bit by reading SCS1 with SCTE set and then writing to SCDR. Reset sets the SCTE bit.

- 1 = SCDR data transferred to transmit shift register

- 0 = SCDR data not transferred to transmit shift register

## TC — Transmission Complete Bit

This read-only bit is set when the SCTE bit is set, and no data, preamble, or break character is being transmitted. TC generates an ESCI transmitter CPU interrupt request if the TCIE bit in SCC2 is also set. TC is cleared automatically when data, preamble, or break is queued and ready to be sent. There may be up to 1.5 transmitter clocks of latency between queueing data, preamble, and break and the transmission actually starting. Reset sets the TC bit.

- 1 = No transmission in progress

- 0 = Transmission in progress

### SCRF — ESCI Receiver Full Bit

This clearable, read-only bit is set when the data in the receive shift register transfers to the ESCI data register. SCRF can generate an ESCI receiver CPU interrupt request. When the SCRIE bit in SCC2 is set the SCRF generates a CPU interrupt request. In normal operation, clear the SCRF bit by reading SCS1 with SCRF set and then reading the SCDR. Reset clears SCRF.

- 1 = Received data available in SCDR

- 0 = Data not available in SCDR

## IDLE — Receiver Idle Bit

This clearable, read-only bit is set when 10 or 11 consecutive 1s appear on the receiver input. IDLE generates an ESCI receiver CPU interrupt request if the ILIE bit in SCC2 is also set. Clear the IDLE bit by reading SCS1 with IDLE set and then reading the SCDR. After the receiver is enabled, it must receive a valid character that sets the SCRF bit before an idle condition can set the IDLE bit. Also, after the IDLE bit has been cleared, a valid character must again set the SCRF bit before an idle condition can set the IDLE bit. Reset clears the IDLE bit.

- 1 = Receiver input idle

- 0 = Receiver input active (or idle since the IDLE bit was cleared)

#### **OR** — Receiver Overrun Bit

This clearable, read-only bit is set when software fails to read the SCDR before the receive shift register receives the next character. The OR bit generates an ESCI error CPU interrupt request if the ORIE bit in SCC3 is also set. The data in the shift register is lost, but the data already in the SCDR is not affected. Clear the OR bit by reading SCS1 with OR set and then reading the SCDR. Reset clears the OR bit.

- 1 = Receive shift register full and SCRF = 1

- 0 = No receiver overrun

Software latency may allow an overrun to occur between reads of SCS1 and SCDR in the flag-clearing sequence. Figure 14-14 shows the normal flag-clearing sequence and an example of an overrun caused by a delayed flag-clearing sequence. The delayed read of SCDR does not clear the OR bit because OR was not set when SCS1 was read. Byte 2 caused the overrun and is lost. The next flag-clearing sequence reads byte 3 in the SCDR instead of byte 2.

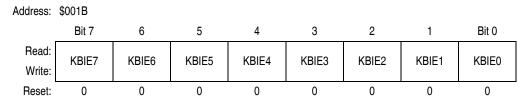

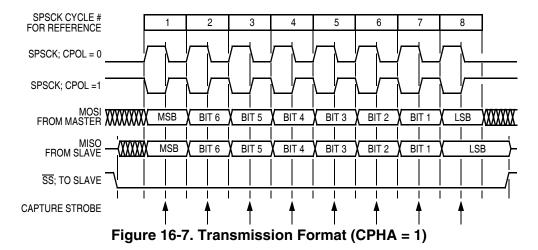

Figure 16-6. CPHA/SS Timing

## 16.5.3 Transmission Format When CPHA = 1

Figure 16-7 shows an SPI transmission in which CPHA is 1. The figure should not be used as a replacement for data sheet parametric information. Two waveforms are shown for SPSCK: one for CPOL = 0 and another for CPOL = 1. The diagram may be interpreted as a master or slave timing diagram since the serial clock (SPSCK), master in/slave out (MISO), and master out/slave in (MOSI) pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The SS line is the slave select input to the slave. The slave SPI drives its MISO output only when its slave select input (SS) is at 0, so that only the selected slave drives to the master. The SS pin of the master is not shown but is assumed to be inactive. The SS pin of the master must be high or must be reconfigured as general-purpose I/O not affecting the SPI. (See 16.7.2 Mode Fault Error.) When CPHA = 1, the master begins driving its MOSI pin on the first SPSCK edge. Therefore, the slave uses the first SPSCK edge as a start transmission signal. The SS pin can remain low between transmissions. This format may be preferable in systems having only one master and only one slave driving the MISO data line.

When CPHA = 1 for a slave, the first edge of the SPSCK indicates the beginning of the transmission. This causes the SPI to leave its idle state and begin driving the MISO pin with the MSB of its data. Once the transmission begins, no new data is allowed into the shift register from the transmit data register. Therefore, the SPI data register of the slave must be loaded with transmit data before the first edge of SPSCK. Any data written after the first edge is stored in the transmit data register and transferred to the shift register after the current transmission.

## 16.5.4 Transmission Initiation Latency

When the SPI is configured as a master (SPMSTR = 1), writing to the SPDR starts a transmission. CPHA has no effect on the delay to the start of the transmission, but it does affect the initial state of the SPSCK

Freescale Semiconductor 201

MC68HC908GR16 Data Sheet, Rev. 5.0

#### Serial Peripheral Interface (SPI) Module

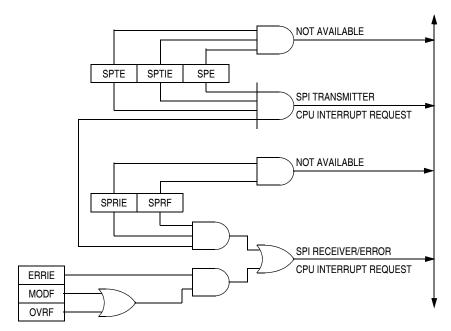

Figure 16-12. SPI Interrupt Request Generation

## 16.9 Resetting the SPI

Any system reset completely resets the SPI. Partial resets occur whenever the SPI enable bit (SPE) is low. Whenever SPE is low, the following occurs:

- The SPTE flag is set.

- Any transmission currently in progress is aborted.

- The shift register is cleared.

- The SPI state counter is cleared, making it ready for a new complete transmission.

- All the SPI port logic is defaulted back to being general-purpose I/O.

These items are reset only by a system reset:

- All control bits in the SPCR register

- All control bits in the SPSCR register (MODFEN, ERRIE, SPR1, and SPR0)

- The status flags SPRF, OVRF, and MODF

By not resetting the control bits when SPE is low, the user can clear SPE between transmissions without having to set all control bits again when SPE is set back high for the next transmission.

By not resetting the SPRF, OVRF, and MODF flags, the user can still service these interrupts after the SPI has been disabled. The user can disable the SPI by writing 0 to the SPE bit. The SPI can also be disabled by a mode fault occurring in an SPI that was configured as a master with the MODFEN bit set.

## 16.10 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

Serial Peripheral Interface (SPI) Module

## 16.12.1 MISO (Master In/Slave Out)

MISO is one of the two SPI module pins that transmits serial data. In full duplex operation, the MISO pin of the master SPI module is connected to the MISO pin of the slave SPI module. The master SPI simultaneously receives data on its MISO pin and transmits data from its MOSI pin.

Slave output data on the MISO pin is enabled only when the SPI is configured as a slave. The SPI is configured as a slave when its SPMSTR bit is 0 and its  $\overline{SS}$  pin is at 0. To support a multiple-slave system, a 1 on the  $\overline{SS}$  pin puts the MISO pin in a high-impedance state.

When enabled, the SPI controls data direction of the MISO pin regardless of the state of the data direction register of the shared I/O port.

## 16.12.2 MOSI (Master Out/Slave In)

MOSI is one of the two SPI module pins that transmits serial data. In full-duplex operation, the MOSI pin of the master SPI module is connected to the MOSI pin of the slave SPI module. The master SPI simultaneously transmits data from its MOSI pin and receives data on its MISO pin.

When enabled, the SPI controls data direction of the MOSI pin regardless of the state of the data direction register of the shared I/O port.

## 16.12.3 SPSCK (Serial Clock)

The serial clock synchronizes data transmission between master and slave devices. In a master MCU, the SPSCK pin is the clock output. In a slave MCU, the SPSCK pin is the clock input. In full-duplex operation, the master and slave MCUs exchange a byte of data in eight serial clock cycles.

When enabled, the SPI controls data direction of the SPSCK pin regardless of the state of the data direction register of the shared I/O port.

## **16.12.4 SS** (Slave Select)

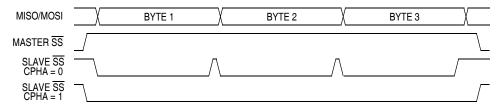

The  $\overline{SS}$  pin has various functions depending on the current state of the SPI. For an SPI configured as a slave, the  $\overline{SS}$  is used to select a slave. For CPHA = 0, the  $\overline{SS}$  is used to define the start of a transmission. (See 16.5 Transmission Formats.) Since it is used to indicate the start of a transmission, the  $\overline{SS}$  must be toggled high and low between each byte transmitted for the CPHA = 0 format. However, it can remain low between transmissions for the CPHA = 1 format. See Figure 16-13.

Figure 16-13. CPHA/SS Timing

When an SPI is configured as a slave, the  $\overline{SS}$  pin is always configured as an input. It cannot be used as a general-purpose I/O regardless of the state of the MODFEN control bit. However, the MODFEN bit can still prevent the state of the  $\overline{SS}$  from creating a MODF error. See 16.13.2 SPI Status and Control Register.

# Chapter 17 Timebase Module (TBM)

## 17.1 Introduction

This section describes the timebase module (TBM). The TBM will generate periodic interrupts at user selectable rates using a counter clocked by the external clock source. This TBM version uses 15 divider stages, eight of which are user selectable. A configuration option bit to select an additional 128 divide of the external clock source can be selected. See Chapter 5 Configuration Register (CONFIG)

## 17.2 Features

Features of the TBM module include:

- External clock or an additional divide-by-128 selected by configuration option bit as clock source

- Software configurable periodic interrupts with divide-by: 8, 16, 32, 64, 128, 2048, 8192, and 32768 taps of the selected clock source

- Configurable for operation during stop mode to allow periodic wakeup from stop

## 17.3 Functional Description

This module can generate a periodic interrupt by dividing the clock source supplied from the clock generator module, CGMXCLK.

The counter is initialized to all 0s when TBON bit is cleared. The counter, shown in Figure 17-1, starts counting when the TBON bit is set. When the counter overflows at the tap selected by TBR2–TBR0, the TBIF bit gets set. If the TBIE bit is set, an interrupt request is sent to the CPU. The TBIF flag is cleared by writing a 1 to the TACK bit. The first time the TBIF flag is set after enabling the timebase module, the interrupt is generated at approximately half of the overflow period. Subsequent events occur at the exact period.

The timebase module may remain active after execution of the STOP instruction if the crystal oscillator has been enabled to operate during stop mode through the OSCENINSTOP bit in the configuration register. The timebase module can be used in this mode to generate a periodic wakeup from stop mode.

## 17.4 Interrupts

The timebase module can periodically interrupt the CPU with a rate defined by the selected TBMCLK and the select bits TBR2–TBR0. When the timebase counter chain rolls over, the TBIF flag is set. If the TBIE bit is set, enabling the timebase interrupt, the counter chain overflow will generate a CPU interrupt request.

## NOTE

Interrupts must be acknowledged by writing a 1 to the TACK bit.

MC68HC908GR16 Data Sheet, Rev. 5.0

c. Write 1:0 (to clear output on compare) or 1:1 (to set output on compare) to the edge/level select bits, ELSxB:ELSxA. The output action on compare must force the output to the complement of the pulse width level. See Table 18-3.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare can also cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

5. In the TIM status control register (TSC), clear the TIM stop bit, TSTOP.

Setting MS0B links channels 0 and 1 and configures them for buffered PWM operation. The TIM channel 0 registers (TCH0H:TCH0L) initially control the buffered PWM output. TIM status control register 0 (TSCR0) controls and monitors the PWM signal from the linked channels.

Clearing the toggle-on-overflow bit, TOVx, inhibits output toggles on TIM overflows. Subsequent output compares try to force the output to a state it is already in and have no effect. The result is a 0% duty cycle output.

Setting the channel x maximum duty cycle bit (CHxMAX) and setting the TOVx bit generates a 100% duty cycle output. See 18.9.4 TIM Channel Status and Control Registers.

## 18.5 Interrupts

The following TIM sources can generate interrupt requests:

- TIM overflow flag (TOF) The TOF bit is set when the TIM counter reaches the modulo value programmed in the TIM counter modulo registers. The TIM overflow interrupt enable bit, TOIE, enables TIM overflow CPU interrupt requests. TOF and TOIE are in the TIM status and control register.

- TIM channel flags (CH1F:CH0F) The CHxF bit is set when an input capture or output compare occurs on channel x. Channel x TIM CPU interrupt requests are controlled by the channel x interrupt enable bit, CHxIE. Channel x TIM CPU interrupt requests are enabled when CHxIE = 1. CHxF and CHxIE are in the TIM channel x status and control register.

## 18.6 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 18.6.1 Wait Mode

The TIM remains active after the execution of a WAIT instruction. In wait mode, the TIM registers are not accessible by the CPU. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

Freescale Semiconductor 229

MC68HC908GR16 Data Sheet, Rev. 5.0

#### **Timer Interface Module (TIM)**

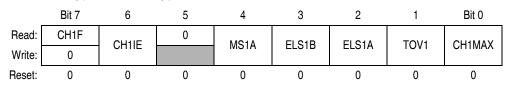

Address: T1SC1, \$0028 and T2SC1, \$0033

Figure 18-11. TIM Channel 1 Status and Control Register (TSC1)

## CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM counter registers matches the value in the TIM channel x registers.

When TIM CPU interrupt requests are enabled (CHxIE = 1), clear CHxF by reading TIM channel x status and control register with CHxF set and then writing a 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a 1 to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

## CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM CPU interrupt service requests on channel x. Reset clears the CHxIE bit.

- 1 = Channel x CPU interrupt requests enabled

- 0 = Channel x CPU interrupt requests disabled

#### MSxB — Mode Select Bit B

This read/write bit selects buffered output compare/PWM operation. MSxB exists only in the TIM1 channel 0 and TIM2 channel 0 status and control registers.

Setting MS0B disables the channel 1 status and control register and reverts TCH1 to general-purpose I/O.

Reset clears the MSxB bit.

- 1 = Buffered output compare/PWM operation enabled

- 0 = Buffered output compare/PWM operation disabled

## MSxA — Mode Select Bit A

When ELSxB:A  $\neq$  00, this read/write bit selects either input capture operation or unbuffered output compare/PWM operation. See Table 18-3.

- 1 = Unbuffered output compare/PWM operation

- 0 = Input capture operation

When ELSxB:A = 00, this read/write bit selects the initial output level of the TCHx pin. See Table 18-3. Reset clears the MSxA bit.

- 1 = Initial output level low

- 0 = Initial output level high

## NOTE

Before changing a channel function by writing to the MSxB or MSxA bit, set the TSTOP and TRST bits in the TIM status and control register (TSC).