Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | HC08                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | LINbus, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM                                              |

| Number of I/O              | 37                                                         |

| Program Memory Size        | 16KB (16K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 1K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                  |

| Data Converters            | A/D 8x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 48-LQFP                                                    |

| Supplier Device Package    | 48-LQFP (7x7)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908gr16mfae |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Memory

| Addr.         | Register Name                                   |                 | Bit 7     | 6          | 5      | 4           | 3              | 2       | 1                | Bit 0 |

|---------------|-------------------------------------------------|-----------------|-----------|------------|--------|-------------|----------------|---------|------------------|-------|

| \$0035        | Timer 2 Channel 1<br>Register Low (T2CH1L)      | Read:<br>Write: | Bit 7     | 6          | 5      | 4           | 3              | 2       | 1                | Bit 0 |

|               | See page 236.                                   | Reset:          |           |            |        | Indetermina | te after reset |         |                  |       |

| \$0036        | PLL Control Register<br>(PCTL)                  | Read:<br>Write: | PLLIE     | PLLF       | PLLON  | BCS         | PRE1           | PRE0    | VPR1             | VPR0  |

|               | See page 70.                                    | Reset:          | 0         | 0          | 1      | 0           | 0              | 0       | 0                | 0     |

| \$0037        | PLL Bandwidth Control<br>Register (PBWC)        | Read:<br>Write: | AUTO      | LOCK       | ACQ    | 0           | 0              | 0       | 0                | R     |

|               | See page 72.                                    | Reset:          | 0         | 0          | 0      | 0           | 0              | 0       | 0                | 0     |

|               | PLL Multiplier Select High                      | Read:           | 0         | 0          | 0      | 0           | MUL11          | MUL10   | MUL9             | MUL8  |

| \$0038        | Register (PMSH)                                 | Write:          |           |            |        |             | MOLTI          | WOLTO   | MOLS             | MOLO  |

|               | See page 73.                                    | Reset:          | 0         | 0          | 0      | 0           | 0              | 0       | 0                | 0     |

| \$0039        | PLL Multiplier Select Low<br>Register (PMSL)    | Read:<br>Write: | MUL7      | MUL6       | MUL5   | MUL4        | MUL3           | MUL2    | MUL1             | MULO  |

|               | See page 73.                                    | Reset:          | 0         | 1          | 0      | 0           | 0              | 0       | 0                | 0     |

| \$003A        | PLL VCO Select Range<br>Register (PMRS)         | Read:<br>Write: | VRS7      | VRS6       | VRS5   | VRS4        | VRS3           | VRS2    | VRS1             | VRS0  |

|               | See page 74.                                    | Reset:          | 0         | 1          | 0      | 0           | 0              | 0       | 0                | 0     |

| \$003B        | PLL Reference Divider<br>Select Register (PMDS) | Read:<br>Write: | 0         | 0          | 0      | 0           | RDS3           | RDS2    | RDS1             | RDS0  |

|               | See page 74.                                    | Reset:          | 0         | 0          | 0      | 0           | 0              | 0       | 0                | 1     |

| \$003C        | ADC Status and Control<br>Register (ADSCR)      | Read:<br>Write: | COCO<br>R | AIEN       | ADCO   | ADCH4       | ADCH3          | ADCH2   | ADCH1            | ADCH0 |

|               | See page 53.                                    | Reset:          | 0         | 0          | 0      | 1           | 1              | 1       | 1                | 1     |

|               | ADC Data High Register                          | Read:           | 0         | 0          | 0      | 0           | 0              | 0       | AD9              | AD9   |

| \$003D        | (ADRH)                                          | Write:          |           |            |        |             |                |         |                  |       |

|               | See page 55.                                    | Reset:          |           |            |        | Unaffecte   | d by reset     |         |                  |       |

|               | ADC Data Low Register                           | Read:           | AD7       | AD6        | AD5    | AD4         | A3             | AD2     | AD1              | AD0   |

| \$003E        | (ADRL)                                          | Write:          |           |            |        |             |                |         |                  |       |

|               | See page 55.                                    | Reset:          | [         | 1          | 1      | Unaffecte   | d by reset     |         |                  |       |

| \$003F        | ADC Clock Register<br>(ADCLK)                   | Read:<br>Write: | ADIV2     | ADIV1      | ADIV0  | ADICLK      | MODE1          | MODE0   | R                | 0     |

|               | See page 57.                                    | Reset:          | 0         | 0          | 0      | 0           | 0              | 1       | 0                | 0     |

| \$FE00        | Break Status Register<br>(BSR)                  | Read:<br>Write: | R         | R          | R      | R           | R              | R       | SBSW<br>(Note 2) | R     |

| See page 241. |                                                 | Reset:          | 0         | 0          | 0      | 0           | 0              | 0       | 0                | 0     |

| 2. Writing a  | a 0 clears SBSW.                                |                 |           |            |        |             |                |         |                  |       |

|               |                                                 |                 |           | = Unimplem | nented | R           | = Reserved     | U = Una | ffected          |       |

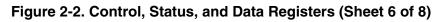

Figure 3-2. ADC Block Diagram

## 3.3.2 Voltage Conversion

When the input voltage to the ADC equals  $V_{REFH}$ , the ADC converts the signal to \$3FF (full scale). If the input voltage equals  $V_{REFL}$ , the ADC converts it to \$000. Input voltages between  $V_{REFH}$  and  $V_{REFL}$  are a straight-line linear conversion.

#### NOTE

The ADC input voltage must always be greater than  $V_{SSAD}$  and less than  $V_{DDAD}$ .

Connect the  $V_{DDAD}$  pin to the same voltage potential as the  $V_{DD}$  pin, and connect the  $V_{SSAD}$  pin to the same voltage potential as the  $V_{SS}$  pin.

The V<sub>DDAD</sub> pin should be routed carefully for maximum noise immunity.

**Clock Generator Module (CGM)**

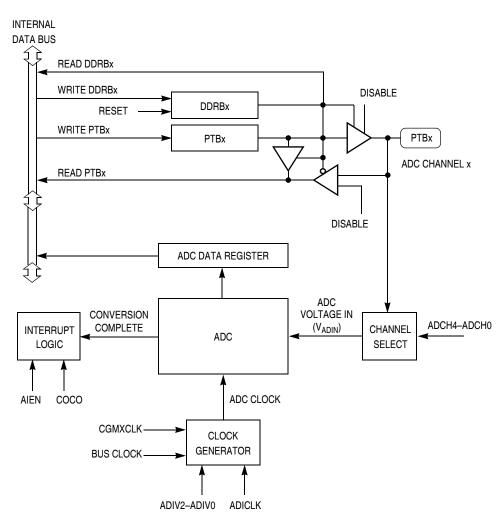

# 4.5.1 PLL Control Register

The PLL control register (PCTL) contains the interrupt enable and flag bits, the on/off switch, the base clock selector bit, the prescaler bits, and the VCO power-of-two range selector bits.

## Figure 4-4. PLL Control Register (PCTL)

## PLLIE — PLL Interrupt Enable Bit

This read/write bit enables the PLL to generate an interrupt request when the LOCK bit toggles, setting the PLL flag, PLLF. When the AUTO bit in the PLL bandwidth control register (PBWC) is clear, PLLIE cannot be written and reads as a 0. Reset clears the PLLIE bit.

1 = PLL interrupts enabled

0 = PLL interrupts disabled

## PLLF — PLL Interrupt Flag Bit

This read-only bit is set whenever the LOCK bit toggles. PLLF generates an interrupt request if the PLLIE bit also is set. PLLF always reads as a 0 when the AUTO bit in the PLL bandwidth control register (PBWC) is clear. Clear the PLLF bit by reading the PLL control register. Reset clears the PLLF bit.

1 = Change in lock condition

0 = No change in lock condition

### NOTE

Do not inadvertently clear the PLLF bit. Any read or read-modify-write operation on the PLL control register clears the PLLF bit.

### PLLON — PLL On Bit

This read/write bit activates the PLL and enables the VCO clock, CGMVCLK. PLLON cannot be cleared if the VCO clock is driving the base clock, CGMOUT (BCS = 1). (See 4.3.8 Base Clock Selector Circuit.) Reset sets this bit so that the loop can stabilize as the MCU is powering up.

1 = PLL on

0 = PLL off

### BCS — Base Clock Select Bit

This read/write bit selects either the crystal oscillator output, CGMXCLK, or the VCO clock, CGMVCLK, as the source of the CGM output, CGMOUT. CGMOUT frequency is one-half the frequency of the selected clock. BCS cannot be set while the PLLON bit is clear. After toggling BCS, it may take up to three CGMXCLK and three CGMVCLK cycles to complete the transition from one source clock to the other. During the transition, CGMOUT is held in stasis. (See 4.3.8 Base Clock Selector Circuit.) Reset clears the BCS bit.

1 = CGMVCLK divided by two drives CGMOUT

0 = CGMXCLK divided by two drives CGMOUT

### NOTE

PLLON and BCS have built-in protection that prevents the base clock selector circuit from selecting the VCO clock as the source of the base clock

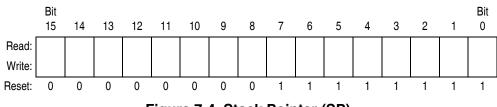

## 7.3.3 Stack Pointer

The stack pointer is a 16-bit register that contains the address of the next location on the stack. During a reset, the stack pointer is preset to \$00FF. The reset stack pointer (RSP) instruction sets the least significant byte to \$FF and does not affect the most significant byte. The stack pointer decrements as data is pushed onto the stack and increments as data is pulled from the stack.

In the stack pointer 8-bit offset and 16-bit offset addressing modes, the stack pointer can function as an index register to access data on the stack. The CPU uses the contents of the stack pointer to determine the conditional address of the operand.

Figure 7-4. Stack Pointer (SP)

#### NOTE

The location of the stack is arbitrary and may be relocated anywhere in random-access memory (RAM). Moving the SP out of page 0 (\$0000 to \$00FF) frees direct address (page 0) space. For correct operation, the stack pointer must point only to RAM locations.

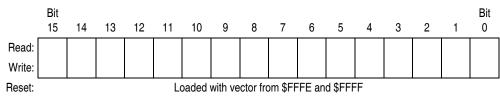

## 7.3.4 Program Counter

The program counter is a 16-bit register that contains the address of the next instruction or operand to be fetched.

Normally, the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, and interrupt operations load the program counter with an address other than that of the next sequential location.

During reset, the program counter is loaded with the reset vector address located at \$FFFE and \$FFFF. The vector address is the address of the first instruction to be executed after exiting the reset state.

Figure 7-5. Program Counter (PC)

**Functional Description**

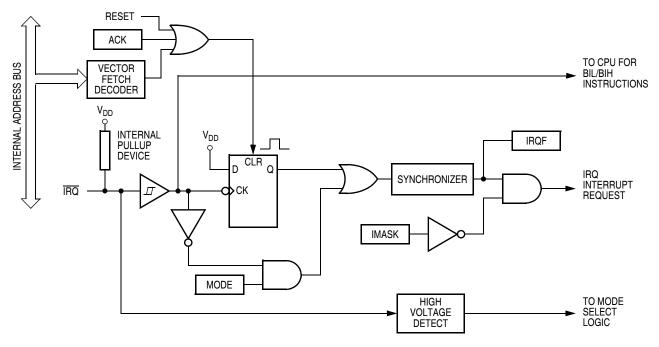

Figure 8-2. IRQ Module Block Diagram

When an interrupt pin is both falling-edge and low-level triggered (MODE = 1), the interrupt remains set until both of these events occur:

- Vector fetch or software clear

- Return of the interrupt pin to 1

The vector fetch or software clear may occur before or after the interrupt pin returns to 1. As long as the pin is low, the interrupt request remains pending. A reset will clear the latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

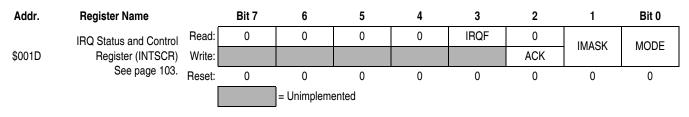

When set, the IMASK bit in the INTSCR mask all external interrupt requests. A latched interrupt request is not presented to the interrupt priority logic unless the IMASK bit is clear.

**NOTE** The interrupt mask (I) in the condition code register (CCR) masks all interrupt requests, including external interrupt requests.

Figure 8-3. IRQ I/O Register Summary

Input/Output Ports (PORTS)

# 12.2 Port A

Port A is an 8-bit special-function port that shares all eight of its pins with the keyboard interrupt (KBI) module. Port A also has software configurable pullup devices if configured as an input port.

## 12.2.1 Port A Data Register

The port A data register (PTA) contains a data latch for each of the eight port A pins.

| Address:                 | \$0000 |      |      |           |            |      |      |       |

|--------------------------|--------|------|------|-----------|------------|------|------|-------|

|                          | Bit 7  | 6    | 5    | 4         | 3          | 2    | 1    | Bit 0 |

| Read:<br>Write:          | PTA7   | PTA6 | PTA5 | PTA4      | PTA3       | PTA2 | PTA1 | PTA0  |

| Reset:                   |        |      |      | Unaffecte | d by reset |      |      |       |

| Alternative<br>Function: | KBD7   | KBD6 | KBD5 | KBD4      | KBD3       | KBD2 | KBD1 | KBD0  |

Figure 12-2. Port A Data Register (PTA)

### PTA7-PTA0 — Port A Data Bits

These read/write bits are software programmable. Data direction of each port A pin is under the control of the corresponding bit in data direction register A. Reset has no effect on port A data.

### KBD7-KBD0 — Keyboard Inputs

The keyboard interrupt enable bits, KBIE7–KBIE0, in the keyboard interrupt control register (KBICR) enable the port A pins as external interrupt pins. See Chapter 9 Keyboard Interrupt Module (KBI).

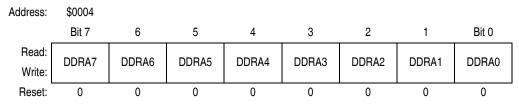

## 12.2.2 Data Direction Register A

Data direction register A (DDRA) determines whether each port A pin is an input or an output. Writing a 1 to a DDRA bit enables the output buffer for the corresponding port A pin; a 0 disables the output buffer.

## DDRA7–DDRA0 — Data Direction Register A Bits

These read/write bits control port A data direction. Reset clears DDRA7–DDRA0, configuring all port A pins as inputs.

1 = Corresponding port A pin configured as output

0 = Corresponding port A pin configured as input

### NOTE

Avoid glitches on port A pins by writing to the port A data register before changing data direction register A bits from 0 to 1.

Figure 12-4 shows the port A I/O logic.

#### Enhanced Serial Communications Interface (ESCI) Module

| RT3, RT5, and RT7 Samples | Start Bit Verification | Noise Flag |

|---------------------------|------------------------|------------|

| 000                       | Yes                    | 0          |

| 001                       | Yes                    | 1          |

| 010                       | Yes                    | 1          |

| 011                       | No                     | 0          |

| 100                       | Yes                    | 1          |

| 101                       | No                     | 0          |

| 110                       | No                     | 0          |

| 111                       | No                     | 0          |

#### Table 14-2. Start Bit Verification

If start bit verification is not successful, the RT clock is reset and a new search for a start bit begins.

To determine the value of a data bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 14-3 summarizes the results of the data bit samples.

| RT8, RT9, and RT10 Samples | Data Bit Determination | Noise Flag |

|----------------------------|------------------------|------------|

| 000                        | 0                      | 0          |

| 001                        | 0                      | 1          |

| 010                        | 0                      | 1          |

| 011                        | 1                      | 1          |

| 100                        | 0                      | 1          |

| 101                        | 1                      | 1          |

| 110                        | 1                      | 1          |

| 111                        | 1                      | 0          |

Table 14-3. Data Bit Recovery

#### NOTE

The RT8, RT9, and RT10 samples do not affect start bit verification. If any or all of the RT8, RT9, and RT10 start bit samples are 1s following a successful start bit verification, the noise flag (NF) is set and the receiver assumes that the bit is a start bit.

To verify a stop bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 14-4 summarizes the results of the stop bit samples.

| RT8, RT9, and RT10 Samples | Framing Error Flag | Noise Flag |

|----------------------------|--------------------|------------|

| 000                        | 1                  | 0          |

| 001                        | 1                  | 1          |

| 010                        | 1                  | 1          |

| 011                        | 0                  | 1          |

| 100                        | 1                  | 1          |

| 101                        | 0                  | 1          |

| 110                        | 0                  | 1          |

| 111                        | 0                  | 0          |

Table 14-4. Stop Bit Recovery

When the ESCI is receiving 8-bit characters, R8 is a copy of the eighth bit (bit 7). Reset has no effect on the R8 bit.

#### T8 — Transmitted Bit 8

When the ESCI is transmitting 9-bit characters, T8 is the read/write ninth bit (bit 8) of the transmitted character. T8 is loaded into the transmit shift register at the same time that the SCDR is loaded into the transmit shift register. Reset clears the T8 bit.

#### **ORIE** — Receiver Overrun Interrupt Enable Bit

This read/write bit enables ESCI error CPU interrupt requests generated by the receiver overrun bit, OR. Reset clears ORIE.

- 1 = ESCI error CPU interrupt requests from OR bit enabled

- 0 = ESCI error CPU interrupt requests from OR bit disabled

#### NEIE — Receiver Noise Error Interrupt Enable Bit

This read/write bit enables ESCI error CPU interrupt requests generated by the noise error bit, NE. Reset clears NEIE.

1 = ESCI error CPU interrupt requests from NE bit enabled

0 = ESCI error CPU interrupt requests from NE bit disabled

#### FEIE — Receiver Framing Error Interrupt Enable Bit

This read/write bit enables ESCI error CPU interrupt requests generated by the framing error bit, FE. Reset clears FEIE.

1 = ESCI error CPU interrupt requests from FE bit enabled

0 = ESCI error CPU interrupt requests from FE bit disabled

#### PEIE — Receiver Parity Error Interrupt Enable Bit

This read/write bit enables ESCI receiver CPU interrupt requests generated by the parity error bit, PE. Reset clears PEIE.

1 = ESCI error CPU interrupt requests from PE bit enabled

0 = ESCI error CPU interrupt requests from PE bit disabled

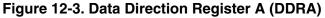

## 14.8.4 ESCI Status Register 1

ESCI status register 1 (SCS1) contains flags to signal these conditions:

- Transfer of SCDR data to transmit shift register complete

- Transmission complete

- Transfer of receive shift register data to SCDR complete

- Receiver input idle

- Receiver overrun

- Noisy data

- Framing error

- Parity error

Figure 14-13. ESCI Status Register 1 (SCS1)

#### Enhanced Serial Communications Interface (ESCI) Module

### SCTE — ESCI Transmitter Empty Bit

This clearable, read-only bit is set when the SCDR transfers a character to the transmit shift register. SCTE can generate an ESCI transmitter CPU interrupt request. When the SCTIE bit in SCC2 is set, SCTE generates an ESCI transmitter CPU interrupt request. In normal operation, clear the SCTE bit by reading SCS1 with SCTE set and then writing to SCDR. Reset sets the SCTE bit.

- 1 = SCDR data transferred to transmit shift register

- 0 = SCDR data not transferred to transmit shift register

### TC — Transmission Complete Bit

This read-only bit is set when the SCTE bit is set, and no data, preamble, or break character is being transmitted. TC generates an ESCI transmitter CPU interrupt request if the TCIE bit in SCC2 is also set. TC is cleared automatically when data, preamble, or break is queued and ready to be sent. There may be up to 1.5 transmitter clocks of latency between queueing data, preamble, and break and the transmission actually starting. Reset sets the TC bit.

- 1 = No transmission in progress

- 0 = Transmission in progress

### SCRF — ESCI Receiver Full Bit

This clearable, read-only bit is set when the data in the receive shift register transfers to the ESCI data register. SCRF can generate an ESCI receiver CPU interrupt request. When the SCRIE bit in SCC2 is set the SCRF generates a CPU interrupt request. In normal operation, clear the SCRF bit by reading SCS1 with SCRF set and then reading the SCDR. Reset clears SCRF.

- 1 = Received data available in SCDR

- 0 = Data not available in SCDR

### IDLE — Receiver Idle Bit

This clearable, read-only bit is set when 10 or 11 consecutive 1s appear on the receiver input. IDLE generates an ESCI receiver CPU interrupt request if the ILIE bit in SCC2 is also set. Clear the IDLE bit by reading SCS1 with IDLE set and then reading the SCDR. After the receiver is enabled, it must receive a valid character that sets the SCRF bit before an idle condition can set the IDLE bit. Also, after the IDLE bit has been cleared, a valid character must again set the SCRF bit before an idle condition can set the IDLE bit. Reset clears the IDLE bit.

- 1 = Receiver input idle

- 0 = Receiver input active (or idle since the IDLE bit was cleared)

### **OR** — Receiver Overrun Bit

This clearable, read-only bit is set when software fails to read the SCDR before the receive shift register receives the next character. The OR bit generates an ESCI error CPU interrupt request if the ORIE bit in SCC3 is also set. The data in the shift register is lost, but the data already in the SCDR is not affected. Clear the OR bit by reading SCS1 with OR set and then reading the SCDR. Reset clears the OR bit.

- 1 = Receive shift register full and SCRF = 1

- 0 = No receiver overrun

Software latency may allow an overrun to occur between reads of SCS1 and SCDR in the flag-clearing sequence. Figure 14-14 shows the normal flag-clearing sequence and an example of an overrun caused by a delayed flag-clearing sequence. The delayed read of SCDR does not clear the OR bit because OR was not set when SCS1 was read. Byte 2 caused the overrun and is lost. The next flag-clearing sequence reads byte 3 in the SCDR instead of byte 2.

Enhanced Serial Communications Interface (ESCI) Module

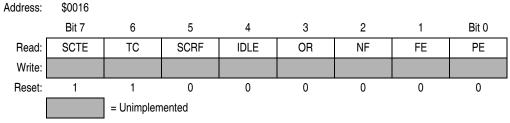

Figure 14-23. Bit Time Measurement with ACLK = 1, Scenario B

## 14.9.4 Arbitration Mode

If AM[1:0] is set to 10, the arbiter module operates in arbitration mode. On every rising edge of SCI\_TxD (output of the ESCI module, internal chip signal), the counter is started. When the counter reaches \$38 (ACLK = 0) or \$08 (ACLK = 1), RxD is statically sensed. If in this case, RxD is sensed low (for example, another bus is driving the bus dominant) ALOST is set. As long as ALOST is set, the TxD pin is forced to 1, resulting in a seized transmission.

If SCI\_TxD is sensed 0 without having sensed a 0 before on RxD, the counter will be reset, arbitration operation will be restarted after the next rising edge of SCI\_TxD.

**Reset and System Initialization**

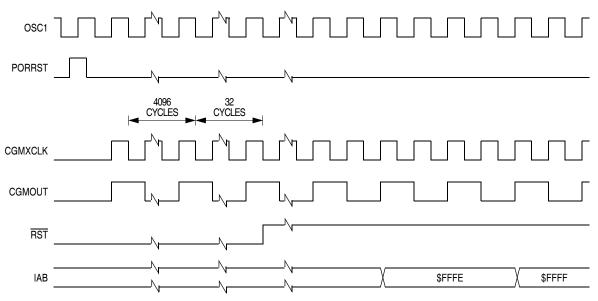

### Figure 15-8. POR Recovery

## 15.3.2.2 Computer Operating Properly (COP) Reset

An input to the SIM is reserved for the COP reset signal. The overflow of the COP counter causes an internal reset and sets the COP bit in the SIM reset status register (SRSR). The SIM actively pulls down the RST pin for all internal reset sources.

The COP module is disabled if the  $\overline{\text{RST}}$  pin or the  $\overline{\text{IRQ}}$  pin is held at V<sub>TST</sub> while the MCU is in monitor mode. The COP module can be disabled only through combinational logic conditioned with the high voltage signal on the  $\overline{\text{RST}}$  or the  $\overline{\text{IRQ}}$  pin. This prevents the COP from becoming disabled as a result of external noise. During a break state, V<sub>TST</sub> on the  $\overline{\text{RST}}$  pin disables the COP module.

### 15.3.2.3 Illegal Opcode Reset

The SIM decodes signals from the CPU to detect illegal instructions. An illegal instruction sets the ILOP bit in the SIM reset status register (SRSR) and causes a reset.

If the stop enable bit, STOP, in the mask option register is 0, the SIM treats the STOP instruction as an illegal opcode and causes an illegal opcode reset. The SIM actively pulls down the  $\overline{\text{RST}}$  pin for all internal reset sources.

#### 15.3.2.4 Illegal Address Reset

An opcode fetch from an unmapped address generates an illegal address reset. The SIM verifies that the CPU is fetching an opcode prior to asserting the ILAD bit in the SIM reset status register (SRSR) and resetting the MCU. A data fetch from an unmapped address does not generate a reset. The SIM actively pulls down the RST pin for all internal reset sources.

#### 15.3.2.5 Low-Voltage Inhibit (LVI) Reset

The low-voltage inhibit module (LVI) asserts its output to the SIM when the  $V_{DD}$  voltage falls to the  $LVI_{TRIPF}$  voltage. The LVI bit in the SIM reset status register (SRSR) is set, and the external reset pin (RST) is held low while the SIM counter counts out 4096 + 32 CGMXCLK cycles.

#### System Integration Module (SIM)

| Priority | Interrupt Source        | Interrupt Status Register Flag |

|----------|-------------------------|--------------------------------|

| lighest  | Reset                   |                                |

| <b>A</b> | SWI instruction         | _                              |

| Î        | IRQ pin                 | l1                             |

|          | CGM clock monitor       | 12                             |

|          | TIM1 channel 0          | 13                             |

|          | TIM1 channel 1          | 14                             |

|          | TIM1 overflow           | 15                             |

|          | TIM2 channel 0          | 16                             |

|          | TIM2 channel 1          | 17                             |

|          | TIM2 overflow           | 18                             |

|          | SPI receiver full       | 19                             |

|          | SPI transmitter empty   | 110                            |

|          | SCI receive error       | l11                            |

|          | SCI receive             | 112                            |

|          | SCI transmit            | 113                            |

|          | Keyboard                | 114                            |

| *        | ADC conversion complete | 115                            |

| owest    | Timebase module         | l16                            |

#### Table 15-3. Interrupt Sources

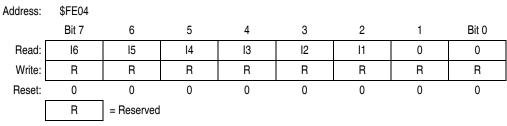

#### Interrupt Status Register 1

## Figure 15-13. Interrupt Status Register 1 (INT1)

#### I6–I1 — Interrupt Flags 1–6

These flags indicate the presence of interrupt requests from the sources shown in Table 15-3.

1 = Interrupt request present

0 = No interrupt request present

## Bit 0 and Bit 1 — Always read 0

#### **Transmission Formats**

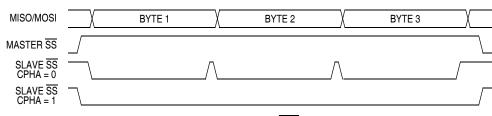

Figure 16-6. CPHA/SS Timing

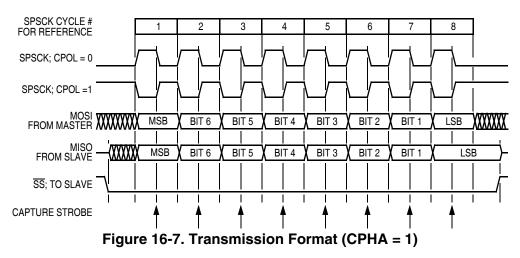

## 16.5.3 Transmission Format When CPHA = 1

Figure 16-7 shows an SPI transmission in which CPHA is 1. The figure should not be used as a replacement for data sheet parametric information. Two waveforms are shown for SPSCK: one for CPOL = 0 and another for CPOL = 1. The diagram may be interpreted as a master or slave timing diagram since the serial clock (SPSCK), master in/slave out (MISO), and master out/slave in (MOSI) pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The  $\overline{SS}$  line is the slave select input to the slave. The slave SPI drives its MISO output only when its slave select input ( $\overline{SS}$ ) is at 0, so that only the selected slave drives to the master. The  $\overline{SS}$  pin of the master is not shown but is assumed to be inactive. The  $\overline{SS}$  pin of the master must be high or must be reconfigured as general-purpose I/O not affecting the SPI. (See 16.7.2 Mode Fault Error.) When CPHA = 1, the master begins driving its MOSI pin on the first SPSCK edge. Therefore, the slave uses the first SPSCK edge as a start transmission signal. The  $\overline{SS}$  pin can remain low between transmissions. This format may be preferable in systems having only one master and only one slave driving the MISO data line.

When CPHA = 1 for a slave, the first edge of the SPSCK indicates the beginning of the transmission. This causes the SPI to leave its idle state and begin driving the MISO pin with the MSB of its data. Once the transmission begins, no new data is allowed into the shift register from the transmit data register. Therefore, the SPI data register of the slave must be loaded with transmit data before the first edge of SPSCK. Any data written after the first edge is stored in the transmit data register and transferred to the shift register after the current transmission.

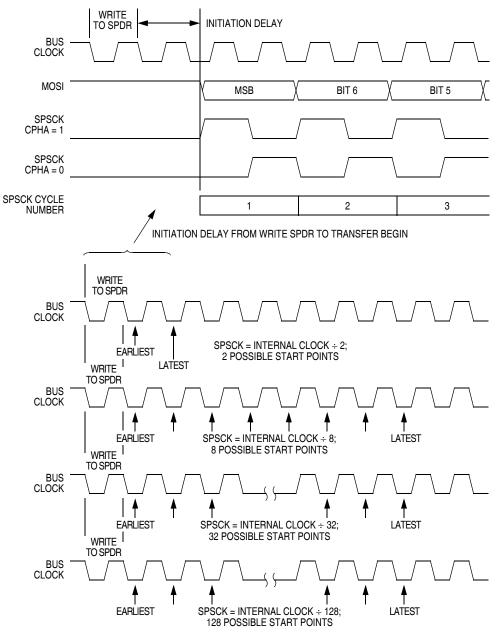

## 16.5.4 Transmission Initiation Latency

When the SPI is configured as a master (SPMSTR = 1), writing to the SPDR starts a transmission. CPHA has no effect on the delay to the start of the transmission, but it does affect the initial state of the SPSCK

#### Serial Peripheral Interface (SPI) Module

signal. When CPHA = 0, the SPSCK signal remains inactive for the first half of the first SPSCK cycle. When CPHA = 1, the first SPSCK cycle begins with an edge on the SPSCK line from its inactive to its active level. The SPI clock rate (selected by SPR1:SPR0) affects the delay from the write to SPDR and the start of the SPI transmission. (See Figure 16-8.) The internal SPI clock in the master is a free-running derivative of the internal MCU clock. To conserve power, it is enabled only when both the SPE and SPMSTR bits are set. SPSCK edges occur halfway through the low time of the internal MCU clock. Since the SPI clock is free-running, it is uncertain where the write to the SPDR occurs relative to the slower SPSCK. This uncertainty causes the variation in the initiation delay shown in Figure 16-8. This delay is no longer than a single SPI bit time. That is, the maximum delay is two MCU bus cycles for DIV2, eight MCU bus cycles for DIV8, 32 MCU bus cycles for DIV32, and 128 MCU bus cycles for DIV128.

Figure 16-8. Transmission Start Delay (Master)

Serial Peripheral Interface (SPI) Module

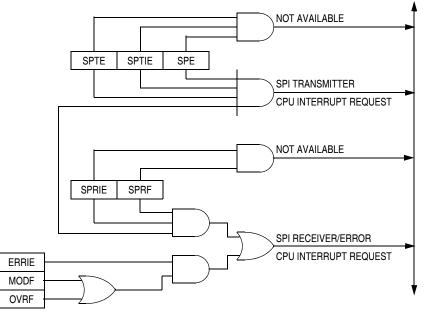

Figure 16-12. SPI Interrupt Request Generation

# 16.9 Resetting the SPI

Any system reset completely resets the SPI. Partial resets occur whenever the SPI enable bit (SPE) is low. Whenever SPE is low, the following occurs:

- The SPTE flag is set.

- Any transmission currently in progress is aborted.

- The shift register is cleared.

- The SPI state counter is cleared, making it ready for a new complete transmission.

- All the SPI port logic is defaulted back to being general-purpose I/O.

These items are reset only by a system reset:

- All control bits in the SPCR register

- All control bits in the SPSCR register (MODFEN, ERRIE, SPR1, and SPR0)

- The status flags SPRF, OVRF, and MODF

By not resetting the control bits when SPE is low, the user can clear SPE between transmissions without having to set all control bits again when SPE is set back high for the next transmission.

By not resetting the SPRF, OVRF, and MODF flags, the user can still service these interrupts after the SPI has been disabled. The user can disable the SPI by writing 0 to the SPE bit. The SPI can also be disabled by a mode fault occurring in an SPI that was configured as a master with the MODFEN bit set.

# 16.10 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### Timebase Module (TBM)

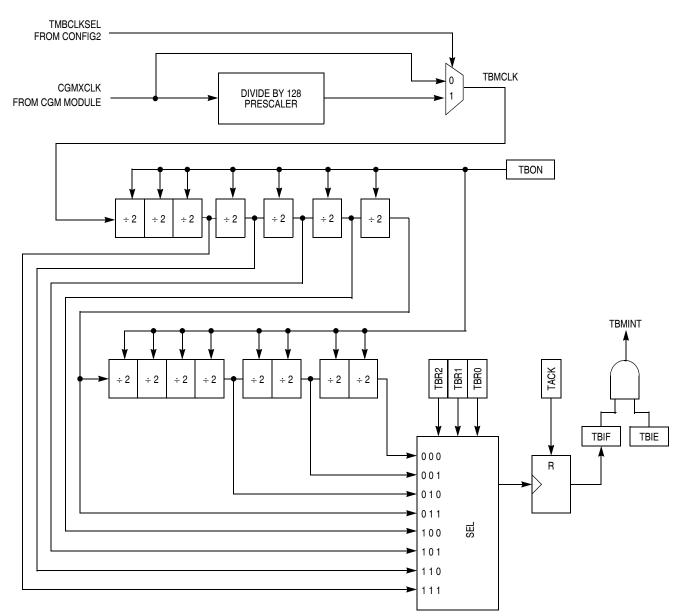

Figure 17-1. Timebase Block Diagram

## 17.5 TBM Interrupt Rate

The interrupt rate is determined by the equation:

$t_{\text{TBMRATE}} = \frac{1}{f_{\text{TBMRATE}}} = \frac{\text{Divider}}{f_{\text{TBMCLK}}}$

where:

f<sub>TBMCLK</sub> = Frequency supplied from the clock generator (CGM) module

Divider = Divider value as determined by TBR2–TBR0 settings, see Table 17-1

Development Support

# 19.3 Monitor ROM (MON)

This section describes the monitor ROM (MON) and the monitor mode entry methods. The monitor ROM allows complete testing of the microcontroller unit (MCU) through a single-wire interface with a host computer. Monitor mode entry can be achieved without use of the higher test voltage,  $V_{TST}$ , as long as vector addresses \$FFFE and \$FFFF are blank, thus reducing the hardware requirements for in-circuit programming.

Features of the monitor ROM include:

- Normal user-mode pin functionality

- One pin dedicated to serial communication between monitor read-only memory (ROM) and host computer

- Standard mark/space non-return-to-zero (NRZ) communication with host computer

- Standard communication baud rate (9,600 @ 2.4576-MHz bus frequency)

- Execution of code in random-access memory (RAM) or FLASH

- FLASH memory security feature<sup>(1)</sup>

- FLASH memory programming interface

- 350 bytes monitor ROM code size (\$FE20 to \$FF6A)

- Monitor mode entry without high voltage, V<sub>TST</sub>, if reset vector is blank (\$FFFE and \$FFFF contain \$FF)

- Normal monitor mode entry if high voltage is applied to IRQ

## 19.3.1 Functional Description

Figure 19-9 shows a simplified diagram of the monitor mode.

The monitor ROM receives and executes commands from a host computer.

Figure 19-10 and Figure 19-11 show example circuits used to enter monitor mode and communicate with a host computer via a standard RS-232 interface.

Simple monitor commands can access any memory address. In monitor mode, the MCU can execute code downloaded into RAM by a host computer while most MCU pins retain normal operating mode functions. All communication between the host computer and the MCU is through the PTA0 pin. A level-shifting and multiplexing interface is required between PTA0 and the host computer. PTA0 is used in a wired-OR configuration and requires a pullup resistor.

Table 19-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a power-on reset (POR) and will allow communication at 14,400 baud provided one of the following sets of conditions is met:

- If \$FFFE and \$FFFF does not contain \$FF (programmed state):

- The external clock is 4.9152 MHz

- <u>PTB</u>4 = low

- IRQ = V<sub>TST</sub>

- If \$FFFE and \$FFFF do not contain \$FF (programmed state):

- The external clock is 9.8304 MHz

- PTB4 = high

- IRQ = V<sub>TST</sub>

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

# 20.6 3.3-Vdc Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                                                                                                                                          | Symbol                                                                    | Min                                                                     | Typ <sup>(2)</sup>          | Мах                | Unit                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------|--------------------|----------------------|

| Output high voltage<br>$(I_{Load} = -0.6 \text{ mA}) \text{ all I/O pins}$<br>$(I_{Load} = -4.0 \text{ mA}) \text{ all I/O pins}$<br>$(I_{Load} = -10.0 \text{ mA}) \text{ pins PTCO-PTC4 only}$                       | V <sub>OH</sub><br>V <sub>OH</sub><br>V <sub>OH</sub>                     | V <sub>DD</sub> – 0.3<br>V <sub>DD</sub> – 1.0<br>V <sub>DD</sub> – 1.0 |                             |                    | V<br>V<br>V          |

| Maximum combined I <sub>OH</sub> for port PTA7–PTA3,<br>port PTC0–PTC1, port E, port PTD0–PTD3                                                                                                                         | I <sub>OH1</sub>                                                          | -                                                                       | _                           | 30                 | mA                   |

| Maximum combined I <sub>OH</sub> for port PTA2–PTA0,<br>port B, port PTC2–PTC6, port PTD4–PTD7                                                                                                                         | I <sub>OH2</sub>                                                          | —                                                                       | _                           | 30                 | mA                   |

| Maximum total I <sub>OH</sub> for all port pins                                                                                                                                                                        | I <sub>OHT</sub>                                                          | —                                                                       | —                           | 60                 | mA                   |

| Output low voltage<br>(I <sub>Load</sub> = 1.6 mA) all I/O pins<br>(I <sub>Load</sub> = 10 mA) all I/O pins<br>(I <sub>Load</sub> = 20 mA) pins PTC0–PTC4 only<br>Maximum combined I <sub>OH</sub> for port PTA7–PTA3, | V <sub>OL</sub><br>V <sub>OL</sub><br>V <sub>OL</sub><br>I <sub>OL1</sub> | <br>                                                                    |                             | 0.3<br>1.0<br>0.8  | V<br>V<br>V          |

| port PTC0–PTC1, port E, port PTD0–PTD3<br>Maximum combined I <sub>OH</sub> for port PTA2–PTA0,<br>port B, port PTC2–PTC6, port PTD4–PTD7                                                                               | I <sub>OL2</sub>                                                          | _                                                                       | _                           | 30<br>30           | mA<br>mA             |

| Maximum total I <sub>OL</sub> for all port pins                                                                                                                                                                        | I <sub>OLT</sub>                                                          | —                                                                       | —                           | 60                 | mA                   |

| Input high voltage<br>All ports, IRQ, RST, OSC1                                                                                                                                                                        | V <sub>IH</sub>                                                           | $0.7 	imes V_{DD}$                                                      | —                           | $V_{DD}$           | v                    |

| Input low voltage<br>All ports, IRQ, RST, OSC1                                                                                                                                                                         | V <sub>IL</sub>                                                           | V <sub>SS</sub>                                                         | _                           | $0.3\times V_{DD}$ | V                    |

| V <sub>DD</sub> supply current<br>Run <sup>(3)</sup><br>Wait <sup>(4)</sup><br>Stop <sup>(5)</sup>                                                                                                                     |                                                                           |                                                                         | 8<br>3                      | 12<br>6            | mA<br>mA             |

| 25°C<br>25°C with TBM enabled <sup>(6)</sup><br>25°C with LVI and TBM enabled <sup>(6)</sup><br>–40°C to 125°C with TBM enabled <sup>(6)</sup><br>–40°C to 125°C with LVI and TBM enabled <sup>(6)</sup>               | I <sub>DD</sub>                                                           | <br><br>                                                                | 2<br>12<br>200<br>30<br>300 | <br><br>           | μΑ<br>μΑ<br>μΑ<br>μΑ |

| DC injection current, all ports                                                                                                                                                                                        | I <sub>INJ</sub>                                                          | -2                                                                      | —                           | +2                 | mA                   |

| Total dc current injection (sum of all I/O)                                                                                                                                                                            | I <sub>INJTOT</sub>                                                       | -25                                                                     | —                           | +25                | mA                   |

| I/O ports Hi-Z leakage current <sup>(7)</sup>                                                                                                                                                                          | IIL                                                                       | -10                                                                     | —                           | +10                | μA                   |

| Input current                                                                                                                                                                                                          | I <sub>In</sub>                                                           | -1                                                                      | —                           | +1                 | μA                   |

| Pullup resistors (as input only)<br>Ports PTA7/KBD7–PTA0/KBD0, PTC6–PTC0,<br>PTD7/T2CH1–PTD0/SS                                                                                                                        | R <sub>PU</sub>                                                           | 20                                                                      | 45                          | 65                 | kΩ                   |

| Capacitance<br>Ports (as input or output)                                                                                                                                                                              | C <sub>Out</sub><br>C <sub>In</sub>                                       |                                                                         |                             | 12<br>8            | pF                   |

Continued on next page

NOTES:

- 1. DIMENSIONS AND TOLERANCING PER ASME Y14.5M-1994.

- 2. CONTROLLING DIMENSION: MILLIMETER.

- 3. DATUM PLANE AB IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

- 4. DATUMS T, U, AND Z TO BE DETERMINED AT DATUM PLANE AB.

$\mathbf{X}$  dimensions to be determined at seating plane ac.

6. DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.250 PER SIDE. DIMENSIONS DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE AB.

THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.350.

8. MINIMUM SOLDER PLATE THICKNESS SHALL BE 0.0076.

9. EXACT SHAPE OF EACH CORNER IS OPTIONAL.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | LOUTLINE                   | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|----------------------------|------------------|-------------|

| TITLE:                                                  |           | DOCUMENT NO                | ): 98ASH00962A   | REV: G      |

| LQFP, 48 LEAD, 0.50 PITCH<br>(7.0 X 7.0 X 1.4)          |           | CASE NUMBER: 932–03 14 APF |                  | 14 APR 2005 |

|                                                         | 1.4)      | STANDARD: JE               | DEC MS-026-BBC   |             |

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2004, 2007. All rights reserved.

MC68HC908GR16 Rev. 5.0, 04/2007