Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Active                                                     |

| Core Processor             | HC08                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | LINbus, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM                                              |

| Number of I/O              | 37                                                         |

| Program Memory Size        | 16KB (16K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 1K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                  |

| Data Converters            | A/D 8x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 48-LQFP                                                    |

| Supplier Device Package    | 48-LQFP (7x7)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908gr16vfae |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Revision History**

# **Revision History (Continued)**

| Date               | Revision<br>Level | Description                                                                                                                                                                                                | Page<br>Number(s) |

|--------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

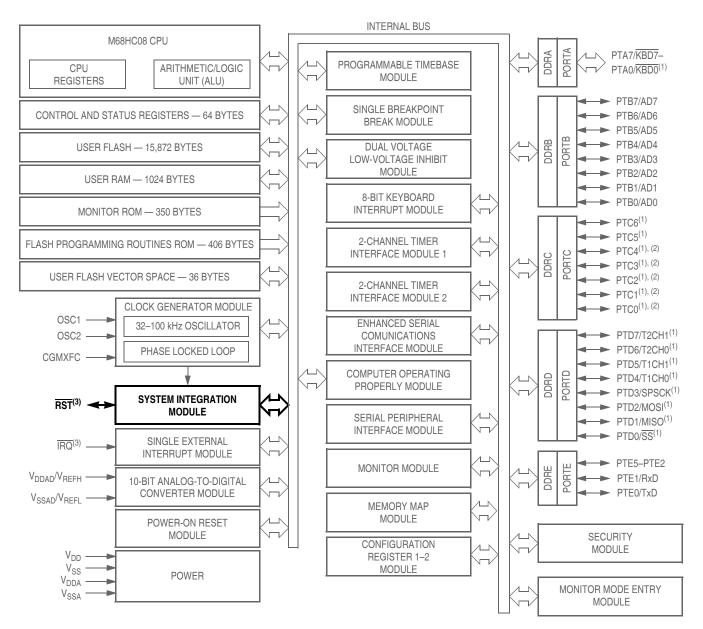

|                    |                   | Figure 1-1. MCU Block Diagram — Removed data bus switch module                                                                                                                                             | 22                |

|                    |                   | Figure 2-2. Control, Status, and Data Registers and Figure 5-1. Configuration<br>Register 2 (CONFIG2) — Changed name of bit 0 from SCIBDSRC to<br>ESCIBDSRC                                                | 29<br>and<br>78   |

|                    |                   | 14.8.8 ESCI Prescaler Register — Updated description in this subsection                                                                                                                                    | 168               |

| Sontombor          |                   | 14.9.1 ESCI Arbiter Control Register — Updated description of ACLK bit                                                                                                                                     | 172               |

| September,<br>2004 | 2.0               | 14.9.3 Bit Time Measurement — Updated bit time measurement mode for ACLK = 0                                                                                                                               | 173               |

|                    |                   | Added dc injection current values to:<br>20.5 5.0-Vdc Electrical Characteristics<br>20.6 3.3-Vdc Electrical Characteristics                                                                                | 253<br>255        |

|                    |                   | 20.9.1 CGM Component Specifications — Corrected series resistor values                                                                                                                                     | 258               |

|                    |                   | 20.15 Memory Characteristics — Table updated to reflect new values                                                                                                                                         | 265               |

| March,             | 2.0               | 10.5 Clock Generator Module (CGM) — Updated description to remove erroneous information.                                                                                                                   | 112               |

| 2005               | 3.0               | 20.9 Clock Generation Module Characteristics — Updated to reflect correct values.                                                                                                                          | 260               |

|                    |                   | Table 13-2. Interrupt Source Flags — Changed IF7 to TIM2 channel instead of Reserved.                                                                                                                      | 144               |

| January,<br>2007   | 4.0               | Table 2-1. Vector Addresses — Changed address \$FFEE to TIM2 Channel 1   Vector (High) and \$FFEF to TIM2 Channel 1 Vector (Low) from Reserved                                                             | 37                |

|                    |                   | Figure 2-2. Control, Status, and Data Registers — Changed addresses \$0033 to \$0035 to show TIM2 Channel 1 registers.                                                                                     | 29                |

|                    |                   | Figure 2-2. Control, Status, and Data Registers — Replaced TMCLKSEL with TMBCLKSEL to be compatile with development tool nomenclature                                                                      | 32                |

|                    |                   | Chapter 5 Configuration Register (CONFIG) — Changed COPCLK to CGMXCLK, replaced TMCLKSEL with TMBCLKSEL to be compatible with development tool nomenclature, and replaced exponents for COP timeout period | 79                |

|                    |                   | 6.2 Functional Description — Replaced exponents for COP timeout period                                                                                                                                     | 84                |

| April,             |                   | 10.6.2 Stop Mode — Changed COPCLK to CGMXCLK                                                                                                                                                               | 113               |

| 2007               | 5.0               | Figure 14-2. ESCI Module Block Diagram — Replaced BUS_CLK with BUS CLOCK and removed reference to rx BUSCLK                                                                                                | 149               |

|                    |                   | Figure 14-5. ESCI Transmitter and Figure 14-6. ESCI Receiver Block<br>Diagram — Added CGMXCLK OR to BUS CLOCK designator                                                                                   | 151<br>154        |

|                    |                   | 14.8.7 ESCI Baud Rate Register — Replaced description of the LINT and LINR bits                                                                                                                            | 169               |

|                    |                   | Figure 17-1 . Timebase Block Diagram and 17.5 TBM Interrupt Rate—<br>Replaced TBMCLKSEL with TMBCLKSEL to be compatible with<br>development tool nomenclature                                              | 218<br>219        |

# **Table of Contents**

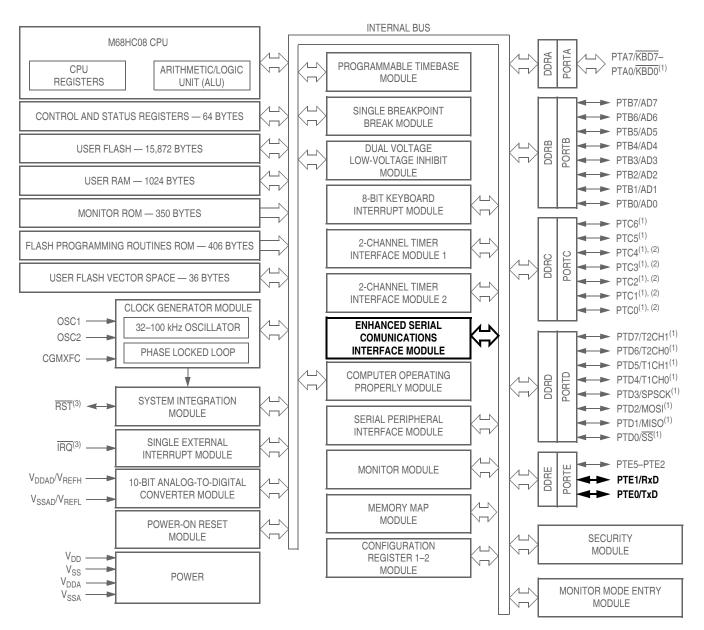

## Chapter 1 General Description

|                                                                                                                  | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| -                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Pin Functions                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Power Supply Pins (V <sub>DD</sub> and V <sub>SS</sub> )                                                         | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Oscillator Pins (OSC1 and OSC2)                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| External Reset Pin (RST)                                                                                         | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| External Interrupt Pin (IRQ)                                                                                     | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CGM Power Supply Pins (V <sub>DDA</sub> and V <sub>SSA</sub> )                                                   | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| External Filter Capacitor Pin (V <sub>CGMXFC</sub> )                                                             | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ADC Power Supply/Reference Pins (V <sub>DDAD</sub> /V <sub>REFH</sub> and V <sub>SSAD</sub> /V <sub>REFL</sub> ) | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Port A Input/Output (I/O) Pins (PTA7/KBD7–PTA0/KBD0)                                                             | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Port B I/O Pins (PTB7/AD7–PTB0/AD0)                                                                              | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Port C I/O Pins (PTC6–PTC0)                                                                                      | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Port D I/O Pins (PTD7/T2CH1–PTD0/SS)                                                                             | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Port E I/O Pins (PTE5–PTE2 and PTE0/TxD)                                                                         | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                  | Power Supply Pins (V <sub>DD</sub> and V <sub>SS</sub> ).   Oscillator Pins (OSC1 and OSC2).   External Reset Pin (RST).   External Interrupt Pin (IRQ)   CGM Power Supply Pins (V <sub>DDA</sub> and V <sub>SSA</sub> ).   External Filter Capacitor Pin (V <sub>CGMXFC</sub> )   ADC Power Supply/Reference Pins (V <sub>DDAD</sub> /V <sub>REFH</sub> and V <sub>SSAD</sub> /V <sub>REFL</sub> ).   Port A Input/Output (I/O) Pins (PTA7/KBD7–PTA0/KBD0)   Port B I/O Pins (PTB7/AD7–PTB0/AD0)   Port D I/O Pins (PTD7/T2CH1–PTD0/SS) |

# Chapter 2 Memory

| 2.1     | Introduction                      |

|---------|-----------------------------------|

| 2.2     | Unimplemented Memory Locations 27 |

| 2.3     | Reserved Memory Locations         |

| 2.4     | Input/Output (I/O) Section        |

| 2.5     | Random-Access Memory (RAM)        |

| 2.6     | FLASH Memory (FLASH)              |

| 2.6.1   | Functional Description            |

| 2.6.1.1 | FLASH Control Register            |

| 2.6.1.2 | FLASH Page Erase Operation 40     |

| 2.6.1.3 | FLASH Mass Erase Operation 41     |

| 2.6.1.4 | FLASH Program/Read Operation 41   |

| 2.6.1.5 |                                   |

| 2.6.1.6 | FLASH Block Protect Register 44   |

| 2.6.2   | Wait Mode                         |

| 2.6.3   | Stop Mode                         |

## 3.8.3 ADC Clock Register

\$003F Address: Bit 7 6 5 4 3 2 Bit 0 1 0 Read: ADIV1 ADIV0 MODE0 ADIV2 ADICLK MODE1 R Write: 0 0 0 0 1 0 0 Reset: 0 = Unimplemented R = Reserved

The ADC clock register (ADCLK) selects the clock frequency for the ADC.

Figure 3-9. ADC Clock Register (ADCLK)

### ADIV2–ADIV0 — ADC Clock Prescaler Bits

ADIV2–ADIV0 form a 3-bit field which selects the divide ratio used by the ADC to generate the internal ADC clock. Table 3-2 shows the available clock configurations. The ADC clock should be set to approximately 1 MHz.

| ADIV2 | ADIV1            | ADIV0 ADC Clock Rate  |                      |  |  |

|-------|------------------|-----------------------|----------------------|--|--|

| 0     | 0                | 0                     | ADC input clock ÷ 1  |  |  |

| 0     | 0                | 1 ADC input clock ÷ 2 |                      |  |  |

| 0     | 1                | 0 ADC input clock ÷ 4 |                      |  |  |

| 0     | 1                | 1                     | ADC input clock ÷ 8  |  |  |

| 1     | X <sup>(1)</sup> | X <sup>(1)</sup>      | ADC input clock ÷ 16 |  |  |

Table 3-2. ADC Clock Divide Ratio

1. X = Don't care

### ADICLK — ADC Input Clock Select Bit

ADICLK selects either the bus clock or the oscillator output clock (CGMXCLK) as the input clock source to generate the internal ADC clock. Reset selects CGMXCLK as the ADC clock source.

1 = Internal bus clock

0 = Oscillator output clock (CGMXCLK)

The ADC requires a clock rate of approximately 1 MHz for correct operation. If the selected clock source is not fast enough, the ADC will generate incorrect conversions. See 20.10 5.0-Volt ADC Characteristics and 20.11 3.3-Volt ADC Characteristics.

$$f_{ADIC} = \frac{f_{CGMXCLK} \text{ or bus frequency}}{ADIV[2:0]} \cong 1 \text{ MHz}$$

### MODE1 and MODE0 — Modes of Result Justification Bits

MODE1 and MODE0 select among four modes of operation. The manner in which the ADC conversion results will be placed in the ADC data registers is controlled by these modes of operation. Reset returns right-justified mode.

00 = 8-bit truncation mode

01 = Right justified mode

10 = Left justified mode

11 = Left justified signed data mode

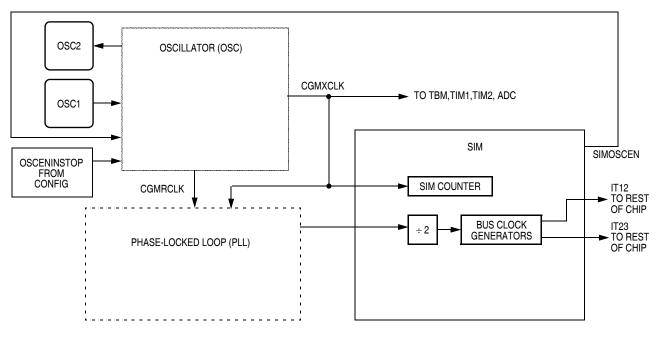

# Chapter 4 Clock Generator Module (CGM)

# 4.1 Introduction

This section describes the clock generator module. The CGM generates the crystal clock signal, CGMXCLK, which operates at the frequency of the crystal. The CGM also generates the base clock signal, CGMOUT, which is based on either the crystal clock divided by two or the phase-locked loop (PLL) clock, CGMVCLK, divided by two. In user mode, CGMOUT is the clock from which the SIM derives the system clocks, including the bus clock, which is at a frequency of CGMOUT/2. In monitor mode, PTC3 determines the bus clock. The PLL is a fully functional frequency generator designed for use with crystals or ceramic resonators. The PLL can generate an 8-MHz bus frequency using a 32-kHz crystal.

## 4.2 Features

Features of the CGM include:

- Phase-locked loop with output frequency in integer multiples of an integer dividend of the crystal reference

- Low-frequency crystal operation with low-power operation and high-output frequency resolution

- Programmable prescaler for power-of-two increases in frequency

- Programmable hardware voltage-controlled oscillator (VCO) for low-jitter operation

- Automatic bandwidth control mode for low-jitter operation

- Automatic frequency lock detector

- CPU interrupt on entry or exit from locked condition

- Configuration register bit to allow oscillator operation during stop mode

# 4.3 Functional Description

The CGM consists of three major submodules:

- Crystal oscillator circuit The crystal oscillator circuit generates the constant crystal frequency clock, CGMXCLK.

- Phase-locked loop (PLL) The PLL generates the programmable VCO frequency clock, CGMVCLK.

- Base clock selector circuit This software-controlled circuit selects either CGMXCLK divided by two or the VCO clock, CGMVCLK, divided by two as the base clock, CGMOUT. The SIM derives the system clocks from either CGMOUT or CGMXCLK.

Figure 4-1 shows the structure of the CGM.

**Clock Generator Module (CGM)**

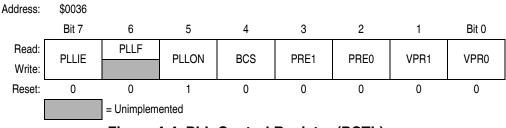

## 4.5.1 PLL Control Register

The PLL control register (PCTL) contains the interrupt enable and flag bits, the on/off switch, the base clock selector bit, the prescaler bits, and the VCO power-of-two range selector bits.

## Figure 4-4. PLL Control Register (PCTL)

## PLLIE — PLL Interrupt Enable Bit

This read/write bit enables the PLL to generate an interrupt request when the LOCK bit toggles, setting the PLL flag, PLLF. When the AUTO bit in the PLL bandwidth control register (PBWC) is clear, PLLIE cannot be written and reads as a 0. Reset clears the PLLIE bit.

1 = PLL interrupts enabled

0 = PLL interrupts disabled

### PLLF — PLL Interrupt Flag Bit

This read-only bit is set whenever the LOCK bit toggles. PLLF generates an interrupt request if the PLLIE bit also is set. PLLF always reads as a 0 when the AUTO bit in the PLL bandwidth control register (PBWC) is clear. Clear the PLLF bit by reading the PLL control register. Reset clears the PLLF bit.

1 = Change in lock condition

0 = No change in lock condition

### NOTE

Do not inadvertently clear the PLLF bit. Any read or read-modify-write operation on the PLL control register clears the PLLF bit.

### PLLON — PLL On Bit

This read/write bit activates the PLL and enables the VCO clock, CGMVCLK. PLLON cannot be cleared if the VCO clock is driving the base clock, CGMOUT (BCS = 1). (See 4.3.8 Base Clock Selector Circuit.) Reset sets this bit so that the loop can stabilize as the MCU is powering up.

1 = PLL on

0 = PLL off

### BCS — Base Clock Select Bit

This read/write bit selects either the crystal oscillator output, CGMXCLK, or the VCO clock, CGMVCLK, as the source of the CGM output, CGMOUT. CGMOUT frequency is one-half the frequency of the selected clock. BCS cannot be set while the PLLON bit is clear. After toggling BCS, it may take up to three CGMXCLK and three CGMVCLK cycles to complete the transition from one source clock to the other. During the transition, CGMOUT is held in stasis. (See 4.3.8 Base Clock Selector Circuit.) Reset clears the BCS bit.

1 = CGMVCLK divided by two drives CGMOUT

0 = CGMXCLK divided by two drives CGMOUT

### NOTE

PLLON and BCS have built-in protection that prevents the base clock selector circuit from selecting the VCO clock as the source of the base clock

# Chapter 7 Central Processor Unit (CPU)

# 7.1 Introduction

The M68HC08 CPU (central processor unit) is an enhanced and fully object-code-compatible version of the M68HC05 CPU. The *CPU08 Reference Manual* (document order number CPU08RM/AD) contains a description of the CPU instruction set, addressing modes, and architecture.

# 7.2 Features

Features of the CPU include:

- Object code fully upward-compatible with M68HC05 Family

- 16-bit stack pointer with stack manipulation instructions

- 16-bit index register with x-register manipulation instructions

- 8-MHz CPU internal bus frequency

- 64-Kbyte program/data memory space

- 16 addressing modes

- Memory-to-memory data moves without using accumulator

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- Enhanced binary-coded decimal (BCD) data handling

- Modular architecture with expandable internal bus definition for extension of addressing range beyond 64 Kbytes

- Low-power stop and wait modes

# 7.3 CPU Registers

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

### Keyboard Interrupt Module (KBI)

The vector fetch or software clear and the return of all enabled keyboard interrupt pins to 1 may occur in any order.

If the MODEK bit is clear, the keyboard interrupt pin is falling-edge-sensitive only. With MODEK clear, a vector fetch or software clear immediately clears the keyboard interrupt request.

Reset clears the keyboard interrupt request and the MODEK bit, clearing the interrupt request even if a keyboard interrupt pin stays at 0.

The keyboard flag bit (KEYF) in the keyboard status and control register can be used to see if a pending interrupt exists. The KEYF bit is not affected by the keyboard interrupt mask bit (IMASKK) which makes it useful in applications where polling is preferred.

To determine the logic level on a keyboard interrupt pin, use the data direction register to configure the pin as an input and read the data register.

### NOTE

Setting a keyboard interrupt enable bit (KBIEx) forces the corresponding keyboard interrupt pin to be an input, overriding the data direction register. However, the data direction register bit must be a 0 for software to read the pin.

## 9.4 Keyboard Initialization

When a keyboard interrupt pin is enabled, it takes time for the internal pullup to reach a 1. Therefore, a false interrupt can occur as soon as the pin is enabled.

To prevent a false interrupt on keyboard initialization:

- 1. Mask keyboard interrupts by setting the IMASKK bit in the keyboard status and control register.

- 2. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

- 3. Write to the ACKK bit in the keyboard status and control register to clear any false interrupts.

- 4. Clear the IMASKK bit.

An interrupt signal on an edge-triggered pin can be acknowledged immediately after enabling the pin. An interrupt signal on an edge- and level-triggered interrupt pin must be acknowledged after a delay that depends on the external load.

Another way to avoid a false interrupt:

- 1. Configure the keyboard pins as outputs by setting the appropriate DDRA bits in data direction register A.

- 2. Write 1s to the appropriate port A data register bits.

- 3. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

## 9.5 Low-Power Modes

The WAIT and STOP instructions put the microcontroller unit (MCU) in low power-consumption standby modes.

## 9.5.1 Wait Mode

The keyboard module remains active in wait mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of wait mode.

### Keyboard Interrupt Module (KBI)

### ACKK — Keyboard Acknowledge Bit

Writing a 1 to this write-only bit clears the keyboard interrupt request. ACKK always reads as 0. Reset clears ACKK.

### IMASKK — Keyboard Interrupt Mask Bit

Writing a 1 to this read/write bit prevents the output of the keyboard interrupt mask from generating interrupt requests. Reset clears the IMASKK bit.

- 1 = Keyboard interrupt requests masked

- 0 = Keyboard interrupt requests not masked

### MODEK — Keyboard Triggering Sensitivity Bit

This read/write bit controls the triggering sensitivity of the keyboard interrupt pins. Reset clears MODEK.

1 = Keyboard interrupt requests on falling edges and low levels

0 = Keyboard interrupt requests on falling edges only

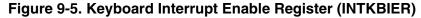

### 9.7.2 Keyboard Interrupt Enable Register

The keyboard interrupt enable register enables or disables each port A pin to operate as a keyboard interrupt pin.

| Address:        | \$001B |       |       |       |       |       |       |       |

|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

|                 | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| Read:<br>Write: | KBIE7  | KBIE6 | KBIE5 | KBIE4 | KBIE3 | KBIE2 | KBIE1 | KBIE0 |

| Reset:          | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

### KBIE7–KBIE0 — Keyboard Interrupt Enable Bits

Each of these read/write bits enables the corresponding keyboard interrupt pin to latch interrupt requests. Reset clears the keyboard interrupt enable register.

1 = PTAx pin enabled as keyboard interrupt pin

0 = PTAx pin not enabled as keyboard interrupt pin

# 10.3 Break Module (BRK)

## 10.3.1 Wait Mode

If enabled, the break (BRK) module is active in wait mode. In the break routine, the user can subtract one from the return address on the stack if the SBSW bit in the break status register is set.

## 10.3.2 Stop Mode

The break module is inactive in stop mode. A break interrupt causes exit from stop mode and sets the SBSW bit in the break status register. The STOP instruction does not affect break module register states.

# 10.4 Central Processor Unit (CPU)

## 10.4.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

## 10.4.2 Stop Mode

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

## 10.5 Clock Generator Module (CGM)

### 10.5.1 Wait Mode

The clock generator module (CGM) remains active in wait mode. Before entering wait mode, software can disengage and turn off the PLL by clearing the BCS and PLLON bits in the PLL control register (PCTL). Less power-sensitive applications can disengage the PLL without turning it off. Applications that require the PLL to wake the MCU from wait mode also can deselect the PLL output without turning off the PLL.

### 10.5.2 Stop Mode

If the OSCSTOPEN bit in the CONFIG register is cleared (default), then the STOP instruction disables the CGM (oscillator and phase-locked loop) and holds low all CGM outputs (CGMXCLK, CGMOUT, and CGMINT).

If the OSCSTOPEN bit in the CONFIG register is set, then the phase locked loop is shut off, but the oscillator will continue to operate in stop mode.

# 12.2 Port A

Port A is an 8-bit special-function port that shares all eight of its pins with the keyboard interrupt (KBI) module. Port A also has software configurable pullup devices if configured as an input port.

## 12.2.1 Port A Data Register

The port A data register (PTA) contains a data latch for each of the eight port A pins.

| Address:                 | \$0000 |      |      |           |            |      |      |       |

|--------------------------|--------|------|------|-----------|------------|------|------|-------|

|                          | Bit 7  | 6    | 5    | 4         | 3          | 2    | 1    | Bit 0 |

| Read:<br>Write:          | PTA7   | PTA6 | PTA5 | PTA4      | PTA3       | PTA2 | PTA1 | PTA0  |

| Reset:                   |        |      |      | Unaffecte | d by reset |      |      |       |

| Alternative<br>Function: | KBD7   | KBD6 | KBD5 | KBD4      | KBD3       | KBD2 | KBD1 | KBD0  |

Figure 12-2. Port A Data Register (PTA)

### PTA7-PTA0 — Port A Data Bits

These read/write bits are software programmable. Data direction of each port A pin is under the control of the corresponding bit in data direction register A. Reset has no effect on port A data.

### KBD7-KBD0 — Keyboard Inputs

The keyboard interrupt enable bits, KBIE7–KBIE0, in the keyboard interrupt control register (KBICR) enable the port A pins as external interrupt pins. See Chapter 9 Keyboard Interrupt Module (KBI).

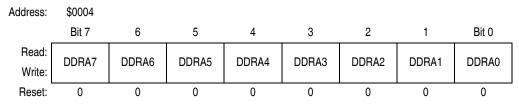

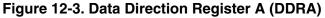

## 12.2.2 Data Direction Register A

Data direction register A (DDRA) determines whether each port A pin is an input or an output. Writing a 1 to a DDRA bit enables the output buffer for the corresponding port A pin; a 0 disables the output buffer.

## DDRA7–DDRA0 — Data Direction Register A Bits

These read/write bits control port A data direction. Reset clears DDRA7–DDRA0, configuring all port A pins as inputs.

1 = Corresponding port A pin configured as output

0 = Corresponding port A pin configured as input

### NOTE

Avoid glitches on port A pins by writing to the port A data register before changing data direction register A bits from 0 to 1.

Figure 12-4 shows the port A I/O logic.

# 12.4 Port C

Port C is a 7-bit, general-purpose bidirectional I/O port. Port C also has software configurable pullup devices if configured as an input port.

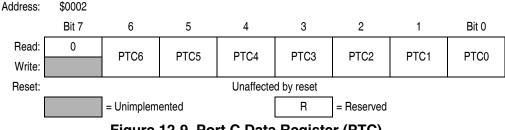

## 12.4.1 Port C Data Register

The port C data register (PTC) contains a data latch for each of the port C pins.

Figure 12-9. Port C Data Register (PTC)

### PTC6 and PTC0 — Port C Data Bits

These read/write bits are software-programmable. Data direction of each port C pin is under the control of the corresponding bit in data direction register C. Reset has no effect on port C data.

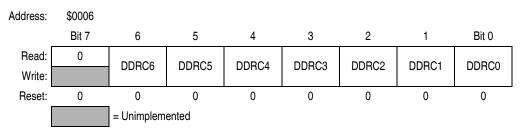

## 12.4.2 Data Direction Register C

Data direction register C (DDRC) determines whether each port C pin is an input or an output. Writing a 1 to a DDRC bit enables the output buffer for the corresponding port C pin; a 0 disables the output buffer.

Figure 12-10. Data Direction Register C (DDRC)

## DDRC6 and DDRC0 — Data Direction Register C Bits

These read/write bits control port C data direction. Reset clears DDRC6 and DDRC0, configuring all port C pins as inputs.

1 = Corresponding port C pin configured as output

0 = Corresponding port C pin configured as input

## NOTE

Avoid glitches on port C pins by writing to the port C data register before changing data direction register C bits from 0 to 1.

Figure 12-11 shows the port C I/O logic.

### PTCPUE1 and PTCPUE0 — Port C Input Pullup Enable Bits

These writable bits are software programmable to enable pullup devices on an input port bit.

- 1 = Corresponding port C pin configured to have internal pullup

- 0 = Corresponding port C pin internal pullup disconnected

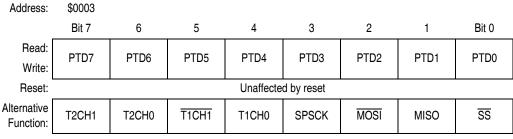

# 12.5 Port D

Port D is an 8-bit special-function port that shares four of its pins with the serial peripheral interface (SPI) module and three of its pins with two timer interface (TIM1 and TIM2) modules. Port D also has software configurable pullup devices if configured as an input port.

## 12.5.1 Port D Data Register

The port D data register (PTD) contains a data latch for each of the eight port D pins.

Figure 12-13. Port D Data Register (PTD)

### PTD7-PTD0 — Port D Data Bits

These read/write bits are software-programmable. Data direction of each port D pin is under the control of the corresponding bit in data direction register D. Reset has no effect on port D data.

### T2CH1 and T2CH0 — Timer 2 Channel I/O Bits

The PTD6/T2CH0–PTD7/T2CH1 pins are the TIM2 input capture/output compare pins. The edge/level select bits, ELSxB and ELSxA, determine whether the PTD6/T2CH0–PTD7/T2CH1 pins are timer channel I/O pins or general-purpose I/O pin. See Chapter 18 Timer Interface Module (TIM).

### T1CH1 and T1CH0 — Timer 1 Channel I/O Bits

The PTD4/T1CH0–PTD5/T1CH1 pins are the TIM1 input capture/output compare pins. The edge/level select bits, ELSxB and ELSxA, determine whether the PTD4/T1CH0–PTD5/T1CH1 pins are timer channel I/O pins or general-purpose I/O pins. See Chapter 18 Timer Interface Module (TIM).

### SPSCK — SPI Serial Clock

The PTD3/SPSCK pin is the serial clock input of the SPI module. When the SPE bit is clear, the PTD3/SPSCK pin is available for general-purpose I/O.

### MOSI — Master Out/Slave In

The PTD2/MOSI pin is the master out/slave in terminal of the SPI module. When the SPE bit is clear, the PTD2/MOSI pin is available for general-purpose I/O.

### MISO — Master In/Slave Out

The PTD1/MISO pin is the master in/slave out terminal of the SPI module. When the SPI enable bit, SPE, is clear, the SPI module is disabled, and the PTD0/SS pin is available for general-purpose I/O.

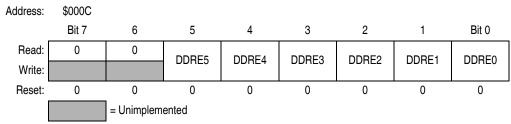

## 12.6.2 Data Direction Register E

Data direction register E (DDRE) determines whether each port E pin is an input or an output. Writing a 1 to a DDRE bit enables the output buffer for the corresponding port E pin; a 0 disables the output buffer.

### Figure 12-18. Data Direction Register E (DDRE)

### DDRE5–DDRE0 — Data Direction Register E Bits

These read/write bits control port E data direction. Reset clears DDRE5–DDRE0, configuring all port E pins as inputs.

1 = Corresponding port E pin configured as output

0 = Corresponding port E pin configured as input

### NOTE

Avoid glitches on port E pins by writing to the port E data register before changing data direction register E bits from 0 to 1.

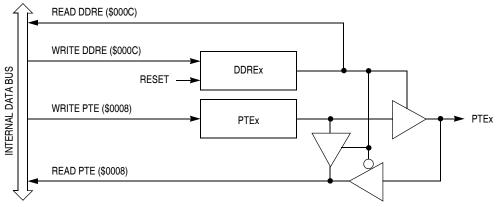

Figure 12-19 shows the port E I/O logic.

### Figure 12-19. Port E I/O Circuit

When bit DDREx is a 1, reading address \$0008 reads the PTEx data latch. When bit DDREx is a 0, reading address \$0008 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 12-6 summarizes the operation of the port E pins.

### Table 12-6. Port E Pin Functions

| DDRE | PTE              | I/O Pin                    | Accesses to DDRE | Access    | ses to PTE               |

|------|------------------|----------------------------|------------------|-----------|--------------------------|

| Bit  | Bit              | Mode                       | Read/Write       | Read      | Write                    |

| 0    | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRE5-DDRE0      | Pin       | PTE5–PTE0 <sup>(3)</sup> |

| 1    | Х                | Output                     | DDRE5-DDRE0      | PTE5–PTE0 | PTE5–PTE0                |

1. X = Don't care

2. Hi-Z = High impedance

3. Writing affects data register, but does not affect input.

# Chapter 13 Resets and Interrupts

# **13.1 Introduction**

Resets and interrupts are responses to exceptional events during program execution. A reset re-initializes the microcontroller (MCU) to its startup condition. An interrupt vectors the program counter to a service routine.

# 13.2 Resets

A reset immediately returns the MCU to a known startup condition and begins program execution from a user-defined memory location.

## 13.2.1 Effects

A reset:

- Immediately stops the operation of the instruction being executed

- Initializes certain control and status bits

- Loads the program counter with a user-defined reset vector address from locations \$FFFE and \$FFFF, \$FEFE and \$FEFF in monitor mode

- Selects CGMXCLK divided by four as the bus clock

## 13.2.2 External Reset

A 0 applied to the RST pin for a time, t<sub>RL</sub>, generates an external reset. An external reset sets the PIN bit in the system integration module (SIM) reset status register.

## 13.2.3 Internal Reset

Sources:

- Power-on reset (POR)

- Computer operating properly (COP)

- Low-power reset circuits

- Illegal opcode

- Illegal address

All internal reset sources pull the RST pin low for 32 CGMXCLK cycles to allow resetting of external devices. The MCU is held in reset for an additional 32 CGMXCLK cycles after releasing the RST pin.

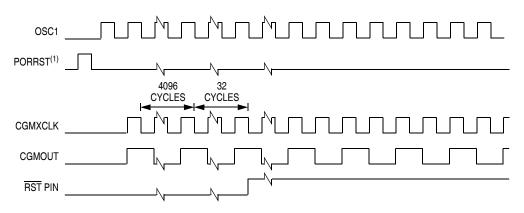

## 13.2.3.1 Power-On Reset (POR)

A power-on reset (POR) is an internal reset caused by a positive transition on the  $V_{DD}$  pin.  $V_{DD}$  at the POR must go below  $V_{POR}$  to reset the MCU. This distinguishes between a reset and a POR. The POR is not a brown-out detector, low-voltage detector, or glitch detector.

#### Resets and Interrupts

A power-on reset:

- Holds the clocks to the central processor unit (CPU) and modules inactive for an oscillator stabilization delay of 4096 CGMXCLK cycles

- Drives the  $\overline{RST}$  pin low during the oscillator stabilization delay

- Releases the RST pin 32 CGMXCLK cycles after the oscillator stabilization delay

- Releases the CPU to begin the reset vector sequence 64 CGMXCLK cycles after the oscillator stabilization delay

- Sets the POR and LVI bits in the SIM reset status register and clears all other bits in the register

1. PORRST is an internally generated power-on reset pulse.

Figure 13-1. Power-On Reset Recovery

### 13.2.3.2 Computer Operating Properly (COP) Reset

A computer operating properly (COP) reset is an internal reset caused by an overflow of the COP counter. A COP reset sets the COP bit in the SIM reset status register.

To clear the COP counter and prevent a COP reset, write any value to the COP control register at location \$FFFF.

## 13.2.3.3 Low-Voltage Inhibit (LVI) Reset

A low-voltage inhibit (LVI) reset is an internal reset caused by a drop in the power supply voltage to the LVI<sub>TRIPF</sub> voltage.

An LVI reset:

- Holds the clocks to the CPU and modules inactive for an oscillator stabilization delay of 4096 CGMXCLK cycles after the power supply voltage rises to the LVI<sub>TRIPR</sub> voltage

- Drives the RST pin low for as long as V<sub>DD</sub> is below the LVI<sub>TRIPR</sub> voltage and during the oscillator stabilization delay

- Releases the RST pin 32 CGMXCLK cycles after the oscillator stabilization delay

- Releases the CPU to begin the reset vector sequence 64 CGMXCLK cycles after the oscillator stabilization delay

- Sets the LVI bit in the SIM reset status register

Enhanced Serial Communications Interface (ESCI) Module

1. Ports are software configurable with pullup device if input port.

2. Higher current drive port pins

3. Pin contains integrated pullup device

## Figure 14-1. Block Diagram Highlighting ESCI Block and Pins

| Generic Pin Names | RxD      | TxD      |

|-------------------|----------|----------|

| Full Pin Names    | PTE1/RxD | PTE0/TxD |

### Table 14-1. Pin Name Conventions

**I/O Registers**

### PDS2–PDS0 — Prescaler Divisor Select Bits

These read/write bits select the prescaler divisor as shown in Table 14-9. Reset clears PDS2–PDS0.

NOTE

The setting of '000' will bypass not only this prescaler but also the prescaler divisor fine adjust (PDFA). It is not recommended to bypass the prescaler while ENSCI is set, because the switching is not glitch free.

| PS[2:1:0] | Prescaler Divisor (PD) |

|-----------|------------------------|

| 000       | Bypass this prescaler  |

| 001       | 2                      |

| 0 1 0     | 3                      |

| 0 1 1     | 4                      |

| 100       | 5                      |

| 101       | 6                      |

| 1 1 0     | 7                      |

| 1 1 1     | 8                      |

### Table 14-9. ESCI Prescaler Division Ratio

### PSSB4–PSSB0 — Clock Insertion Select Bits

These read/write bits select the number of clocks inserted in each 32 output cycle frame to achieve more timing resolution on the **average** prescaler frequency as shown in Table 14-10. Reset clears PSSB4–PSSB0.

Use the following formula to calculate the ESCI baud rate:

Baud rate =  $\frac{\text{Frequency of the SCI clock source}}{64 \text{ x BPD x BD x (PD + PDFA)}}$

### where:

Frequency of the SCI clock source =  $f_{Bus}$  or CGMXCLK (selected by

ESCIBDSRC in the CONFIG2 register)

BPD = Baud rate register prescaler divisor

BD = Baud rate divisor

PD = Prescaler divisor

PDFA = Prescaler divisor fine adjust

Table 14-11 shows the ESCI baud rates that can be generated with a 4.9152-MHz bus frequency.

#### System Integration Module (SIM)

1. Ports are software configurable with pullup device if input port.

2. Higher current drive port pins

3. Pin contains integrated pullup device

## Figure 15-1. Block Diagram Highlight SIM Block and Pins

### System Integration Module (SIM)

| Addr.  | Register Name                         |                 | Bit 7          | 6               | 5    | 4    | 3          | 2      | 1                           | Bit 0 |

|--------|---------------------------------------|-----------------|----------------|-----------------|------|------|------------|--------|-----------------------------|-------|

| \$FE00 | Break Status Register<br>(BSR)        | Read:<br>Write: | R              | R               | R    | R    | R          | R      | SBSW<br>Note <sup>(1)</sup> | R     |

|        | See page 192.                         | Reset:          | 0              | 0               | 0    | 0    | 0          | 0      | 0                           | 0     |

|        |                                       |                 | 1. Writing a a | a 0 clears SB   | SW.  |      |            |        |                             |       |

|        | SIM Reset Status Register             | Read:           | POR            | PIN             | COP  | ILOP | ILAD       | MODRST | LVI                         | 0     |

| \$FE01 | (SRSR)                                | Write:          |                |                 |      |      |            |        |                             |       |

|        | See page 193.                         | POR:            | 1              | 0               | 0    | 0    | 0          | 0      | 0                           | 0     |

| \$FE03 | Break Flag Control Register<br>(BFCR) | Read:<br>Write: | BCFE           | R               | R    | R    | R          | R      | R                           | R     |

|        | See page 194.                         | Reset:          | 0              |                 |      |      |            |        |                             |       |

|        | Interrupt Status Register 1           | Read:           | IF6            | IF5             | IF4  | IF3  | IF2        | IF1    | 0                           | 0     |

| \$FE04 | (INT1)                                | Write:          | R              | R               | R    | R    | R          | R      | R                           | R     |

|        | See page 188.                         | Reset:          | 0              | 0               | 0    | 0    | 0          | 0      | 0                           | 0     |

|        | Interrupt Status Register 2           | Read:           | IF14           | IF13            | IF12 | IF11 | IF10       | IF9    | IF8                         | IF7   |

| \$FE05 | (INT2)                                | Write:          | R              | R               | R    | R    | R          | R      | R                           | R     |

|        | See page 189.                         | Reset:          | 0              | 0               | 0    | 0    | 0          | 0      | 0                           | 0     |

|        | Interrupt Status Register 3           | Read:           | 0              | 0               | IF20 | IF19 | IF18       | IF17   | IF16                        | IF15  |

| \$FE06 | (INT3)                                | Write:          | R              | R               | R    | R    | R          | R      | R                           | R     |

|        | See page 189.                         | Reset:          | 0              | 0               | 0    | 0    | 0          | 0      | 0                           | 0     |

|        |                                       |                 |                | = Unimplemented |      | R    | = Reserved |        |                             |       |

Figure 15-3. SIM I/O Register Summary

## **18.2 Features**

Features of the TIM include:

- Two input capture/output compare channels:

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Buffered and unbuffered pulse-width-modulation (PWM) signal generation

- Programmable TIM clock input with 7-frequency internal bus clock prescaler selection

- Free-running or modulo up-count operation

- Toggle any channel pin on overflow

- TIM counter stop and reset bits

## **18.3 Pin Name Conventions**

The text that follows describes both timers, TIM1 and TIM2. The TIM input/output (I/O) pin names are T[1,2]CH0 (timer channel 0) and T[1,2]CH1 (timer channel 1), where "1" is used to indicate TIM1 and "2" is used to indicate TIM2. The two TIMs share four I/O pins with four port D I/O port pins. The full names of the TIM I/O pins are listed in Table 18-1. The generic pin names appear in the text that follows.

Table 18-1. Pin Name Conventions

| TIM Generic Pin Nan | nes: | T[1,2]CH0  | T[1,2]CH1  |

|---------------------|------|------------|------------|

| Full TIM Bin Namos  | TIM1 | PTD4/T1CH0 | PTD5/T1CH1 |

| Full TIM Pin Names: | TIM2 | PTD6/T2CH0 | PTD7/T2CH1 |

### NOTE

References to either timer 1 or timer 2 may be made in the following text by omitting the timer number. For example, TCH0 may refer generically to T1CH0 and T2CH0, and TCH1 may refer to T1CH1 and T2CH1.

## **18.4 Functional Description**

Figure 18-1 shows the structure of the TIM. The central component of the TIM is the 16-bit TIM counter that can operate as a free-running counter or a modulo up-counter. The TIM counter provides the timing reference for the input capture and output compare functions. The TIM counter modulo registers, TMODH:TMODL, control the modulo value of the TIM counter. Software can read the TIM counter value at any time without affecting the counting sequence.

The two TIM channels (per timer) are programmable independently as input capture or output compare channels. If a channel is configured as input capture, then an internal pullup device may be enabled for that channel. See 12.5.3 Port D Input Pullup Enable Register.

Figure 18-3 summarizes the timer registers.

### NOTE

References to either timer 1 or timer 2 may be made in the following text by omitting the timer number. For example, TSC may generically refer to both T1SC and T2SC.