#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                       |

|---------------------------------|--------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                               |

| Speed                           | 333MHz                                                       |

| Co-Processors/DSP               | Security; SEC 3.3                                            |

| RAM Controllers                 | DDR, DDR2                                                    |

| Graphics Acceleration           | No                                                           |

| Display & Interface Controllers | -                                                            |

| Ethernet                        | 10/100/1000Mbps (2)                                          |

| SATA                            | -                                                            |

| USB                             | USB 2.0 + PHY (1)                                            |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                             |

| Operating Temperature           | -40°C ~ 105°C (TA)                                           |

| Security Features               | Cryptography, Random Number Generator                        |

| Package / Case                  | 620-BBGA Exposed Pad                                         |

| Supplier Device Package         | 620-HBGA (29x29)                                             |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8314ecvrafda |

|                                 |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Overview

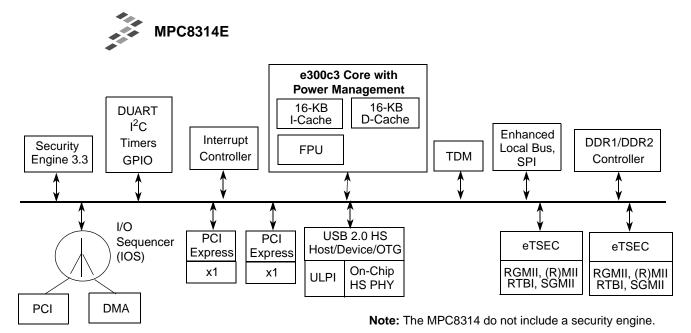

The MPC8314E incorporates the e300c3 (MPC603e-based) core, which includes 16 Kbytes of L1 instruction and data caches, on-chip memory management units (MMUs), and floating-point support. In addition to the e300 core, the SoC platform includes features such as dual enhanced three-speed 10, 100, 1000 Mbps Ethernet controllers (eTSECs) with SGMII support, a 32- or 16-bit DDR1/DDR2 SDRAM memory controller, a security engine to accelerate control and data plane security protocols, and a high degree of software compatibility with previous-generation PowerQUICC processor-based designs for backward compatibility and easier software migration. The MPC8314E also offers peripheral interfaces such as a 32-bit PCI interface with up to 66 MHz operation, 16-bit enhanced local bus interface with up to 66 MHz operation, TDM interface, and USB 2.0 with an on-chip USB 2.0 PHY.

8314E offers additional high-speed interconnect support with dual single-lane PCI Express interfaces. When not used for PCI Express, the SerDes interface may be configured to support SGMII. The MPC8314E security engine (SEC 3.3) allows CPU-intensive cryptographic operations to be offloaded from the main CPU core. This figure shows a block diagram of the MPC8314E.

Figure 1. MPC8314E Block Diagram

# 2 MPC8314E Features

The following features are supported in the MPC8314E.

### 2.1 e300 Core

The e300 core has the following features:

- Operates at up to 400 MHz

- 16-Kbyte instruction cache, 16-Kbyte data cache

- One floating point unit and two integer units

- Software-compatible with the Freescale processor families implementing the PowerPC Architecture

- Performance monitor

### 2.2 Serial Interfaces

The following interfaces are supported in the MPC8314E.

- Two enhanced TSECs (eTSECs)

- Two Ethernet interfaces using one RGMII/MII/RMII/RTBI or SGMII (no GMII)

- Dual UART, one I<sup>2</sup>C, and one SPI interface

### 2.3 Security Engine

The security engine is optimized to handle all the algorithms associated with IPSec, 802.11i, and iSCSI. The security engine contains one crypto-channel, a controller, and a set of crypto execution units (EUs). The execution units are:

- Public key execution unit (PKEU)

- RSA and Diffie-Hellman (to 4096 bits)

- Programmable field size up to 2048 bits

- Elliptic curve cryptography (1023 bits)

- F2m and F(p) modes

- Programmable field size up to 511 bits

- Data encryption standard execution unit (DEU)

- DES, 3DES

- Two key (K1, K2) or three key (K1, K2, K3)

- ECB, CBC, CFB-64 and OFB-64 modes for both DES and 3DES

- Advanced encryption standard unit (AESU)

- Implements the Rinjdael symmetric key cipher

- Key lengths of 128, 192, and 256 bits

- ECB, CBC, CCM, CTR, GCM, CMAC, OFB, CFB, XCBC-MAC and LRW modes

- XOR acceleration

- Message digest execution unit (MDEU)

- SHA with 160-bit, 256-bit, 384-bit and 512-bit message digest

- SHA-384/512

- MD5 with 128-bit message digest

- HMAC with either algorithm

- Random number generator (RNG)

MPC8314E Features

## 2.9 Dual Enhanced Three-Speed Ethernet Controllers (eTSECs)

The eTSECs include the following features:

- Two SGMII/RGMII/MII/RMII/RTBI interfaces

- Two controllers designed to comply with IEEE Std 802.3<sup>TM</sup>, IEEE 802.3u<sup>TM</sup>, IEEE 802.3x<sup>TM</sup>, IEEE 802.3au<sup>TM</sup>, IEEE 802.3au<sup>TM</sup>, IEEE 802.3ab<sup>TM</sup>, and IEEE Std 1588<sup>TM</sup>

- Support for Wake-on-Magic Packet<sup>™</sup>, a method to bring the device from standby to full operating mode

- MII management interface for external PHY control and status.

## 2.10 Integrated Programmable Interrupt Controller (IPIC)

The integrated programmable interrupt controller (IPIC) provides a flexible solution for general-purpose interrupt control. The IPIC programming model is compatible with the MPC8260 interrupt controller and supports external and internal discrete interrupt sources. Interrupts can also be redirected to an external interrupt controller.

## 2.11 Power Management Controller (PMC)

The MPC8314E supports a range of power management states that significantly lower power consumption under the control of the power management controller. The PMC includes the following features:

- Provides power management when the device is used in both PCI host and agent modes

- PCI Power Management 1.2 D0, D1, D2, D3hot, and D3cold states

- PME generation in PCI agent mode, PME detection in PCI host mode

- Wake-up from Ethernet (magic packet), USB, GPIO, and PCI (PME input as host) while in the D1, D2 and D3hot states

- A new low-power standby power management state called D3warm

- The PMC, one Ethernet port, and the GTM block remain powered via a split power supply controlled through an external power switch

- Wake-up events include Ethernet (magic packet), GTM, GPIO, or IRQ inputs and cause the device to transition back to normal operation

- PCI agent mode is not be supported in D3warm state

- PCI Express-based PME events are not supported

# 2.12 Serial Peripheral Interface (SPI)

The serial peripheral interface (SPI) allows the MPC8314E to exchange data between other PowerQUICC family chips, Ethernet PHYs for configuration, and peripheral devices such as EEPROMs, real-time clocks, A/D converters, and ISDN devices.

The SPI is a full-duplex, synchronous, character-oriented channel that supports a four-wire interface (receive, transmit, clock, and slave select). The SPI block consists of transmitter and receiver sections, an independent baud-rate generator, and a control unit.

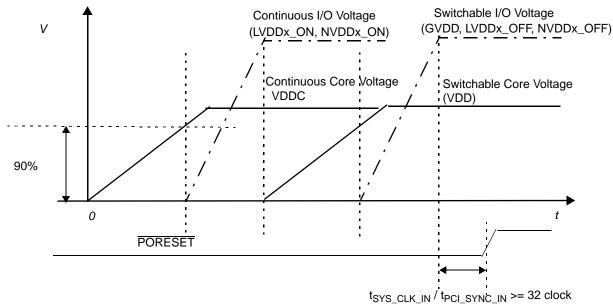

### CAUTION

When the device is in D3 warm (standby) mode, all external voltage supplies applied to any I/O pins, with the exception of wake-up pins, must be turned off. Applying supplied external voltage to any I/O pins, except the wake up pins, while the device is in D3 warm standby mode may cause permanent damage to the device.

An example of the power-up sequence is shown in Figure 4 when implemented along with low power D3 warm mode.

Figure 4. Power Up Sequencing Example with Low power D3 Warm Mode

# **4 Power Characteristics**

(Does not include I/O power dissipation)

This table shows the estimated typical power dissipation for this family of devices.

### Table 4. MPC8314E Power Dissipation

| Core Frequency (MHz) | CSB Frequency (MHz) | Typical <sup>1,3</sup> | Maximum <sup>1,2</sup> | Unit |

|----------------------|---------------------|------------------------|------------------------|------|

| 266                  | 133                 | 1.116                  | 1.646                  | W    |

| 333                  | 133                 | 1.142                  | 1.665                  | W    |

| 400                  | 133                 | 1.167                  | 1.690                  | W    |

Note:

1. The values do not include I/O supply power, but do include core, AVDD, USB PLL, and digital SerDes power.

Maximum power is based on a voltage of V<sub>dd</sub> = 1.05V, a junction temperature of T<sub>j</sub> = 105°C, and an artificial smoker test.

3. Typical power is based on a voltage of  $V_{dd}$  = 1.05V, and an artificial smoker test running at room temperature.

This table shows the estimated typical I/O power dissipation for this family of devices.

| Interface                                            | Frequency                  | GV <sub>DD</sub><br>(1.8 V) | GV <sub>DD</sub><br>(2.5 V) | NV <sub>DD</sub><br>(3.3 V) | LVDD1_OFF/<br>LVDD2_ON<br>(3.3V) | LVDD2<br>_ON<br>(3.3V) | VDD33PLL,<br>VDD33ANA<br>(3.3V) | SATA_VDD,<br>VDD1IO,<br>VDD1ANA<br>(1.0V) | XCOREVDD,<br>XPADVDD,<br>SDAVDD<br>(1.0V) | Unit |

|------------------------------------------------------|----------------------------|-----------------------------|-----------------------------|-----------------------------|----------------------------------|------------------------|---------------------------------|-------------------------------------------|-------------------------------------------|------|

| DDR 1<br>Rs = 22Ω                                    | 266MHz,<br>32 bits         | _                           | 0.323                       |                             | _                                |                        | _                               | _                                         | _                                         | W    |

| Rt = 50Ω                                             | 200MHz,<br>32 bits         | _                           | 0.291                       |                             | —                                |                        | —                               | —                                         | —                                         | W    |

| DDR 2<br>Rs = $22\Omega$                             | 266MHz,<br>32 bits         | 0.246                       | _                           |                             | —                                | -                      | —                               | —                                         | —                                         | W    |

| Rt = 75Ω                                             | 200MHz,<br>32bits          | 0.225                       | _                           | _                           | —                                | _                      | —                               | —                                         | —                                         | W    |

| PCI I/O                                              | 33 MHz                     | —                           | —                           | 0.120                       | —                                | _                      | —                               | —                                         | —                                         | W    |

| load = 50pF                                          | 66 MHz                     | —                           | —                           | 0.249                       | —                                | _                      | —                               | —                                         | —                                         | W    |

| Local bus I/O                                        | 66 MHz                     | _                           | —                           | _                           | —                                | 0.056                  | —                               | —                                         | —                                         | W    |

| load = 20pF                                          | 50 MHz                     | _                           | —                           | _                           | —                                | 0.040                  | —                               | —                                         | —                                         | W    |

| eTSEC I/O                                            | MII, 25MHz                 | —                           | —                           | _                           | 0.008                            | —                      | —                               | —                                         | —                                         | W    |

| load = 20pF<br>Multiple by<br>number of<br>interface | RGMII,<br>125MHz<br>(3.3V) | _                           | _                           |                             | 0.078                            | _                      | _                               | _                                         | _                                         | V    |

| used                                                 | RGMII,<br>125MHz<br>(2.5V) | —                           | —                           | _                           | 0.044                            | —                      | _                               | _                                         | _                                         | V    |

| USBDR<br>Controller<br>(ULPI mode)<br>Ioad =20pF     | 60 MHz                     |                             |                             |                             | 0.078                            |                        |                                 | _                                         | _                                         | W    |

| USBDR+<br>Internal PHY<br>(UTMI mode)                | 480 MHz                    | _                           | _                           | _                           | 0.274                            | _                      | _                               | _                                         | —                                         | W    |

| PCI Express<br>two x1lane                            | 2.5 GHz                    | —                           | —                           | _                           | _                                | —                      | _                               | _                                         | 0.190                                     | W    |

| Other I/O                                            | _                          | _                           | —                           | 0.015                       | _                                | _                      | _                               | _                                         | —                                         | W    |

#### Table 5. MPC8314E Power Dissipation

# 5 Clock Input Timing

This section provides the clock input DC and AC electrical characteristics for the MPC8314E.

#### DDR and DDR2 SDRAM

This table provides the DDR2 capacitance when GVDD(typ) = 1.8 V.

#### Table 12. DDR2 SDRAM Capacitance for GVDD(typ) = 1.8 V

| Parameter/Condition                     | Symbol           | Min | Max | Unit | Note |

|-----------------------------------------|------------------|-----|-----|------|------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1    |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1    |

Note:

1. This parameter is sampled. GVDD = 1.8 V  $\pm$  0.090 V, f = 1 MHz, T<sub>A</sub> = 25°C, V<sub>OUT</sub> = GVDD/2, V<sub>OUT</sub> (peak-to-peak) = 0.2 V.

This table provides the recommended operating conditions for the DDR SDRAM component(s) of the MPC8314E when GVDD(typ) = 2.5 V.

#### Table 13. DDR SDRAM DC Electrical Characteristics for GVDD(typ) = 2.5 V

| Parameter/Condition                                             | Symbol          | Min                       | Мах                       | Unit | Note |

|-----------------------------------------------------------------|-----------------|---------------------------|---------------------------|------|------|

| I/O supply voltage                                              | GVDD            | 2.3                       | 2.7                       | V    | 1    |

| I/O reference voltage                                           | MVREF           | $0.49 \times \text{GVDD}$ | $0.51 \times \text{GVDD}$ | V    | 2    |

| I/O termination voltage                                         | V <sub>TT</sub> | MVREF – 0.04              | MVREF + 0.04              | V    | 3    |

| Input high voltage                                              | V <sub>IH</sub> | MVREF + 0.15              | GVDD + 0.3                | V    |      |

| Input low voltage                                               | V <sub>IL</sub> | -0.3                      | MVREF – 0.15              | V    |      |

| Output leakage current                                          | I <sub>OZ</sub> | -9.9                      | -9.9                      | μΑ   | 4    |

| Output high current (V <sub>OUT</sub> = 1.95 V,<br>GVDD = 2.3V) | I <sub>OH</sub> | -16.2                     | _                         | mA   | —    |

| Output low current ( $V_{OUT} = 0.35 V$ )                       | I <sub>OL</sub> | 16.2                      | —                         | mA   | —    |

Note:

1. GVDD is expected to be within 50 mV of the DRAM GVDD at all times.

2. MVREF is expected to be equal to 0.5 × GVDD, and to track GVDD DC variations as measured at the receiver. Peak-to-peak noise on MVREF may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MVREF. This rail should track variations in the DC level of MVREF.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GVDD.

This table provides the DDR capacitance when GVDD(typ) = 2.5 V.

#### Table 14. DDR SDRAM Capacitance for GVDD(typ) = 2.5 V Interface

| Parameter/Condition                     | Symbol           | Min | Мах | Unit | Note |

|-----------------------------------------|------------------|-----|-----|------|------|

| Input/output capacitance: DQ,DQS        | C <sub>IO</sub>  | 6   | 8   | pF   | 1    |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | —   | 0.5 | pF   | 1    |

Note:

1. This parameter is sampled. GVDD =  $2.5 \text{ V} \pm 0.125 \text{ V}$ , f = 1 MHz, T<sub>A</sub> =  $25^{\circ}$ C, V<sub>OUT</sub> = GVDD/2, V<sub>OUT</sub> (peak-to-peak) = 0.2 V.

This table provides the current draw characteristics for MV<sub>REF</sub>.

#### Table 15. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter / Condition              | Symbol             | Min | Max | Unit | Note |

|------------------------------------|--------------------|-----|-----|------|------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> | _   | 500 | μΑ   | 1    |

DDR and DDR2 SDRAM

#### Table 15. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter / Condition | Symbol | Min | Max | Unit | Note |

|-----------------------|--------|-----|-----|------|------|

| Note:                 |        |     |     |      |      |

1. The voltage regulator for  $MV_{REF}$  must be able to supply up to 500  $\mu$ A current.

## 7.2 DDR and DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR and DDR2 SDRAM interface.

### 7.2.1 DDR and DDR2 SDRAM Input AC Timing Specifications

This table lists the input AC timing specifications for the DDR2 SDRAM (GVDD(typ) = 1.8 V).

#### Table 16. DDR2 SDRAM Input AC Timing Specifications for 1.8-V Interface

At recommended operating conditions with GVDD of  $1.8V \pm 100 \text{ mV}$

| Parameter             | Symbol          | Min          | Мах          | Unit | Note |

|-----------------------|-----------------|--------------|--------------|------|------|

| AC input low voltage  | V <sub>IL</sub> | —            | MVREF – 0.45 | V    | —    |

| AC input high voltage | V <sub>IH</sub> | MVREF + 0.45 | —            | V    | —    |

This table lists the input AC timing specifications for the DDR SDRAM when GVDD(typ)=2.5 V.

Table 17. DDR SDRAM Input AC Timing Specifications for 2.5 V Interface

At recommended operating conditions with GVDD of  $2.5V \pm 200 \text{ mV}$

| Parameter             | Symbol          | Min          | Мах          | Unit | Note |

|-----------------------|-----------------|--------------|--------------|------|------|

| AC input low voltage  | V <sub>IL</sub> | —            | MVREF – 0.51 | V    |      |

| AC input high voltage | V <sub>IH</sub> | MVREF + 0.51 | _            | V    |      |

The following two tables list the input AC timing specifications for the DDR SDRAM interface.

#### Table 18. DDR2 SDRAM Input AC Timing Specifications

At recommended operating conditions with GVDD of (1.8 V $\pm$  100 mV)

| Parameter                                          | Symbol              | Min         | Max         | Unit | Note    |

|----------------------------------------------------|---------------------|-------------|-------------|------|---------|

| Controller Skew for MDQS—MDQ<br>266 MHz<br>200 MHz | t <sub>CISKEW</sub> | 875<br>1250 | 875<br>1250 | ps   | 1, 2, 3 |

Note:

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit to be captured with MDQS[n]. This should be subtracted from the total timing budget.

The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: tDISKEW =+/-(T/4 – abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

3. Memory controller ODT value of 150  $\Omega$  is recommended.

#### Table 19. DDR SDRAM Input AC Timing Specifications

At recommended operating conditions with GVDD of  $(2.5V \pm 200 \text{ mV})$

|  | Parameter | Symbol | Min | Мах | Unit | Note |  |

|--|-----------|--------|-----|-----|------|------|--|

|--|-----------|--------|-----|-----|------|------|--|

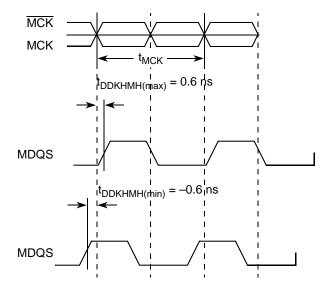

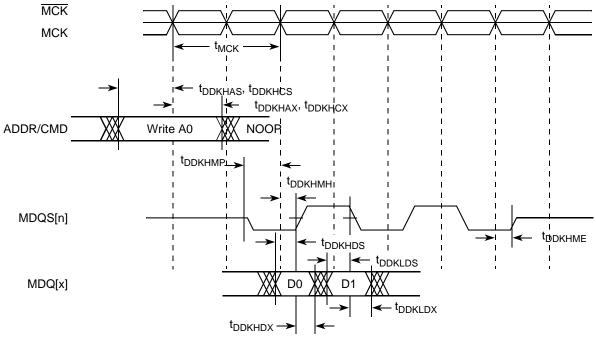

This figure shows the DDR SDRAM output timing for the MCK to MDQS skew measurement  $(t_{DDKHMH})$ .

Figure 6. Timing Diagram for t<sub>DDKHMH</sub>

This figure shows the DDR and DDR2 SDRAM output timing diagram.

Figure 7. DDR and DDR2 SDRAM Output Timing Diagram

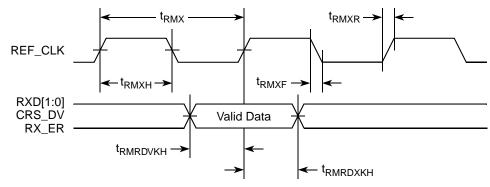

#### Table 28. RMII Receive AC Timing Specifications (continued)

At recommended operating conditions with LVDD of 3.3 V  $\pm$  300 mv

| Parameter/Condition                                               | Symbol <sup>1</sup>  | Min | Тур | Max | Unit |

|-------------------------------------------------------------------|----------------------|-----|-----|-----|------|

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK                     | t <sub>RMRDVKH</sub> | 4.0 | —   | _   | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK                      | t <sub>RMRDXKH</sub> | 2.0 | —   | -   | ns   |

| REF_CLK clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>RMXR</sub>    | 1.0 | —   | 4.0 | ns   |

| REF_CLK clock fall time $V_{IH}(max)$ to $V_{IL}(min)$            | t <sub>RMXF</sub>    | 1.0 | —   | 4.0 | ns   |

Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first three letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>RMRDVKH</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>RMX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>RMRDXKL</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>RMX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>RMRDXKL</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>RMX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII (RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

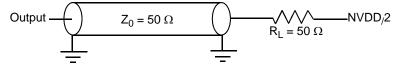

This figure provides the AC test load.

Figure 13. AC Test Load

This figure shows the RMII receive AC timing diagram.

Figure 14. RMII Receive AC Timing Diagram

### 9.2.3 RGMII and RTBI AC Timing Specifications

This table presents the RGMII and RTBI AC timing specifications.

#### Table 29. RGMII and RTBI AC Timing Specifications

At recommended operating conditions (see Table 2)

| Parameter/Condition                                 | Symbol <sup>1</sup> | Min  | Тур | Max | Unit |

|-----------------------------------------------------|---------------------|------|-----|-----|------|

| Data to clock output skew (at transmitter)          | t <sub>SKRGT</sub>  | -0.6 | _   | 0.6 | ns   |

| Data to clock input skew (at receiver) <sup>2</sup> | t <sub>SKRGT</sub>  | 1.0  |     | 2.6 | ns   |

I<sup>2</sup>C

# 13.2 I<sup>2</sup>C AC Electrical Specifications

This table provides the AC timing parameters for the  $I^2C$  interface.

Table 48. I<sup>2</sup>C AC Electrical Specifications

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 47)

| Parameter                                                                                    | Symbol <sup>1</sup>            | Min                      | Max              | Unit |

|----------------------------------------------------------------------------------------------|--------------------------------|--------------------------|------------------|------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>               | 0                        | 400              | kHz  |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub>              | 1.3                      |                  | μs   |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub>              | 0.6                      |                  | μS   |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub>            | 0.6                      |                  | μS   |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub>            | 0.6                      | —                | μs   |

| Data setup time                                                                              | t <sub>I2DVKH</sub>            | 100                      |                  | ns   |

| Data hold time:<br>CBUS compatible masters<br>I <sup>2</sup> C bus devices                   | t <sub>I2DXKL</sub>            | $\frac{1}{0^2}$          | 0.9 <sup>3</sup> | μS   |

| Fall time of both SDA and SCL signals                                                        | t <sub>I2CF</sub> <sup>4</sup> | —                        | 300              | ns   |

| Setup time for STOP condition                                                                | t <sub>I2PVKH</sub>            | 0.6                      |                  | μS   |

| Bus free time between a STOP and START condition                                             | t <sub>I2KHDX</sub>            | 1.3                      |                  | μS   |

| Noise margin at the LOW level for each connected device (including hysteresis)               | V <sub>NL</sub>                | $0.1 \times \text{NVDD}$ |                  | V    |

| Noise margin at the HIGH level for each connected device (including hysteresis)              | V <sub>NH</sub>                | $0.2\times\text{NVDD}$   |                  | V    |

Note:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>12DVKH</sub> symbolizes I<sup>2</sup>C timing (I2) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>12C</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>12SXKL</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the start condition (S) went invalid (X) relative to the t<sub>12C</sub> clock reference (K) going to the low (L) state or hold time. Also, t<sub>12PVKH</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the start condition (S) went invalid (X) relative to the t<sub>12C</sub> clock reference (K) going to the stop condition (P) reaching the valid state (V) relative to the t<sub>12C</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

- MPC8314E provides a hold time of at least 300 ns for the SDA signal (referred to the V<sub>IHmin</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- 3. The maximum t<sub>I2DVKH</sub> has to be met only if the device does not stretch the LOW period (t<sub>I2CL</sub>) of the SCL signal.

- 4. MPC8314E does not follow the I2C-BUS Specifications version 2.1 regarding the tI2CF AC parameter.

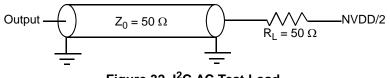

This figure provides the AC test load for the  $I^2C$ .

Figure 32. I<sup>2</sup>C AC Test Load

PCI

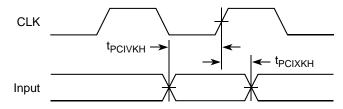

#### Table 50. PCI AC Timing Specifications at 66 MHz (continued)

| Parameter             | Symbol <sup>1</sup> | Min | Max | Unit | Note |

|-----------------------|---------------------|-----|-----|------|------|

| Input hold from clock | t <sub>PCIXKH</sub> | 0   |     | ns   | 2, 4 |

Note:

Note that the symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

2. See the timing measurement conditions in the PCI 2.3 Local Bus Specifications.

- 3. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 4. Input timings are measured at the pin.

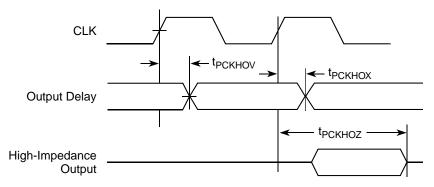

### This table shows the PCI AC Timing Specifications at 33 MHz.

| Table 51. PCI AC Timing Specifications at 33 MHz | Table 51. | PCI AC | Timing | <b>Specifications</b> | at 33 MHz |

|--------------------------------------------------|-----------|--------|--------|-----------------------|-----------|

|--------------------------------------------------|-----------|--------|--------|-----------------------|-----------|

| Parameter                      | Symbol <sup>1</sup> | Min | Max | Unit | Note |

|--------------------------------|---------------------|-----|-----|------|------|

| Clock to output valid          | t <sub>PCKHOV</sub> | _   | 11  | ns   | 2    |

| Output hold from clock         | t <sub>PCKHOX</sub> | 2   | —   | ns   | 2    |

| Clock to output high impedance | t <sub>PCKHOZ</sub> | —   | 14  | ns   | 2, 3 |

| Input setup to clock           | t <sub>PCIVKH</sub> | 4.0 | —   | ns   | 2, 4 |

| Input hold from clock          | t <sub>PCIXKH</sub> | 0   | —   | ns   | 2, 4 |

Note:

Note that the symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

2. See the timing measurement conditions in the PCI 2.3 Local Bus Specifications.

- 3. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 4. Input timings are measured at the pin.

This figure provides the AC test load for PCI.

Figure 34. PCI AC Test Load

This figure shows the PCI input AC timing conditions.

Figure 35. PCI Input AC Timing Measurement Conditions

This figure shows the PCI output AC timing conditions.

Figure 36. PCI Output AC Timing Measurement Condition

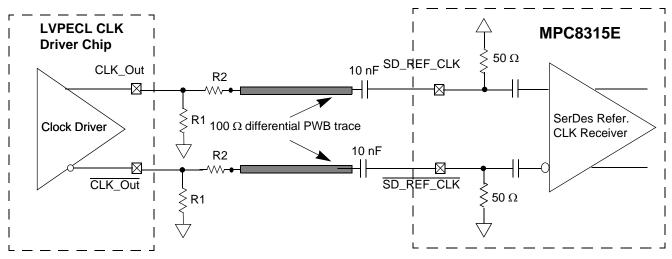

# 15 High-Speed Serial Interfaces (HSSI)

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes Reference Clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

### 15.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 37 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for description. The figure shows waveform for either a transmitter output (TXn and  $\overline{TXn}$ ) or a receiver input (RXn and  $\overline{RXn}$ ). Each signal swings between A Volts and B Volts where A > B.

Using this waveform, the definitions are as follows. To simplify illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

### 1. Single-Ended Swing

The transmitter output signals and the receiver input signals TXn,  $\overline{TXn}$ , RXn and  $\overline{RXn}$  each have a peak-to-peak swing of A – B Volts. This is also referred as each signal wire's Single-Ended Swing.

2. Differential Output Voltage, V<sub>OD</sub> (or Differential Output Swing):

#### High-Speed Serial Interfaces (HSSI)

assumes that the LVPECL clock driver's output impedance is  $50\Omega$ . R1 is used to DC-bias the LVPECL outputs prior to AC-coupling. Its value could be ranged from  $140\Omega$  to  $240\Omega$  depending on clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's  $50-\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the MPC8315E SerDes reference clock's differential input amplitude requirement (between 200mV and 800mV differential peak). For example, if the LVPECL output's differential peak is 900mV and the desired SerDes reference clock input amplitude is selected as 600mV, the attenuation factor is 0.67, which requires R2 =  $25\Omega$ . Please consult clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 44. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

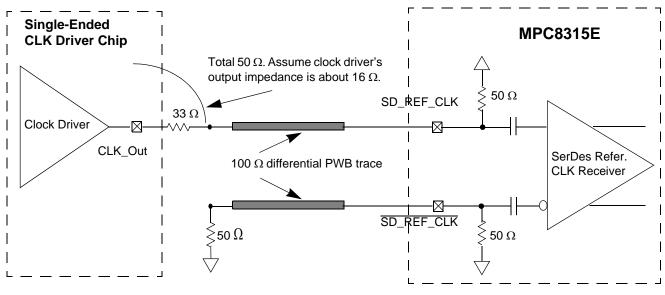

This figure shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with MPC8315E SerDes reference clock input's DC requirement.

Figure 45. Single-Ended Connection (Reference Only)

### 15.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected should provide a high quality reference clock with low phase noise and cycle-to-cycle jitter. Phase noise less than 100KHz can be tracked by the PLL and data recovery loops and is less of a problem. Phase noise above 15MHz is filtered by the PLL. The most problematic phase noise occurs in the 1-15MHz range. The source impedance of the clock driver should be 50  $\Omega$  to match the transmission line and reduce reflections which are a source of noise to the system.

This table describes some AC parameters common to SGMII and PCI Express protocols.

#### Table 52. SerDes Reference Clock Common AC Parameters

At recommended operating conditions with XCOREVDD= 1.0V  $\pm$  5%

| Parameter                                                                  | Symbol                | Min  | Max  | Unit | Note |

|----------------------------------------------------------------------------|-----------------------|------|------|------|------|

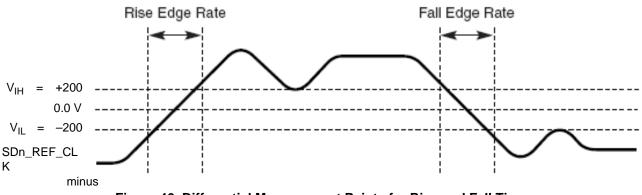

| Rising Edge Rate                                                           | Rise Edge Rate        | 1.0  | 4.0  | V/ns | 2, 3 |

| Falling Edge Rate                                                          | Fall Edge Rate        | 1.0  | 4.0  | V/ns | 2, 3 |

| Differential Input High Voltage                                            | V <sub>IH</sub>       | +200 | —    | mV   | 2    |

| Differential Input Low Voltage                                             | V <sub>IL</sub>       |      | -200 | mV   | 2    |

| Rising edge rate (SDn_REF_CLK) to falling edge rate (SDn_REF_CLK) matching | Rise-Fall<br>Matching | _    | 20   | %    | 1, 4 |

Note:

- 1. Measurement taken from single ended waveform.

- 2. Measurement taken from differential waveform.

- Measured from -200 mV to +200 mV on the differential waveform (derived from SDn\_REF\_CLK minus SDn\_REF\_CLK). The signal must be monotonic through the measurement region for rise and fall time. The 400 mV measurement window is centered on the differential zero crossing. See Figure 46.

- 4. Matching applies to rising edge rate for SDn\_REF\_CLK and falling edge rate for SDn\_REF\_CLK. It is measured using a 200 mV window centered on the median cross point where SDn\_REF\_CLK rising meets SDn\_REF\_CLK falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The Rise Edge Rate of SDn\_REF\_CLK should be compared to the Fall Edge Rate of SDn\_REF\_CLK, the maximum allowed difference should not exceed 20% of the slowest edge rate. See Figure 47.

Figure 46. Differential Measurement Points for Rise and Fall Time

### NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary.

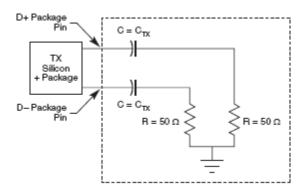

Figure 51. Compliance Test/Measurement Load

# 17 Timers

This section describes the DC and AC electrical specifications for the timers of the MPC8314E.

### **17.1 Timers DC Electrical Characteristics**

This table provides the DC electrical characteristics for the timers pins, including TIN,  $\overline{\text{TOUT}}$ ,  $\overline{\text{TGATE}}$ , and RTC\_CLK.

| Characteristic      | Symbol          | Condition                           | Min  | Max        | Unit |

|---------------------|-----------------|-------------------------------------|------|------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA           | 2.4  | —          | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA            | _    | 0.5        | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA            | _    | 0.4        | V    |

| Input high voltage  | V <sub>IH</sub> | _                                   | 2.1  | NVDD + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                                   | -0.3 | 0.8        | V    |

| Input current       | I <sub>IN</sub> | $0 \text{ V} \leq V_{IN} \leq NVDD$ | _    | ± 5        | μΑ   |

Table 56. Timers DC Electrical Characteristics

## 17.2 Timers AC Timing Specifications

This table provides the timers input and output AC timing specifications.

### Table 57. Timers Input AC Timing Specifications

| Characteristic                    |                    | Min | Unit |

|-----------------------------------|--------------------|-----|------|

| Timers inputs—minimum pulse width | t <sub>TIWID</sub> | 20  | ns   |

Package and Pin Listings

| Signal                          | Package Pin Number | Pin Type | Power<br>Supply | Note |

|---------------------------------|--------------------|----------|-----------------|------|

| PCI_AD[23]                      | C22                | I/O      | NVDD2_OFF       | _    |

| PCI_AD[24]                      | E19                | I/O      | NVDD2_OFF       |      |

| PCI_AD[25]                      | A22                | I/O      | NVDD2_OFF       |      |

| PCI_AD[26]                      | C20                | I/O      | NVDD2_OFF       | _    |

| PCI_AD[27]                      | B21                | I/O      | NVDD2_OFF       | _    |

| PCI_AD[28]                      | D19                | I/O      | NVDD2_OFF       |      |

| PCI_AD[29]                      | A19                | I/O      | NVDD2_OFF       |      |

| PCI_AD[30]                      | A21                | I/O      | NVDD2_OFF       | _    |

| PCI_AD[31]                      | B19                | I/O      | NVDD2_OFF       | _    |

| PCI_C/BE[0]                     | H24                | I/O      | NVDD2_OFF       | _    |

| PCI_C/BE[1]                     | C27                | I/O      | NVDD2_OFF       | —    |

| PCI_C/BE[2]                     | A25                | I/O      | NVDD2_OFF       | _    |

| PCI_C/BE[3]                     | E21                | I/O      | NVDD2_OFF       | _    |

| PCI_PAR                         | G24                | I/O      | NVDD2_OFF       | —    |

| PCI_FRAME                       | C28                | I/O      | NVDD2_OFF       | 5    |

| PCI_TRDY                        | A24                | I/O      | NVDD2_OFF       | 5    |

| PCI_IRDY                        | D25                | I/O      | NVDD2_OFF       | 5    |

| PCI_STOP                        | D23                | I/O      | NVDD2_OFF       | 5    |

| PCI_DEVSEL                      | E22                | I/O      | NVDD2_OFF       | 5    |

| PCI_IDSEL                       | D26                | I        | NVDD2_OFF       | _    |

| PCI_SERR                        | C25                | I/O      | NVDD2_OFF       | 5    |

| PCI_PERR                        | D21                | I/O      | NVDD2_OFF       | 5    |

| PCI_REQ0                        | E18                | I/O      | NVDD2_OFF       | _    |

| PCI_REQ1/CPCI_HS_ES             | C18                | I        | NVDD2_OFF       |      |

| PCI_REQ2                        | E17                | I        | NVDD2_OFF       |      |

| PCI_GNT0                        | B20                | I/O      | NVDD2_OFF       | —    |

| PCI_GNT1/CPCI_HS_LED            | D17                | 0        | NVDD2_OFF       |      |

| PCI_GNT2/CPCI_HS_ENUM           | E15                | 0        | NVDD2_OFF       | _    |

| M66EN                           | L24                | I        | NVDD2_OFF       | _    |

| PCI_CLK0                        | E23                | 0        | NVDD2_OFF       | —    |

| PCI_CLK1                        | F24                | 0        | NVDD2_OFF       | —    |

| PCI_CLK2                        | E25                | 0        | NVDD2_OFF       | —    |

| PCI_PME                         | B23                | I/O      | NVDD2_OFF       | 2    |

| ł                               | ETSEC1/_USBULPI    |          |                 |      |

| GPIO_24/TSEC1_COL/USBDR_TXDRXD0 | J1                 | I/O      | LVDD1_OFF       | _    |

| GPIO_25/TSEC1_CRS/USBDR_TXDRXD1 | H1                 | I/O      | LVDD1_OFF       |      |

|                                 |                    |          |                 |      |

### Table 66. MPC8314E TEPBGA II Pinout Listing (continued)

#### Clocking

The primary clock source can be one of two inputs, SYS\_CLK\_IN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. When the device is configured as a PCI host device, SYS\_CLK\_IN is its primary input clock. SYS\_CLK\_IN feeds the PCI clock divider (÷2) and the multiplexors for PCI\_SYNC\_OUT and PCI\_CLK\_OUT. The CFG\_SYS\_CLKIN\_DIV configuration input selects whether SYS\_CLK\_IN or SYS\_CLK\_IN/2 is driven out on the PCI\_SYNC\_OUT signal.

PCI\_SYNC\_OUT is connected externally to PCI\_SYNC\_IN to allow the internal clock subsystem to synchronize to the system PCI clocks. PCI\_SYNC\_OUT must be connected properly to PCI\_SYNC\_IN, with equal delay to all PCI agent devices in the system, to allow the device to function. When the device is configured as a PCI agent device, PCI\_CLK is the primary input clock. When the device is configured as a PCI agent device the SYS\_CLK\_IN signal should be tied to GND.

As shown in Figure 60, the primary clock input (frequency) is multiplied up by the system phase-locked loop (PLL) and the clock unit to create the coherent system bus clock ( $csb\_clk$ ), the internal clock for the DDR controller ( $ddr\_clk$ ), and the internal clock for the local bus interface unit ( $lbiu\_clk$ ).

The *csb\_clk* frequency is derived from a complex set of factors that can be simplified into the following equation:

$csb_clk = \{PCI_SYNC_IN \times (1 + \sim \overline{CFG_SYS_CLKIN_DIV})\} \times SPMF$

In PCI host mode, PCI\_SYNC\_IN  $\times$  (1 + ~  $\overline{CFG_SYS_CLKIN_DIV}$ ) is the SYS\_CLK\_IN frequency.

The *csb\_clk* serves as the clock input to the e300 core. A second PLL inside the e300 core multiplies up the *csb\_clk* frequency to create the internal clock for the e300 core (*core\_clk*). The system and core PLL multipliers are selected by the SPMF and COREPLL fields in the reset configuration word low (RCWL) which is loaded at power-on reset or by one of the hard-coded reset options. See Chapter 4, "Reset, Clocking, and Initialization," in the *MPC8315E PowerQUICC II Pro Integrated Host Processor Family Reference Manual* for more information on the clock subsystem.

The internal *ddr\_clk* frequency is determined by the following equation:

$ddr_clk = csb_clk \times (1 + \text{RCWL}[\text{DDRCM}])$

Note that  $ddr_clk$  is not the external memory bus frequency;  $ddr_clk$  passes through the DDR clock divider (÷2) to create the differential DDR memory bus clock outputs (MCK and MCK). However, the data rate is the same frequency as  $ddr_clk$ .

The internal *lbiu\_clk* frequency is determined by the following equation:

$lbiu_clk = csb_clk \times (1 + RCWL[LBCM])$

Note that *lbiu\_clk* is not the external local bus frequency; *lbiu\_clk* passes through the LBIU clock divider to create the external local bus clock outputs (LCLK[0:1]). The LBIU clock divider ratio is controlled by LCRR[CLKDIV].

In addition, some of the internal units may be required to be shut off or operate at lower frequency than the  $csb\_clk$  frequency. Those units have a default clock ratio that can be configured by a memory mapped register after the device comes out of reset. Table 67 specifies which units have a configurable clock frequency.

| Conf. No. | SPMF | Core\PLL | Input Clock Frequency (MHz) | CSB Frequency (MHz) | Core Frequency (MHz) |

|-----------|------|----------|-----------------------------|---------------------|----------------------|

| 6         | 0010 | 0000101  | 66.67                       | 133.33              | 333.33               |

| 7         | 0101 | 0000110  | 25                          | 125                 | 375                  |

| 8         | 0100 | 0000110  | 33.33                       | 133.33              | 400                  |

| 9         | 0010 | 0000110  | 66.67                       | 133.33              | 400                  |

Table 73. Suggested PLL Configurations

# 24 Thermal

This section describes the thermal specifications of the MPC8314E.

### 24.1 Thermal Characteristics

This table provides the package thermal characteristics for the  $620.29 \times 29$  mm TEPBGA II.

| Characteristic                         | Board type              | Symbol                 | Value | Unit | Note    |

|----------------------------------------|-------------------------|------------------------|-------|------|---------|

| Junction to ambient natural convection | Single layer board (1s) | $R_{	ext{	heta}JA}$    | 23    | °C/W | 1, 2    |

| Junction to ambient natural convection | Four layer board (2s2p) | $R_{	ext{	heta}JA}$    | 16    | °C/W | 1, 2, 3 |

| Junction to ambient (@200 ft/min)      | Single layer board (1s) | $R_{\thetaJMA}$        | 18    | °C/W | 1, 3    |

| Junction to ambient (@200 ft/min)      | Four layer board (2s2p) | $R_{	extsf{	heta}JMA}$ | 13    | °C/W | 1, 3    |

| Junction to board                      | —                       | $R_{\theta JB}$        | 8     | °C/W | 4       |

| Junction to case                       | _                       | $R_{	ext{	heta}JC}$    | 6     | °C/W | 5       |

| Junction to package top                | Natural convection      | $\Psi_{\text{JT}}$     | 6     | °C/W | 6       |

Table 74. Package Thermal Characteristics for TEPBGA II

Note:

- 2. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

|         | Millennium Electronics (MEI)                    | 408-436-8770 |

|---------|-------------------------------------------------|--------------|

|         | Loroco Sites                                    |              |

|         | 671 East Brokaw Road                            |              |

|         | San Jose, CA 95112                              |              |

|         | Internet: www.mei-thermal.com                   |              |

|         | Tyco Electronics                                | 800-522-6752 |

|         | Chip Coolers <sup>TM</sup>                      |              |

|         | P.O. Box 3668                                   |              |

|         | Harrisburg, PA 17105                            |              |

|         | Internet: www.tycoelectronics.com               |              |

|         | Wakefield Engineering                           | 603-635-2800 |

|         | 33 Bridge St.                                   |              |

|         | Pelham, NH 03076                                |              |

|         | Internet: www.wakefield.com                     |              |

| Interfa | terface material vendors include the following: |              |

|         | Chomerics, Inc.                                 | 781-935-4850 |

|         | 77 Dragon Ct.                                   |              |

|         | Woburn, MA 01801                                |              |

|         | Internet: www.chomerics.com                     |              |

|         | Dow-Corning Corporation                         | 800-248-2481 |

|         | Corporate Center                                |              |

|         | PO BOX 994                                      |              |

|         | Midland, MI 48686-0994                          |              |

|         | Internet: www.dowcorning.com                    |              |

|         | Shin-Etsu MicroSi, Inc.                         | 888-642-7674 |

|         | 10028 S. 51st St.                               |              |

|         | Phoenix, AZ 85044                               |              |

|         | Internet: www.microsi.com                       |              |

|         | The Bergquist Company                           | 800-347-4572 |

|         | 18930 West 78th St.                             |              |

|         | Chanhassen, MN 55317                            |              |

|         | Internet: www.bergquistcompany.com              |              |

### 24.3 Heat Sink Attachment

When attaching heat sinks to these devices, an interface material is required. The best method is to use thermal grease and a spring clip. The spring clip should connect to the printed circuit board, either to the board itself, to hooks soldered to the board, or to a plastic stiffener. Avoid attachment forces which would lift the edge of the package or peel the package from the board. Such peeling forces reduce the solder joint lifetime of the package. Recommended maximum force on the top of the package is 10 lb force (45 Newtons). If an adhesive attachment is planned, the adhesive should be intended for attachment to painted or plastic surfaces and its performance verified under the application requirements.

Power and ground connections must be made to all external VDD, GVDD, LVDD, NVDD, and GND pins of the device.

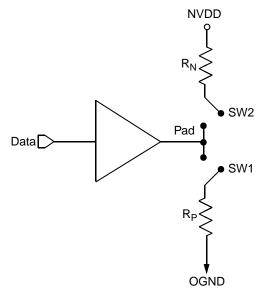

### 25.5 Output Buffer DC Impedance

The MPC8314E drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

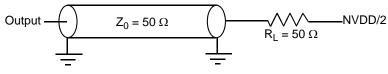

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to NVDD or GND. Then, the value of each resistor is varied until the pad voltage is NVDD/2 (see Figure 62). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_p$  is trimmed until the voltage at the pad equals NVDD/2.  $R_p$  then becomes the resistance of the pull-up devices.  $R_p$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_p + R_N)/2$ .

Figure 62. Driver Impedance Measurement

The value of this resistance and the strength of the driver's current source can be found by making two measurements. First, the output voltage is measured while driving logic 1 without an external differential termination resistor. The measured voltage is  $V_1 = R_{source} \times I_{source}$ . Second, the output voltage is measured while driving logic 1 with an external precision differential termination resistor of value  $R_{term}$ . The measured voltage is  $V_2 = (1/(1/R_1 + 1/R_2)) \times I_{source}$ . Solving for the output impedance gives  $R_{source} = R_{term} \times (V_1/V_2 - 1)$ . The drive current is then  $I_{source} = V_1/R_{source}$ .