Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                     |

|----------------------------|---------------------------------------------------------------------|

| Product Status             | Obsolete                                                            |

| Core Processor             | nX-U8/100                                                           |

| Core Size                  | 8-Bit                                                               |

| Speed                      | 4.2MHz                                                              |

| Connectivity               | I <sup>2</sup> C, SSP, UART/USART                                   |

| Peripherals                | LCD, Melody Driver, POR, PWM, WDT                                   |

| Number of I/O              | 14                                                                  |

| Program Memory Size        | 48KB (24K x 16)                                                     |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 4K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.1V ~ 3.6V                                                         |

| Data Converters            | A/D 2x12b, 2x24b                                                    |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -20°C ~ 70°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 128-TQFP                                                            |

| Supplier Device Package    | -                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/rohm-semi/ml610q428-nnntbz03a7 |

#### PWM

- Resolution 16 bits × 3 channel

- Synchronous serial port

- Master/slave selectable

- LSB first/MSB first selectable

- 8-bit length/16-bit length selectable

- Timer interrupt is used as a serial clock and selection is possible

#### • UART

- TXD/RXD × 1 channel

- Bit length, parity/no parity, odd parity/even parity, 1 stop bit/2 stop bits

- Positive logic/negative logic selectable

- Built-in baud rate generator

- I<sup>2</sup>C bus interface

- Master function only

- Fast mode (400 kbps@4MHz), standard mode (100 kbps@4MHz, 50kbps@500kHz)

- Melody driver

- Scale: 29 types (Melody sound frequency: 508 Hz to 32.768 kHz)

- Tone length: 63 types

- Tempo: 15 types

- Buzzer output mode (4 output modes, 8 frequencies, 16 duty levels)

- RC oscillation type A/D converter

- 24-bit counter

- Time division × 2 channels

- Successive approximation type A/D converter

- 12-bit A/D converter

- Input × 2 channels

- General-purpose ports

- Non-maskable interrupt input port × 1 channel

- Input-only port × 10 channels (including secondary functions)

- Output-only port × 3 channels (including secondary functions)

- Input/output port

- ML610Q428: 14 channels (including secondary functions)

- ML610Q429: 20 channels (including secondary functions)

#### • LCD driver

– Dot matrix can be supported.

ML610Q428: 1392 dots max. (58 seg  $\times$  24 com), 1/1 to 1/24 duty

ML610Q429: 512 dots max. (64 seg  $\times$  8 com) , 1/1 to 1/8 duty

- 1/3 or 1/4 bias (built-in bias generation circuit)

- Frame frequency selecable (approx. 32Hz, 64 Hz, 73 Hz, 85 Hz, and 102 Hz)

- Bias voltage multiplying clock selectable (8 types)

- Contrast adjustment (1/3 bias: 32 steps, 1/4 bias: 20 steps)

- LCD drive stop mode, LCD display mode, all LCDs on mode, and all LCDs off mode selectable

- Programmable display allocation function (available only when 1/1~1/8 duty is selected)

#### Reset

- Reset through the RESET\_N pin

- Power-on reset generation when powered on

- Reset when oscillation stop of the low-speed clock is detected

- Reset by the watchdog timer (WDT) overflow

- Power supply voltage detect function

Judgment voltages: One of 16 levels

Judgment accuracy: ±2% (Typ.)

#### Clock

Low-speed clock: (This LSI can not guarantee the operation withoug low-speed clock)

Crystal oscillation (32.768 kHz)

- High-speed clock:

Built-in RC oscillation (2M/500kHz)

Built-in PLL oscillation (8.192 MHz ±2.5%), crystal/ceramic oscillation (4.096 MHz), external clock

Selection of high-speed clock mode by software:

Built-in RC oscillation, built-in PLL oscillation, crystal/ceramic oscillation, external clock

#### • Power management

- HALT mode: Instruction execution by CPU is suspended (peripheral circuits are in operating states).

- STOP mode: Stop of low-speed oscillation and high-speed oscillation (Operations of CPU and peripheral circuits are stopped.)

- Clock gear: The frequency of high-speed system clock can be changed by software (1/1, 1/2, 1/4, or 1/8 of the oscillation clock)

- Block Control Function: Power down (reset registers and stop clock supply) the circuits of unused peripherals.

#### Guaranteed operating range

Operating temperature: -20°C to 70°C

Operating voltage: V<sub>DD</sub> = 1.1V to 3.6V

$\label{eq:continuous} \bullet \mbox{ Product name} - \mbox{Supported Function}$  The lien up to the ML610Q428and ML610Q429 is below.

| - Chip (Die) -  | ROM type  | Operating temperature | Product availability |

|-----------------|-----------|-----------------------|----------------------|

| ML610Q428-xxxWA | Flash ROM | -20°C to +70°C        | Yes                  |

| ML610Q429-xxxWA | Flash ROM | -20°C to +70°C        | Yes                  |

| -128-pin plastic<br>TQFP - | ROM type  | Operating temperature | Product availability |

|----------------------------|-----------|-----------------------|----------------------|

| ML610Q428-xxxTB            | Flash ROM | -20°C to +70°C        | Yes                  |

| ML610Q429-xxxTB            | Flash ROM | -20°C to +70°C        | Yes                  |

xxx: ROM code number (xxx of the blank product is NNN)

Q:Flash ROM version

WA: Chip TB: TQFP

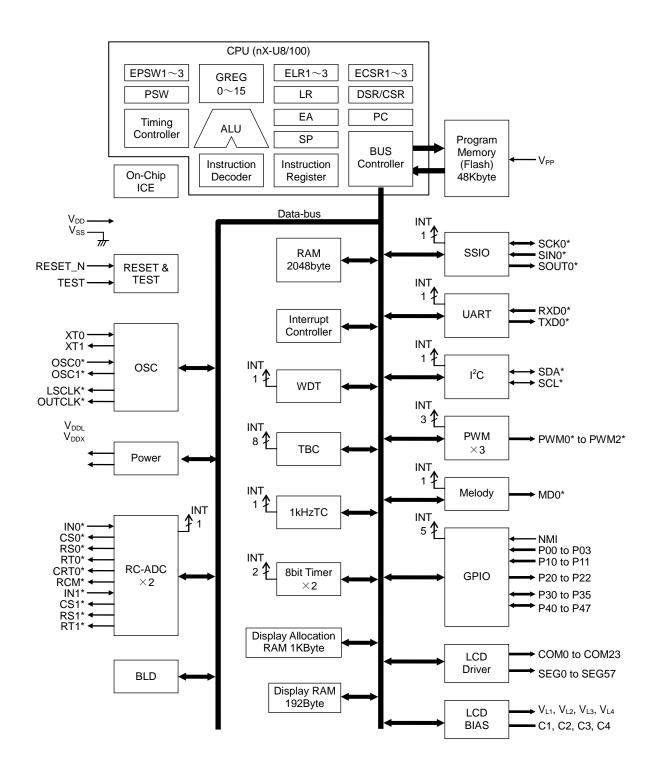

# BLOCK DIAGRAM ML610Q428 Block Diagram

Figure 1 show the block diagram of the ML610Q428. "\*" indicates the secondary function of each port.

Figure 1 ML610Q428 Block Diagram

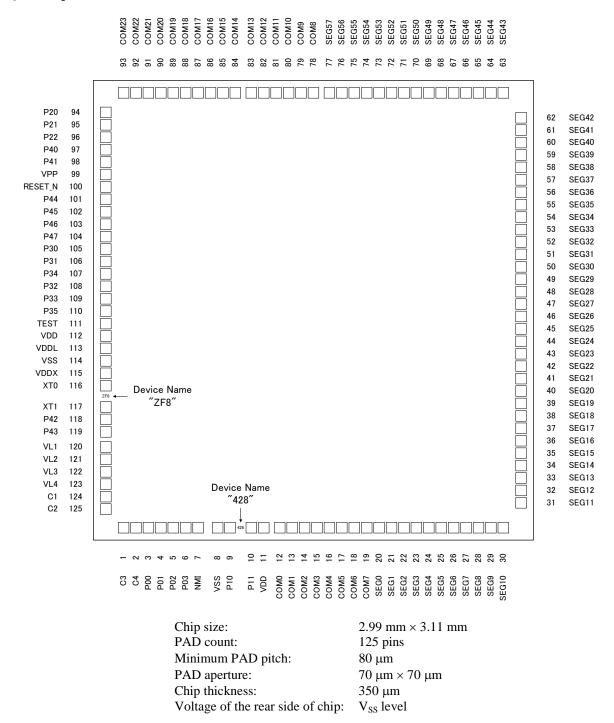

#### ML610Q428 Chip Dimension

Figure 5 ML610Q428 Chip Dimension

#### Note:

Figure 5 is an image figure of the order of PAD, and it differs from an actual image. Refer to the PAD coordinate for detailed arrangement.

A chip angle can be checked by the distinguishing mark of three figures.

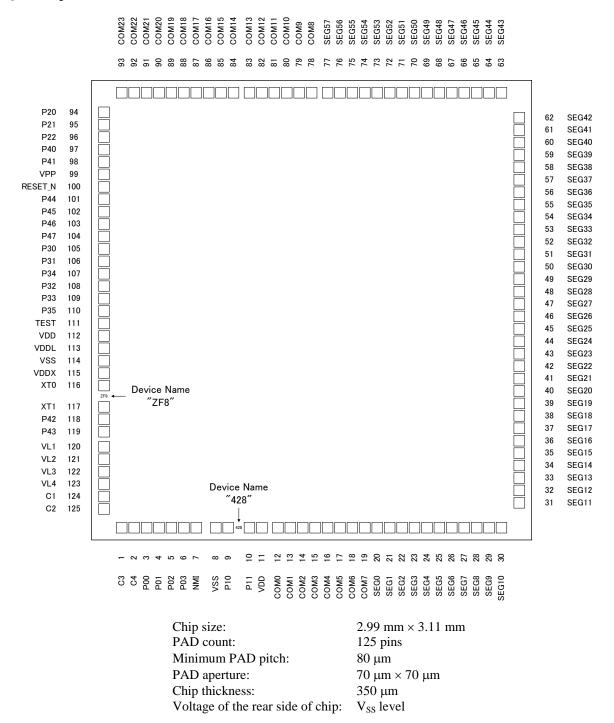

#### ML610Q429 Chip Dimension

## Figure 6 ML610Q429 Chip Dimension

#### Note:

Figure 6 is an image figure of the order of PAD, and it differs from an actual image. Refer to the PAD coordinate for detailed arrangement.

A chip angle can be checked by the distinguishing mark of three figures.

# PIN LIST

| PAD No. Primary function |        |                            |     | S                                                                                   | Secor    | ndary function |          | Teri     | tiary function |          |

|--------------------------|--------|----------------------------|-----|-------------------------------------------------------------------------------------|----------|----------------|----------|----------|----------------|----------|

| Q429                     | Q428   | Pin name                   | 1/0 | Function                                                                            | Pin name |                | Function | Pin name |                | Function |

| 8,114                    |        | Vss                        |     | Negative power supply pin                                                           |          | _              | —        | <u> </u> |                | —        |

| 11,112                   | 11,112 | $V_{DD}$                   | —   | Positive power supply pin                                                           | _        | _              | _        | _        | _              | _        |

| 113                      | 113    | $V_{DDL}$                  | _   | Power supply pin for internal logic (internally generated)                          |          | _              | _        |          |                | _        |

| 115                      | 115    | $V_{DDX}$                  | _   | Power supply pin for<br>low-speed oscillation<br>(internally generated)             | _        | _              | _        | _        |                | _        |

| 99                       | 99     | $V_{PP}$                   | _   | Power supply pin for Flash ROM                                                      | _        | _              | _        | _        | _              | _        |

| 120                      | 120    | $V_{L1}$                   | —   | Power supply pin for LCD bias (internally generated)                                | _        | _              | _        | _        | _              | _        |

| 121                      | 121    | $V_{L2}$                   | _   | Power supply pin for LCD bias (internally generated)                                | _        | _              | _        | _        |                | _        |

| 122                      | 122    | V <sub>L3</sub>            | _   | Power supply pin for LCD bias (internally generated)                                | _        | _              | _        | _        |                | _        |

| 123                      | 123    | $V_{L4}$                   | _   | Power supply pin for LCD bias (internally generated)                                | _        | _              | _        | _        | -              | _        |

| 124                      | 124    | C1                         | _   | Capacitor connection pin for LCD bias generation                                    | _        | _              | _        | _        |                | _        |

| 125                      | 125    | C2                         | _   | Capacitor connection pin for LCD bias generation                                    | _        | _              | _        | _        | _              | _        |

| 1                        | 1      | C3                         | _   | Capacitor connection pin for LCD bias generation                                    | _        | _              | _        | _        |                | _        |

| 2                        | 2      | C4                         | _   | Capacitor connection pin for LCD bias generation                                    | _        | _              | _        | _        |                | _        |

| 111                      | 111    | TEST                       | I/O | Input/output pin for testing                                                        | _        | —              | _        | _        |                | _        |

| 100                      | 100    | RESET_N                    | ı   | Reset input pin                                                                     |          | _              | _        | _        | _              | _        |

| 116                      | 116    | XT0                        | I   | Low-speed clock oscillation pin                                                     | _        | _              | _        | _        | _              | _        |

| 117                      | 117    | XT1                        | 0   | Low-speed clock oscillation pin                                                     | _        | _              | _        | _        |                | _        |

| 7                        | 7      | NMI                        | I   | Non-maskable interrupt pin                                                          | _        | _              | _        | _        | _              | _        |

| 3                        | 3      | P00/EXI0                   | I   | Input port, External interrupt 0 input                                              | _        | _              | _        | _        | _              | _        |

| 4                        | 4      | P01/EXI1                   | I   | Input port, External interrupt 1 input                                              | _        |                | _        | _        | _              | _        |

| 5                        | 5      | P02/EXI2<br>/RXD0<br>/P2CK | I   | Input port, External<br>interrupt 2, UART0<br>receive, PWM2<br>external clock input | _        | _              | _        | _        | _              | _        |

| 6                        | 6      | P03/EXI3                   | ı   | Input port, External interrupt 3                                                    | _        | _              |          | _        | _              |          |

| 90                       | _      | P04/EXI4                   | I/O | Input port, External interrupt 4                                                    | _        | _              | _        | _        |                | _        |

| 91                       | _      | P05/EXI5                   | I/O | Input port, External interrupt 5                                                    | _        | _              | _        | _        | _              | _        |

| 92                       | _      | P06/EXI6                   | I/O | Input port, External interrupt 6                                                    | _        | _              | _        | _        | _              | _        |

| 93                       | —      | P07/EXI7                   | I/O | Input port, External                                                                | _        | —              | _        | _        | —              | _        |

# ML610Q428/ML610Q429

| PAD   | No.   |                 | Prima | ary function                                                       | S            | Secor | ndary function                                        |               | Ter  | tiary function          |

|-------|-------|-----------------|-------|--------------------------------------------------------------------|--------------|-------|-------------------------------------------------------|---------------|------|-------------------------|

| Q429  | Q428  | Pin name        | 1/0   | Function                                                           | Pin name     | 1/0   | Function                                              | Pin name      | I/O  | Function                |

| Q IZO | Q 120 | Tillinanio      | ,, 0  | interrupt 7                                                        | 1 III Hairio | ",    | T directori                                           | i iii iidiiio | ., 0 | T directori             |

| 9     | 9     | P10             | I     | Input port                                                         | OSC0         | I     | High-speed oscillation                                | _             | _    | _                       |

| 10    | 10    | P11             | I     | Input port                                                         | OSC1         | 0     | High-speed oscillation                                | _             | _    | _                       |

| 94    | 94    | P20/LED0        | 0     | Output port                                                        | LSCLK        | 0     | Low-speed clock output                                | PWM2          | 0    | PWM2 output             |

| 95    | 95    | P21/LED1        | 0     | Output port                                                        | OUTCLK       | 0     | High-speed clock output                               | _             | _    | _                       |

| 96    | 96    | P22/LED2        | 0     | Output port                                                        | MD0          | 0     | Melody output                                         | _             | _    | _                       |

| 105   | 105   | P30             | I/O   | Input/output port                                                  | IN0          | ı     | RC type ADC0 oscillation input pin                    | PWM2          | 0    | PWM2 output             |

| 106   | 106   | P31             | I/O   | Input/output port                                                  | CS0          | 0     | RC type ADC0 reference capacitor connection pin       | _             | _    | _                       |

| 108   | 108   | P32             | I/O   | Input/output port                                                  | RS0          | 0     | RC type ADC0 reference resistor connection pin        | _             | _    | _                       |

| 109   | 109   | P33             | I/O   | Input/output port                                                  | RT0          | 0     | RC type ADC0 resistor sensor connection pin           | _             | _    | _                       |

| 107   | 107   | P34             | I/O   | Input/output port                                                  | RCT0         | 0     | RC type ADC0 resistor/capacitor sensor connection pin | PWM0          | 0    | PWM0 output             |

| 110   | 110   | P35             | I/O   | Input/output port                                                  | RCM          | 0     | RC type ADC oscillation monitor                       | PWM1          | 0    | PWM1 output             |

| 97    | 97    | P40             | I/O   | Input/output port                                                  | SDA          | I/O   | I <sup>2</sup> C data input/output                    | SIN0          | ı    | SSIO data input         |

| 98    | 98    | P41             | I/O   | Input/output port                                                  | SCL          | I/O   | I <sup>2</sup> C clock input/output                   | SCK0          | I/O  | SSIO synchronous clock  |

| 118   | 118   | P42             | I/O   | Input/output port                                                  | RXD0         | ı     | UART data input                                       | SOUT0         | 0    | SSIO data output        |

| 119   | 119   | P43             | I/O   | Input/output port                                                  | TXD0         | 0     | UART data output                                      | PWM0          | 0    | PWM0 output             |

| 101   | 101   | P44/T02P<br>0CK | I/O   | Input/output port, Timer<br>0/Timer 2/PWM0<br>external clock input | IN1          | Ι     | RC type ADC1 oscillation input pin                    | SIN0          | _    | SSIO0 data input        |

| 102   | 102   | P45/T13P<br>1CK | I/O   | Input/output port, Timer 1/Timer 3/PWM1 external clock input       | CS1          | 0     | RC type ADC1 reference capacitor connection pin       | SCK0          | I/O  | SSIO0 synchronous clock |

| 103   | 103   | P46/T46P<br>2CK | I/O   | Input/output port,<br>PWM2 external clock<br>input                 | RS1          | 0     | RC type ADC1 reference resistor connection pin        | SOUT0         | 0    | SSIO0 data output       |

| 104   | 1004  | P47             | I/O   | Input/output port                                                  | RT1          | 0     | RC type ADC1 resistor sensor connection pin           | PWM1          | 0    | PWM1 output             |

| 84    | _     | PA0             | I/O   | Input/output port                                                  | _            | _     | _                                                     | _             | —    | _                       |

| 85    | _     | PA1             | I/O   | Input/output port                                                  | _            | _     | _                                                     | _             | _    | _                       |

| 86    | _     | PA2             | I/O   | Input/output port                                                  | _            | _     | _                                                     | _             | _    | _                       |

| 87    | _     | PA3             | I/O   | Input/output port                                                  | _            | _     | _                                                     | _             | _    | _                       |

| 88    | _     | PA4             | I/O   | Input/output port                                                  |              | _     | _                                                     | _             | —    | _                       |

| 89    |       | PA5             | I/O   | Input/output port                                                  | _            | _     |                                                       | _             | _    | _                       |

| 12    | 12    | COM0            | 0     | LCD common pin                                                     | _            | _     |                                                       | _             | _    | _                       |

| 13    | 13    | COM1            | 0     | LCD common pin                                                     |              | _     |                                                       |               | _    | _                       |

| 14    | 14    | COM2            | 0     | LCD common pin                                                     |              | _     |                                                       |               | _    | _                       |

| 15    | 15    | COM3            | 0     | LCD common pin                                                     | _            | _     |                                                       |               | _    | _                       |

| 16    | 16    | COM4            | 0     | LCD common pin                                                     |              | _     | _                                                     |               | _    | _                       |

| 17    | 17    | COM5            | 0     | LCD common pin                                                     |              | _     | _                                                     |               | _    | _                       |

| 18    | 18    | COM6            | 0     | LCD common pin                                                     |              | _     | _                                                     |               | _    | _                       |

| 19    | 19    | COM7            | 0     | LCD common pin                                                     |              | _     | _                                                     | _             | _    | _                       |

|       | 78    | COM8            | 0     | LCD common pin                                                     | _            | _     |                                                       | _             | _    | _                       |

|       | 79    | COM9            | 0     | LCD common pin                                                     | _            |       | <u> </u>                                              | _             | _    | _                       |

| _     | 80    | COM10           | 0     | LCD common pin                                                     |              | _     |                                                       |               | _    | _                       |

|       | 81    | COM11           | 0     | LCD common pin                                                     | _            |       |                                                       | _             | _    | _                       |

|       | 82    | COM12           | 0     | LCD common pin                                                     | _            | _     | <u> </u>                                              | _             | _    | _                       |

| _     | 83    | COM13           | 0     | LCD common pin                                                     | _            | _     | <u> </u>                                              | _             | _    | _                       |

|       | 84    | COM14           | 0     | LCD common pin                                                     | _            | _     | <del></del>                                           |               | _    | _                       |

| _     | 85    | COM15           | 0     | LCD common pin                                                     | _            | _     | _                                                     |               | _    | _                       |

# PIN DESCRIPTION

|               |        |                                                                                              | Primary/   |           |

|---------------|--------|----------------------------------------------------------------------------------------------|------------|-----------|

| Pin name      | 1/0    | Description                                                                                  | Secondary/ | Logic     |

| 1 III Hallio  | 1,0    | Beschption                                                                                   | Tertiary   | Logic     |

| System        | l      |                                                                                              | Tortiary   |           |

| RESET_N       | ı      | Reset input pin. When this pin is set to a "L" level, system reset mode is                   | _          | Negative  |

|               |        | set and the internal section is initialized. When this pin is set to a "H" level             |            | rioganio  |

|               |        | subsequently, program execution starts. A pull-up resistor is internally                     |            |           |

|               |        | connected.                                                                                   |            |           |

| XT0           | -      | Crystal connection pin for low-speed clock.                                                  | _          | _         |

| XT1           | 0      | A 32.768 kHz crystal oscillator (see measuring circuit 1) is connected to                    |            |           |

|               |        | this pin. Capacitors CDL and CGL are connected across this pin and $V_{\rm SS}$ as required. | _          | _         |

| OSC0          |        | Crystal/ceramic connection pin for high-speed clock.                                         | Secondary  |           |

| OSC1          | 0      | A crystal or ceramic is connected to this pin (4.1 MHz max.). Capacitors                     | Secondary  |           |

| 0301          |        | CDH and CGH (see measuring circuit 1) are connected across this pin                          | Secondary  | _         |

|               |        | and V <sub>SS</sub> .                                                                        |            |           |

|               |        | This pin is used as the secondary function of the P10 pin(OSC0) and P11                      |            |           |

|               |        | pin(OSC1).                                                                                   |            |           |

| LSCLK         | 0      | Low-speed clock output pin. This pin is used as the secondary function of                    | Secondary  | _         |

| OUTOUK        |        | the P20 pin.                                                                                 | 0          |           |

| OUTCLK        | 0      | High-speed clock output pin. This pin is used as the secondary function of the P21 pin.      | Secondary  | _         |

| General-purpo | ose in | put port                                                                                     |            |           |

| P00-P03       | Ι      | General-purpose input port.                                                                  | Primary    | Positive  |

|               |        | Since these pins have secondary functions, the pins cannot be used as a                      |            |           |

|               |        | port when the secondary functions are used.                                                  |            |           |

| P04-P07       | I      | General-purpose input port.                                                                  | Primary    | Positive  |

|               |        | Since these pins have secondary functions, the pins cannot be used as a                      |            |           |

|               |        | port when the secondary functions are used.                                                  |            |           |

|               |        | These pins are for the ML610Q429, but are not provided in the ML610Q428.                     |            |           |

| P10-P11       | ı      | General-purpose input port.                                                                  | Drimon     | Positive  |

| P10-P11       | '      | Since these pins have secondary functions, the pins cannot be used as a                      | Primary    | Positive  |

|               |        | port when the secondary functions are used.                                                  |            |           |

| General-purpo | ose oi |                                                                                              | 1          |           |

| P20-P22       | 0      | General-purpose output port.                                                                 | Primary    | Positive  |

| 1 20 1 22     |        | Since these pins have secondary functions, the pins cannot be used as a                      | 1 minary   | 1 0311110 |

|               |        | port when the secondary functions are used.                                                  |            |           |

| General-purpo | ose in | put/output port                                                                              |            |           |

| P30-P35       | I/O    |                                                                                              | Primary    | Positive  |

|               |        | Since these pins have secondary functions, the pins cannot be used as a                      |            |           |

|               |        | port when the secondary functions are used.                                                  |            |           |

| P40-P47       | I/O    | General-purpose input/output port.                                                           | Primary    | Positive  |

|               |        | Since these pins have secondary functions, the pins cannot be used as a                      |            |           |

|               |        | port when the secondary functions are used.                                                  |            |           |

| PA0-PA5       | I/O    | General-purpose input/output port.                                                           | Primary    | Positive  |

|               |        | These pins are for the ML610Q429, but are not provided in the                                |            |           |

|               |        | ML610Q428.                                                                                   |            |           |

| Pin name                    |        |                                                                                                                                                                                                                                              | Primary/<br>Secondary/<br>Tertiary | Logic                 |

|-----------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|

| UART                        |        |                                                                                                                                                                                                                                              |                                    |                       |

| TXD0                        | 0      | UART data output pin. This pin is used as the secondary function of the P43 pin.                                                                                                                                                             | Secondary                          | Positive              |

| RXD0                        | I      | UART data input pin. This pin is used as the secondary function of the P42 or the primary function of the P02 pin.                                                                                                                           | Primary/Se condary                 | Positive              |

| I <sup>2</sup> C bus interf | ace    |                                                                                                                                                                                                                                              |                                    |                       |

| SDA                         | I/O    | I <sup>2</sup> C data input/output pin. This pin is used as the secondary function of the P40 pin. This pin has an NMOS open drain output. When using this pin as a function of the I <sup>2</sup> C, externally connect a pull-up resistor. | Secondary                          | Positive              |

| SCL                         | 0      | I <sup>2</sup> C clock output pin. This pin is used as the secondary function of the P41 pin. This pin has an NMOS open drain output. When using this pin as a function of the I <sup>2</sup> C, externally connect a pull-up resistor.      | Secondary                          | Positive              |

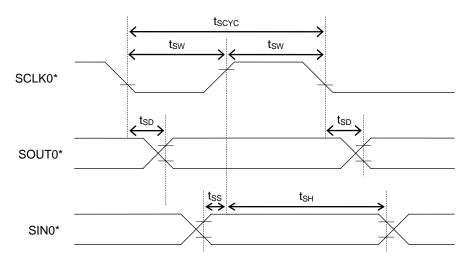

| Synchronous                 | serial | (SSIO)                                                                                                                                                                                                                                       |                                    |                       |

| SCK0                        | I/O    | Synchronous serial clock input/output pin. This pin is used as the tertiary function of the P41 or P45 pin.                                                                                                                                  | Tertiary                           | _                     |

| SIN0                        | I      | Synchronous serial data input pin. This pin is used as the tertiary function of the P40 or P44 pin.                                                                                                                                          | Tertiary                           | Positive              |

| SOUT0                       | 0      | Synchronous serial data output pin. This pin is used as the tertiary function of the P42 or P46 pin.                                                                                                                                         | Tertiary                           | Positive              |

| PWM                         |        |                                                                                                                                                                                                                                              |                                    |                       |

| PWM0                        | 0      | PWM0 output pin. This pin is used as the tertiary function of the P43 or P34 pin.                                                                                                                                                            | Tertiary                           | Positive              |

| T0P0CK                      | I      | PWM0 external clock input pin. This pin is used as the primary function of the P44 pin.                                                                                                                                                      |                                    | _                     |

| PWM1                        | 0      | PWM1 output pin. This pin is used as the tertiary function of the P47 or P35 pin.                                                                                                                                                            | Tertiary                           | Positive              |

| T1P1CK                      | I      | PWM1 external clock input pin. This pin is used as the primary function of the P45 pin.                                                                                                                                                      | Primary                            | _                     |

| PWM2                        | 0      | PWM2 output pin. This pin is used as the tertiary function of the P20 or P30 pin.                                                                                                                                                            | Tertiary                           | Positive              |

| P2CK                        | I      | PWM2 external clock input pin. This pin is used as the primary function of the P02 pin.                                                                                                                                                      | Primary                            |                       |

| External inter              | rupt   |                                                                                                                                                                                                                                              |                                    |                       |

| NMI                         | ı      | External non-maskable interrupt input pin. An interrupt is generated on both edges.                                                                                                                                                          | Primary                            | Positive/<br>negative |

| EXI0-7                      | I      | External maskable interrupt input pins. Interrupt enable and edge selection can be performed for each bit by software. These pins are used as the primary functions of the P00-P07 pins.                                                     | Primary                            | Positive/<br>negative |

| Timer                       |        |                                                                                                                                                                                                                                              |                                    |                       |

| T0P0CK                      | I      | External clock input pin used for Timer 0. This pin is used as the primary function of the P44 pin.                                                                                                                                          | Primary                            | _                     |

| T1P1CK                      | I      | External clock input pin used for Timer 1. This pin is used as the primary function of the P45 pin.                                                                                                                                          | Primary                            |                       |

| Melody                      |        |                                                                                                                                                                                                                                              |                                    |                       |

| MD0                         | 0      | Melody/buzzer signal output pin. This pin is used as the secondary function of the P22 pin.                                                                                                                                                  | Secondary                          | Positive/<br>negative |

| LED drive                   |        |                                                                                                                                                                                                                                              |                                    |                       |

| LED0-2                      | 0      | Nch open drain output pins to drive LED.                                                                                                                                                                                                     | Primary                            | Positive/<br>negative |

| Pin name         | I/O                                                                                                                                                                          | Description                                                                                                                                                                                             | Primary/<br>Secondary/ | Logic |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|--|

|                  |                                                                                                                                                                              | '                                                                                                                                                                                                       | Tertiary               |       |  |

| RC oscillation   | type                                                                                                                                                                         | A/D converter                                                                                                                                                                                           |                        |       |  |

| IN0              | N0 I Channel 0 oscillation input pin. This pin is used as the secondary function of the P30 pin.  S0 O Channel 0 reference capacitor connection pin. This pin is used as the |                                                                                                                                                                                                         |                        |       |  |

| CS0              | 0                                                                                                                                                                            | Secondary                                                                                                                                                                                               | _                      |       |  |

| RS0              | 0                                                                                                                                                                            | secondary function of the P31 pin.  This pin is used as the secondary function of the P32 pin which is the reference resistor connection pin of Channel 0.                                              | Secondary              | _     |  |

| RT0              | 0                                                                                                                                                                            | Resistor sensor connection pin of Channel 0 for measurement. This pin is used as the secondary function of the P34 pin.                                                                                 | Secondary              | _     |  |

| CRT0             | 0                                                                                                                                                                            | Resistor/capacitor sensor connection pin of Channel 0 for measurement. This pin is used as the secondary function of the P33 pin.                                                                       | Secondary              | _     |  |

| RCM              | 0                                                                                                                                                                            | RC oscillation monitor pin. This pin is used as the secondary function of the P35 pin.                                                                                                                  | Secondary              | _     |  |

| IN1              | I                                                                                                                                                                            | Oscillation input pin of Channel 1. This pin is used as the secondary function of the P44 pin.                                                                                                          | Secondary              | _     |  |

| CS1              | 0                                                                                                                                                                            | Reference capacitor connection pin of Channel 1. This pin is used as the secondary function of the P45 pin.                                                                                             | Secondary              |       |  |

| RS1              | 0                                                                                                                                                                            | Reference resistor connection pin of Channel 1. This pin is used as the secondary function of the P46 pin.                                                                                              | Secondary              | _     |  |

| RT1              | 0                                                                                                                                                                            | Resistor sensor connection pin for measurement of Channel 1. This pin is used as the secondary function of the P47 pin.                                                                                 | Secondary              | _     |  |

| LCD drive sig    | ınal                                                                                                                                                                         | ·                                                                                                                                                                                                       |                        |       |  |

| COM0-7           | 0                                                                                                                                                                            | Common output pins.                                                                                                                                                                                     | _                      | _     |  |

| COM8-23          | 0                                                                                                                                                                            | Common output pins. These pins are for the ML610Q428, but are not provided in the ML610Q429.                                                                                                            | _                      | _     |  |

| SEG0-57          | 0                                                                                                                                                                            | Segment output pin.                                                                                                                                                                                     | _                      | _     |  |

| SEG58-63         | 0                                                                                                                                                                            | Segment output pins. These pins are for the ML610Q429, but are not provided in the ML610Q428.                                                                                                           | _                      | _     |  |

| LCD driver po    | ower s                                                                                                                                                                       |                                                                                                                                                                                                         | ı.                     |       |  |

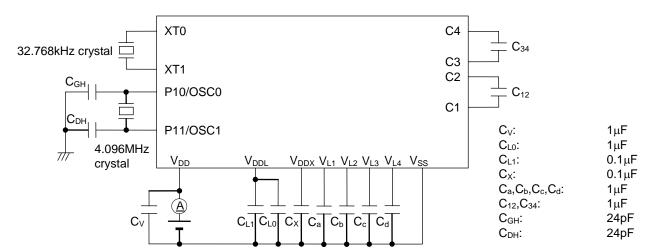

| V <sub>L1</sub>  |                                                                                                                                                                              | Power supply pins for LCD bias (internally generated). Capacitors Ca, Cb,                                                                                                                               | _                      |       |  |

| V <sub>L2</sub>  |                                                                                                                                                                              | Cc, and Cd (see measuring circuit 1) are connected between V <sub>SS</sub> and V <sub>L1</sub> ,                                                                                                        |                        |       |  |

| V <sub>L2</sub>  |                                                                                                                                                                              | $V_{L2}$ , $V_{L3}$ , and $V_{L4}$ , respectively.                                                                                                                                                      |                        |       |  |

|                  |                                                                                                                                                                              |                                                                                                                                                                                                         | _                      |       |  |

| V <sub>L4</sub>  | _                                                                                                                                                                            |                                                                                                                                                                                                         | _                      |       |  |

| C1               | <u> </u>                                                                                                                                                                     | Power supply pins for LCD bias (internally generated). Capacitors C12                                                                                                                                   |                        |       |  |

| C2               | <u> </u>                                                                                                                                                                     | and C34 (see measuring circuit 1) are connected between C1 and C2 and                                                                                                                                   |                        | _     |  |

| C3               | _                                                                                                                                                                            | between C3 and C4, respectively.                                                                                                                                                                        | _                      | _     |  |

| C4               | _                                                                                                                                                                            |                                                                                                                                                                                                         |                        |       |  |

| For testing      |                                                                                                                                                                              |                                                                                                                                                                                                         |                        |       |  |

| TEST             | I/O                                                                                                                                                                          | Input/output pin for testing. A pull-down resistor is internally connected.                                                                                                                             | _                      | _     |  |

| Power supply     |                                                                                                                                                                              | •                                                                                                                                                                                                       |                        |       |  |

| V <sub>SS</sub>  | _                                                                                                                                                                            | Negative power supply pin.                                                                                                                                                                              | _                      | _     |  |

| V <sub>DD</sub>  | <b> </b>                                                                                                                                                                     | Positive power supply pin.                                                                                                                                                                              |                        |       |  |

| V <sub>DDL</sub> | _                                                                                                                                                                            | Positive power supply pin:  Positive power supply pin (internally generated) for internal logic.  Capacitors CL0 and CL1 (see measuring circuit 1) are connected between this pin and V <sub>SS</sub> . | _                      |       |  |

| $V_{DDX}$        | _                                                                                                                                                                            | Plus-side power supply pin (internally generated) for low-speed oscillation. Capacitor Cx (see measuring circuit 1) is connected between this pin and V <sub>SS</sub> .                                 | _                      | _     |  |

| $V_{PP}$         | _                                                                                                                                                                            | Power supply pin for programming Flash ROM. A pull-up resistor is internally connected.                                                                                                                 |                        | _     |  |

# **ELECTRICAL CHARACTERISTICS**

# ABSOLUTE MAXIMUM RATINGS

$(V_{SS} = 0V)$

| Parameter              | Symbol            | Condition          | Rating                       | Unit |

|------------------------|-------------------|--------------------|------------------------------|------|

| Power supply voltage 1 | $V_{DD}$          | Ta = 25°C          | -0.3 to +4.6                 | V    |

| Power supply voltage 2 | V <sub>PP</sub>   | Ta = 25°C          | -0.3 to +9.5                 | V    |

| Power supply voltage 3 | V <sub>DDL</sub>  | Ta = 25°C          | -0.3 to +3.6                 | V    |

| Power supply voltage 4 | V <sub>DDX</sub>  | Ta = 25°C          | -0.3 to +3.6                 | V    |

| Power supply voltage 5 | V <sub>L1</sub>   | Ta = 25°C          | -0.3 to +1.75                | V    |

| Power supply voltage 6 | $V_{L2}$          | Ta = 25°C          | -0.3 to +3.5                 | V    |

| Power supply voltage 7 | V <sub>L3</sub>   | Ta = 25°C          | -0.3 to +5.25                | V    |

| Power supply voltage 8 | V <sub>L4</sub>   | Ta = 25°C          | -0.3 to +7.0                 | V    |

| Input voltage          | V <sub>IN</sub>   | Ta = 25°C          | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output voltage         | V <sub>OUT</sub>  | Ta = 25°C          | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output current 1       | I <sub>OUT1</sub> | Port3–A, Ta = 25°C | -12 to +11                   | mA   |

| Output current 2       | I <sub>OUT2</sub> | Port2, Ta = 25°C   | Port2, Ta = 25°C —12 to +20  |      |

| Power dissipation      | PD                | Ta = 25°C          | 122                          | mW   |

| Storage temperature    | T <sub>STG</sub>  | _                  | −55 to +150                  | °C   |

## RECOMMENDED OPERATING CONDITIONS

$(V_{SS} = 0V)$

|                                                                                 |                                   |                                                                                                                         |                                          | •    |

|---------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------|

| Parameter                                                                       | Symbol                            | Condition                                                                                                               | Range                                    | Unit |

| Operating temperature                                                           | T <sub>OP</sub>                   | <u> </u>                                                                                                                | -20 to +70                               | °C   |

| Operating voltage                                                               | $V_{DD}$                          | <del></del>                                                                                                             | 1.1 to 3.6                               | V    |

| Operating frequency (CPU)                                                       | f <sub>OP</sub>                   | $V_{DD} = 1.1 \text{ to } 3.6 \text{V}$ $V_{DD} = 1.3 \text{ to } 3.6 \text{V}$ $V_{DD} = 1.8 \text{ to } 3.6 \text{V}$ | 30k to 36k<br>30k to 650k<br>30k to 4.2M | Hz   |

| Capacitor externally connected to V <sub>DDL</sub> pin                          | C <sub>L0</sub>                   | <del>-</del>                                                                                                            | 1.0±30%<br>0.1±30%                       | μF   |

| Capacitor externally connected to V <sub>DDX</sub> pin                          | C <sub>X</sub>                    | _                                                                                                                       | 0.1±30%                                  | μF   |

| Capacitors externally connected to V <sub>L1, 2, 3, 4</sub> pins                | C <sub>a, b, c, d</sub>           | _                                                                                                                       | 1.0±30%                                  | μF   |

| Capacitors externally connected across C1 and C2 pins and across C3 and C4 pins | C <sub>12</sub> , C <sub>34</sub> | _                                                                                                                       | 1.0±30%                                  | μF   |

# ML610Q428/ML610Q429

#### **CLOCK GENERATION CIRCUIT OPERATING CONDITIONS**

$(V_{SS} = 0V)$

|                                                                                 |                                  | 0 1111                                              |      | Rating        |      |      |

|---------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------|------|---------------|------|------|

| Parameter                                                                       | Symbol                           | Condition                                           | Min. | Тур.          | Max. | Unit |

| Low-speed crystal oscillation frequency                                         | f <sub>XTL</sub>                 | _                                                   | _    | 32.768k       | _    | Hz   |

| Recommended equivalent series resistance value of low-speed crystal oscillation | $R_L$                            | _                                                   | _    | _             | 40k  | Ω    |

|                                                                                 |                                  | C <sub>L</sub> =6pF of<br>crystal<br>oscillation *2 |      | 0             | _    |      |

| Low-speed crystal oscillation external capacitor *1                             | C <sub>DL</sub> /C <sub>GL</sub> | C <sub>L</sub> =9pF of<br>crystal<br>oscillation    | _    | 6             | _    | pF   |

|                                                                                 |                                  | C <sub>L</sub> =12pF of<br>crystal<br>oscillation   | _    | 12            | _    |      |

| High-speed crystal/ceramic oscillation frequency                                | f <sub>XTH</sub>                 |                                                     |      | 4.0M / 4.096M |      | Hz   |

| High-speed crystal oscillation                                                  | Срн                              | _                                                   |      | 24            | _    | nE   |

| external capacitor                                                              | $C_GH$                           | _                                                   | _    | 24            | _    | pF   |

<sup>\*1:</sup> The external C<sub>DL</sub> and C<sub>GL</sub> need to be adjusted in consideration of variation of internal loading capacitance C<sub>D</sub> and C<sub>G</sub>, and other additional capacitance such as PCB layout.

When using a crystal oscillator  $C_L = 6pF$ , there is a possibility that can not be adjusted by external  $C_{DL}$  and  $C_{GL}$ .

### DC CHARACTERISTICS (4/5)

$(V_{DD} = 1.1 \text{ to } 3.6\text{V}, V_{SS} = 0\text{V}, \text{ Ta} = -20 \text{ to } +70^{\circ}\text{C}, \text{ unless otherwise specified)}$  (4/5)

|                                              |        |                                | .1 to 3.6V, $V_{SS} = 0V$ , T                                                      | <u>a = -20 t</u>        | Rating                  | uriless o  |         | Measuring |

|----------------------------------------------|--------|--------------------------------|------------------------------------------------------------------------------------|-------------------------|-------------------------|------------|---------|-----------|

| Parameter                                    | Symbol | Con                            | dition                                                                             | Min.                    | Тур.                    | Max.       | Unit    | circuit   |

|                                              |        | IOH1 = -0.5mA,                 | $V_{DD} = 1.8 \text{ to } 3.6 \text{V}$                                            | V <sub>DD</sub><br>-0.5 | _                       | _          |         |           |

| Output voltage 1 (P20–P22/2 <sup>nd</sup>    | VOH1   | IOH1 = -0.1mA,                 | IOH1 = -0.1mA, $V_{DD}$ = 1.3 to 3.6V                                              |                         | _                       |            |         |           |

| function is selected)                        |        | IOH1 = -0.03mA, \              | $V_{\rm DD} = 1.1 \text{ to } 3.6 \text{V}$                                        | V <sub>DD</sub><br>-0.3 | _                       | _          |         |           |

| (P30–P36)<br>(P40–P47)                       |        | IOL1 = +0.5mA,                 | $V_{DD} = 1.8 \text{ to } 3.6 \text{V}$                                            | _                       | _                       | 0.5        | 1       |           |

| (PA0-PA5)*1                                  | VOL1   | IOL1 = +0.1mA,                 | $V_{DD} = 1.3 \text{ to } 3.6 \text{V}$                                            | _                       | _                       | 0.5        | ]       |           |

| ,                                            | VOLI   | IOL1 = +0.03mA                 | $V_{DD} = 1.1 \text{ to } 3.6 \text{ V}$                                           | _                       | _                       | 0.3        |         |           |

|                                              |        | IOH1 = −0.5mA,                 | $V_{DD} = 1.8 \text{ to } 3.6 \text{V}$                                            | V <sub>DD</sub><br>-0.5 | _                       | _          |         |           |

| Output voltage 2<br>(P20–P22/2 <sup>nd</sup> | VOH2   | IOH1 = -0.1mA,                 | V <sub>DD</sub> = 1.3 to 3.6V                                                      | V <sub>DD</sub><br>-0.3 | _                       | _          |         |           |

| function is Not selected)                    |        | IOH1 = -0.03mA                 | , V <sub>DD</sub> = 1.1 to 3.6V                                                    | V <sub>DD</sub><br>-0.3 | _                       | _          |         |           |

|                                              | VOL2   | IOL2 = +5mA, \                 | $V_{DD} = 1.8 \text{ to } 3.6 \text{V}$                                            | _                       | _                       | 0.5        |         |           |

| Output voltage 3 (P40–P41)                   | VOL3   |                                | V <sub>DD</sub> = 2.0 to 3.6V ode is selected)                                     | _                       | _                       | 0.4        | V       | 2         |

|                                              | VOH4   | ,                              | mA, VL1=1.2V                                                                       | V <sub>L4</sub><br>-0.2 | _                       | _          |         |           |

|                                              | VOMH4  | IOMH4 = +0.2                   | — —                                                                                | _                       | V <sub>L3</sub><br>+0.2 |            |         |           |

|                                              | VOMH4S | IOMH4S = −0.                   | V <sub>L3</sub><br>-0.2                                                            | _                       |                         |            |         |           |

| Output voltage 4<br>(COM0–23)                | VOM4   | IOM4 = +0.2                    | -0.2                                                                               | _                       | V <sub>L2</sub><br>+0.2 |            |         |           |

| (SEG0-63)                                    | VOM4S  | IOM4S = −0.2                   | V <sub>L2</sub><br>-0.2                                                            | _                       | _                       |            |         |           |

|                                              | VOML4  | IOML4 = +0.2                   | _                                                                                  |                         | V <sub>L1</sub><br>+0.2 |            |         |           |

|                                              | VOML4S | IOML4S = −0.                   | 2mA, VL1=1.2V                                                                      | V <sub>L1</sub><br>-0.2 | _                       | _          |         |           |

|                                              | VOL4   | IOL4 = +0.2r                   | mA, VL1=1.2V                                                                       | _                       | _                       | 0.2        | 1       |           |

| Output leakage<br>(P20–P22)<br>(P30–P35)     | ЮОН    | VOH = V <sub>DD</sub> (in hig  | h-impedance state)                                                                 | _                       | _                       | 1          | μА      | 3         |

| (P40–P47)<br>(PA0–PA5) <sup>*1</sup>         | IOOL   | VOL = V <sub>SS</sub> (in high | h-impedance state)                                                                 | -1                      | _                       | _          |         |           |

|                                              | IIH1   | VIH1                           | = V <sub>DD</sub>                                                                  | 0                       |                         | 1          |         |           |

| Input current 1                              |        |                                | $V_{DD} = 1.8 \text{ to } 3.6 \text{V}$                                            | -600                    | -300                    | -20        |         |           |

| (RESET_N)                                    | IIL1   | VIL1 = V <sub>SS</sub>         | $V_{DD} = 1.3 \text{ to } 3.6 \text{V}$                                            | -600                    | -300                    | -10        |         |           |

|                                              |        |                                | $V_{DD} = 1.1 \text{ to } 3.6 \text{V}$                                            | -600                    | -300                    | -2         |         |           |

| Input current 1                              | IIH1   | VIH1 = V <sub>DD</sub>         | $V_{DD} = 1.8 \text{ to } 3.6 \text{V}$<br>$V_{DD} = 1.3 \text{ to } 3.6 \text{V}$ | 20<br>10                | 300                     | 600<br>600 |         |           |

| Input current 1<br>(TEST)                    | ''''   | VIIII = VDD                    | $V_{DD} = 1.3 \text{ to } 3.6 \text{V}$ $V_{DD} = 1.1 \text{ to } 3.6 \text{V}$    | 2                       | 300<br>300              | 600        | μΑ      | 4         |

| · - ·/                                       | IIL1   | VII.1                          | $I = V_{ss}$                                                                       | -1                      | _                       | _          | μΑ      | 7         |

| Input current 0                              |        |                                | $V_{DD} = 1.8 \text{ to } 3.6 \text{V}$                                            | 2                       | 30                      | 200        |         |           |

| Input current 2<br>(NMI)                     | IIH2   | $VIH2 = V_{DD}$                | $V_{DD} = 1.3 \text{ to } 3.6 \text{V}$                                            | 0.2                     | 30                      | 200        | 1       |           |

| (P00–P03)<br>(P04–P07) *1                    |        | (when pulled-down)             | $V_{DD} = 1.1 \text{ to } 3.6 \text{V}$                                            | 0.01                    | 30                      | 200        | 1       |           |

|                                              | III o  | VIL2 = V <sub>SS</sub>         | $V_{DD} = 1.8 \text{ to } 3.6 \text{V}$                                            | -200                    | -30                     | -2         |         |           |

| (P10-P11)                                    | IIL2   | (when pulled-up)               | $V_{DD} = 1.3 \text{ to } 3.6 \text{V}$                                            | -200                    | -30                     | -0.2       | <u></u> |           |

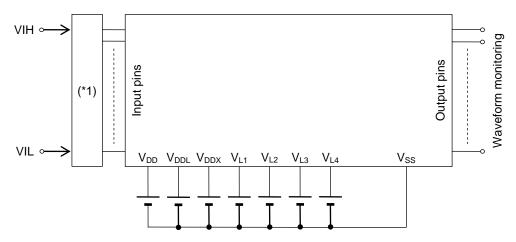

#### **MEASURING CIRCUITS**

#### **MEASURING CIRCUIT 1**

32.768kHz crystal resonator DT-26 (Load capacitance 6pF) (Made by KDS:DAISHINKU CORP.)

4.096MHz crystal: HC49SFWB (Kyocera)

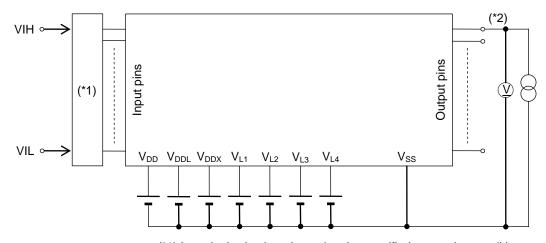

#### **MEASURING CIRCUIT 2**

- (\*1) Input logic circuit to determine the specified measuring conditions.

- (\*2) Measured at the specified output pins.

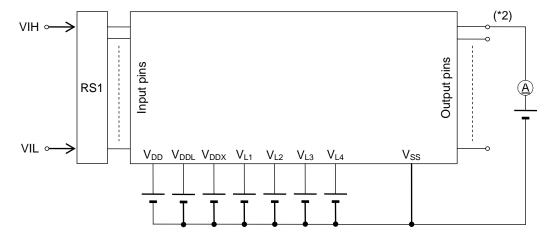

#### **MEASURING CIRCUIT 3**

- \*1: Input logic circuit to determine the specified measuring conditions.

- \*2: Measured at the specified output pins.

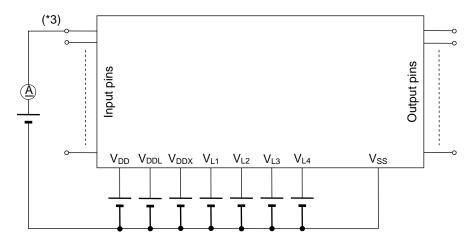

#### **MEASURING CIRCUIT 4**

\*3: Measured at the specified output pins.

## **MEASURING CIRCUIT 5**

\*1: Input logic circuit to determine the specified measuring conditions.

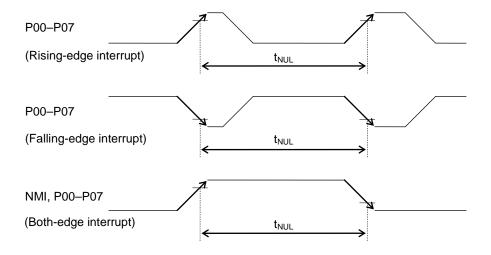

# **AC CHARACTERISTICS (External Interrupt)**

$(V_{DD} = 1.1 \text{ to } 3.6\text{V}, V_{SS} = 0\text{V}, \text{Ta} = -20 \text{ to } +70^{\circ}\text{C}, \text{ unless otherwise specified})$

| Davamatar                         | Symbol           | Condition                                                                      | Rating |      |       | l limit |

|-----------------------------------|------------------|--------------------------------------------------------------------------------|--------|------|-------|---------|

| Parameter                         |                  |                                                                                | Min.   | Тур. | Max.  | Unit    |

| External interrupt disable period | T <sub>NUL</sub> | Interrupt: Enabled (MIE = 1),<br>CPU: NOP operation<br>System clock: 32.768kHz | 76.8   | _    | 106.8 | μS      |

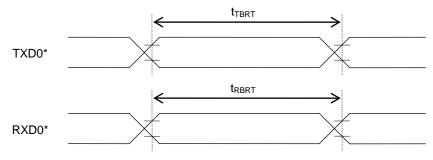

#### AC CHARACTERISTICS (UART)

$(V_{DD} = 1.3 \text{ to } 3.6 \text{V}, V_{SS} = 0 \text{V}, \text{Ta} = -20 \text{ to } +70 ^{\circ}\text{C}, \text{ unless otherwise specified})$

| Parameter          | Symbol            | Condition | Rating                   |       |                          | Linit |

|--------------------|-------------------|-----------|--------------------------|-------|--------------------------|-------|

|                    |                   |           | Min.                     | Тур.  | Max.                     | Unit  |

| Transmit baud rate | t <sub>TBRT</sub> | _         | _                        | BRT*1 | _                        | s     |